# FPDLINK DSI 协议简析

---

Lijia Zhu

## 摘要

随着新能源汽车的高速发展，汽车从电动化转向智能化，高阶辅助驾驶和智能座舱在各大 OEM 和 Tier1 快速落地，越来越多的摄像头和屏幕出现在车上，FPDLINK 是 TI 的车载高速 SERDES 器件，广泛应用在摄像头和 ADAS 域控制器，屏幕和座舱域控制器之间的互联场景，并支持包括 DSI 接口在内的各种接口协议。

DSI 是移动行业处理器接口联盟 (MIPI) 开发的一种显示侧串行通信协议，全称为 **Display Serial Interface**。传统的显示接口(如 RGB 和并行接口)需要较多的引脚数以支持高分辨率和刷新率。MIPI 串行接口只需要较少的引脚连接，同时保持相同的性能水平。但是作为一个较为复杂的协议，在应用过程中会遇到各种问题，本文 FPDLINK 的 DSI 协议进行介绍，并梳理如何更好的使用示波器和协议分析仪实测数据加速问题的定位。

## 目录

|       |               |    |

|-------|---------------|----|

| 1     | 引言            | 3  |

| 2     | MIPI DSI 接口简述 | 3  |

| 2.1   | D-PHY 协议简述    | 3  |

| 2.1.1 | D-PHY 收发器     | 4  |

| 2.1.2 | D-PHY 数据格式    | 5  |

| 2.1.3 | D-PHY 关键参数设置  | 7  |

| 2.2   | DSI 协议简述      | 7  |

| 2.2.1 | DSI 数据包       | 8  |

| 2.2.2 | DSI 数据格式      | 11 |

| 2.3   | DSI 告警        | 15 |

| 3     | DSI 波形示例简析    | 16 |

| 3.1   | 实测波形分析示例      | 16 |

| 3.1.1 | 示波器波形分析       | 16 |

| 3.1.2 | 协议分析仪数据分析     | 19 |

| 4     | 参考文献          | 22 |

## 图

|           |                 |   |

|-----------|-----------------|---|

| Figure 1. | D-PHY 收发器模型     | 4 |

| Figure 2. | D-PHY 电平        | 5 |

| Figure 3. | D-PHY 各逻辑状态含义汇总 | 5 |

|                   |                                                    |    |

|-------------------|----------------------------------------------------|----|

| <b>Figure 4.</b>  | <b>HS Burst 传输波形示意图</b>                            | 6  |

| <b>Figure 5.</b>  | <b>时钟高速模式和 LP 模式切换波形示意图</b>                        | 6  |

| <b>Figure 6.</b>  | <b>D-PHY 关键参数汇总</b>                                | 7  |

| <b>Figure 7.</b>  | <b>DSI 协议分层</b>                                    | 8  |

| <b>Figure 8.</b>  | <b>DSI 数据分发与合并示意图</b>                              | 8  |

| <b>Figure 9.</b>  | <b>DSI 短包示意图</b>                                   | 9  |

| <b>Figure 10.</b> | <b>DSI 长包示意图</b>                                   | 9  |

| <b>Figure 11.</b> | <b>DSI 数据包传输示意图</b>                                | 10 |

| <b>Figure 12.</b> | <b>DSI 长数据包小端传输示意图 (LSB first-MSB last)</b>        | 10 |

| <b>Figure 13.</b> | <b>DSI 数据类型</b>                                    | 11 |

| <b>Figure 14.</b> | <b>Non-Burst Mode with Sync Pulses 视频格式</b>        | 12 |

| <b>Figure 15.</b> | <b>Non-Burst Mode with Sync Events 视频格式</b>        | 13 |

| <b>Figure 16.</b> | <b>Burst Mode 视频格式</b>                             | 13 |

| <b>Figure 17.</b> | <b>另一个角度看 Non-Burst Mode with Sync Pulses 视频格式</b> | 14 |

| <b>Figure 18.</b> | <b>另一个角度看 Non-Burst Mode with Sync Events 视频格式</b> | 15 |

| <b>Figure 19.</b> | <b>另一个角度看 Burst Mode 视频格式</b>                      | 15 |

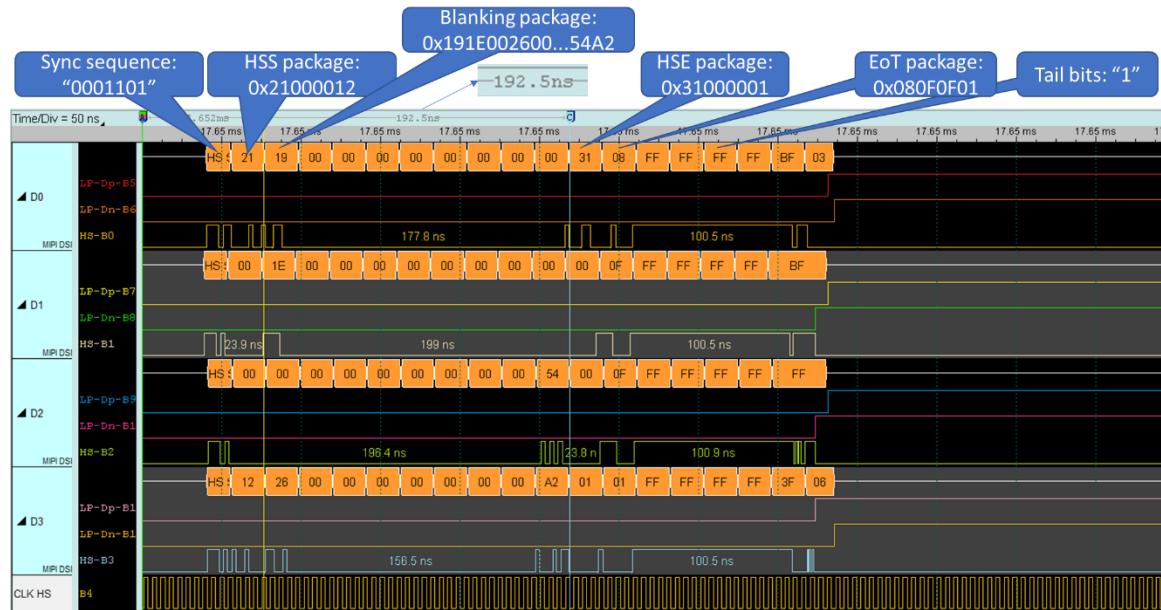

| <b>Figure 20.</b> | <b>差分探头下的 D-PHY 波形 1</b>                           | 17 |

| <b>Figure 21.</b> | <b>差分探头下的 D-PHY 波形 2</b>                           | 18 |

| <b>Figure 22.</b> | <b>差分探头下的 D-PHY 波形 3</b>                           | 18 |

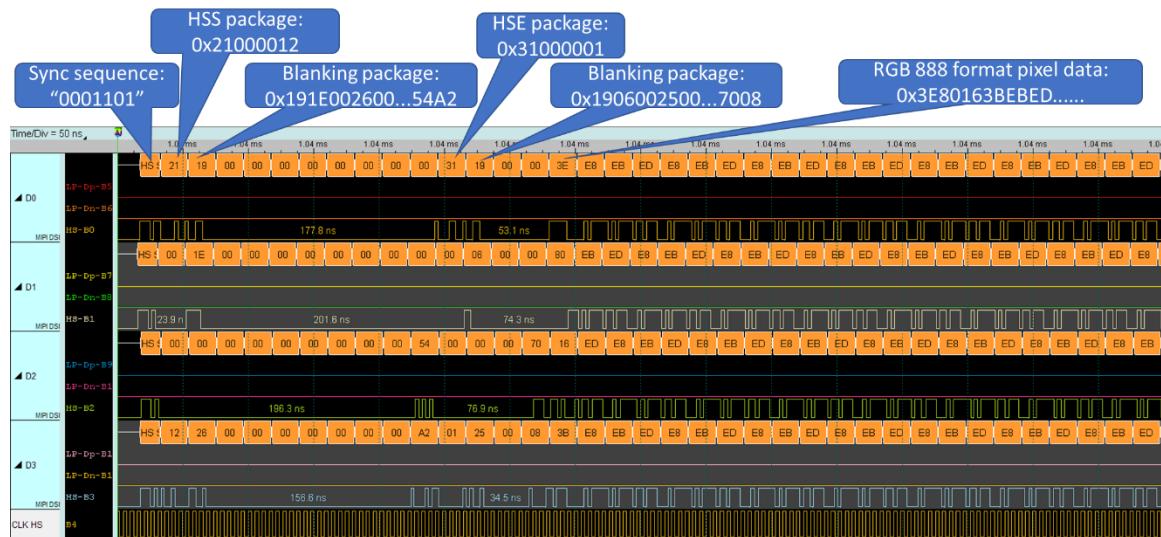

| <b>Figure 23.</b> | <b>协分下的 DSI 波形 1</b>                               | 20 |

| <b>Figure 24.</b> | <b>协分下的 DSI 波形 2</b>                               | 21 |

| <b>Figure 25.</b> | <b>协分下的 DSI 波形 3</b>                               | 21 |

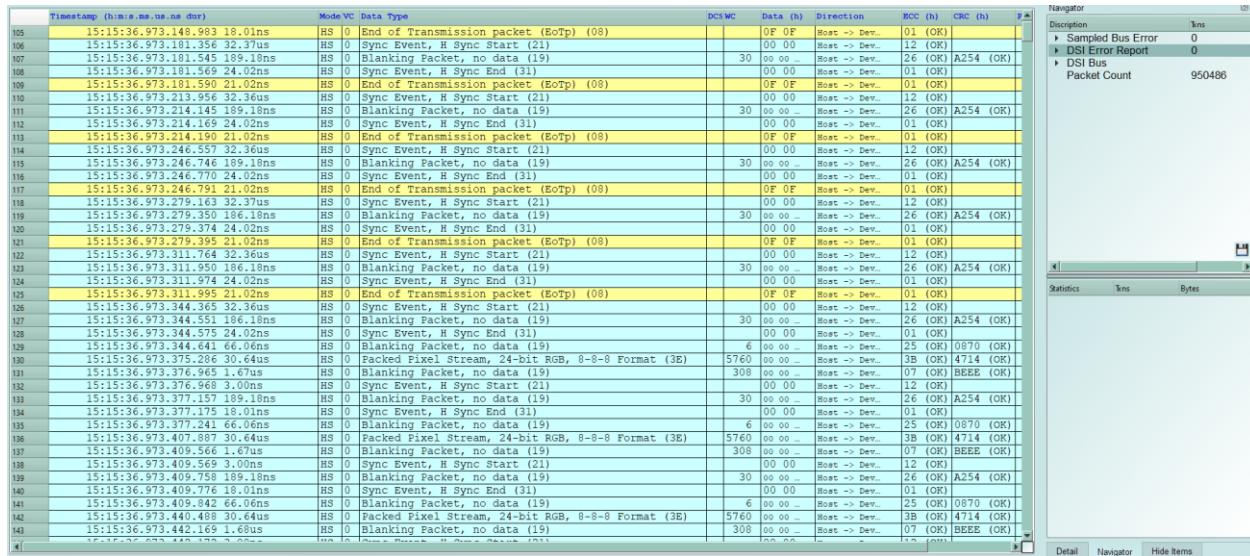

| <b>Figure 26.</b> | <b>协分解析后的 DSI 数据</b>                               | 22 |

## 1 引言

DS90Ux941/DS90Ux981 是 MIPI DSI 至 FPD-Link III/IV 的加串器，支持串行化 MIPI DSI 输入的视频信号到 SERDES 上，支持双路 DSI 接口输入，每路接口包括四对差分数据线和一对差分时钟线，支持以下功能：

1. 兼容 MIPI D-PHY v1.2 / DSI v1.3.1。

2. DSI data lane 线序交叉。

3. DSI lane 极性翻转。

4. 支持 burst 和 non-burst 模式。

5. 两路 DSI 独立使用传输两个视频流或拼合使用共同传输一路视频。

6. 支持多种输入格式，包括 Packed Pixel Stream 和 Loosely Packed Pixel Stream，具体支持的格式类型参考对应数据手册的对应内容。

DSI 接口作为一种 SERDES，解决了并行接口速率较低，PCB 面积大，占芯片 pin 数量多的问题，但是其应用上会相对复杂。本文会结合实测波形对 DSI 协议进行简析，并梳理如何更好的利用这些波形和数据加速 DSI 相关问题的定位。

## 2 MIPI DSI 接口简述

MIPI DSI 协议可以粗略的分为两各层次，底层是物理接口层，它规定了通信的线序、速率、电平、时序等要求，有 A-PHY，C-PHY，D-PHY 等多种 PHY，941/981 使用 D-PHY，本文仅讨论 D-PHY。高层是数据层，规定了数据的分发、打包、传输、校验等功能的实现，可以进一步细分为三层，后续章节会展开介绍。

### 2.1 D-PHY 协议简述

D-PHY 在主设备和从设备之间提供同步通信，PHY 由一个时钟信号和一个或多个数据信号组成。时钟信号是单向的，生成于自主设备，发送到从设备。数据信号可以是单向或双向的。

D-PHY 链路包括用于快速数据流量的高速信号模式和用于控制目的的低功耗信号模式。在高速模式下，每条通道的两侧均端接，并由低摆幅差分信号驱动。高速模式下实际可实现的最大比特率取决于收发器件和互连的性能。在不进行去偏斜校准的情况下每通道支持 80 至 1500 Mbps/lane 通信比特率，在进行去偏斜校准的情况下最高可达 2500 Mbps/lane。对于固定时钟频率，可以使用更多数据通道来增通信速率。此外，固定时钟速率的情况下，可以采用突发模式（burst）通信来降低实际有效数据吞吐量，同时可以降低整体的功耗。在低功耗模式下，所有线均以单端和无端接的方式工作，最大数据速率为 10 Mbps。

实际器件会在上述协议规范的基础上进行裁剪，比如 941/981 仅支持数据从主设备到从设备的单向通信，941 支持最高 1500Mbps 的比特率等等，各器件的实际能力请参考对应数据手册的内容。

### 2.1.1 D-PHY 收发器

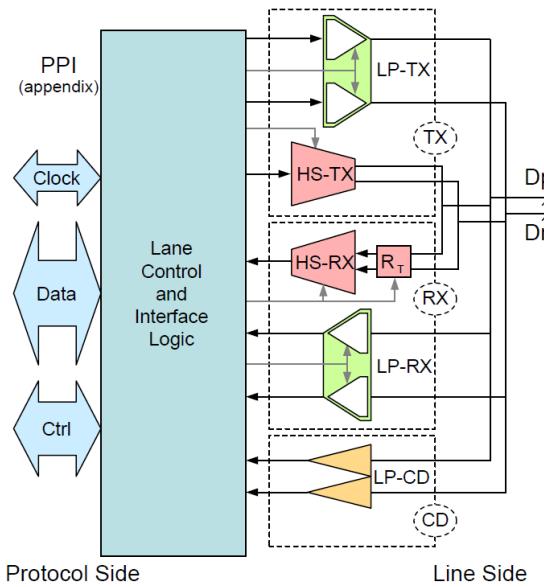

D-PHY 收发器的模型如图 1 所示，图中所示是一个功能模块全集，实际器件可以在此基础上进行模块的删减。按功能来分，这些模块可以分为发送器（TX）和接收器（RX）；按速率来分，可以分为高速（HS）模块低功耗（LP）模块。

HS-TX 和 HS-RX 是负责高速数据收发的模块，HS 即 High Speed 的意思。一个芯片内部至少包含 TX 或 RX 模块中的一个（单向通信器件），或者两者都存在（支持双向通信的器件）。HS-TX 和 HS-RX 模块工作在差分模式，两端必须都确保差分  $100\text{ohm}$  的端接，在非 HS 模式下，收发模块处于高阻状态。941/981 仅支持数据的单向传输，因此仅包含 HS-RX 模块。

LP-TX，LP-RX 和 LP-CD 是负责控制信号传递的模块，LP 即 Low Power 的意思。LP-TX 和 LP-RX 共同组成 LP 模式下的收发链路，和 HS 模块类似，一个芯片内部可以是包含 TX 或 RX 模块中的一个，或者两者都存在，同时，LP 的 TX/RX 需要和 HS 的 TX/RX 配对存在，即当芯片内集成了 HS-TX，则 LP-TX 也需要存在，反之亦然。LP-CD 模块是双向通信场景下所需的模块，在 LP-TX 驱动低功耗状态时启用 LP-CD 功能以检测争用情况，CD 即 Contention Detector 的意思。941/981 仅支持数据的单向传输，因此仅包含 LP-RX 模块。

**Figure 1. D-PHY 收发器模型**

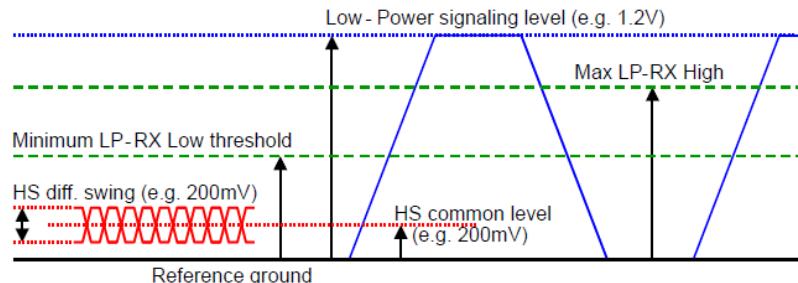

D-PHY 发送器（TX）通过驱动数据链路到特定电平来传输特定数据或指令。在正常情况下，HS-TX 或 LP-TX 两者中仅有一个模块驱动外部链路，不存在同时驱动的情况。HS-TX 使用低压差分信号传输高速数据流；一个 HS-TX 驱动一对差分链路。LP-TX 使用单端信号传输低速控制流，两个 LP-TX 分别驱动两条单端链路。因此总共有两种 HS 逻辑状态和四种 LP 逻辑状态，这六种逻辑状态对应的逻辑电平范围如图 2 所示。HS 的两种逻辑状态为差分 0 和差分 1（或高速 0 和高速 1），每一根差分线上是  $200\text{mV}$  直流偏置， $200\text{mV}$  摆幅的电压信号。LP 的四种状态分别为 LP00，LP01，LP10 和 LP11，分别由两根数据线上的电平组合得到，其中低电平为  $0\text{V}$ ，高电平为  $1.2\text{V}$ 。可以看到，LP 接收器始终将差分 0 和差分 1 解释为 LP-00。

**Figure 2. D-PHY 电平**

### 2.1.2 D-PHY 数据格式

在正常工作场景下，数据链路可以处于低速模式或高速模式中任意一种状态。高速数据传输发生在一个burst中，差分0和差分1代表高速传输模式下的数据0和数据1。而LP00, LP01, LP10, LP11在不同的模式下表示不同的含义，各逻辑状态的含义汇总如图3所示。

| State Code | Line Voltage Levels |         | High-Speed     | Low-Power    |             |

|------------|---------------------|---------|----------------|--------------|-------------|

|            | Dp-Line             | Dn-Line |                | Control Mode | Escape Mode |

| HS-0       | HS Low              | HS High | Differential-0 | N/A, Note 1  | N/A, Note 1 |

| HS-1       | HS High             | HS Low  | Differential-1 | N/A, Note 1  | N/A, Note 1 |

| LP-00      | LP Low              | LP Low  | N/A            | Bridge       | Space       |

| LP-01      | LP Low              | LP High | N/A            | HS-Rqst      | Mark-0      |

| LP-10      | LP High             | LP Low  | N/A            | LP-Rqst      | Mark-1      |

| LP-11      | LP High             | LP High | N/A            | Stop         | N/A, Note 2 |

**Figure 3. D-PHY 各逻辑状态含义汇总**

一个burst从停止状态(LP-11)开始，结束后链路回到LP11状态，进入高速模式的需要LP收发器传递特定的控制序列。Escape模式只能通过控制模式中的请求进入，检测到停止状态后，数据通道应退出Escape模式并返回控制模式。941/981不支持Escape模式。如果未处于高速或Escape模式，则数据链路应保持在控制模式。对于数据线和时钟线，LP11用作一般待机状态，并且可以持续任何时间段（需要大于协议规定的最小值 $T_{LPX}$ ）。

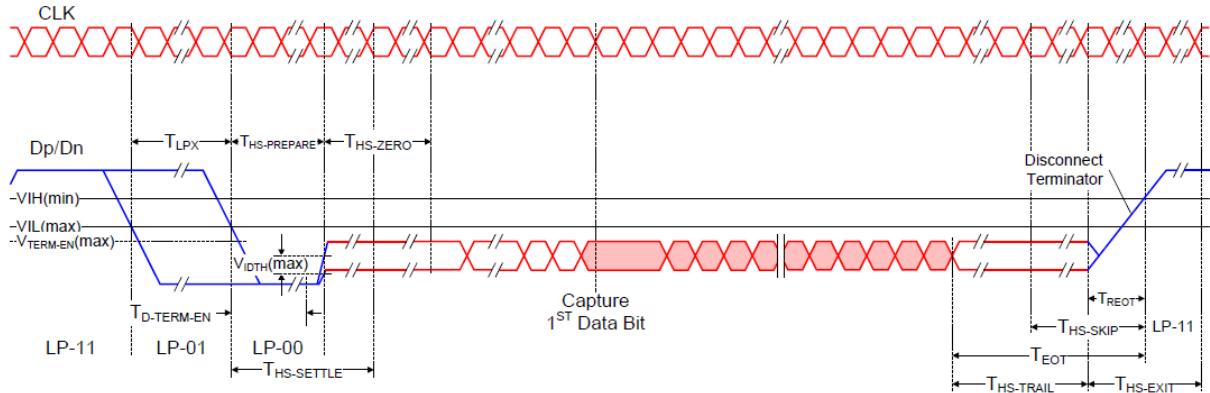

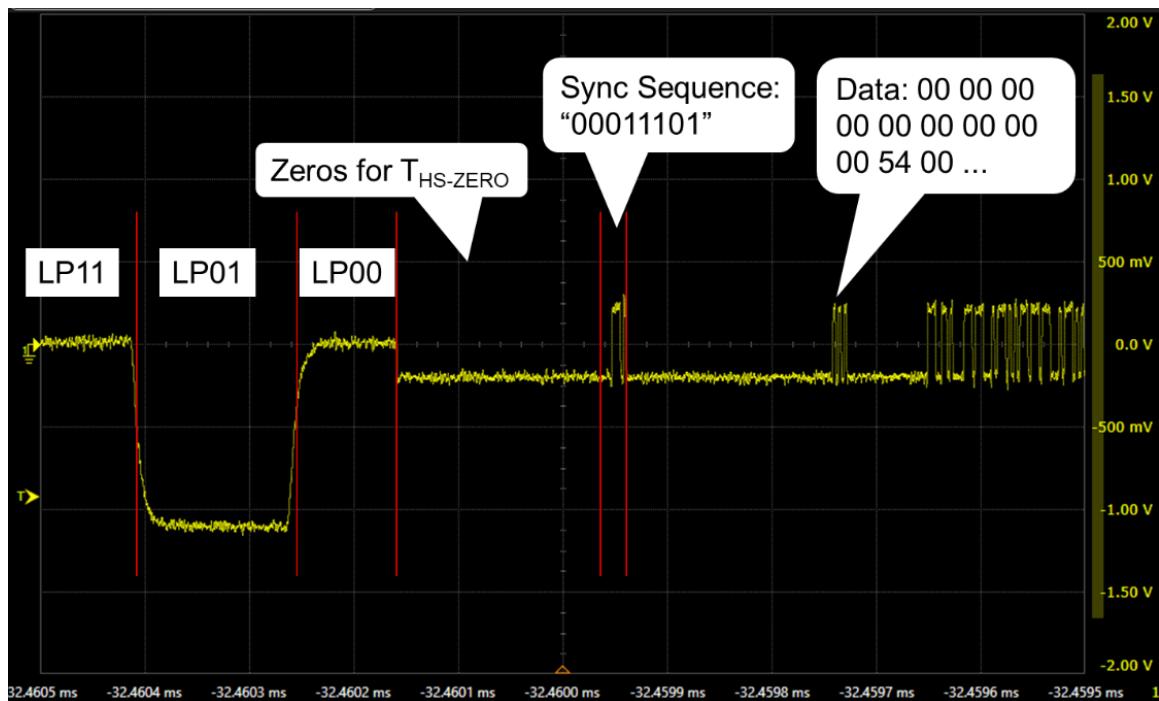

图4所示为一个HS Burst传输的波形，完成一个Burst需要满足一定的时序要求，按先后顺序依次为：LP-11（停止状态，进入HS模式前默认的链路状态）->LP-01（HS request，高速模式的请求状态）->LP-00（Bridge状态），此后数据链路将保持在高速模式，直至HS发送停止并传递LP-11。其中从待机状态进入burst在状态需要经过的特定序列称为SoT（Start-of-Transmission Sequence）。LP11是默认的待机状态，TX发送LP01请求进入HS模式，持续 $T_{LPX}$ 时长后，TX发送LP00。TX在发送LP00后，在 $T_{HS-PREPARE}$ 时长内应关闭LP-TX并开启HS-TX，在接收端检测到从LP01到LP00的切换边沿后经过 $T_{D-TERM-EN}$ 时延，RX使能内部端接电阻。在LP发送器和HS发送器切换的过程中的瞬态电平被RX误解码，RX应忽略 $T_{HS-SETTLE}$ 时长内的所有TX数据，同时，伴随此过程的是TX发送的 $T_{HS-ZERO}$ 时长的差分0。为帮助RX同步，差分0序列后需要发送同步头00011101，之后才是正常的HS数据bit流。HS数据可以是任意长度，没有最大长度上限，唯一的要求是长度需为整字节。

Figure 4. HS Burst 传输波形示意图

结束 HS 数据传输后，需要特定的 EoT (End-of-Transmission Sequence) 退回待机状态。需要注意，EoT 可能由上层协议（比如 DSI 协议规定在 Burst 的最后可以发送可选的 EoT package）规定或使用 D-PHY 协议的默认规定。D-PHY 协议规定的 EoT 如下，在发送完最后 1bit HS 数据后，TX 立即翻转 HS 发送器的状态，即最后一个 HS 数据 bit 是差分 1 则输出翻转为差分 0，反之亦然，并持续  $T_{HS-TRAIL}$  时长，之后禁用 HS-TX，开启 LP-TX，驱动数据链路从 LP00 到 LP11 状态，与 LP-TX 和 HS-TX 不会同时使能不同，LP-RX 和 HS-RX 同时使能，因此 LP-RX 会检测到 LP00 到 LP11 的切换边沿。为了避免切换造成的瞬态被 RX 误解码，RX 应忽略 LP00 到 LP11 切换动作前  $T_{HS-SKIP}$  时间内的所有数据。

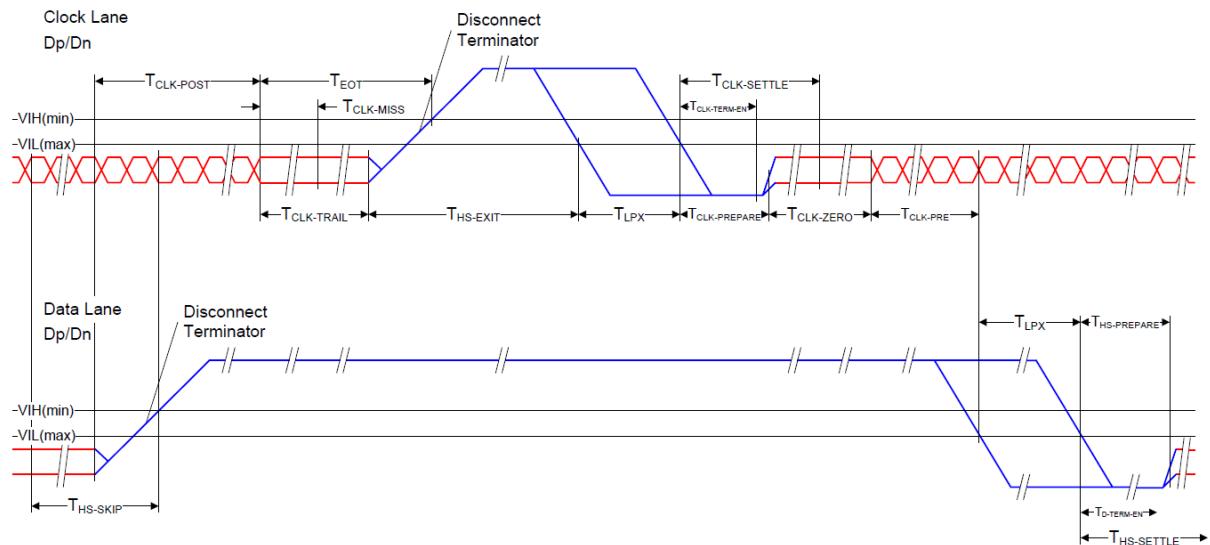

和数据线不一样的是，时钟线可以始终保持在 HS 模式连续发送，如图 4 所示的始终那样，或者伴随数据的 Burst 周期性进入 LP 模式，图 5 所示的是时钟线和数据线进出 LP 模式的时序关系。时钟需要在数据开始进入 HS 状态（LP00 到 LP01 边沿）前  $T_{CLK-PRE}$  时长建立，在数据结束 HS 状态后继续保持  $T_{CLK-POST}$  时长。941/981 对此两种时钟模式都支持。

Figure 5. 时钟高速模式和 LP 模式切换波形示意图

### 2.1.3 D-PHY 关键参数设置

从上述的流程可以看到，为了正常通信，有很多参数需要设置，这些参数的汇总和协议推荐值如图 6 所示，它们既有发送端也有接收端的参数。941/981 手册中对于  $T_{HS-SKIP}$  的设置有详细讨论，建议的设置值为  $TSKIP\_CNT = \text{ROUND}((130*fdsi)/4000-3)$ ，取最接近的偶数值，单位为时钟周期。其余的 RX 参数一般使用默认值，但是在实际应用过程中，需要注意和 TX 端参数的匹配，同时 TX 端的参数也需要合理配置。

| Parameter                        | Description                                                                                                                                                                                                                                                                                                         | Min                                | Typ | Max              | Unit | Notes                         |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|------------------|------|-------------------------------|

| $T_{CLK-MISS}$                   | Timeout for receiver to detect absence of Clock transitions and disable the Clock Lane HS-RX.                                                                                                                                                                                                                       |                                    |     | 60               | ns   | 941/981 support, fixed        |

| $T_{CLK-POST}$                   | Time that the transmitter continues to send HS clock after the last associated Data Lane has transitioned to LP Mode. Interval is defined as the period from the end of $T_{HS-TRAIL}$ to the beginning of $T_{CLK-TRAIL}$ .                                                                                        | 60 ns + 52*UI                      |     |                  | ns   | Transmitter parameter         |

| $T_{CLK-PRE}$                    | Time that the HS clock shall be driven by the transmitter prior to any associated Data Lane beginning the transition from LP to HS mode.                                                                                                                                                                            | 8                                  |     |                  | UI   | Transmitter parameter         |

| $T_{CLK-PREPARE}$                | Time that the transmitter drives the Clock Lane LP-00 Line state immediately before the HS-0 Line state starting the HS transmission.                                                                                                                                                                               | 38                                 |     | 95               | ns   | Transmitter parameter         |

| $T_{CLK-SETTLE}$                 | Time interval during which the HS receiver should ignore any Clock Lane HS transitions, starting from the beginning of $T_{CLK-PREPARE}$ .                                                                                                                                                                          | 95                                 |     | 300              | ns   | 941/981 support, programmable |

| $T_{CLK-TERM-EN}$                | Time for the Clock Lane receiver to enable the HS line termination, starting from the time point when Dn crosses $V_{IL,MAX}$ .                                                                                                                                                                                     | Time for Dn to reach $V_{TERM-EN}$ |     | 38               | ns   | 941/981 support, programmable |

| $T_{CLK-TRAIL}$                  | Time that the transmitter drives the HS-0 state after the last payload clock bit of a HS transmission burst.                                                                                                                                                                                                        | 60                                 |     |                  | ns   | Transmitter parameter         |

| $T_{CLK-PREPARE} + T_{CLK-ZERO}$ | $T_{CLK-PREPARE} +$ time that the transmitter drives the HS-0 state prior to starting the Clock.                                                                                                                                                                                                                    | 300                                |     |                  | ns   | Transmitter parameter         |

| $T_{D-TERM-EN}$                  | Time for the Data Lane receiver to enable the HS line termination, starting from the time point when Dn crosses $V_{IL,MAX}$ .                                                                                                                                                                                      | Time for Dn to reach $V_{TERM-EN}$ |     | 35 ns + 4*UI     |      | 941/981 support, programmable |

| $T_{EOT}$                        | Transmitted time interval from the start of $T_{HS-TRAIL}$ or $T_{CLK-TRAIL}$ , to the start of the LP-11 state following a HS burst.                                                                                                                                                                               |                                    |     | 105 ns + n*12*UI |      | Transmitter parameter         |

| $T_{HS-EXIT}$                    | Time that the transmitter drives LP-11 following a HS burst.                                                                                                                                                                                                                                                        | 100                                |     |                  | ns   | Transmitter parameter         |

| $T_{HS-PREPARE}$                 | Time that the transmitter drives the Data Lane LP-00 Line state immediately before the HS-0 Line state starting the HS transmission                                                                                                                                                                                 | 40 ns + 4*UI                       |     | 85 ns + 6*UI     | ns   | Transmitter parameter         |

| $T_{HS-PREPARE} + T_{HS-ZERO}$   | $T_{HS-PREPARE} +$ time that the transmitter drives the HS-0 state prior to transmitting the Sync sequence.                                                                                                                                                                                                         | 145 ns + 10*UI                     |     |                  | ns   | Transmitter parameter         |

| $T_{HS-SETTLE}$                  | Time interval during which the HS receiver shall ignore any Data Lane HS transitions, starting from the beginning of $T_{HS-PREPARE}$ .<br>The HS receiver shall ignore any Data Lane transitions before the minimum value, and the HS receiver shall respond to any Data Lane transitions after the maximum value. | 85 ns + 6*UI                       |     | 145 ns + 10*UI   | ns   | 941/981 support, programmable |

| $T_{HS-SKIP}$                    | Time interval during which the HS-RX should ignore any transitions on the Data Lane, following a HS burst. The end point of the interval is defined as the beginning of the LP-11 state following the HS burst.                                                                                                     | 40                                 |     | 55 ns + 4*UI     | ns   | 941/981 support, programmable |

| $T_{HS-TRAIL}$                   | Time that the transmitter drives the flipped differential state after last payload data bit of a HS transmission burst                                                                                                                                                                                              | max( n*8*UI, 60 ns + n*4*UI )      |     |                  | ns   | Transmitter parameter         |

| $T_{LPX}$                        | Transmitted length of any Low-Power state period                                                                                                                                                                                                                                                                    | 50                                 |     |                  | ns   | Transmitter parameter         |

**Figure 6. D-PHY 关键参数汇总**

## 2.2 DSI 协议简述

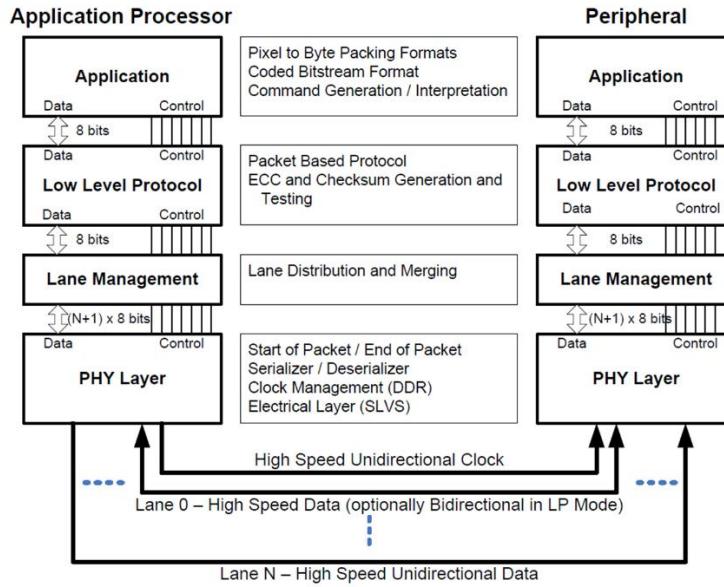

如图 7 所示是 DSI 协议的分层。第一层是物理层，前文已讨论。第二层是链路管理层，DSI 可以使用 1-4 根任意数量的数据线进行通信，这一层控制数据的如何在数量可变的数据线上进行分发（Distributor）和合并（Merger）。第三层是低级协议层，既规定了 bit 位和字节的顺序，也规定了如何将数据字节组织成数据包和错误校验。第四层是应用层，它规定了高层的编码规则，包括视频像素和控制信号的编码规则等。

Figure 2 DSI Layers

Figure 7. DSI 协议分层

### 2.2.1 DSI 数据包

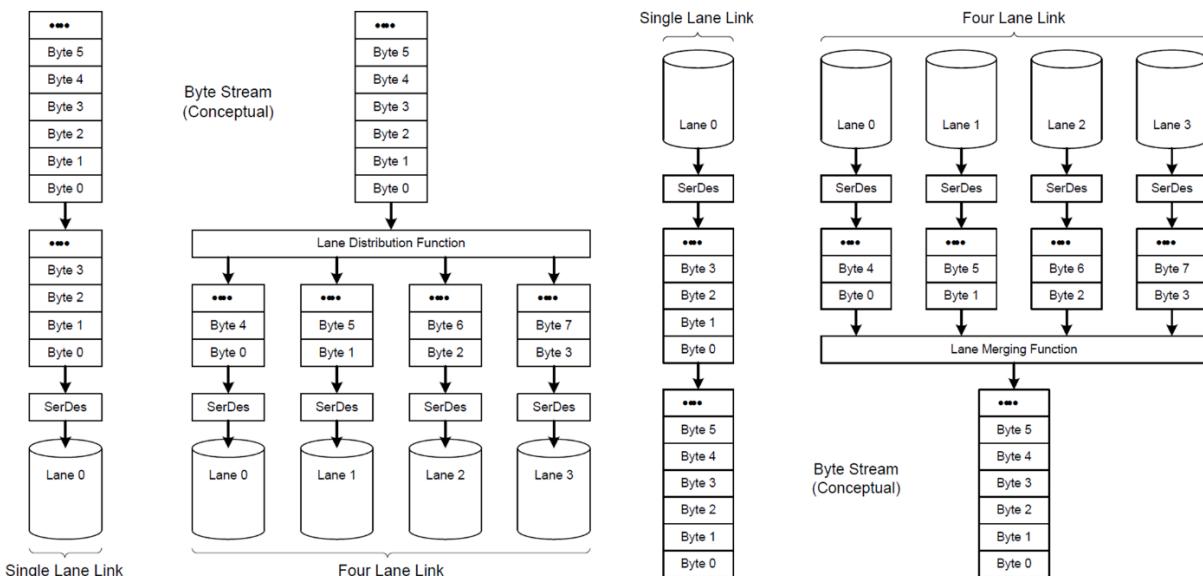

链路管理层具有基于字节的分发和合并功能，如图 8 所示。当仅有 1 根数据线被使用时，从高层来的打包好的数据字节按先后顺序逐次发送到数据线上，接收端按同样的顺序接收后给到高层进行解码；当多于 1 根数据线被使用时，链路管理层会平均的按照轮询的顺序将数据字节分发到各个数据线上，接收端按照相反的顺序对数据进行合并。

Figure 8. DSI 数据分发与合并示意图

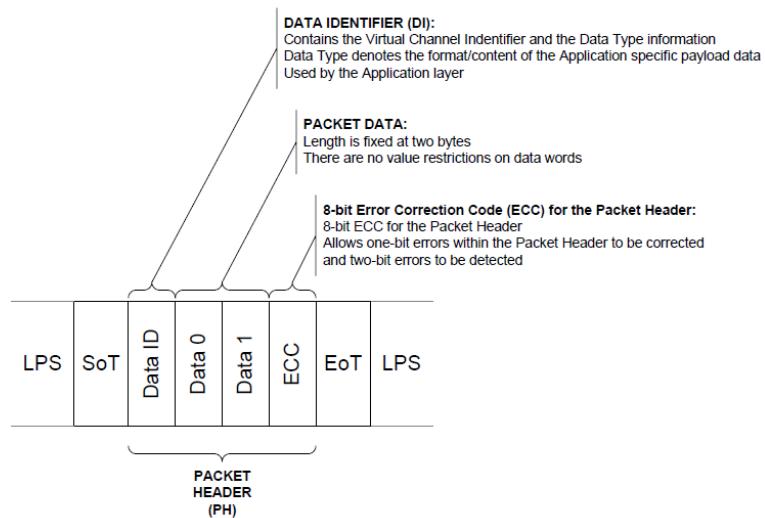

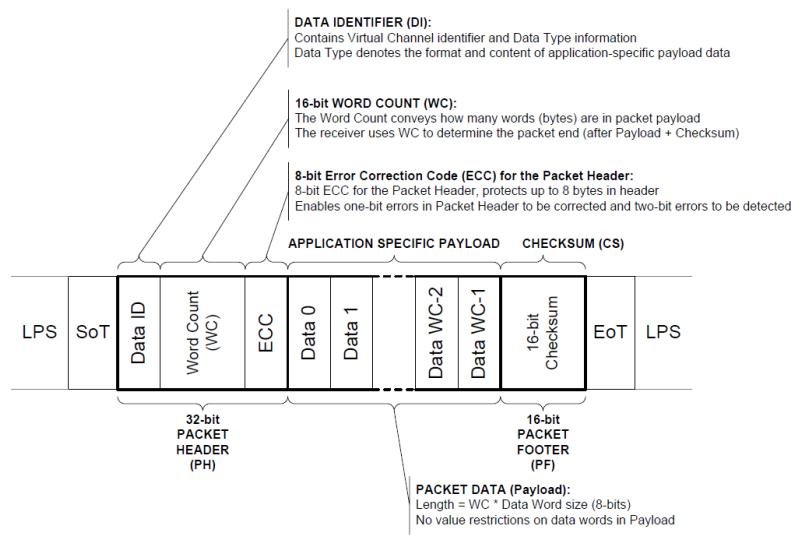

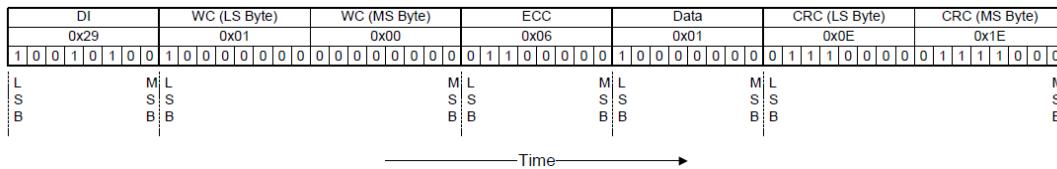

DSI 有两种数据包，短包和长包，他们由低级协议层的电路生成和解析。一个短包的组成如图 9 所示，它由四个字节组成，Data ID 是表示此数据包功能的字节，Data0 和 Data1 的数据可以是任意的没有实际意义，最后一个字节是 ECC 校验字节，短包一般用来传输控制命令。一个长包的组成如图 10 所示，它由五部分组成，Data ID 表示此数据包的功能或后续数据的格式，WC 字段表示此数据包的长度，ECC 是包括 Data ID 和 WC 在内的校验字节，Payload 是实际要传输的数据，它的长度可以从 0 到  $2^{16}-1$ ，最后两个字节是对于整个包的数据校验字节，长包用来传输视频的像素数据，一般一个长包传输一整行或一整帧（非消隐区）的数据。

**Figure 9. DSI 短包示意图**

**Figure 10. DSI 长包示意图**

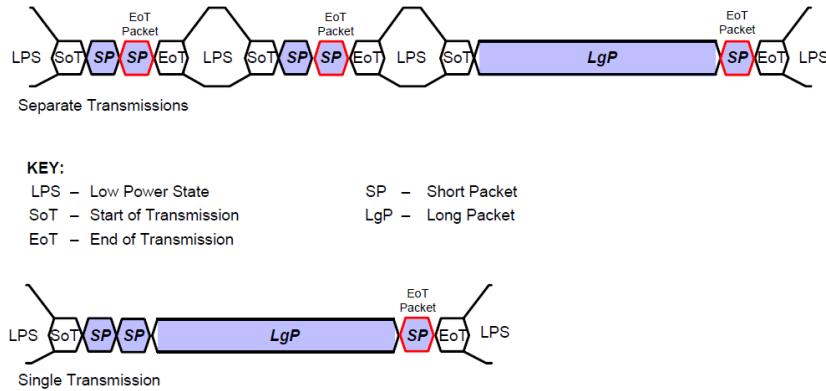

传输多个数据包时，他们之间可以相互串联或被 LPS（即 D-PHY 的 LP 模式）隔开，如图 11 所示的分别是这两种情况。图中红色高亮所示的短包是 EoT package，它是一种特殊的短包（Data ID 是 0x08），它是 DSI 协议为了提供传输稳定性设计的表示 HS 数据传输结束的数据包，它需要跟随在各个其他数据包之后发送而不能独立存在，系统中发送此数据包与否是可选的，因为部分老器件不支持此功能。941/981 支持接收 EoTp。

DSI 使用小端传输，即每个字节的 LSB 最先传输，WC 和 CRC 校验位等多字节的数据，低字节先传输，如图 12 所示。

**Figure 11. DSI 数据传输示意图**

**Figure 12. DSI 长数据包小端传输示意图 (LSB first-MSB last)**

Data ID 的 bit6 和 7 是虚拟通道 VCID 的指示位。Bit0-bit5 是"数据类型"的指示字段，该字段指定此数据包是长包还是短包以及具体的数据包格式。"数据类型"字段以及长数据包的 WC 字段通知接收方数据包的剩余部分还有多少字节，这允许数据包本体可以传输任意数据，但也要求数据包报头明确指定数据包的大小和数据类型。常用的部分"数据类型"如图 13 所示。

| Data Type, hex | Data Type, binary | Description                                             | Packet Size |

|----------------|-------------------|---------------------------------------------------------|-------------|

| 0x01           | 00 0001           | Sync Event, V Sync Start                                | Short       |

| 0x11           | 01 0001           | Sync Event, V Sync End                                  | Short       |

| 0x21           | 10 0001           | Sync Event, H Sync Start                                | Short       |

| 0x31           | 11 0001           | Sync Event, H Sync End                                  | Short       |

| 0x08           | 00 1000           | End of Transmission packet (EoTp)                       | Short       |

| 0x09           | 00 1001           | Null Packet, no data                                    | Long        |

| 0x19           | 01 1001           | Blanking Packet, no data                                | Long        |

| 0x0C           | 00 1100           | Loosely Packed Pixel Stream, 20-bit YCbCr, 4:2:2 Format | Long        |

| 0x1C           | 01 1100           | Packed Pixel Stream, 24-bit YCbCr, 4:2:2 Format         | Long        |

| 0x2C           | 10 1100           | Packed Pixel Stream, 16-bit YCbCr, 4:2:2 Format         | Long        |

| 0x0D           | 00 1101           | Packed Pixel Stream, 30-bit RGB, 10-10-10 Format        | Long        |

| 0x1D           | 01 1101           | Packed Pixel Stream, 36-bit RGB, 12-12-12 Format        | Long        |

| 0x3D           | 11 1101           | Packed Pixel Stream, 12-bit YCbCr, 4:2:0 Format         | Long        |

| 0x0E           | 00 1110           | Packed Pixel Stream, 16-bit RGB, 5-6-5 Format           | Long        |

| 0x1E           | 01 1110           | Packed Pixel Stream, 18-bit RGB, 6-6-6 Format           | Long        |

| 0x2E           | 10 1110           | Loosely Packed Pixel Stream, 18-bit RGB, 6-6-6 Format   | Long        |

| 0x3E           | 11 1110           | Packed Pixel Stream, 24-bit RGB, 8-8-8 Format           | Long        |

**Figure 13. DSI 数据类型**

## 2.2.2 DSI 数据格式

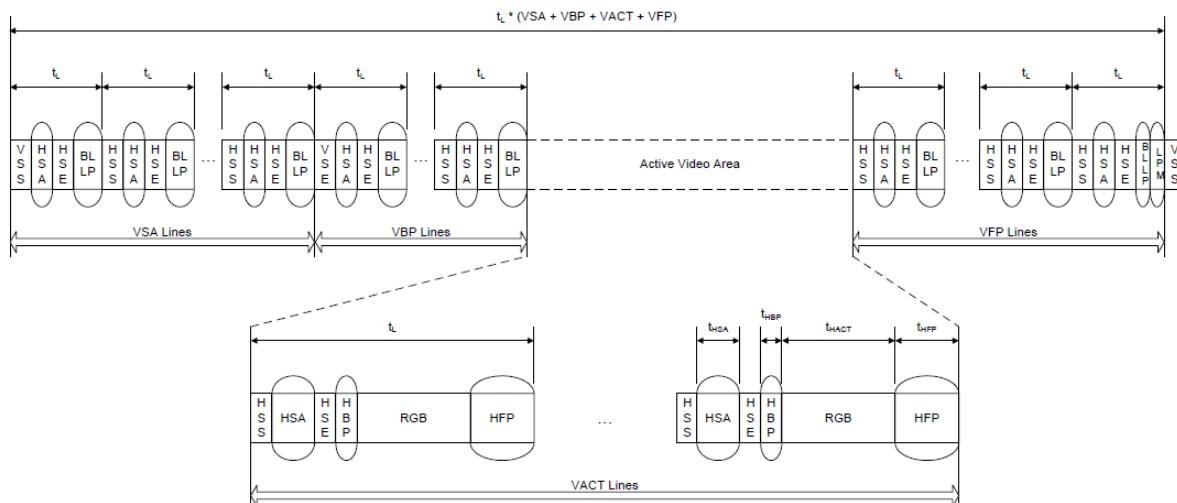

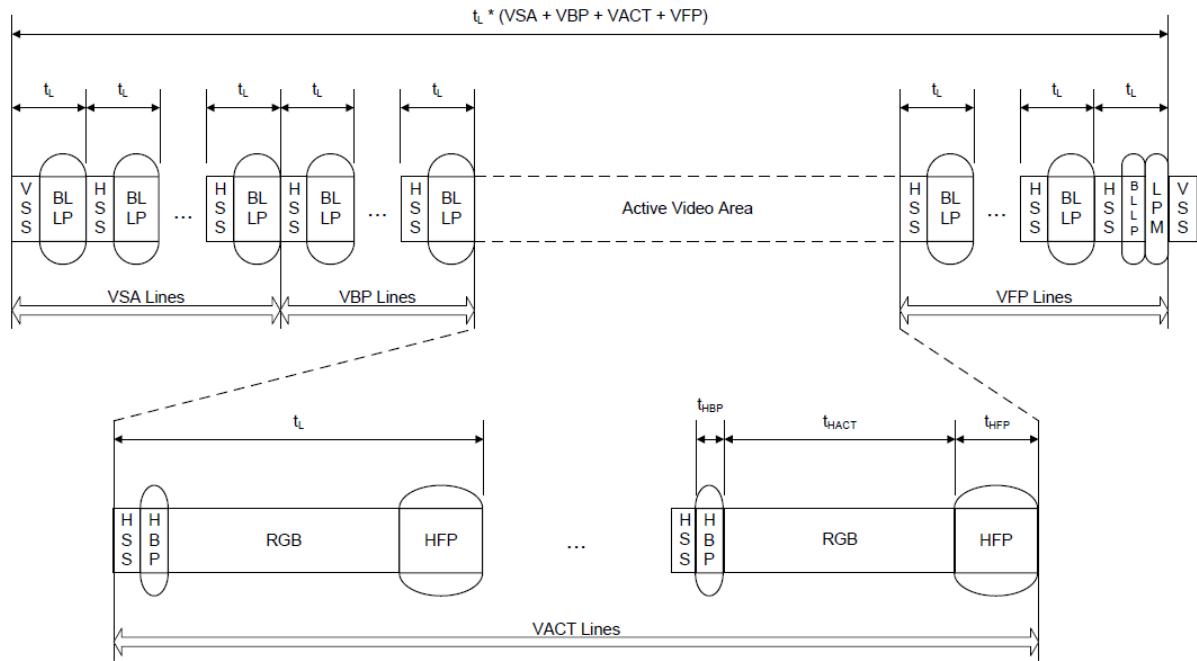

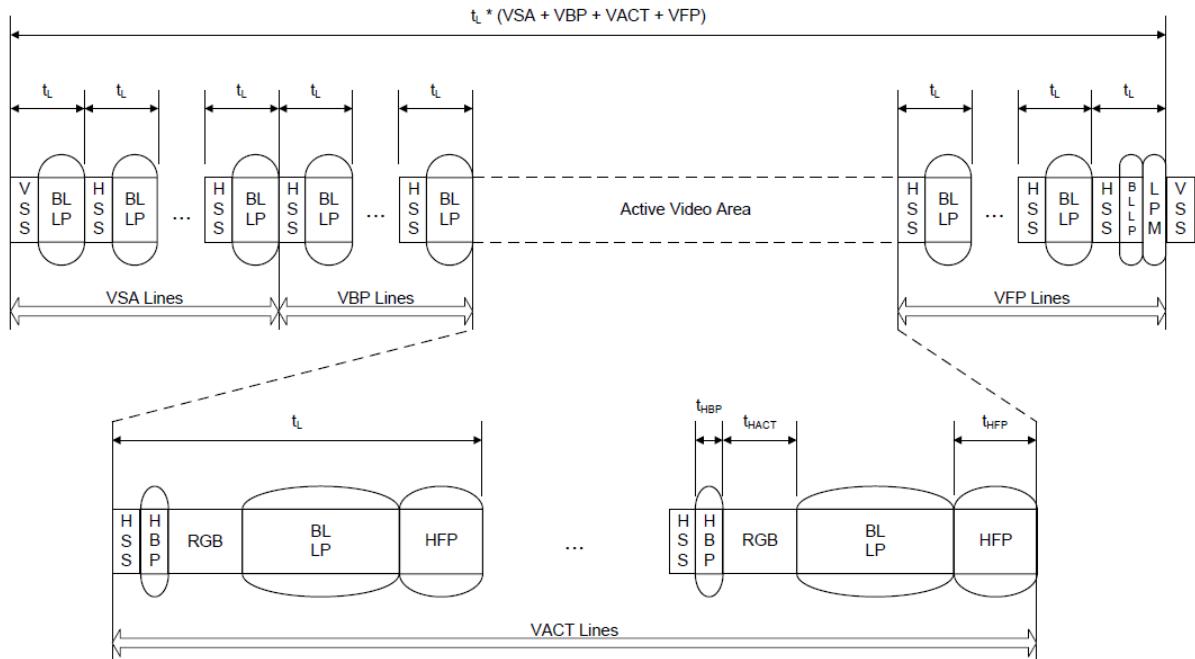

视频通过逐帧刷新的方式显示，每一帧图像又包括有效区和消隐区，有效区时实际视频被显示出来的部分，消隐区是没有被显示出来的部分，它的功能仅仅是时序的控制，关于视频显示格式的相关内容请参考其他资料，本文假设读者对此有比较清除的了解。DSI 传输视频时，长包和短包按固定的格式组合起来可以表征视频的显示时序，长包用来传递有效区的行，短包则被用来传递消隐区的内容。

DSI 协议规定了三种视频传输格式，分别为：

**Non-Burst Mode with Sync Pulses:** 如图 14 所示，时钟连续发送，不进入 LP 模式，数据按需求间歇性以 burst 方式发送，同步脉冲的上升沿和下降沿都通过短包发送出来。

**Non-Burst Mode with Sync Events:** 如图 15 所示，和 Non-Burst Mode with Sync Pulses 的唯一区别是仅有同步脉冲的上升沿通过短包发送出来。

**Burst mode:** 如图 16 所示，时钟和数据都按需求间歇性以 Burst 发送，其他时刻整个 DSI 进入 LP 模式以降低功耗。

941/981 支持以上全部三种模式。图中各个时间块的意义如下：

**VSS:** Vertical Sync Start 时间块，传递一个 0x01 类型的短包。

**VSE:** Vertical Sync End 时间块，传递一个 0x11 类型的短包。

HSS: Horizontal Sync Start 时间块, 传递一个 0x21 类型的短包。

HSE: Horizontal Sync End 时间块, 传递一个 0x31 类型的短包。

HSA: Horizontal Sync Active 时间块, 可以用一个 blanking 长包 (0x19 类型), 或直接进入 LP 模式来填充, 持续时间 (Blanking 包的时长需要包括打包开销在内计算时长, 比如 Data ID 和 ECC) 和 Sync Pulse 的持续时长相等。

HFP: Horizontal Front Porch 时间块, 和 HSA 一样可以用一个 Blanking 包, 或进入 LP 模式填充, 持续时间 (Blanking 包的时长需要包括打包开销在内计算时长) 和 HFP 的持续时长相等。

HBP: Horizontal Back Porch 时间块, 和 HSA 一样可以用一个 Blanking 包, 或进入 LP 模式填充, 持续时间 (Blanking 包的时长需要包括打包开销在内计算时长) 和 HBP 的持续时长相等。

BLLP: 不考虑 escape mode 的情况下, BLLP 时间块包括以下几种可能: 1. 进入 LP 模式; 2. 保持在 HS 模式并传输非视频数据包 (比如 Blanking 包); 3. 保持在 HS 模式, 传输其他 VC 的数据。

RGB: 包括有效像素的显示数据或非像素数据 (比如 Blanking 包), 用一个或多个长包填充时长等于一行的时长。多个长包填充的情况发生在时钟速率较快, 像素数据发送完后仍有多余时长的情况。此时可以使用 blanking 包填充剩余的时长。CSI 对于像素数据包和 blanking 数据包的顺序没有要求, 即使是两者打散了交替发送也是可以的。

LPM: DSI 需要周期性的进入 LP 模式来确保收发的同步, LPM 可以发生在任意一个可以进入 LP 的位置, 比如 BLLP 和 HFP, 图中仅为示意, 位置不固定, 要求每一帧进入一次 LP 模式即可。

Figure 14. Non-Burst Mode with Sync Pulses 视频格式

**Figure 15. Non-Burst Mode with Sync Events** 视频格式

**Figure 16. Burst Mode** 视频格式

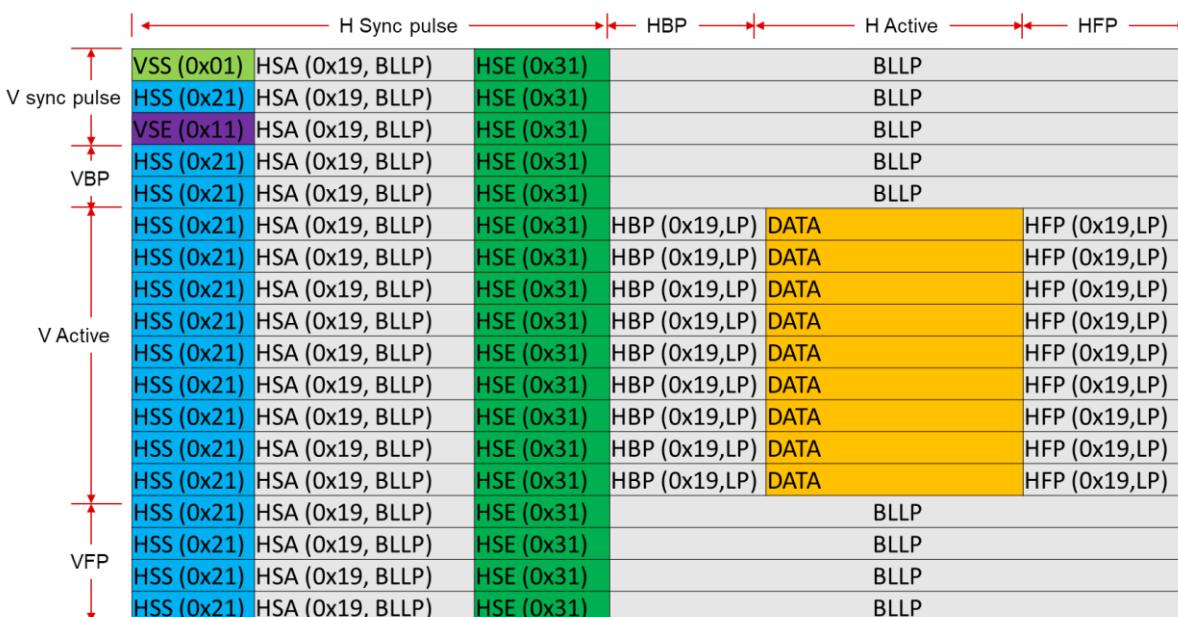

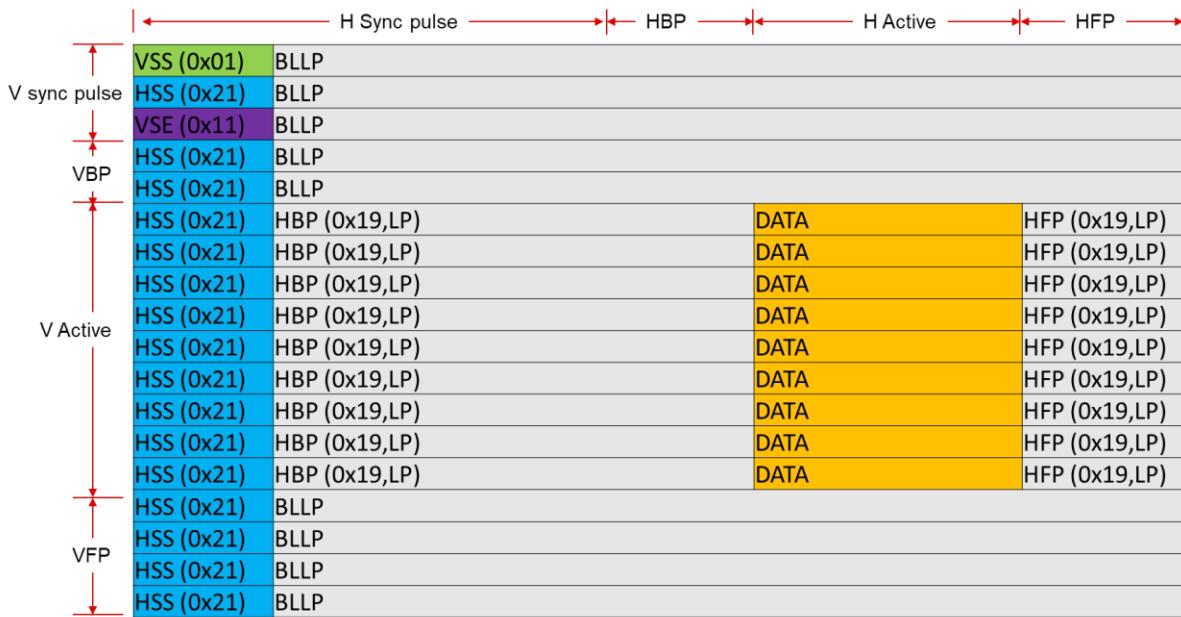

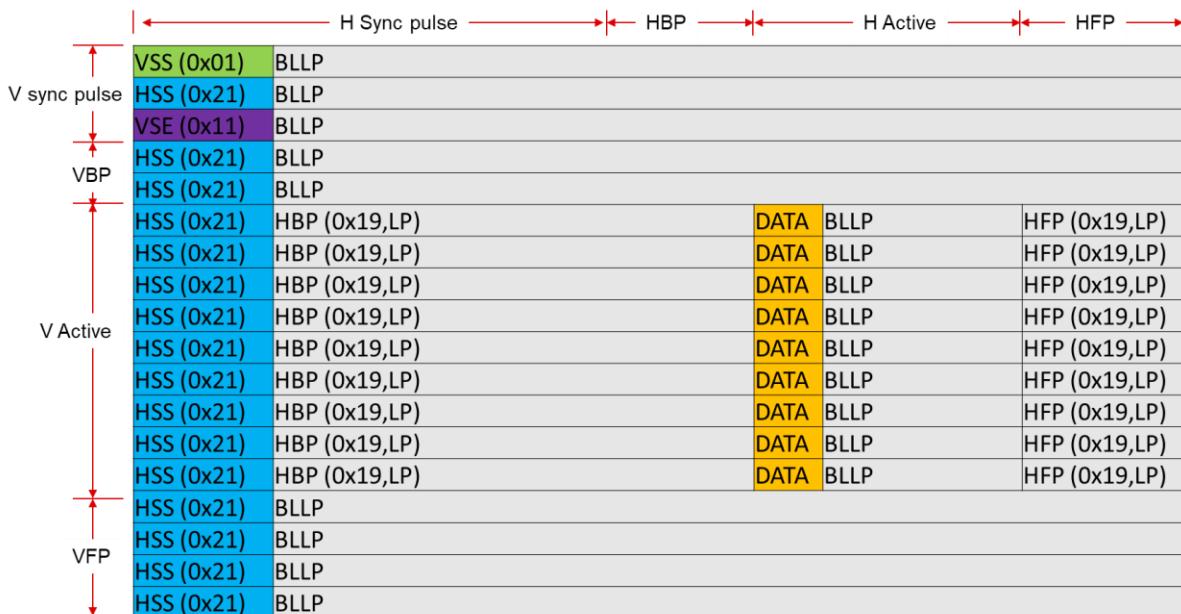

图 14-16 的格式基于 DSI 发送的时间先后顺序进行示意，我们可以从另一个维度来看这些数据包，图 17-19 是将各个时间块重新组合成了视频的一帧示意图，以我们方便理解。Non-Burst Mode with Sync Pulses 模式传递完整的显示时序，HSS 和 HSE 之间的时长就是 H sync pulse 的时长，VSS 到 VSE 之间的时长就是 V sync pulse 的时长。HSA/HBP/HFP 这几个时间块如果足够长，可以选择进入 LP 模式以降低功耗。

对于 Non-Burst Mode with Sync Events 来说，它仅传递每次同步脉冲的起始边沿，接收器需要后续自己生成完整的显示时序，对于 941/981 来说，需要设置对应的寄存器使能此功能（D-PHY 页的 0x20 寄存器）。

Burst Mode 和 Non-Burst Mode with Sync Events 很相似，不看时钟是否进入 LP 模式的话单从数据波形上无法区分（两者的 HPB, HFP 和 BLLP 都可以选择进入 LP 模式，此时除了 DATA 长短有区别外从数据线上看不出任何区别），对于接收端来说，两者区别不大，941/981 同样设置 D-PHY 页的 0x20 寄存器即可，额外需要注意的是，941 使用 DSI 时钟作为芯片参考时钟时，不能使用 Burst Mode。

**Figure 17. 另一个角度看 Non-Burst Mode with Sync Pulses 视频格式**

| H Sync pulse |            |               |      | HBP           | H Active | HFP |

|--------------|------------|---------------|------|---------------|----------|-----|

| V sync pulse | VSS (0x01) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

| VBP          | VSE (0x11) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

| V Active     | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | HFP (0x19,LP) |          |     |

| VFP          | HSS (0x21) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

|              | HSS (0x21) | BLLP          |      |               |          |     |

**Figure 18. 另一个角度看 Non-Burst Mode with Sync Events 视频格式**

| H Sync pulse |            |               |      | HBP  | H Active      | HFP |

|--------------|------------|---------------|------|------|---------------|-----|

| V sync pulse | VSS (0x01) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

| VBP          | VSE (0x11) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

| V Active     | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

|              | HSS (0x21) | HBP (0x19,LP) | DATA | BLLP | HFP (0x19,LP) |     |

| VFP          | HSS (0x21) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

|              | HSS (0x21) | BLLP          |      |      |               |     |

**Figure 19. 另一个角度看 Burst Mode 视频格式**

## 2.3 DSI 告警

DSI 告警主要有以下这些，981 相比 941 有更多 DSI 上层协议的告警，这里取两者的全集：

- SoT Error: 同步序列“00011101”发生了单 bit 误码，可以被纠正，没有影响同步。

- **SoT Sync Error:** 同步序列发生多 bit 误码, 无法修正, 影响同步。

- **EoT Sync Error:** 传输的最后一个 bit 不在字节边界处, 即传输了非整数字节数据。

以上三个故障是 **D-PHY** 底层的故障, 可能的原因是物理层信号完整性和 **D-PHY** 收发两端的参数设置不正确, 可以使用示波器排查物理层传输是否发送按照正确的格式发送。

- **DSI\_NO\_EOTPkt:** 数据包结尾缺失 EOT packet。

- **IS\_INV\_TYPE\_GLW\_ERR:** 长包格式无效。

- **IS\_INV\_WC\_GLW\_ERR:** 长包包长度计数字段无效。

- **IS\_INV\_VC\_ERR:** VC 数据无效, 超出了 VC 的上限。

- **IS\_INV\_DT\_ERR:** 数据类型无效, 比如传输视频数据的包被打上了控制包的类型。

- **IS\_CHECKSUM\_ERR:** CRC 校验位出错, 数据传输出错。

- **IS\_ECC\_MULTI\_ERR:** ECC 多 bit 误码, 无法被纠正, 数据传输出错。

- **IS\_ECC\_SINGLE\_ERR:** ECC 单 bit 误码, 可被纠正, 数据传输不受影响。

以上这几个故障是 **DSI** 上层的故障, 可能导致的原因有 **EMC**, 信号完整性和发送端设置错误等可能, 需要借助协议分析仪进一步分析。

## 3 DSI 波形示例简析

观察 **DSI** 信号有两个方法, 一是示波器, 二是 **DSI** 协议分析仪。示波器方式的优点是便于获取和操作方便, 它可以用来观察 **D-PHY** 是否正常, 缺点是无法对数据进行自动解码; 协议分析仪的优点是可以直接分析视频的格式是否正确, 主要用来看是否出现 **DSI** 协议相关的错误, 其缺点是仪器较难获取, 操作较复杂, 需要额外的学习成本。下面以一个实际的例子举一例分析用示波器和协议分析仪分别能看到哪些信息, 并简述这些信息可以如何指导问题的定位。

### 3.1 实测波形分析示例

#### 3.1.1 示波器波形分析

**DSI** 时钟速率很快, 因此使用示波器测量 **DSI** 波形时需要注意示波器的带宽和探头的选择, 一般使用高速差分探头对 **DSI** 波形进行测量。首先可以测试时钟线来看一下时钟速率是否是预期的值, 并确定模式 (连续模式或非连续模式) 是否符合预期。其次数据线上面可以看一下时序是否满足 **D-PHY** 协议的规范, 如图 20 所示的是 **D-PHY** 上从 **LP** 到 **HS** 模式切换的波形, 各个时间段的意义标记在图中, 主要关注是否成功进入 **HS** 模式, 同步序列是否正确, 信号幅值是否正确等等。

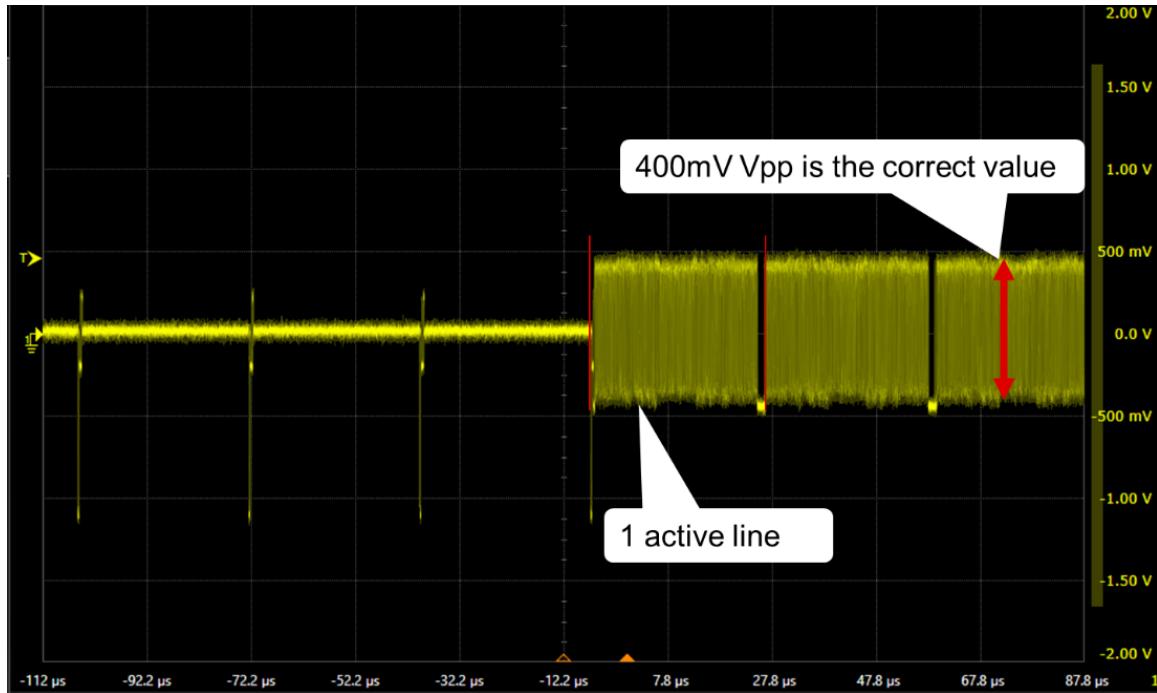

如图 21 所示, 从更宏观的角度可以看一下每一行的时长是否符合预期, 一个常见的问题是发送端在 HFP 等较短的时间块内进入了 LP 模式, 而 LP 模式持续实际必须大于  $T_{LPX}$ , 当此时间块的长度本身短于  $T_{LPX}$  时, 此时间块被人为拉长, 视频时序发生错误, 这可以通过示波器波形看出来。需要注意图 21 中 Active line 部分的信号幅值是错误的, 正常的幅值是 400mVpp (这可以作为一个通过示波器定位到故障的例子, 根因是 TX 端参数设置错误, RX 的端接电阻成功没有使能, 信号幅值变成了错误的 800mVpp)。

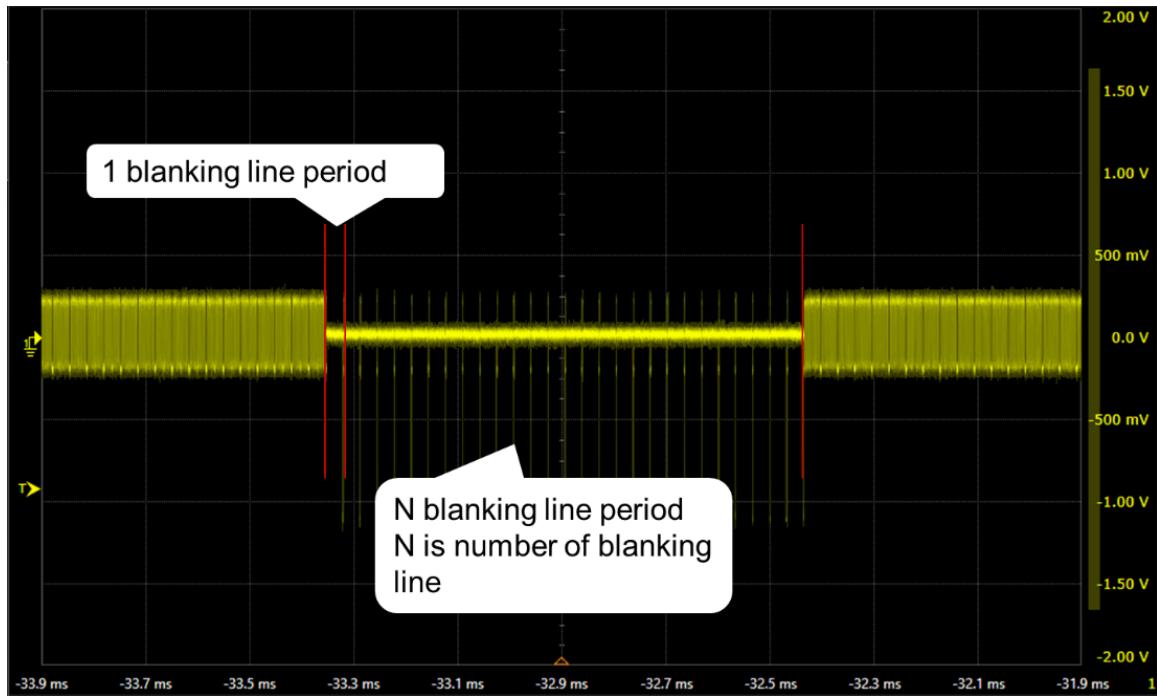

Non-Burst Mode with Sync Pulses 下, 可以很方便找到消隐区行所在的位置, 他们由一串短包序列组成, 如图 22 所示, 在每一个短包之间有一段时间的 LP, LP 的个数等于消隐区的行数, 在没有协议分析仪的情况下通过示波器也可以简单的确认下发送的图像参数是否错误 (排除法, 消隐区格式出错那就一定有错, 反之则不一定)。此外, 没有 LPM 的问题也可以通过示波器进行确认。

**Figure 20.** 差分探头下的 D-PHY 波形 1

Figure 21. 差分探头下的 D-PHY 波形 2

Figure 22. 差分探头下的 D-PHY 波形 3

### 3.1.2 协议分析仪数据分析

协分数据主要用来确认视频时序是否符合预期，是否存传输错误以及传输错误的分布特点等信息。在这里以 Non-Burst Mode With Sync Pulses 模式采集到的 DSI 协议数据为例进行分析。视频的参数如下：

$AHW = 1920$

$AVW = 480$

$HBP = 4$

$VBP = 20$

$HSW = 12$

$VSW = 4$

$HFP = 52$

$VFP = 8$

$PCLK = 61.071 \text{ MHz}$

$Bits\_per\_pixel = 24$

DSI 协分采集的数据有两个维度，一是波形维度，二是解析后的数据维度，相两者各有优势，波形维度可以方便的拖动软件内的光标测量各个时间块的时长，但是无法很方便的确认是否出现传输错误，数据维度则反之，软件可以很方便的统计出是否有数据传输错误，但是确认各个时间块的长度需要手动去加减时间戳来获得，反而可能带来额外工作量。

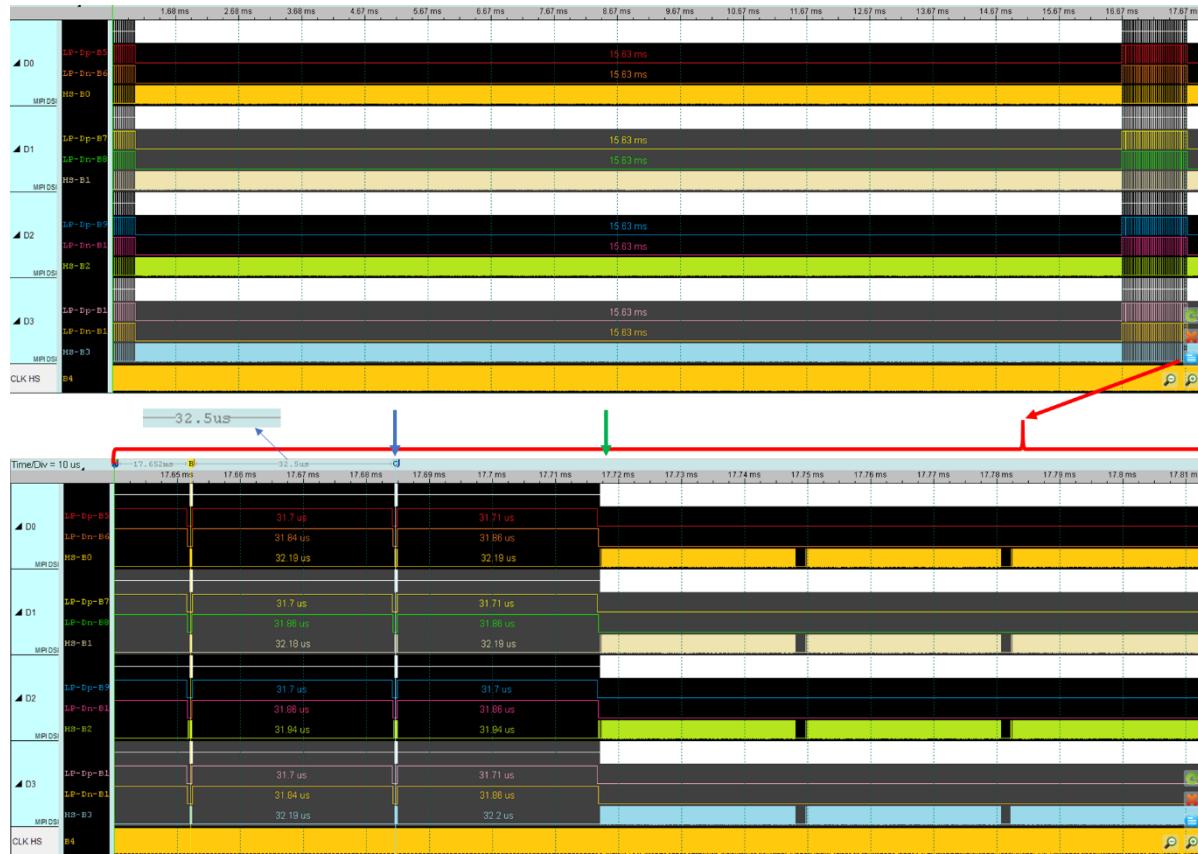

先看波形维度，宏观角度 DSI 波形如图 23 所示，和示波器一样可以快速的查看消隐行的长度是否符合预期，图中光标 B 和 C 之间的时长约是  $32.5\mu\text{s}$ ，理论值经计算可得  $\text{Frame rate} / V_{\text{total}} = 1/60 / (480+20+8+4) = 32.552\mu\text{s}$ ，两者可以很好的对应。如果对于精度有更高的要求，就需要找到 HSS/HSE/VSS/VSE 等特定的数据包来标定每个时间块的具体长度。这就需要对 DSI 数据格式有一定的了解，结合前面章节介绍的内容，以图 24 和 25 来举例，他们分别是图 23 中蓝色和绿色箭头所指位置的局部放大。

Figure 23. 协分下的 DSI 波形 1

如图 24 所示的波形对应的是 H sync pulse 部分，每个数据包对应的内容在图中已经标出，通过找到 0x21 开头和 0x31 开头的这两个短包，可以界定 HSS 和 HSE 的位置，他们中间的时长就是 H sync pulse 的时长，图中光标测量得到 192ns 左右，实际计算值为  $\text{Frame rate} / V_{\text{Total}} / H_{\text{Total}} \times H_{\text{sync width}} = 1/60 / (480+20+8+4) / (1920+4+12+52) \times 12 = 196\text{ns}$ ，测量值和理论值较接近，符合预期。

图 25 所示波形对应的是 HBP+H Active 的部分，每个数据包对应的内容在图中已经标出，通过找到 0x3E 开头的长包，可以确定发送端发送的确实是 RGB888 的数据，且可以根据 WC 的长度 0x1680 得到总共发送了 5760 各字节的数据，即 1920 个像素，这个数据和预期值可以很好的对应上。

**Figure 24. 协分下的 DSI 波形 2**

**Figure 25. 协分下的 DSI 波形 3**

图 26 所示的是 DSI 协分数据解析后的界面，在这个界面上可以看到每一个数据包的类型以及对应的时间戳，可以通过时间戳计算得到确认时序是否正确，举个例子，126 行和 122 行的时间戳相减可以得到一行的时长，计算得  $376.968-344.356=32.612\mu s$ ，理论值前面计算过是  $32.552\mu s$ ，两者可以较好得对应。同时在软件得右侧可以看到统计的结果，没有任何 DSI 得数据出错，DSI 告警数量为 0。

Figure 26. 协分解析后的 DSI 数据

## 4 参考文献

1. Datasheet “DS90UB981-Q1 4K DSI to FPD-Link IV Bridge Serializer”(request through CDDS)

2. Datasheet “[DS90UB941AS-Q1 2K DSI to FPD-Link III Bridge Serializer with Video Splitting](#)”

3. Application Note “[DS90UB941AS-Q1 DSI Bringup Guide](#)”

4. Technical specifications “Specification for D-PHY V1.2”(request from MIPI alliance)

5. Technical specifications “Specification for Display Serial Interface V1.3.1”(request from MIPI alliance)

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月