*Application Note***AM62x、AM62Ax、AM62Px、AM62Lx 展频时钟**

Luis Parga

Sitara MPU

**摘要**

利用高频时钟发送和接收数据的电气接口会辐射能量，可能干扰附近器件的。这种辐射称为电磁干扰 (EMI)。通过使用展频时钟 (SSC)，可以降低 EMI 来满足发射标准和法规。SSC 是一种用于引入时钟信号频率受控变化以降低 EMI 的技术。实现 SSC 时，EMI 分布在更宽的频率范围内，而不是仅仅集中在额定时钟频率。必须注意在整个系统的容差范围内调制时钟，以避免相关电路和器件之间的通信中断。

本文档介绍了在使用具有 24 位 RGB 数据输出的显示并行接口 (DPI) 通过 SSC 调制像素时钟频率时如何降低 EMI。该方法适用于 AM62x、AM62Ax、AM62Px 和 AM62Lx 片上系统 (SoC) 设计。

**内容**

|                                              |          |

|----------------------------------------------|----------|

| <b>1 展频时钟</b> .....                          | <b>2</b> |

| 1.1 SSC 调制速率.....                            | 2        |

| 1.2 SSC 调制深度.....                            | 2        |

| 1.3 SSC 展频类型.....                            | 3        |

| 1.4 SSC 调制曲线.....                            | 3        |

| <b>2 PLL SSC 实现详细信息</b> .....                | <b>4</b> |

| 2.1 PLL SSC 配置寄存器.....                       | 4        |

| 2.2 AM62Px 上使用 DSS PLL17 的 PLL SSC 实现序列..... | 5        |

| <b>3 SSC 结论和注意事项</b> .....                   | <b>6</b> |

**插图清单**

|                    |   |

|--------------------|---|

| 图 1-1. SSC 特性..... | 2 |

|--------------------|---|

**表格清单**

|                         |   |

|-------------------------|---|

| 表 2-1. SSC 支持的配置.....   | 4 |

| 表 2-2. SSC 相关寄存器字段..... | 4 |

**商标**

所有商标均为其各自所有者的财产。

## 1 展频时钟

由于数字时钟信号的周期性和方形属性，时钟的大部分能量集中在中心频率和奇次谐波上。SSC 以受控方式调制时钟额定频率，以减少时钟信号本身的辐射发射。在频域中，SSC 通过在更宽的频率范围内扩展局部峰值能量来降低数字时钟信号的峰值振幅。在时域中，SSC 向时钟信号注入抖动，但电压振幅保持不变。使用以下参数全面描述了 SoC 的 SSC：调制速率、调制深度、展频类型和调制曲线。

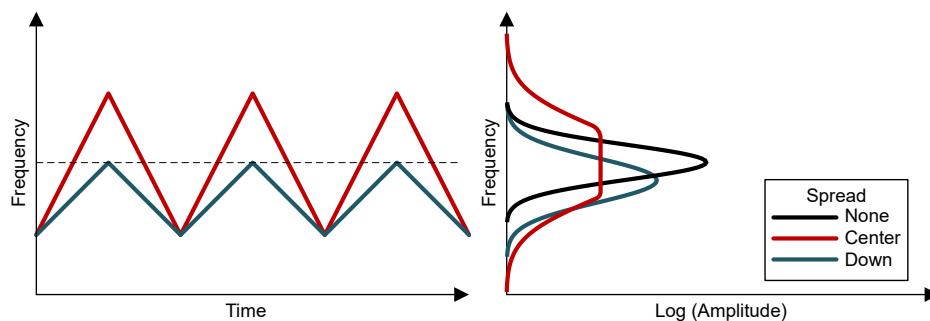

图 1-1 展示了使用常见三角波形状 SSC 调制曲线时的 SSC 特性。SSC 可针对时钟信号进行配置，以产生对称调制输出或配置为产生向下展频调制输出。向下展频类型可根据中心频率降低时钟频率。

图 1-1. SSC 特性

### 1.1 SSC 调制速率

调制周期是指将时钟额定频率从初始值循环到调制曲线上所有不同值并再循环回到初始值所需的时间。调制速率是周期的倒数。

1. 调制速率由 CLKSSCG、128 点内部波形表和分频值 MOD\_DIV 根据  $f_{mod} = f_{CLKSSCG} / (128 \times MOD\_DIV)$  进行控制。

2.  $f_{CLKSSCG} = f_{REF} / REFDIV$ 。为 AM62x、AM62Ax、AM62Px 和 AM62Lx 设置分数 N 模式：

$REFDIV = 1$ 。这意味着在这种情况下  $f_{CLKSSCG} = f_{REF}$ ，其中  $f_{REF}$  是 PLL 参考时钟

(例如  $f_{REF} = 25MHz$ )。

3. 对于由 PLL 带宽决定的调制保真度，为了避免干扰音频应用，调制频率通常设置为高于 32kHz 并低于  $f_{CLKSSCG} / 200$ 。例如，如果使用 25MHz 的 PLL 参考时钟频率，则最大调制频率为 125kHz。

### 1.2 SSC 调制深度

调制深度是指频率的最大变化，以时钟中心频率的百分比表示。对于 AM62x、AM62Ax、AM62Px 和 AM62Lx，最小调制深度为 0.1%，最大为 3.1%。调制深度可按 0.1% 的增量进行调节。

## 1.3 SSC 展频类型

时钟频率变化只会在负极侧（较低频率）或在正极侧（较高频率）与负极侧受到影响。当两侧均匀变化时，展频类型称为中心展频。当仅在负极侧变化时，展频类型称为向下展频。

AM62x、AM62Ax、AM62Px 和 AM62Lx SoC 支持中心和向下展频。

### 小心

请谨慎使用中心展频，因为中心展频会将接口的最高频率增加到高于额定值。必须注意接口设计为能够处理这种稍高的频率。相反，向下展频会导致平均频率小于额定频率。

## 1.4 SSC 调制曲线

调制曲线是指描述调制时钟频率变化的曲线形状。传统曲线包括正弦、三角波、锯齿和赫谢波形状。

AM62x、AM62Ax、AM62Px 和 AM62Lx SoC 默认支持三角波调制。外部波形表可用于使用除三角波以外的曲线来调制时钟频率。

## 2 PLL SSC 实现详细信息

PLL 参考时钟频率  $f_{REF}$  经过 REFDIV 的输入预分频器。该级将高速信号转换为较低频版本进行处理。接下来，反馈乘法器 (FB\_DIV\_INT) 充当压控振荡器 (VCO) 并对转换的信号进行滤波。滤波后的输出反馈至微调性能。最后，配置为 HSDIV + 1 的后分频器在由 PLL 时钟发生器提供信号之前进一步降低信号频率。时钟输出频率的计算公式为

$$f_c = (f_{REF} / \text{REFDIV}) \times \text{FB\_DIV\_INT} / (\text{HSDIV} + 1)$$

SSC 通过按照三角波模式以小步长改变 FB\_DIV\_INT 来实现。

对于显示并行接口 (DPI)，默认情况下 AM62x、AM62Ax、AM62Px 和 AM62Lx 的显示子系统 (DSS) 使用的 PLL 通常多路复用到 PLL17。但是，PLL16 或 PLL18 也可用于 DPI。来自 DSS PLL ( 即 PLL17 ) 的 DPI 的像素时钟频率不得超过 165MHz。

**表 2-1. SSC 支持的配置**

| 参数   | 最小值         | 最大值                 | 单位  |

|------|-------------|---------------------|-----|

| 调制深度 | 0.1         | 3.1                 | %   |

| 展频类型 | 支持中心展频和向下展频 |                     |     |

| 调制速率 | 32          | $f_{CLKSSCG} / 200$ | kHz |

**小心**

对于具有 SSC 的 DPI 应用，客户只批准更改分配给 DPI ( PLL16、PLL17 或 PLL18 ) 的 DSS PLL。

不批准也不建议使用其他 PLL。

### 2.1 PLL SSC 配置寄存器

表 2-2 介绍了为 PLL17 配置 SSC 所涉及的寄存器，PLL17 是一个通常用于 DPI 的 DSS PLL。

**表 2-2. SSC 相关寄存器字段**

| 寄存器名称         | 物理地址偏移  | 位字段信息 |               |                                            |

|---------------|---------|-------|---------------|--------------------------------------------|

|               |         | 位编号   | 名称            | 说明                                         |

| PLL17_CTRL    | 0x11020 | 1     | DSM_EN        | $\Delta - \Sigma$ 调制器使能                    |

|               |         |       |               | 1'b0 : $\Delta - \Sigma$ 调制器已禁用 ( 整数分频模式 ) |

|               |         |       |               | 1'b1 : $\Delta - \Sigma$ 调制器已使能 ( 分数分频模式 ) |

|               | 0x11040 | 0     | DAC_EN        | 分数降噪 DAC 使能                                |

|               |         |       |               | 1'b0 : 已禁用分数降噪 DAC                         |

|               |         |       |               | 1'b1 : 已使能分数降噪 DAC                         |

| PLL17_SS_CTRL | 0x11040 | 31    | BYPASS_EN     | 旁路 SS 调制器                                  |

|               |         |       |               | 1'b0 : 已使能展频调制 (SSMOD)                     |

|               |         |       |               | 1'b1 : 已旁路 SSMOD                           |

|               | 4       | 4     | DOWNSPREAD_EN | 中心或向下展频时钟方差选择                              |

|               |         |       |               | 1'b0 : 中心展频                                |

|               |         |       |               | 1'b1 : 向下展频                                |

表 2-2. SSC 相关寄存器字段 (续)

| 寄存器名称           | 物理地址偏移  | 位字段信息 |         |                                                                                         |

|-----------------|---------|-------|---------|-----------------------------------------------------------------------------------------|

|                 |         | 位编号   | 名称      | 说明                                                                                      |

| PLL17_SS_SPREAD | 0x11044 | 19:16 | MOD_DIV | 输入时钟分频器。该分频器设置调制频率。支持 1 - 63 的分频值。<br>$f_{mod} = f_{CLKSSCG} / (128 \times MOD\_DIV)$ 。 |

|                 |         |       |         | 1'h6 : 如果 $f_{CLKSSCG} = 25MHz$ ，则为 32.6kHz                                             |

|                 |         |       |         | 1'h5 : 如果 $f_{CLKSSCG} = 25MHz$ ，则为 39.1kHz                                             |

|                 |         |       |         | 1'h4 : 如果 $f_{CLKSSCG} = 25MHz$ ，则为 48.8kHz                                             |

|                 |         |       |         | 1'h3 : 如果 $f_{CLKSSCG} = 25MHz$ ，则为 65.1kHz                                             |

|                 |         | 4:0   | SPREAD  | 1'h2 : 如果 $f_{CLKSSCG} = 25MHz$ ，则为 97.7kHz                                             |

|                 |         |       |         | 设置展频调制深度                                                                                |

|                 |         |       |         | 5'b00001 : 0.1%                                                                         |

|                 |         |       |         | 5'b01010 : 1%                                                                           |

|                 |         |       |         | 5'b10100 : 2%                                                                           |

|                 |         |       |         | 5'b11001 : 2.5%                                                                         |

|                 |         |       |         | 5'b11111 : 3.1%                                                                         |

## 2.2 AM62Px 上使用 DSS PLL17 的 PLL SSC 实现序列

需要在完整的 PLL 序列 (如 API 固件定义) 发生且 PLL 被锁定后执行下述 SSC 手动实现序列。在 SDK11.2 版本中设置标准 SSC 软件接口后，不再需要手动重新配置本文档中所述的 SSC 寄存器，预计这将在 2025 年底实现。

- 由于在整数模式下不允许展频，要使能分数分频模式，请通过将 **PLL17\_CTRL[1] DSM\_EN** 设置为 1'b1 来使能  $\Delta-\Sigma$  调制器，并通过将 **PLL17\_CTRL[0] DAC\_EN** 设置为 1'b1 来使能分数消噪 DAC (如果尚未使能)。

- 将 0x691020 设为 0x00018013。

- 通过将 **PLL17\_SS\_CTRL[31] BYPASS\_EN** 设置为 1'b0 来使能展频调制

- 将 0x691040 设为 0x00000000。

- 通过将 **PLL17\_SS\_CTRL[4] DOWNSPREAD\_EN** 设置为 1'b0 (对于中心展频) 或设置为 1'b1 (如果向下展频) 来设置展频类型

- 如果向下展频，则将 0x691040 设置为 0x00000010

- 如果中心展频，则将 0x691040 设置为 0x00000000

- 通过设置 **PLL17\_SS\_SPREAD[19:16] MOD\_DIV** 来设置调制速率。1'h6 对应于 32.6kHz 的调制速率，1'h2 对应于 97.7kHz 的调制速率。

- 通过设置 **PLL17\_SS\_SPREAD[4:0] SPREAD** 来设置调制深度。1'h1F 对应于 3.1% 的调制深度、1'h01 对应于 0.1% 的调制深度。

- 如果调制速率为 32.6kHz、调制深度为 3.1%，则将 0x691044 设置为 0x0006001F

- 如果调制速率为 97.7kHz、调制深度为 0.1%，则将 0x691044 设置为 0x00020001

### 小心

使用中心展频时，请保留以下两项：

- 目标显示能够在较高和较低的峰值调制频率下与 SoC 进行通信。

- SSC 之后的时钟最高频率仍必须小于 165MHz。在计算尽可能高的频率时，还必须考虑到调制深度的 20% 过冲。

### 3 SSC 结论和注意事项

某些显示面板可能具有数据表中未指定的时钟限制，因此需要验证显示是否在展频调制引入抖动时具有足够的功

能裕度。任何由于引入 **SSC** 而导致的与显示相关的问题都需要直接与显示面板制造商合作解决。为了尽可能减少

引入抖动对整个系统的影响，建议保持尽可能低的调制深度，同时仍满足发射标准和法规并具有足够的裕度。

#### 小心

客户将全权负责展频时钟的配置和使用。客户必须研究与所选显示面板相关的时钟限制，并将

**SSMOD** 配置为与该特定显示面板兼容。TI 不计划参与相应 **SSMOD** 配置的评估，因为 TI 不了解与

所选显示面板相关的时钟限制。客户还需要验证 **SSMOD** 配置在任何工作条件下都不会导致任何与系

统相关的问题。客户必须与显示面板供应商合作解决因使能带 **SSMOD** 的 **SSC** 而导致的任何问题。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月