## Application Note

**DP83TD510E 疑难解答指南**

Evan Mayhew, Vivaan Jaiswal

**摘要**

本指南提供了一种对 DP83TD510E 进行故障排除的系统方法，重点是识别和解决在开发、验证和部署过程中通常未解决的问题。本文档涵盖原理图和布局的理想操作、元件选择和验证以及 MDI 和 MAC 接口上的信号完整性等关键方面。本指南结合实际测量、测试模式使用和多种诊断技术，可帮助工程师更深入地了解 DP83TD510E 并加快根本原因分析。

**内容**

|                       |           |

|-----------------------|-----------|

| <b>1 简介</b> .....     | <b>2</b>  |

| <b>2 排查应用问题</b> ..... | <b>3</b>  |

| 2.1 原理图和布局检查清单.....   | 3         |

| 2.2 元件检查清单.....       | 3         |

| 2.3 器件运行状况检查.....     | 3         |

| 2.4 读取并检查寄存器值.....    | 5         |

| 2.5 验证 strap 配置.....  | 5         |

| 2.6 环回.....           | 5         |

| 2.7 MDI 运行状况检查.....   | 6         |

| 2.8 MII 运行状况检查.....   | 10        |

| <b>3 总结</b> .....     | <b>13</b> |

| <b>4 参考资料</b> .....   | <b>14</b> |

**商标**

所有商标均为其各自所有者的财产。

## 1 简介

DP83TD510E 是一款符合 IEEE 802.3cg 10Base-T1L 规范的物理层收发器。PHY 使用低噪声耦合信号处理接收器架构来提供更长的电缆距离和超低功耗。该器件支持 IEEE 802.3cg 10Base-T1L 规范定义的 2.4V p2p 和 1V p2p 电压模式。DP83TD510E 支持直接连接到多个介质访问控制器 (MAC) 接口 ( MII、RMII、RGMII 和低功耗 RMII )。该器件还支持背对背 RMII 模式和非托管模式下的 RGMII，从而提供范围扩展和中继器功能。

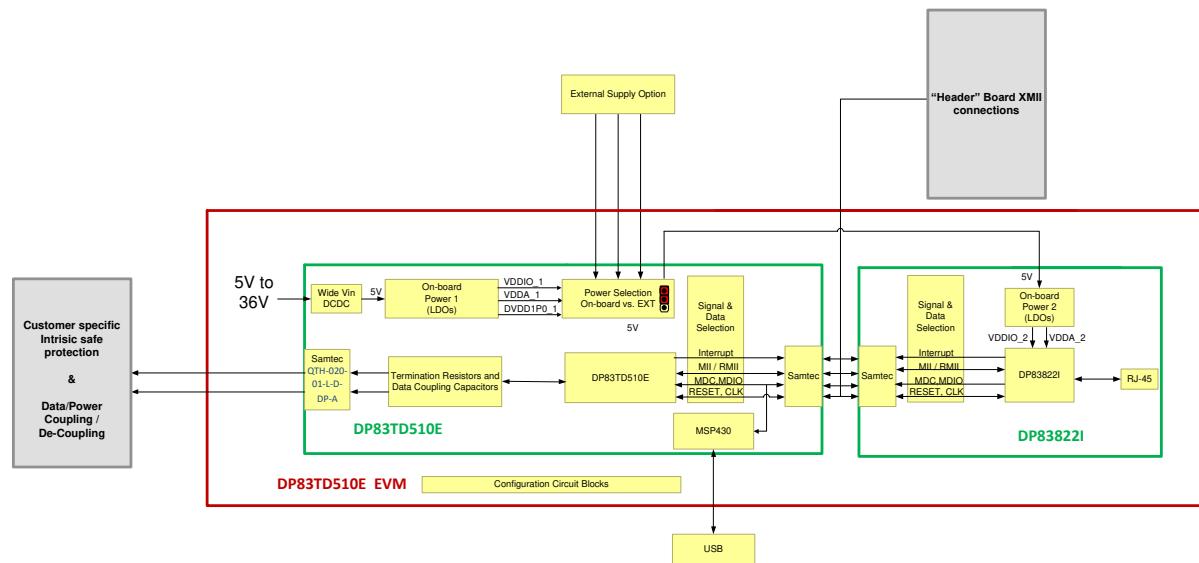

图 1-1 简要概述了使用 DP83TD510E 的典型介质转换应用 (SPE ↔ RJ-45)：

图 1-1. DP83TD510E-EVM 方框图

## 2 排查应用问题

以下各节从较高层次介绍应用调试方法，从具有广泛影响的应用特性开始，然后致力于研究设计的更重点方面。

本应用手册分为三个主要部分：

- [器件运行状况检查](#)

- [MDI 运行状况检查](#)

- [MII 运行状况检查](#)

根据观察到的特定行为，可能不需要所有三个部分。因此，如果观察到正确的行为，则可以跳过某些部分。每部分的开头都提到了这条注释，下面也标注了这条注释。

如果器件符合以下条件，则可跳过器件运行状况检查部分

- 连接到链路伙伴时链路接通（通过寄存器 0x0010 读取状态）或在以太网电缆未连接时显示 NLP 信号

- 按预期响应寄存器访问

如果器件符合以下条件，则可跳过 MDI 运行状况检部分

- 当通过器件发送流量时，已链路接通并通过寄存器 0x0015 报告无数据包错误

本应用手册讨论了几种寄存器设置。为便于访问，本应用手册中包含了一些调试脚本。这些脚本可以与 [USB-2-MDIO](#) 工具配合使用，将 DP83TD510E 重新编程到不同的模式。此处提到的所有脚本的集合以及更多内容，也可参阅 [产品页面](#)。

### 2.1 原理图和布局检查清单

查看原理图和布局时，请确保设计分别遵循原理图和布局检查清单中列出的建议参考指南。这对于验证各种设计选择非常重要，如果这些选择不符合列出的要求，则可能会导致异常的 **PHY** 行为。这种仔细的审查有助于及早发现潜在的设计问题，从而降低后续出现性能问题的可能性。参考并验证以下检查清单中记录的所有原理图和布局建议：

[工业 PHY 布局检查清单](#)

[DP83TD510E 原理图检查清单](#)

以下各节可以介绍 **PHY** 上电并正确初始化后的预期行为。如果与预期行为有任何偏差，则可能会因外设电路不正确而导致误差。

### 2.2 元件检查清单

确保 CMC 和晶体/振荡器等元件满足数据表中列出的要求（在下面也设置了链接）。

[CMC 要求（第 7.2.1.4 节）](#)

[25MHz 晶体要求（第 7.2.2.1.2 节）](#)

[振荡器要求（第 5.6 节）](#)

### 2.3 器件运行状况检查

本节深入介绍器件运行状况检查，该检查可确保器件已充分通电并初始化。如果 DP83TD510 发生如下情况，可以跳过此部分：

- 连接到链路伙伴时链路接通（通过寄存器 0x0010 读取状态）或在以太网电缆未连接时显示 NLP 信号

- 按预期响应寄存器访问

#### 2.3.1 检查电源引脚

在深入进行更复杂的诊断之前，请务必确认 **PHY** 正确供电。DP83TD510E 支持单电源和双电源运行。对于单电源运行，DVDD 必须短接至 C\_EXT，需要测量引脚 VDDA 和 VDDIO 上的电压。但是，在双电源运行中，请检查所有三个电压引脚 VDDA、VDDIO 和 DVDD，以确保电压稳定并处于 [表 2-1](#) 中列出的容差范围内。此外，确保单电源和双电源配置使用正确的去耦电容器（1uF、100nF、10nF）。

应在 **PHY** 电压输入引脚上或尽可能靠近输入引脚测量这些电压

**表 2-1. 电源引脚的预期电压电平**

| 引脚名称     | 引脚编号 | 说明                | 最小值  | 标称值 | 最大值  | 单位 |

|----------|------|-------------------|------|-----|------|----|

| DVDD 1.0 | 1    | 数字电源              | 0.90 | 1.0 | 1.1  | V  |

| VDDA 1.8 | 3    | 模拟电源              | 1.62 | 1.8 | 1.98 | V  |

| VDDA 3.3 |      | 模拟电源              | 3.0  | 3.3 | 3.6  | V  |

| VDDIO    | 17   | 数字电源电压, 以 1.8V 运行 | 1.62 | 1.8 | 1.98 | V  |

|          |      | 数字电源电压, 以 2.5V 运行 | 2.25 | 2.5 | 2.75 |    |

|          |      | 数字电源电压, 以 3.3V 运行 | 3.0  | 3.3 | 3.6  |    |

### 2.3.2 探测 **RST\_N** 引脚

**RST\_N** 引脚是 **PHY** 的低电平有效输入。确认控制器未将 **RST\_N** 信号驱动为低电平, 否则, 器件可能保持复位状态并且可能无法工作。在这种情况下, 器件无法链路接通, 甚至可以访问寄存器。确保该引脚上的电压对应于所选的 **VDDIO** 电压。

### 2.3.3 探测 **CLKOUT** 引脚

**CLKOUT/LED\_1** 引脚 (引脚 30) 是输入/输出 **GPIO** 引脚, 默认输出基准时钟信号, 可用于为电路板上的任何其他器件提供时钟。此基准时钟对于维持 **PHY** 的正常运行至关重要。不符合数据表中的要求可能会导致位错误、读取或写入问题以及一些情况下 **PHY** 完全无法运行。

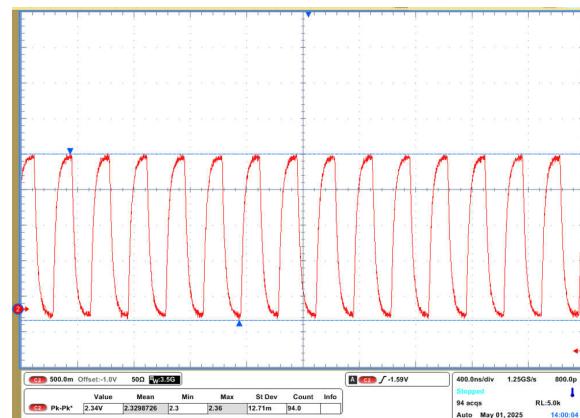

验证输入时钟、晶体或振荡器在加电时是否可用。

该时钟信号是输入时钟晶体或振荡器的缓冲表示形式。如果使用晶体, 请勿直接探测晶体, 因为探测引起的电容变化会改变晶体的行为。

确保此 **CLKOUT** 信号处于 ppm 要求范围内。

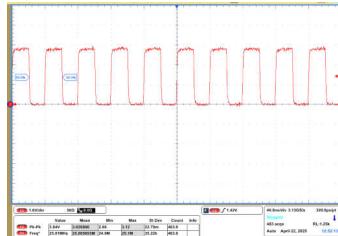

**图 2-1. CLKOUT 信号**

### 2.3.4 探测 **SMI** 引脚

如果寄存器读取和写入成功, 则可以跳过本节。

如果寄存器读取和写入不成功, 则探测 **MDC** 引脚 (引脚 12), 以验证主机控制器提供了  $\leq 1.75\text{MHz}$  的时钟信号。由于这是速度较低的器件, 其速率为  $10\text{Mbps}$ , 因此支持的 **MDC** 时钟速率也较低。另外, 请确保 **MDIO** 引脚具有外部上拉电阻  $2.2\text{k}\Omega - 4.0\text{k}\Omega$ 。此外, 可使用逻辑分析仪对 **MDIO** 信号 (引脚 11) 进行解码。

**图 2-2. MDC/MDIO 信号**

信号 ib [图 2-2](#) 显示了寄存器 0x3 的简单读取命令，其中包含器件型号，DP83TD510 必须始终读取为 0x0181。

注意，要访问 0x1F 以外的寄存器，必须遵循扩展寄存器访问程序，如 [数据表的第 6.3.10 节](#) 所述。

## 2.4 读取并检查寄存器值

读取寄存器并验证返回值与数据表中的默认值匹配。请注意，某些寄存器的初始值可因 strap 配置选项而异。

在 PHY 链接的情况下，使用这些值作为参考来识别预期运行的任何变化。建议检查以下关键寄存器，以确认器件配置：

**表 2-2. DP83TD510E 关键寄存器**

| 寄存器地址                | 复位值    | 关键位/信息                                                                                      |

|----------------------|--------|---------------------------------------------------------------------------------------------|

| 0x0000               | 0x0000 | [15] — 数字复位<br>[14] — MII 回送                                                                |

| 0x0003               | 0x0181 | 器件型号和修订版本号                                                                                  |

| 0x0010               | 0x0000 | [0] — 链路状态                                                                                  |

| 0x0012/0x0013        | 0x0000 | 中断                                                                                          |

| 0x0015               | 0x0000 | MII RX 错误计数                                                                                 |

| 0x0016               | 0x0100 | [8] — 电源模式 ( 睡眠 )<br>[6-0] — 回送                                                             |

| 0x0017<br>( MAC 配置 ) | 0x4001 | [12:11] — RGMII 移位/对齐模式<br>[9] — RGMII 使能<br>[7] — XI 为 {25, 50} MHz<br>[5] — RMII 或 MII 模式 |

| 0x012A               | 0x0000 | [1-0] — TX/RX CRC 错误指示                                                                      |

| 0x012D               | 0x0000 | TX CRC 错误计数器                                                                                |

| 0x0130               | 0x0000 | RX CRC 错误计数器                                                                                |

| 0x0200               | 0x1000 | [15] — AN 复位<br>[12] — AN 使能/禁用                                                             |

| 0x20E ( 自动协商配置 )     | 0xA000 | [15] — T1L 功能<br>[14] — 节能以太网功能<br>[13] — 增加发送/接收电平通告<br>[12] — 增加了发送电平请求                   |

| 0x020F               | 0x0000 | 链路伙伴通告                                                                                      |

| 0x18F6               | 0x0000 | [12] — 发送电平选择<br>[10] — 节能以太网使能                                                             |

## 2.5 验证 strap 配置

不正确的 strap 配置是导致缺少数据吞吐量的常见问题之一。例如，如果选择了不正确的 MII 接口，或者配置了不正确的 PHY 地址，则数据传输无法成功。

加电或复位引脚取消置位期间，确保 MAC 未驱动连接到 PHY 的任何引脚。这可能会导致在此期间对不正确的电压进行采样，并导致 strap 配置值发生变化，因此器件可能会随机运行。PHY 加电或复位结束时，连接到 PHY 的所有 MAC 引脚都必须置于高阻态。

上电时采样的 strap 配置值可使用扩展寄存器访问从寄存器 0x467 (CHIP\_SOR\_1) 中读取。更多有关配置注意事项的信息，请参阅 [数据表的第 6.4.1 节](#)。

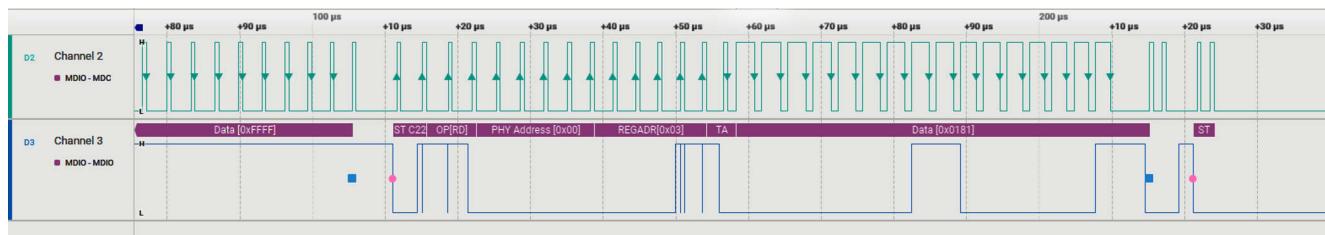

## 2.6 环回

DP83TD510E 具有多个回送选项，可验证 PHY 内的各种功能块。PHY 提供的不同回送模式的方框图如 [图 2-3](#) 中所示。

图 2-3. 回送方框图

MII 回送可通过控制寄存器 ( BMCR , 地址 0x0000 ) 进行配置。所有其他环回模式均通过 BIST 控制寄存器 ( BISCR , 地址 0x0016 ) 启用。这些回送模式可用于验证 PHY 内的 MII 、 MDI 和内部块。这对于缩小数据路径中负责数据包丢失/错误等行为的部分至关重要。

表 2-3 展示了用于使能每种回送模式的寄存器写入 , 假设其他寄存器配置保留为默认值。

表 2-3. 用于回送的寄存器写入

| 回送模式   | 寄存器    | 写入值    |

|--------|--------|--------|

| MII 环回 | 0x0000 | 0x4000 |

| PCS 环回 | 0x0016 | 0x0102 |

| 数字环回   | 0x0016 | 0x0104 |

| 模拟环回   | 0x0016 | 0x0108 |

| 反向环回   | 0x0016 | 0x0110 |

有一些内置的用于 TX 和 RX 的计数器 , 可帮助通过回送进行调试。这些计数器可用于验证在不同回送模式下接收或发送的数据包数量。请注意 , 如果 0x12B 、 0x12C 和 0x12D 用于 TX 计数器 , 0x12E 、 0x12F 和 0x130 用于 RX 计数器 , 则计数器会复位。可以在 表 2-4 中提供的一组寄存器中找到这些计数器。

表 2-4. TX/RX 数据包计数器寄存器

| 寄存器    | 功能                             |

|--------|--------------------------------|

| 0x012A | [1] RX CRC 指示<br>[0] TX CRC 指示 |

| 0x012B | TX 数据包计数器的低 16 位               |

| 0x012C | TX 数据包计数器的高 16 位               |

| 0x012D | 存在 CRC 错误的 TX 数据包              |

| 0x012E | RX 数据包计数器的低 16 位               |

| 0x012F | RX 数据包计数器的高 16 位               |

| 0x0130 | 存在 CRC 错误的 RX 数据包              |

## 2.7 MDI 运行状况检查

MDI 问题通常包括数据包丢失、自动协商问题和链路中断。有几种不同的测试用于缩小遇到意外行为的根本原因。

如果 DP83TD510 发生如下情况 , 可以跳过此部分 :

- 当通过器件发送流量时 , 已链路接通并通过寄存器 0x0015 报告无数据包错误

### 2.7.1 链路接通常见问题

如果 DP83TD510E 在与链路伙伴链路接通时遇到问题 , 请检查以下常见原因。

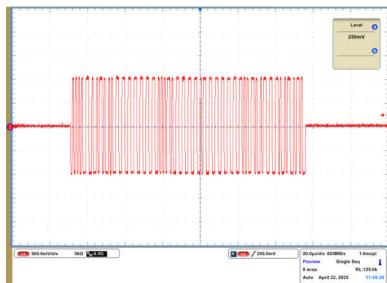

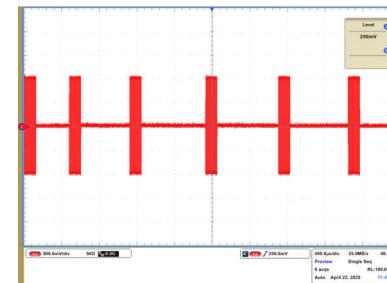

确保器件在连接到未通电的链路伙伴或使用  $50\Omega$  进行正确端接时在 MDI 线路上发送正常链路脉冲 (NLP)。这些信号充当共享链路的 2 个 PHY 之间的信息交换，以便信号能够在专为这两个器件设计的配置中链路接通。以下波形展示了预期信号。

图 2-4. 正常链路脉冲 (放大图)

图 2-5. 正常链路脉冲

DP83TD510 还可绕过此自动协商阶段，通过手动禁用自动协商并配置每个器件，一个配置为主机，另一个配置为客户端，强制建立链路。下面提供了这些功能的脚本。所选的发送电平与器件已配置的电平相同，并反映在寄存器 0x18F6[12] 中。

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0001

000E 0834

000D 4001

000E 4002 // Configure Device as Master, write 0002 for slave

end

```

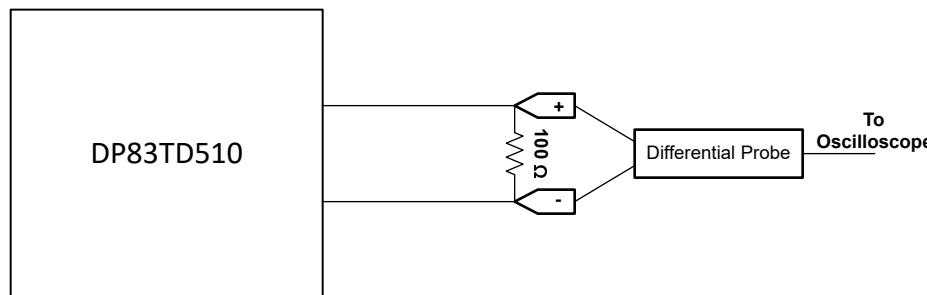

## 2.7.2 发送电平

10Base-T1L 器件能够在 2 个发送电平  $2.4V_{pp}$  和  $1V_{pp}$  之间切换。通常，自动协商负责根据从链路伙伴接收到的通告选择发送电平，但这对于确保将所链接的两个 PHY 配置为通告所需的发送电平非常重要。可以在寄存器 0x20E 的位 12 中查看通告的发送电平

一个很好的过程是必须通过配置为所需的发送电平来选择发送电平，但这些电平也可以在加电后通过寄存器配置进行更改。

同样重要的是确保在测量电压输出电平时使用正确的  $100\Omega$  端接。

图 2-6. MDI 测量

### 2.7.2.1 更改发送电平

一般而言，有两种方法可以切换发送电平。第一种是当没有建立链路时，第二种是在 2 个 PHY 之间建立了链路时。

在没有建立链路时，更改寄存器 0x20E 以仅通告所需的电压。要对此进行测试，请通过使能数字回送来强制链路接通，使能 3 电平输出信号。这将在 MDI 信号上开启空闲波形，可以探测该波形来验证电压摆幅电平。

```

begin

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 001F

000E 0016

000D 401F

000E 0104 // Enable digital loopback to force link up to have three level signal

end

```

在第二种情况下，我们需要更改两个 PHY 上的发送电平，因此这是一个 3 步流程。首先，我们需要禁用自动协商，强制实现所需的电压，更改发送电平通告，并在 PHY 1 上执行软复位。其次，我们需要在 PHY 2 上执行相同的操作，并在最后重新使能自动协商。最后，我们可以返回到 PHY 1 并重新使能自动协商。下面提供了这 3 个步骤的脚本。

#### 第 1 步 (DP83TD510 PHY 1)

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0007

000E 020E

000D 4007

000E B000 // Increase the transmit level advertisement, write 8000 for 1V

000D 001F

000E 0010

000D 401F

000E 4000 // soft reset

end

```

#### 第 2 步 (DP83TD510 PHY 2)

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0007

000E 020E

000D 4007

000E B000 // Increase the transmit level advertisement, write 8000 for 1V

```

```

000D 001F

000E 0010

000D 401F

000E 4000 // soft reset

000D 0007

000E 0200

000D 4007

000E 1000 // Re-enable AN

end

```

### 第 3 步 (DP83TD510 PHY 1)

```

begin

000D 0007

000E 0200

000D 4007

000E 1000 // Re-enable AN

end

```

#### 2.7.3 时域反射法

时间域反射法用于确定电缆、连接器和终端的质量，还可以估算电缆长度。这确定开路、短路、电缆阻抗不匹配、连接器不良、端接不匹配、跨接故障、交叉短路以及电缆上的任何其他不连续性等故障。

此过程涉及通过线对中的每根导线发送一个已知振幅为 1V 的测试脉冲，并测量由任何缺陷以及电缆末端引起的信号反射的返回时间和振幅。

有关 DP83TD510 电缆诊断工具套件的更多信息，请参阅下面链接的应用手册。

#### 电缆诊断工具套件

#### 2.7.4 信号质量检查

通过读取寄存器 0x0010 确认链路接通后，可以使用内置信号质量指标 (SQI) 功能来验证链路的信号质量。链路质量不佳可能是由布局或电缆缺陷引起的，还会导致数据包丢失或错误，甚至导致链路中断。

虽然 TDR 可以提供有关电缆故障存在和位置的信息，但对信号质量的这种实时监测可以通过在链路实现后定期测量信噪比 (SNR)，在故障发生之前提供有价值的信息。

此 MSE 值存储在内存寄存器 0xA85 中。可以将这些值与 [表 2-5](#) 进行比较以评估链路的运行状况。

**表 2-5. SQI 链路运行状况**

| SQI 链路运行状况 | MSE                 | SNR (dB)            |

|------------|---------------------|---------------------|

| 不佳         | MSE > 0660h         | SNR < 17.29         |

| 勉强可用       | 0660h ≥ MSE > 0320h | 17.29 < SNR < 20.38 |

| 好          | MSE ≤ 0320h         | SNR > 20.38         |

有关 DP83TD510 电缆诊断工具套件的更多信息，请参阅 [电缆诊断工具套件](#) 应用手册

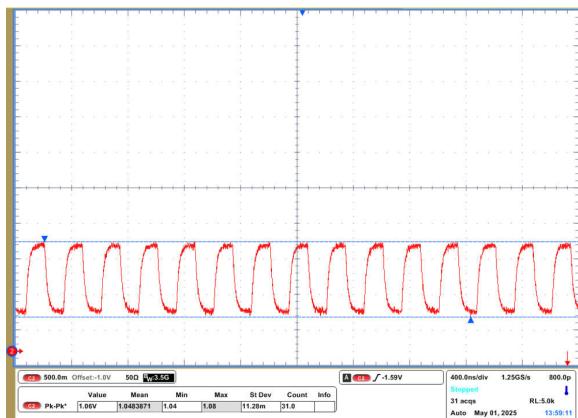

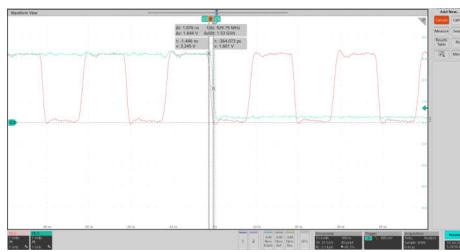

#### 2.7.5 MDI 测试模式

有三种内置测试模式可验证 MDI 输出是否在预期规范内。这些测试模式可通过寄存器 0x18F8 激活。这些测试模式在执行 PMA 合规性测试中以及验证输出电压是否正确非常有用。下图显示了测试模式 1 的一些捕获波形。

图 2-7. 测试模式 1 (1Vpp)

图 2-8. 测试模式 1 (2.4Vpp)

## 2.8 MII 运行状况检查

MII 问题通常包括 MII 模式不匹配、主机或从机配置、时钟和时序差异。DP83TD510 支持 MII、RMII ( 主机和从机 ) 和 RGMII 模式。在进一步研究之前，请确保在 **PHY** 和 **MAC** 上选择了正确的 MII 接口。这可以通过寄存器 0x17 (MAC\_CFG\_1) 的位 5 和 9 来检查。

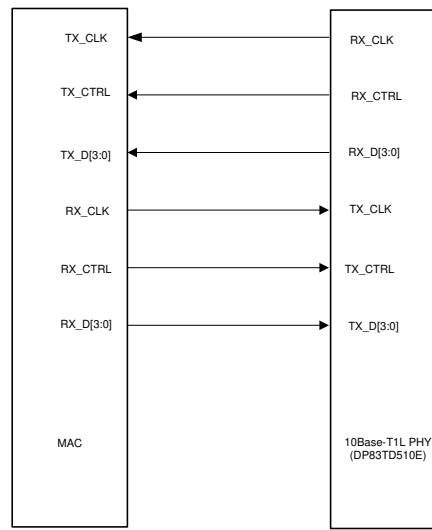

### 2.8.1 RGMII

RGMII 接口可通过配置或使用寄存器 0x17 进行选择。不能满足 RGMII 数据表中列出的时序要求是一个常见问题。虽然 RGMII 接口的时序要求在接口选项中是最严格的，但与千兆位 RGMII 相比，10Mbps 速率的时序要求没有 RGMII 那么严格。无论如何，验证是否满足时序要求至关重要。[数据表第 5.6 节](#) 列出了这些要求。

此外，验证下面所示的 RGMII 所需的信号是否在 **PHY** 和 **MAC** 之间正确布线。

如果怀疑 **MAC** 总线有问题，请探测布线接收器侧的线路，确保满足接收器的建立时间和保持时间以及 VIH/VIL 要求。违反这些规范的典型症状是，当 **PHY** 指示干净的流量 ( 寄存器 0x15 ) 时，**MAC** 上出现数据包错误。

可以使用寄存器 0x0017 位 [12:11] 来切换 RGMII 时钟移位，以便满足这些要求

图 2-9. RGMII 信号

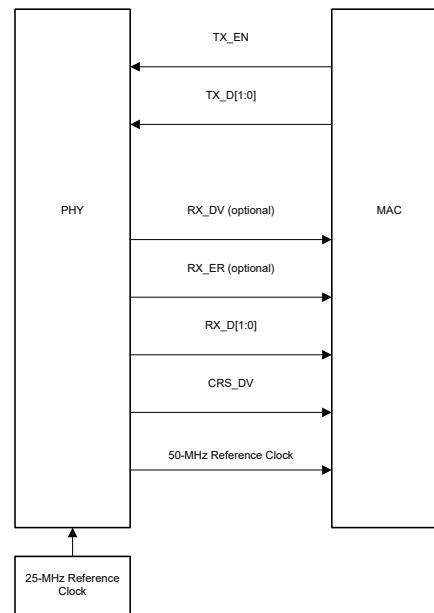

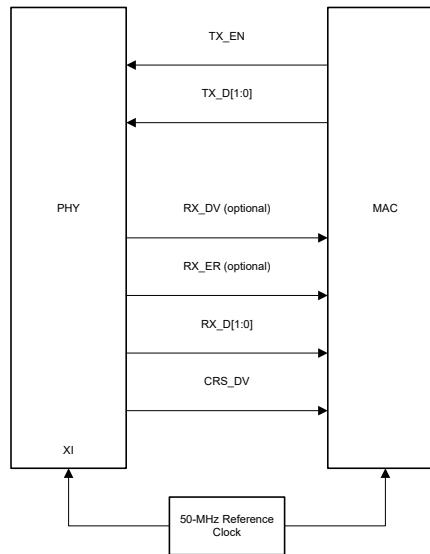

### 2.8.2 RMII

RMII 接口可通过配置或使用寄存器 0x17 进行选择。与 RGMII 和 MII 类似，RMII 也具有一定的时序要求，必须满足这些要求才能使 **PHY** 正常运行。[数据表第 5.6 节](#) 列出了这些要求。

与 RGMII 和 MII 不同，RMII 具有主从模式。可以在加电时配置为这些模式，无法通过寄存器更改。

如果怀疑 MAC 总线有问题，请探测布线接收器侧的线路，确保满足接收器的建立时间和保持时间以及 VIH/VIL 要求。违反这些规范的典型症状是，当 PHY 指示干净的流量（寄存器 0x15）时，MAC 上出现数据包错误。

可使用寄存器 0x0017 位 [8] 来切换 RMII 时钟移位，以便满足这些要求。

在 RMII 主模式下，DP83TD510 采用 25MHz 输入时钟（晶体或振荡器）运行，并为 MAC 提供基准 50MHz 时钟以同步数据。可以移位此时钟，以确保使用寄存器 0x17 [9] 满足接收器（MAC）的建立时间和保持时间。使能此延迟会在 50MHz 输出时钟上增加大约 4ns 的延迟。建立时间和保持时间是重要的时序要求，必须满足该要求才能确保传输过程中不会发生数据包丢失或错误。

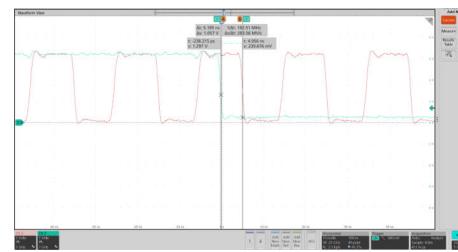

图 2-10. RMII 主信令

图 2-11. RMII 时钟移位已禁用

图 2-12. RMII 时钟移位已使能

在 RMII 从模式下，DP83TD510 采用 50MHz 输入时钟运行，PHY 和 MAC 共用该时钟。或者，PHY 还可采用 MAC 提供的 50MHz 基准时钟运行。确保在 RMII 从模式下为 PHY 提供的此时钟满足  $\pm 100\text{ppm}$  的要求，以使 PHY 正常运行。

图 2-13. RMII 从信令

由于每种模式都需要不同的输入时钟信号，因此请确保在加电期间配置正确或预期的 RMII 模式，以便器件正确启动和执行。

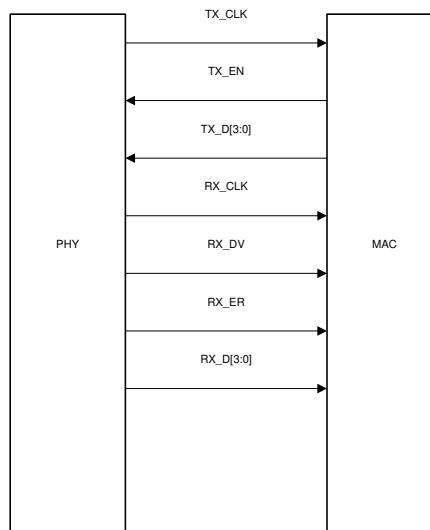

### 2.8.3 MII

MII 接口可通过配置或使用寄存器 0x17 进行选择。与 RGMII 类似，MII 也具有 PHY 正常运行必须满足的某些时序要求。数据表第 5.6 节 列出了这些要求。

此外，验证下面所示的 MII 所需的信号是否在 PHY 和 MAC 之间正确布线。

如果怀疑 MAC 总线有问题，请探测布线接收器侧的线路，确保满足接收器的建立时间和保持时间以及 VIH/VIL 要求。违反这些规范的典型症状是，当 PHY 指示干净的流量（寄存器 0x15）时，MAC 上出现数据包错误。

图 2-14. MII 信令

### 3 总结

本应用手册提供了评估新应用和确认预期功能的建议流程。这些分步建议可以帮助简化 DP83TD510 设计的电路板启动和初始评估。

## 4 参考资料

- 德州仪器 (TI) , [DP83TD510E 超低功耗 802.3cg 10Base-T1L 10M 单线对以太网 PHY](#) , 数据表

- 德州仪器 (TI) , [DP83TD510E 电缆诊断工具套件](#) , 应用手册。

- 德州仪器 (TI) , [DP83TD510E-USB-2-MDIO-SCRIPTS](#) , 支持软件

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址：Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025, 德州仪器 (TI) 公司