*Application Note*

# 如何保护运算放大器免受静电放电和电气过应力损坏

*Carrie Stoll, Art Kay*

## 摘要

运算放大器长期以来一直使用静电放电 (ESD) 单元，以防止器件在使用前损坏。然而，具体设计细节往往处于黑盒状态。本应用手册讨论了 ESD 单元的类型、使用单元的原因、如何查阅器件数据表以确定所用 ESD 单元的类型，以及如何有效保护电路免受 ESD 事件的影响。

## 内容

|                                    |    |

|------------------------------------|----|

| <b>1 简介</b>                        | 2  |

| <b>2 ESD 概述</b>                    | 3  |

| 2.1 什么是静电放电？                       | 3  |

| <b>3 ESD 单元的类型</b>                 | 5  |

| 3.1 双二极管配置                         | 5  |

| 3.2 自举二极管                          | 7  |

| 3.3 吸收器件                           | 8  |

| 3.4 硅控整流器                          | 10 |

| 3.5 CER 和 ECR NPN 二极管              | 11 |

| 3.6 ESD 单元对比                       | 13 |

| <b>4 如何根据数据表确定器件的 ESD 结构</b>       | 14 |

| <b>5 如何保护系统免受电路内 ESD/EOS 事件的影响</b> | 16 |

| 5.1 使用 TVS 二极管和串联电阻实现电路保护          | 17 |

| 5.2 使用肖特基二极管实现电路保护                 | 18 |

| <b>6 如何在系统级电路中测试运算放大器</b>          | 20 |

| 6.1 ESD 保护单元发展历程                   | 21 |

| <b>7 总结</b>                        | 22 |

| <b>8 参考资料</b>                      | 22 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

运算放大器可能会因静电放电 (ESD) 或其他类型的电气过应力 (EOS) 事件而损坏。内部运算放大器器件配有 ESD 保护结构（称为 ESD 单元），旨在防范电路外 ESD 事件。电路外是指在将器件焊接到 PCB 之前，在封装测试过程中对器件施加的 ESD。在某些情况下，ESD 保护结构还可以防范电路内 ESD 以及其他形式的 EOS。但是，了解所用 ESD 单元类型以及其在过应力事件中的行为仍旧十分重要。此外，器件通常需要加装电阻器、TVS 二极管和肖特基二极管等外部元件来提高对过应力信号的抗冲击能力。最后，在电路板级产品测试中，了解所用 ESD 单元类型非常重要，因为不同的 ESD 单元在电路板级测试中具有不同特性。本文档介绍了各种 ESD 单元，并讲解如何搭配使用 ESD 单元与外部元件以保护放大器。本文档还介绍了电路板级产品测试中常见 ESD 单元的一般特性。

## 2 ESD 概述

### 2.1 什么是静电放电？

当两个电荷不平衡的物体靠近时，就会发生静电放电 (ESD)。两个物体之间突然产生电流，这种现象称为 ESD。绝缘体尤其容易积累较大的静电电荷。

ESD 是半导体受损的最常见方式。通过分析 ESD 可产生的电压，可了解到 ESD 放电与人类感知程度之间存在显著差距。某些 IC 在 10V 电压下就会损坏，但人类甚至无法感知到 3500V 以下的放电。CMOS 和运算放大器极易在远低于人类感知电压的电压阈值下损坏。因此，即使未察觉到 ESD 事件发生，也半导体可能损坏。人工操作或与机器接触均会引起静电放电。因此，在投入应用前，保护器件免遭 ESD 事件损坏非常重要。

#### 2.1.1 半导体中的 ESD 单元稳健性

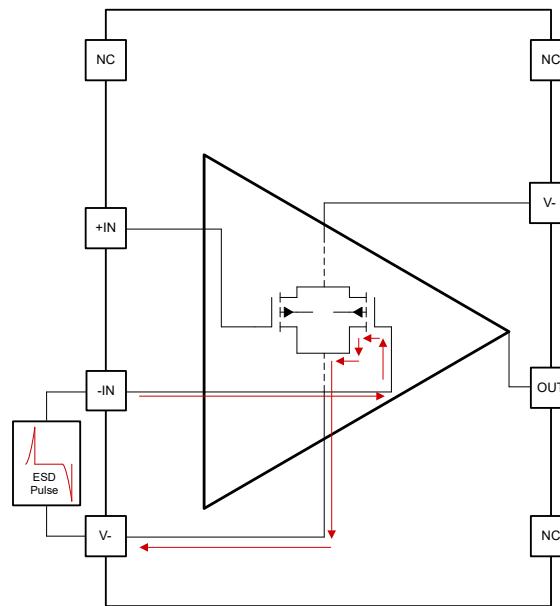

让我们更深入了解半导体器件被 ESD 损坏的典型方式。假设在运算放大器的反相输入端和负电源引脚之间施加较大 ESD 电位或电压 ( 图 2-1 )。

图 2-1. ESD 事件电压路径

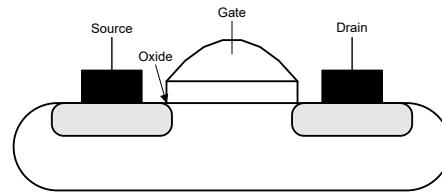

此 ESD 事件会在其中一个输入 MOSFET 的栅极和源极之间施加较大电压，进而导致器件损坏。MOSFET 栅极氧化层的厚度为纳米级，因此 MOSFET 极易受到此类损坏。

图 2-2. MOSFET 示意图

ESD 保护二极管可提供必要防护以防发生此类损坏。器件操作不当可能会导致意外的 ESD 事件。ESD 脉冲产生的常见方式之一是通过 IC 与人的交互。人体可因行走时与地面摩擦、接触家具等行为积聚静电放电。如果未经适当 ESD 保护措施直接接触器件，这些电荷会迅速泄放到 IC 中。静电电压通常可达千伏，彰显了配置 ESD 单元的必要性。为确保器件能够承受此类事件，运算放大器将耐受快速电压浪涌 ( 千伏范围内 )，经过测试后可确保器件仍正常工作。这一仿真称为人体放电模型 (HBM)。

为确保 IC 能够承受 ESD 事件，实验室中模拟的另一个现实 ESD 事件示例是充电器件模型 (CDM)。CDM 通过在器件与自动测试机（或整个组装过程中使用的其他自动化设备）之间的电荷积聚现象，模拟制造和组装过程中最常发生的事件。当器件接触接地导体时，残余电容会放电，可能会对 IC 造成损坏。需要小心操作器件，以免触发 ESD 事件。在模拟此类故障模式时，需要对器件施加高压，然后再进行功能测试。由于放电时间通常以纳秒计，因此大多数故障表现为栅极氧化物损伤（如上所示）和结损伤。

机器模型 (MM) 先前用于模拟最恶劣情况下的 HBM 事件。但这无法准确模拟现实中的 ESD 事件，因此不再使用。现在，半导体的 ESD 稳健性测试均使用 HBM 和 CDM。

JEDEC 是电子器件工程联合委员会，为半导体器件的可接受 ESD 等级（包括 HBM 和 CDM 测试）制定了行业标准。有关 JEDEC 和半导体行业要求的更多详细信息，请参阅官方网站。所有器件数据表都包含相应模型的电压阈值。典型 ESD 等级表示例如 表 2-1 所示，所用器件为 OPA596。了解器件的保护类型十分重要。下一部分将讨论不同类型的 ESD 单元。

**表 2-1. OPA596 的 ESD 等级**

|             |      |                                            | 值          | 单位 |

|-------------|------|--------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静电放电 | 人体放电模型 (HBM)，符合 ANSI/ESDA/JEDEC JS-001 标准  | $\pm 1000$ | V  |

|             |      | 充电器件模型 (CDM)，符合 JANSI/ESDA/JEDEC JS-002 标准 | $\pm 500$  |    |

### 3 ESD 单元的类型

那么该如何防范 ESD？设计必须采用保护措施，防范可能在几纳秒内放电的数千伏电压。解决方案很简单：使用二极管。本质上，所有 ESD 单元都是二极管的变体。一个本质上是 PN 结的二极管在其进入正向偏置状态时会钳制高电压。然而，在反向偏置状态下，二极管则处于高阻抗状态，支持正常运行。因此，该方法非常适合在不影响 IC 正常运行的情况下防护 ESD 单元。

ESD 单元有许多不同的类型。不过，每种 ESD 单元都各有优缺点。本部分将讨论最常见类型的 ESD 单元，以及 IC 设计人员如何为器件选择正确类型的单元。

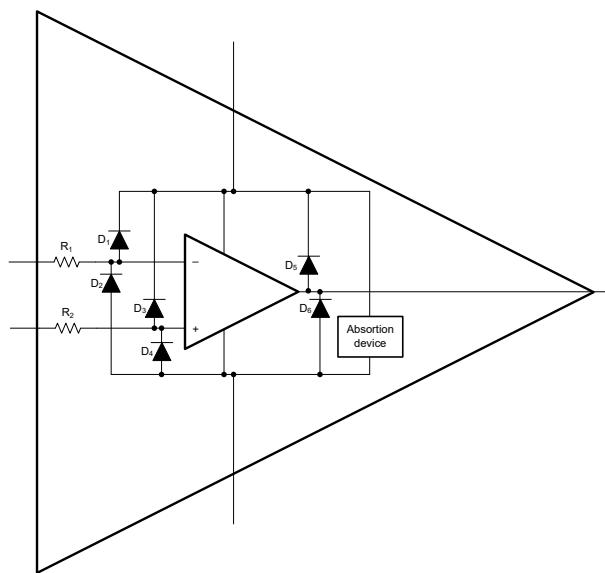

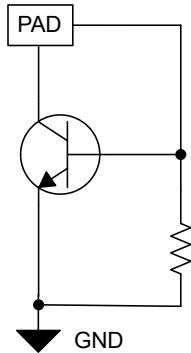

#### 3.1 双二极管配置

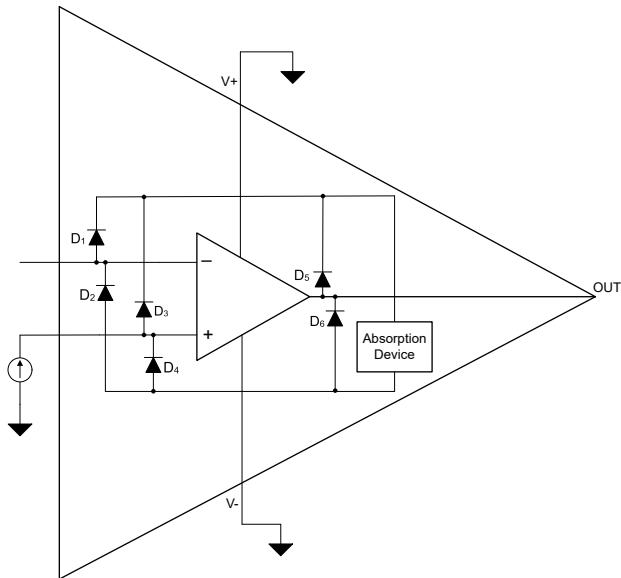

图 3-1 展示了常见的运算放大器 ESD 保护结构。双二极管放置在输入端和输出端，并连接到电源。ESD 二极管会将各类 ESD 瞬变传导至电源。因此，二极管通常称为 ESD 控向二极管。为防止损坏运算放大器电源，电源配备了 ESD 吸收器件。当 ESD 事件发生时，吸收器件触发并发挥低阻抗作用。因此，吸收器件可限制施加在电源上的电压，从而保护器件。

图 3-1. 运算放大器输入和输出端的双二极管配置

双二极管配置的优点包括低漏电流和低电容，进而成为大多数运算放大器的理想选择。二极管占用面积较小，是应对高频输入和输出的首选。但在特定情况下，双二极管配置并不提供保护功能。

### 3.1.1 双二极管配置并非通用之选？

双二极管配置非常适合大多数运算放大器保护设计，但如果输入端电压高于电源电压，则不建议采用此配置。如果在放大器上电之前向其施加输入信号，这类保护设计就会出现问题。某些应用可以关断上电设备，但仍会施加输入信号。如果没有额外的保护，双二极管配置就无法有效抵御此类输入信号。本文档后续的电气过应力部分将具体介绍此问题。

开漏输出是不宜采用双二极管配置另一种情况。开漏输出是指器件的输出连接到晶体管漏极。在此设置中，器件只能灌入电流。在采用开漏输出设计时，传统的双二极管不会放置在输出端。否则，电压会钳制在电源电平，器件无法按预期工作。这方面的示例包括计时器、部分比较器和各种差分放大器。差分放大器的输入信号通常高于电源电压，因此需要采用其他保护方法来避免 ESD。

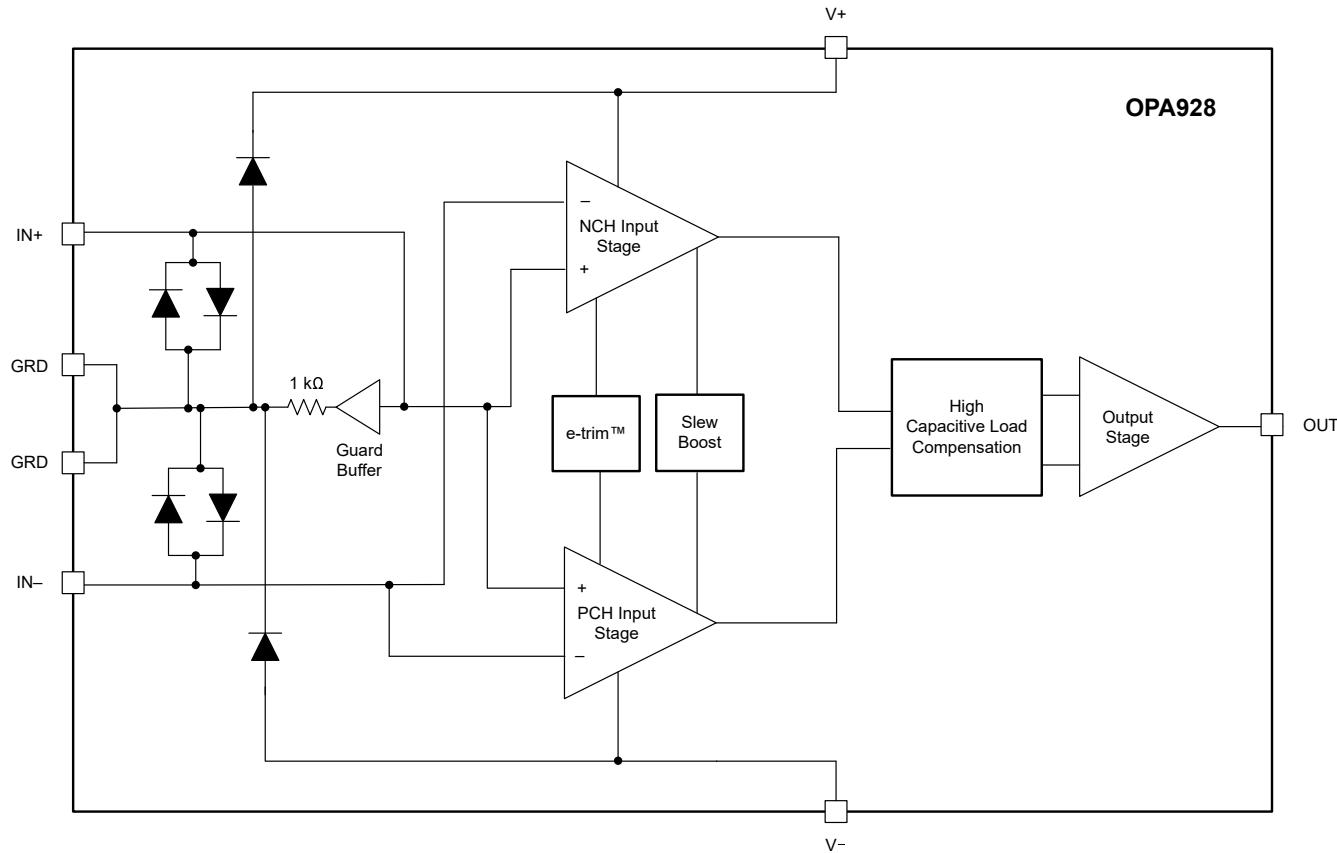

### 3.2 自举二极管

本文仅讨论双二极管 ESD 保护结构。另一种 ESD 保护结构称为自举二极管，其中二极管并联并反向放置。通过在输入端与电源之间加装一个二极管，即可打造与前文相同的保护路径。

典型的 ESD 控向二极管具有漏电流。室温下电流达皮安级，125°C 下电流则可达数千皮安。对于具有高源阻抗的应用，这一漏电流会导致显著的输入失调电压误差。自举可使漏电流在整个温度范围内保持在飞安级。为此，自举会控制输入电压，并在二极管另一侧强制施加相同的电压。强制施加的电压称为防护电压。输入 ESD 二极管在阴阳极上具有相同的电压，因此二极管上的电压为零伏。强制二极管上的电压为零也称为自举，可将漏电流抑制到基本为零。在 ESD 事件期间，输入二极管将 ESD 脉冲传导至与电源相连的二极管。由于电源接有两个二极管，因此测量从输入端到电源的压降。此处压降为 1.4V，即大约两个二极管压降。使用该拓扑的旗舰器件为 OPA928。自举输入可在 25°C 和 85°C 条件下提供 20fA 的输入偏置电流。

图 3-2. OPA928 自举二极管结构

### 3.3 吸收器件

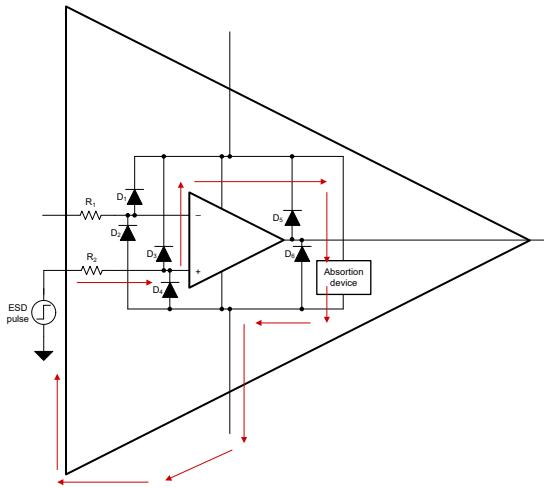

吸收器件是一种内部钳位器件，当输入 ESD 事件通过输入二极管传导至电源时，其用于限制运算放大器电源两端的电压。图 3-3 展示了吸收器件的典型概要结构。

图 3-3. 吸收器件

吸收器件旨在于**电路外 ESD** 事件期间钳制电源电压，进而避免损坏。事件结束后（通常在几纳秒后），吸收器件会因未接通电源而关断。如果吸收器件因**电路内 ESD** 事件而导通，则其可以持续导通并处于低阻抗状态，直到电路断电。因此，在电路内电气过应力事件期间不得导通吸收器件。

图 3-4. ESD 二极管控向

图 3-4 展示了一个向运算放大器同相节点施加 ESD 脉冲的示例。在现实场景中，器件操作不当即会引发此类事故；例如在非静电安全工作台上组装 PCB。请留心，二极管 D3 将变为正向偏置并将 ESD 脉冲导引至吸收器件。吸收器件旨在限制电压和吸收 ESD 脉冲的能量。注意如果将 ESD 脉冲施加到不同的引脚上，则会导通不同的二极管并将脉冲导引至吸收器件。另请注意的是输入电阻 R2 会限制来自 ESD 脉冲的输入电流。R2 的值越大，电路就越可靠稳健，因为电阻会限制进入器件的电流。然而偏置电流和噪声也会带来误差，进而影响电路的频率响应。

### 3.3.1 有源钳位

有源钳位是半导体中非常常见的吸收器件。有源钳位是一类大功率 MOS，其在 ESD 条件下处于有源模式，在正常工作条件下处于高阻抗状态。在 ESD 事件期间，MOS 充当开关，可在低压降下实现均匀的电流流动。此器件支持边沿触发（基于  $dv/dt$ ）以及电平触发。这类器件最常用于在电源断电但仍有输入信号时提供保护。

图 3-5. 有源钳位

该结构的一个优点是钳位电压非常低。但是，具体性能基于漏极电流饱和，钳位由此会占用很大的面积。因此，如果集成电路的尺寸是关键参数，则其他类型的钳位会更加实用。

### 3.3.2 GCNMOS 钳位

栅极耦合 NMOS (GCNMOS) 钳位是吸收器件的另一种常见形式。NMOS 的栅极连接到 RC 触发电路，该电路会在 ESD 事件期间被拉至高电平。通常情况下，电路的响应时间小于 10ns。此类钳位与有源钳位有类似的优缺点，其中尺寸是主要考量因素，同时钳位电压也更低。

图 3-6. GCNMOS 钳位

有源钳位和 GCNMOS 钳位都均为回弹保护结构的形式。下一部分重点介绍其他形式的回弹 ESD 保护单元。

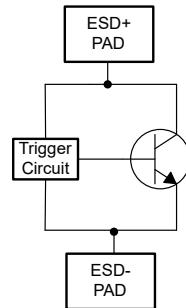

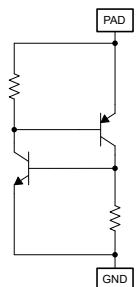

### 3.4 硅控整流器

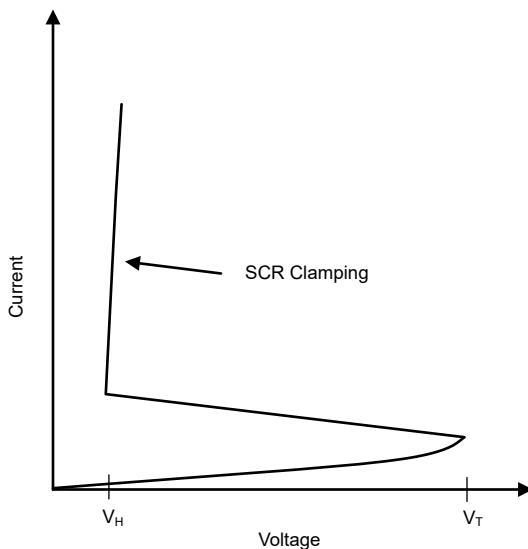

硅控整流器 (SCR) 是用于钳位的另一常见选择。SCR 利用 MOSFET 漏极的空穴生成特性来提升 NPN 的基极电流。该设计具有级联效应，进而会提升寄生 PNP 中的电流，从而实现再生。SCR 利用级联 PNP/NPN 器件结构来实现 ESD 保护。SCR 具有低保持电压 ( $V_H$ )，但触发电压 ( $V_T$ ) 较高，这会导致深度快速恢复现象。在 IV 曲线 (图 3-7) 中可以清楚地看到这一现象。图 3-8 是典型 SCR 的概要设计图。

图 3-7. SCR IV 曲线

图 3-8. SCR 钳位

由于 SCR 尺寸小巧，其通常应用于面积作为关键参数的设计。SCR 还具有极低的漏电流和电容，为低偏置电流设计带来了额外优势。但是，由于 ESD 单元的保持电压低于  $VDD$ ，因此其具有更高的闩锁风险。当 NPN/PNP 之间存在正反馈时，就会发生闩锁。如果器件中确实发生了闩锁，理想操作是通过上下电防止器件损坏。

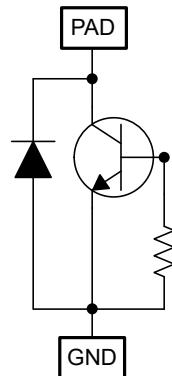

### 3.5 CER 和 ECR NPN 二极管

CER/ECR NPN ESD 保护结构是另一种常见的选择，尤其是对于更高电压而言。该结构的行为类似于快速恢复二极管，即电压在下降回阈值电压之前达到特定电平。[图 3-9](#) 展示了常规布局。

**图 3-9. CER 二极管结构**

该保护结构可提高基极电位以降低 NPN 触发电压。当器件能够承受高触发电压或钳位电压时，首选使用此类保护结构。请注意，一个焊盘通过二极管接地。另一个焊盘则为电压触发。这实现了 ESD 保护，同时占用面积相对较小，但仍大于 SCR 结构。这些结构也存在优势，因为有别于更易发生闩锁的 SCR，此类结构通常视为无闩锁设计。

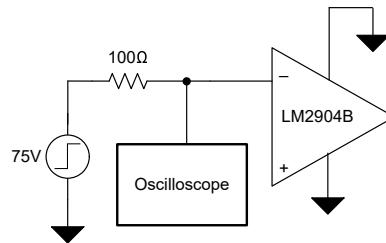

#### 3.5.1 测量 ECR/CER ESD 单元的响应

[图 3-10](#) 展示了用于测量 LM2904B ESD 行为的电路设置。请注意， $100\Omega$  串联限制电阻器是用于确保器件的输入电流不会大于  $10mA$ 。该器件配有一个 ECR ESD 单元，其触发电平约为  $65V$ 。

**图 3-10. LM2904B 二极管测量电路**

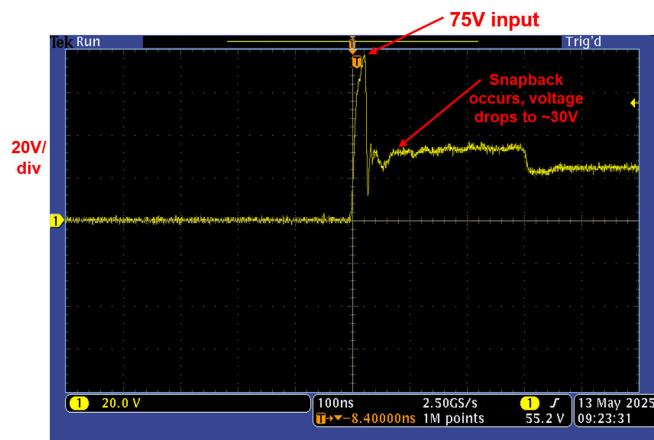

图 3-11 展示了 ESD 单元在时域中的原始测量值。ESD 单元在强制使用 75V 输入后可将电压降至约 30V。

图 3-11. LM2904B 快速恢复测量

### 3.6 ESD 单元对比

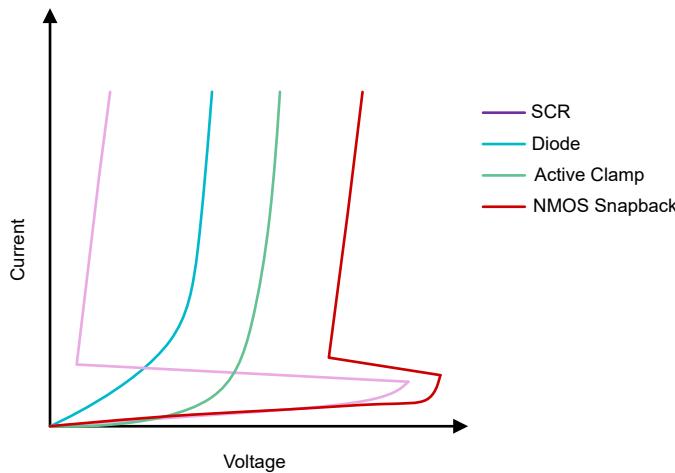

总体而言，在为特定的运算放大器设计 ESD 单元时，需要考虑许多因素。在设计运算放大器时，需考虑权衡每种结构。下文展示了不同类型 ESD 钳位的 IV 曲线，重点介绍了选用正确 ESD 保护结构对应用的重要性。

图 3-12. ESD 钳位对比

## 4 如何根据数据表确定器件的 ESD 结构

如何判断运算放大器的保护类型？ESD 保护有效性于 ESD 等级表的数据表中列明。该规范是通过向所有器件引脚施加仿真 ESD 脉冲，并检查是否出现损坏而制定的。ESD 事件由特殊测试设备生成，其能够产生与现实情况下电荷、电压电平、电感、电阻和电容相同的受控 ESD 脉冲。通常，现实仿真情况是接触低阻抗的人体或带电器件。前一部分提到了这一点。[表 4-1](#) 中规定的 ESD 电压电平反映了在不损坏器件 TLV9141 的情况下可施加的最大 ESD 电压。

**表 4-1. TLV9141 ESD 等级**

| $V_{(ESD)}$ | 静电放电 | 值          | 单位 |

|-------------|------|------------|----|

|             |      | $\pm 4000$ | V  |

|             |      | $\pm 1500$ |    |

(1) JEDEC 文档 JEP155 规定：500V HBM 可实现在标准 ESD 控制流程下安全生产。

(2) JEDEC 文档 JEP157 指出：250V CDM 时能够在标准 ESD 控制流程下安全生产。

有两种方法来判断特定器件是否包含 ESD 保护二极管或采用另一种方法来确保 ESD 稳健性。查看绝对最大额定值表，或在某些情况下，您可以查看标明二极管的功能方框图。在绝对最大额定值表中，当输入电压范围限制在超出电源电压范围约 0.5V 时，器件包含双二极管配置 ESD 二极管（请参阅[表 4-2](#)）。这是由于二极管的正向偏置电压通常约为 0.5V。如果输入信号保持在此范围内，ESD 二极管不会导通。这一保护类型通常还具备  $\pm 10\text{mA}$  的输入电流限值。

**表 4-2. TLV2888 绝对最大额定值（双二极管示例）**

|                     |                             | 最小值                   | 最大值           | 单位 |

|---------------------|-----------------------------|-----------------------|---------------|----|

| $V_S$               | 电源电压， $V_S = (V_+) - (V_-)$ |                       | 26            | V  |

| 输入电压                | 共模                          | $(V_-) - 0.5$         | $(V_+) + 0.5$ | V  |

|                     | 差分                          | $(V_+) - (V_-) + 0.2$ |               |    |

| 输出短路 <sup>(1)</sup> |                             | 持续                    |               |    |

| $T_J$               | 工作结温                        | -40                   | 150           | °C |

| $T_{stg}$           | 贮存温度                        | -65                   | 150           | °C |

(1) 接地短路，每个封装对应一个放大器。

如果器件使用瞬态或电平触发保护，则输入电压范围通常会上升到建议的最大电源电压工作条件。以下使用 LM2904B 数据表对此进行了说明（请参阅[表 4-3](#)）。

**表 4-3. LM2904BQ 绝对最大额定值（电平触发电示例）**

在工作环境温度范围内测得（除非另有说明）<sup>(1)</sup>

|                                                                                                     |      | 最小值  | 最大值 | 单位 |

|-----------------------------------------------------------------------------------------------------|------|------|-----|----|

| 电源电压， $V_S = ([V_+] - [V_-])$                                                                       |      |      | 40  | V  |

| 差分输入电压， $V_{ID}$ <sup>(2)</sup>                                                                     |      | -32  | 32  | V  |

| 输入电压， $V_I$                                                                                         | 任一输入 | -0.3 | 40  | V  |

| 输出对 $V_-$ 短路（一个放大器）的持续时间（在或低于 $T_A = 25^\circ\text{C}$ 、 $V_S \leq 15\text{V}$ <sup>(3)</sup> 的条件下） |      | 无限   |     | s  |

| 工作环境温度， $T_A$                                                                                       |      | -40  | 125 | °C |

| 运行虚拟结温， $T_J$                                                                                       |      |      | 150 | °C |

| 贮存温度， $T_{stg}$                                                                                     |      | -65  | 150 | °C |

(1) 应力超出绝对最大额定值下面列出的值时可能会对器件造成永久损坏。这些列出的值仅仅是应力等级，并不表示器件在这些条件下以及在建议运行条件以外的任何其他条件下能够正常运行。长时间处于绝对最大额定条件下可能会影响器件的可靠性。

(2) 差分电压是相对于 IN- 的 IN+ 上的值。

3) 从输出到电源引脚的短路会导致过热，并且最终会发生损坏。

确定内部 *ESD* 保护方案的另一种简便方法是查看器件功能方框图。数据表通常会提供该图表，而内部二极管通常包含在功能方框图中。这点可见前文的图 3-2 ( OPA928 功能方框图 )。

## 5 如何保护系统免受电路内 ESD/EOS 事件的影响

了解运算放大器的内部保护方案至关重要，因为此类信息可助力整体系统保护方案设计。ESD 二极管专为电路外事件而设计，因此如果要针对各类电路内电气过应力事件 (EOS) 优化系统，则需要额外的设计考量。

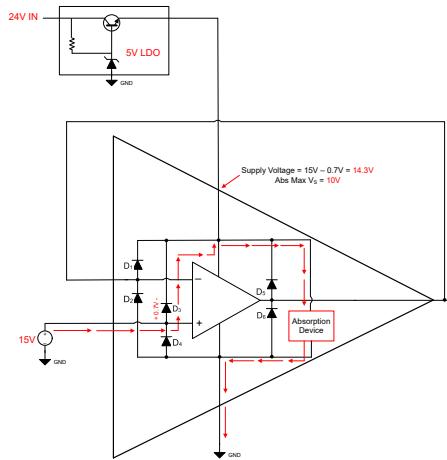

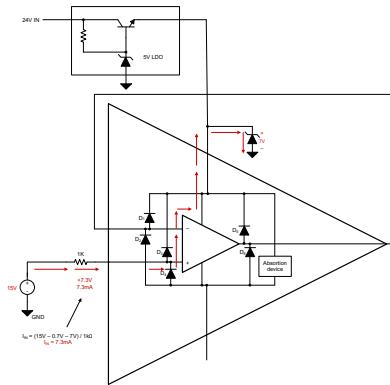

假设采用 图 5-1。该运算放大器通过二极管为保护方案供电，并将 LDO 连接到正电源。运算放大器的最大电源电压为 10V，LDO 可将 24V 调节至 5V。在运算放大器的同相节点上施加 15V 电压。

图 5-1. EOS 事件：过压输入

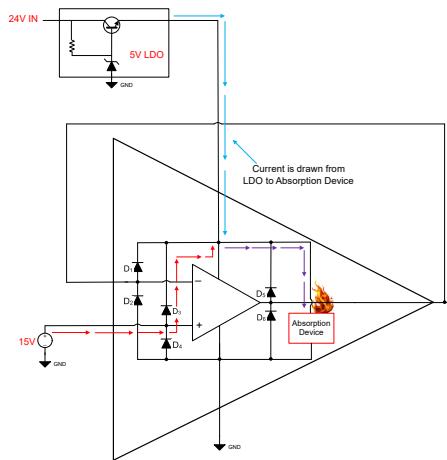

D3 将电压通过器件传导至电源；由于电压高于绝对最大额定值，吸收器件导通。然而供电电压是连续的，因此吸收器件会锁存并保持导通状态，除非电路上下电。当电路导通时，吸收器件从 LDO 汲取大量电流，产生巨量热量，常常导致器件损坏。

图 5-2. EOS 事件 - 吸收器件锁存

如何防止这种情况发生？可采用以下两个简单的步骤。首先是加装输入电阻。然后在电源中加装一个 TVS 二极管。

## 5.1 使用 TVS 二极管和串联电阻实现电路保护

防范 EOS 事件的一种简单方法是在输入端加装一个串联限制电阻器，如 图 5-3 所示。这有助于限制运算放大器在同相节点上测得的电流。所选电阻值应将电流限制为 10mA，并确保电流不会过高，避免电阻器噪声影响电路。

现当施加过应力电压时， $1\text{k}\Omega$  电阻器会限制器件上的电压和电流。电流下降至  $7.3\text{mA}$ ，该值低于大部分数据表的典型  $10\text{mA}$  限值。二极管  $3$  将仍高于最大额定值的电压导引至电源。瞬态电压抑制器 (TVS) 二极管连接到电源，使电源电压限制到  $7\text{V}$ ，吸收器件不会导通。

图 5-3. 采用 TVS 二极管和串联电阻的 EOS 保护

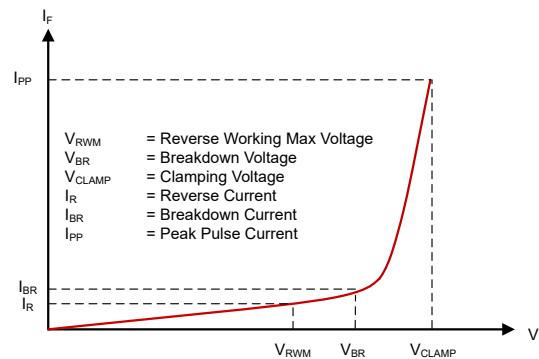

TVS 旨在实现快速导通和大功率耗，因此可选用 TVS 来应对典型 ESD/EOS 事件的大电流和电压浪涌。下图展示了单向 TVS 二极管曲线的 IV 曲线。

图 5-4. 单向 TVS 二极管曲线

选择 TVS 二极管时，了解二极管特性非常重要。 $V_{RWM}$ （最大反向工作电压）是指在漏电流显著增大之前可施加到二极管的最大电压。 $I_R$  是在  $V_{RWM}$  条件下的典型电流。选择 TVS 二极管时，必须确保器件的电源电压等于 TVS 二极管的  $V_{RWM}$ 。由此可显著减少工作期间的漏电流。

峰值脉冲电流对应于 TVS 二极管在发生故障前可应对的最大电流。钳位电压是经受瞬态电流时二极管需要稳压到的电压电平。

击穿电压  $V_{BR}$  是漏电流较高时的电压。所选数值必须小于器件的绝对最大电压。这使得 TVS 二极管能够导通并将电源电压钳位到安全电平，确保电源永远不会达到绝对最大电压。但这并非总是可行，因为有时并无 TVS 二极管在工作电压下具有  $V_{RWM}$ ，且  $V_{BR}$  低于绝对最大额定值。

假设选用 OPA320。此器件的最大工作电源电压为  $5.5\text{V}$ ，绝对最大电压额定值为  $6\text{V}$ 。如果  $V_{RWM}$  设置为  $5.5\text{V}$ ，则 TVS 二极管绝不会在  $6\text{V}$  之前击穿。然而即使外部保护措施并非首选，仍需采取外部保护措施。

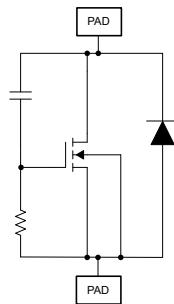

## 5.2 使用肖特基二极管实现电路保护

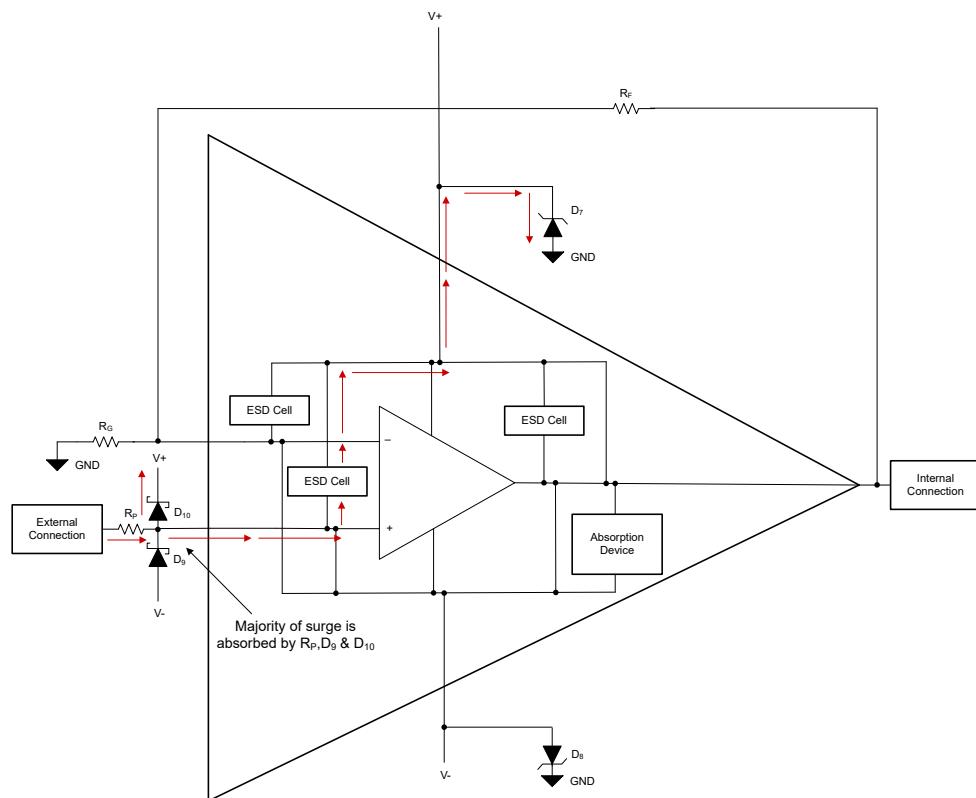

如果运算放大器采用瞬态触发保护方案，则也可能发生 EOS 事件。但是，边沿触发运算放大器的保护方法有别于双二极管保护方案。在边沿触发保护中，ESD 单元仅在特定  $dv/dt$  电平下触发。

在此，肖特基二极管更适合用于保护。肖特基二极管具有高速开关特性，是应对 ESD/EOS 浪涌的首选。由于边沿触发二极管保护结构未设有触发电压，因此肖特基二极管有助于检测浪涌事件，引导绝大部分（若非全部）浪涌电流通过二极管。肖特基二极管具有约 0.3V 的低正向偏置电压。理想情况下，所加装肖特基二极管的正向偏置压降必须低于内部二极管。由此即可让绝大部分 EOS 电流流经外部二极管，从而降低运算放大器损伤概率。

图 5-5 展示了一个同相配置的运算放大器。输入端加装了  $R_p$  以及两个肖特基二极管。通过加装与肖特基二极管串联的  $R_p$ ，即可进一步限制浪涌事件中流经运算放大器的电流。

然而肖特基二极管具有较高的漏电流。因此当该特性成为关键设计要素时，则必须考虑选用其他二极管。在本例中，由于仅有输入侧存在外部连接，因此设计只采用了输入保护。外部连接更容易发生 EOS 事件。这方面的案例包括高感应电压或工厂自动化中常见的长传感器引线。

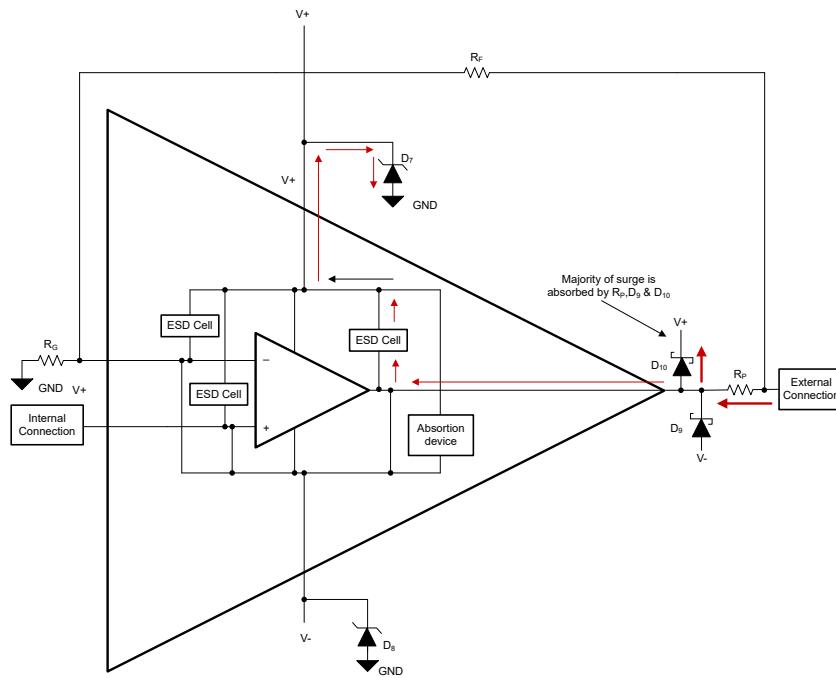

图 5-5. 基于肖特基二极管输入的保护

某些情况下，需要保护运算放大器的输出（请参阅 图 5-6）。下图展示了可供使用的类似电路。在此情况下，选择  $R_p$  时应确保  $R_p$  不会限制运算放大器的输出摆幅。通常，选用 10Ω 到 20Ω 之间的电阻即可实现良好的保护效果和功能。另请注意的是  $R_p$  位于反馈环路内。这样即使  $R_p$  上出现压降，也能保持精确的输出电压。最后需要注意，由于  $R_F$  的值通常远大于  $R_p$ ，因此通过  $R_F$  流向电路输入端的电流极低。

图 5-6. 基于肖特基二极管输出的保护

与所有电路一样，设计也需要权衡取舍。电路引入保护措施也会给系统带来噪声。在设计电路时，应考虑噪声、元件占位面积等因素。但是，这些考虑事项超出了本文的讨论范围。有关如何显著降低噪声的更多详细信息，请参阅[该论文](#)，了解如何在保护运算放大器的同时大幅降低噪声。

## 6 如何在系统级电路中测试运算放大器

诸多系统级设计会在运算放大器断电时进行测试，以确认各元件是否正常工作。在测试运算放大器时，会向输入端施加电压或电流，然后测量电阻。根据具体内部二极管结构，测量结果各不相同。被测电阻是运算放大器内部的 ESD 单元电阻。但在系统级测试期间必须遵循数个关键参数，以确保测量有效，进而保障运算放大器不会在测试中受损。

首先是确保器件未通电。然后将器件的电源接地。图 6-1 展示了运算放大器的有效电路内测试设置。

图 6-1. 电路内测试设置

假设使用以下示例：运算放大器输入端施加电压，同时电源处于悬空状态。由于电源处于悬空状态，因此电压无法到达吸收器件。这可能会导致器件意外上电，从而产生不需要的输出信号，进而影响系统中的其他器件。因此，在系统级测试中验证器件时，最佳实践是将两个电源接地。有关放大器反向供电的更多详细信息，请参阅此[应用手册](#)。

## 6.1 ESD 保护单元发展历程

与各类半导体技术一样，ESD 保护技术数十年来取得了巨大进步。直到 20 世纪 90 年代，ESD 保护才成为运算放大器设计中的标配。因此，20 世纪 70 年代到 80 年代生产的许多器件均未配备 ESD 单元！这些老一代运算放大器采用尺寸更大的器件，因此产品本身就能更可靠地防范 ESD 损坏。但如果 ESD 保护是关键所在，请查看 ESD 规格并确认器件是否符合要求。

部分运算放大器经过多年更新发展，已转为使用革新工艺和技术。在此现代化转型中，产品加装或更改了 ESD 单元。由于拓扑结构发生了变化，二极管结构的固有电阻也各不相同。这可能会导致系统级电路板测试中出现假性故障。

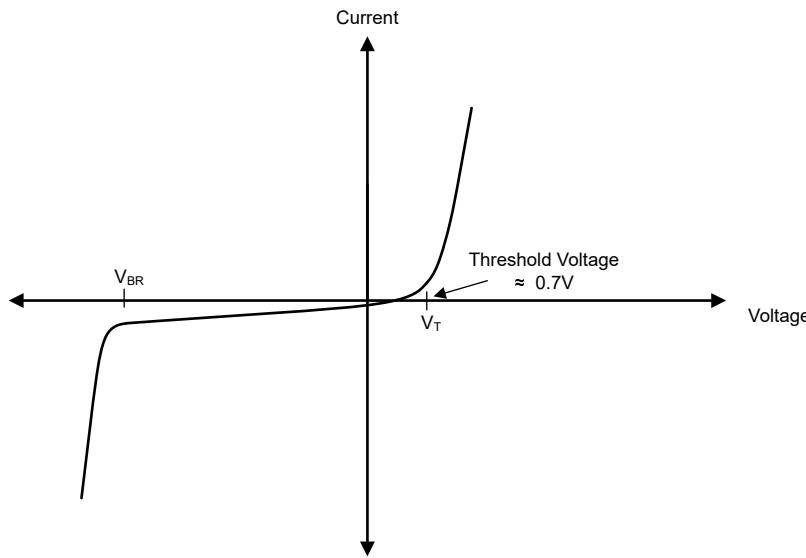

大多数二极管遵循相同的通用 IV 曲线，如下所示。通常情况下，硅二极管的正向偏置电压约为 0.7V。但所有二极管都有所不同，更新 ESD 单元可能会改变运算放大器内 ESD 单元的 IV 曲线特性。

图 6-2. 二极管的 I/V 曲线

OPAx130 系列运算放大器为采用新型 ESD 结构的一个示例。表 6-1 展示了运算放大器与原始 ESD 设计之间的 IV 测量差异以及更新后的设计。在此设置中，引脚强制注入了 100 $\mu$ A 电流，并测量电压。

表 6-1. OPA2130 输入和输出至 VCC 的测量结果

| 引脚至 V+ 电压测量结果       | 引脚 1 至引脚 8 ( OUT A 至 V+ ) | 引脚 2 至引脚 8 (- IN A 至 V+ ) | 引脚 3 至引脚 8 (+IN A 至 V+ ) | 引脚 5 至引脚 8 (+IN B 至 V+ ) | 引脚 6 至引脚 8 (- IN B 至 V+ ) | 引脚 7 至引脚 8 ( OUT B 至 V+ ) |

|---------------------|---------------------------|---------------------------|--------------------------|--------------------------|---------------------------|---------------------------|

| <b>OPA2130 原始设计</b> | 0.609678V                 | 0.699382V                 | 0.668025V                | 0.670190V                | 0.668482V                 | 0.610322V                 |

| <b>OPA2130 重新设计</b> | 0.688358V                 | 0.709175V                 | 0.709203V                | 0.709174V                | 0.709235V                 | 0.688545V                 |

请注意，虽然器件的二极管结构有所变化，但器件行为并未改变。这是因为这些保护结构仅在器件异常运行（例如 ESD）期间触发。

## 7 总结

本应用手册讨论了什么是 ESD，以及如何设计半导体芯片来防范此类事件。设计 ESD 单元时，应考虑面积、触发电压、电容和应用等重要因素。了解器件所用 ESD 单元类型，助力设计单独和系统级保护方案。

## 8 参考资料

- 德州仪器 (TI) , [TIPL ESD/EOS 培训](#) , 视频。

- 德州仪器 (TI) , [运算放大器输入保护会引入噪声](#) , 博客。

- 德州仪器 (TI) , [运算放大器 ESD 保护结构](#) , 应用手册。

- 德州仪器 (TI) , [ESD 钳位](#) , 演示文稿。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025 , 德州仪器 (TI) 公司