# 基于 DS90UB941AS-Q1 和 DS90UB948-Q1 的高可靠车载 视屏传输方案设计要点

Peter Xu

### 摘要

DS90UB941AS-Q1 是一款 MIPI DSI 输入的车规级视频信号串行器,其可最大支持 dual link 210MHz 的视频时钟信号。在 24bit 的色深下,最大能够支持 3K(2880\*1620)30Hz 或者 1080p60Hz 的视频流。同时,它能够支持双 DSI 口输入,dual link 输出两个不同大小的视频流。在使用时,通常将其与解串器配合使用,实现长距离传输视频信号。本文基于目前常用的系统配置,总结了硬件设计以及软件设计的要点。同时总结了在系统调试时常见的问题,并提供了相关的排查 思路和解决措施。

### 目录

| 1    | <b>FPD</b> | )-link 系统简介                | 3  |

|------|------------|----------------------------|----|

| 2    |            | ·设计                        |    |

|      |            | 时钟信号设计                     |    |

|      |            | MODE_SEL PIN 和 IDx PIN 设计  |    |

|      |            | Layout 注意事项                |    |

| 3    | 软件         | ·设计                        | 7  |

|      | 3.1        | 寄存器初始化                     | 7  |

|      | 3.2        | DSI 设置                     | 7  |

| 4    | 问题         | [诊断与调试                     | 8  |

|      | 4.1        | 屏幕端                        | 9  |

|      | 4.2        | 解串器端                       | 9  |

|      | 4.3        | 串行器端                       | 9  |

|      | 4.4        | SoC 端                      | 10 |

| 5    | 参考         | 按太                         | 11 |

| 附件   | 示例         | 代码                         | 12 |

|      | 1 DS       | S90UB941AS-Q1 Pattern 模式代码 | 13 |

|      | 2 DS       | S90UB948-Q1 Pattern 模式代码   | 15 |

|      | 3 DS       | S90UB941AS-Q1 视频传输模式代码     | 16 |

|      |            |                            |    |

|      |            | 图                          |    |

| •    | re 1.      |                            |    |

| Figu | re 2.      |                            |    |

| Figu | ıre 3.     |                            |    |

| Fiau | ire 4.     | . DS90UB941AS-Q1 时钟信号要求    | 4  |

| Figure 5.  | DS90UB941AS-Q1 MODE_SEL0               | 5 |

|------------|----------------------------------------|---|

| Figure 6.  | DS90UB941AS-Q1 MODE_SEL1               |   |

| Figure 7.  | DS90UB948-Q1 MODE_SEL0                 |   |

| Figure 8.  | DS90UB948-Q1 MODE_SEL1                 |   |

|            |                                        |   |

|            | DS90UB941AS-Q1 时钟信号要求                  |   |

|            |                                        |   |

| •          |                                        |   |

| Figure 11. | DS90UB941AS-Q1 时钟信号要求ALP Pattern 模式示意图 | 1 |

## 1 FPD-link 系统简介

FPD-link 协议是一种车载高速视频流传输协议,通过将视频数据从并行数据转换为串行数据,能够实现高速视频流的长距离传输。FPD-link 系统由串行器和解串器组成,在合理配对下,它们能够实现主机到中控屏、仪表屏以及后排屏的长距离视频传输。随着车机系统对视频质量需求的增加,FPD-link 的传输带宽不断提升,对系统的设计以及布线等要求在不断提升,系统对于 FPD-link 器件的稳定性要求也在不断提高。因此,设计出稳定的 FPD-link 系统变得十分重要。

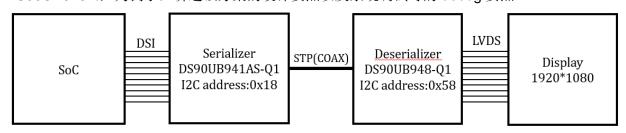

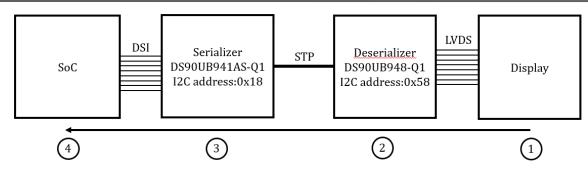

DS90UB941AS-Q1 以及 DS90UB948-Q1 是 TI 第三代 FPD-link 器件,通过合理的配置,它们能够传输 1080P60Hz 的视频流,其系统框图如 Figure 1 所示。本文以 DS90UB941AS-Q1 和 DS90UB948-Q1 为例子,讲述该方案的设计要点以及系统调试时的 debug 要点。

Figure 1. DS90UB941AS-Q1 和 DS90UB948-Q1 系统框图

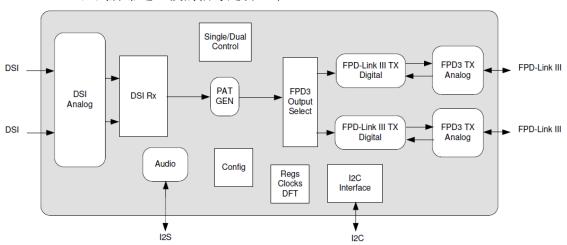

如 Figure 2 所示,为 DS90UB941AS-Q1 的内部框图。在接收到前级传过来的 DSI 信号后,DS90UB941AS-Q1 对其做信号增强处理。再将处理好的信号通过串并行译码器,转化为串行信号,输出到 FPD-Link 端口。为了方便前期调试,DS90UB941AS-Q1 内部有一个 Pattern Generator,无需接收前级 DSI 信号,即可自行发出测试视频信号。通过 Pattern,能够检测 DS90UB941AS-Q1 到屏幕这一段的信号是否正常。

Figure 2. DS90UB941AS-Q1 内部框图

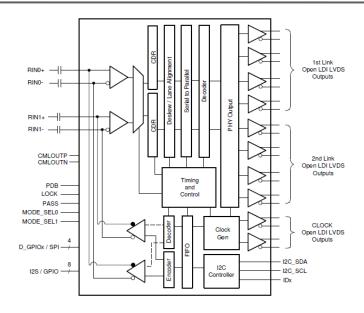

如 Figure 3 所示,为 DS90UB948-Q1 的内部框图。DS90UB948-Q1 接收 DS90UB941AS-Q1 传过来的 FPD-Link 信号。对信号进行相关处理后,通过串并行解码器后输出 OLDI 信号。同样,为了方便前期调试,DS90UB948-Q1 内部有一个 Pattern Generator,无需前级 FPD-link 信号即可自行发出测试视频信号,能够检测 DS90UB948-Q1 到屏幕这一段的信号是否正常。

Figure 3. DS90UB948-Q1 内部框图

## 2 硬件设计

## 2.1时钟信号设计

DS90UB941AS-Q1 以及 DS90UB948-Q1 都要求有稳定的时钟信号输入。 对于串行器 DS90UB941AS-Q1 来说,时钟信号可以来自 SoC,也可以来自晶振。 DS90UB941AS-Q1 对于时钟信号有精准度和误差要求,如 Figure 4 所示。

|                         | PARAMETER                           | TEST CONDITIONS                                                                  | MIN  | TYP               | MAX  | UNIT              |

|-------------------------|-------------------------------------|----------------------------------------------------------------------------------|------|-------------------|------|-------------------|

| f <sub>REFCLK</sub>     | Reference clock frequency           |                                                                                  | 25   | f <sub>PCLK</sub> | 210  | MHz               |

| f <sub>REFCLK_STB</sub> | Reference clock frequency stability | Full temperature range and aging                                                 | -100 |                   | 100  | ppm               |

| t <sub>REFCLK_P</sub>   | Reference clock period              |                                                                                  | 4.76 | Т                 | 40   | ns                |

| t <sub>REFCLK_H</sub>   | Reference clock high time           | f <sub>REFCLK</sub> = f <sub>PCLK</sub> = 25 MHz - 210 MHz                       | 0.4T | 0.5T              | 0.6T | ns                |

| t <sub>REFCLK_L</sub>   | Reference clock low time            |                                                                                  | 0.4T | 0.5T              | 0.6T | ns                |

| t <sub>REFCLK_JIT</sub> | Reference clock jitter              | f <sub>PCLK</sub> / 40 < Jitter frequency < f <sub>PCLK</sub> / 20, TJ@BER<1E-10 |      |                   | 0.28 | UI <sup>(1)</sup> |

Figure 4. DS90UB941AS-Q1 时钟信号要求

如果时钟源是晶振,请注意晶振电路输出的高低电平。当 VDDIO 设置为 3.3V 时,要求时钟信号的高电平大于 2V,低电平小于 0.8V。且占空比应为 40%-60%之间。晶振频率根据视频信号计算,计算公式如下。

$f_{PCLK} = H_{total} \times V_{total} \times frame \ rate$

如果时钟源是 SoC,请咨询 SoC 供应商是否能够提供相关 DSI 信号频率的时钟,且需要 jitter 小于 0.3UI。此时时钟频率和 PCLK 的关系如下公式所示。

$$f_{DSI} = \frac{f_{PCLK} \times N_{DSI\_LANE}}{12}$$

### 2.2MODE SEL PIN 和 IDx PIN 设计

DS90UB941AS-Q1 有 2 个设置运行模式的 PIN,通过设置不同的分压电阻,改变 PIN 的输入电压,从而改变 DS90UB941AS-Q1 的运行模式。在 DS90UB948-Q1 处也会有模式设置的 PIN,DS90UB941AS-Q1 需要与其对应的解串器设置为同样的模式,才能互相识别。如果上电时DS90UB941AS-Q1 和 DS90UB948-Q1 设置为不同的模式,则需要通过修改寄存器的方式将运行模式改正,并对 DS90UB941AS-Q1 和 DS90UB948-Q1 进行软复位的操作,才能互相识别。对于 DS90UB941AS-Q1 MODE\_SEL0,请根据 DSI LANE 数量和是否开启 SPLITTER MODE 去选择 MODE\_SEL0 PIN 对应的模式,找到对应的上拉电阻阻值和下拉电阻阻值。对于 DS90UB941AS-Q1 MODE\_SEL1,请根据 DSI 上电是否默认开启,DS90UB941AS-Q1 和DS90UB948-Q1 之间连接线的类型以及时钟来源选择 MODE\_SEL1 PIN 对应的模式,找到对应的上拉电阻阻值和下拉电阻阻值。在这里,建议选择 DSI 上电默认关闭,连接线类型选择为 STP。对于 DS90UB948-Q1 MODE\_SEL0 和 MODE\_SEL1,请根据屏幕的具体参数和系统设计框架去选择对应的模式。同样建议选择连接线类型为 STP。Figure 5 - Figure 8 为 DS90UB941AS-Q1 和DS90UB948-Q1 的 MODE\_SEL PIN 对应配置表。

| MODE NO. | V <sub>R4</sub> VOLTAGE         |                                 |                                 | V <sub>R4</sub> TARGET<br>VOLTAGE | SUGGESTED STRAP<br>RESISTORS (1% TOL) |                     | - SPLITTER | DSILANES |

|----------|---------------------------------|---------------------------------|---------------------------------|-----------------------------------|---------------------------------------|---------------------|------------|----------|

| MODE NO. | V <sub>MIN</sub>                | V <sub>TYP</sub>                | V <sub>MAX</sub>                | V <sub>(VDD18)</sub> = 1.8        | R <sub>3</sub> (kΩ)                   | R <sub>4</sub> (kΩ) | SPLITTER   | DSILANES |

| 0        | 0                               | 0                               | 0.126 ×<br>V <sub>(VDD18)</sub> | 0                                 | OPEN                                  | 10.0                | 0          | 1        |

| 1        | 0.179 ×<br>V <sub>(VDD18)</sub> | 0.211 ×<br>V <sub>(VDD18)</sub> | 0.244 ×<br>V <sub>(VDD18)</sub> | 0.38                              | 73.2                                  | 20.0                | 0          | 2        |

| 2        | 0.286 ×<br>V <sub>(VDD18)</sub> | 0.325 ×<br>V <sub>(VDD18)</sub> | 0.364 ×<br>V <sub>(VDD18)</sub> | 0.585                             | 60.4                                  | 30.1                | 0          | 3        |

| 3        | 0.404 ×<br>V <sub>(VDD18)</sub> | 0.441 ×<br>V <sub>(VDD18)</sub> | 0.472 ×<br>V <sub>(VDD18)</sub> | 0.794                             | 51.1                                  | 40.2                | 0          | 4        |

| 4        | 0.526 ×<br>V <sub>(VDD18)</sub> | 0.556 ×<br>V <sub>(VDD18)</sub> | 0.590 ×<br>V <sub>(VDD18)</sub> | 1.001                             | 40.2                                  | 51.1                | 1          | 1        |

| 5        | 0.643 ×<br>V <sub>(VDD18)</sub> | 0.673 ×<br>V <sub>(VDD18)</sub> | 0.708 ×<br>V <sub>(VDD18)</sub> | 1.211                             | 30.1                                  | 61.9                | 1          | 2        |

| 6        | 0.763 ×<br>V <sub>(VDD18)</sub> | 0.790 ×<br>V <sub>(VDD18)</sub> | 0.825 ×<br>V <sub>(VDD18)</sub> | 1.421                             | 18.7                                  | 71.5                | 1          | 3        |

| 7        | 0.880 ×<br>V <sub>(VDD18)</sub> | V <sub>(VDD18)</sub>            | V <sub>(VDD18)</sub>            | 1.8                               | 10.0                                  | OPEN                | 1          | 4        |

Figure 5. DS90UB941AS-Q1 MODE\_SEL0

| MODE | V <sub>R6</sub> VOLTAGE         |                                 |                                 | V <sub>R6</sub> TARGET<br>VOLTAGE | ED STRAP<br>S (1% TOL) |                     |   | DISABLE |     |

|------|---------------------------------|---------------------------------|---------------------------------|-----------------------------------|------------------------|---------------------|---|---------|-----|

| NO.  | V <sub>MIN</sub>                | V <sub>TYP</sub>                | V <sub>MAX</sub>                | V <sub>(VDD18)</sub> = 1.8 V      | R <sub>5</sub> (kΩ)    | R <sub>6</sub> (kΩ) |   |         | DSI |

| 0    | 0                               | 0                               | 0.126 ×<br>V <sub>(VDD18)</sub> | 0                                 | OPEN                   | 10.0                | 1 | 0       | 0   |

| 1    | 0.179 ×<br>V <sub>(VDD18)</sub> | 0.211 ×<br>V <sub>(VDD18)</sub> | 0.244 ×<br>V <sub>(VDD18)</sub> | 0.380                             | 73.2                   | 20.0                | 1 | 0       | 1   |

| 2    | 0.286 ×<br>V <sub>(VDD18)</sub> | 0.325 ×<br>V <sub>(VDD18)</sub> | 0.364 ×<br>V <sub>(VDD18)</sub> | 0.585                             | 60.4                   | 30.1                | 1 | 1       | 0   |

| 3    | 0.404 ×<br>V <sub>(VDD18)</sub> | 0.441 ×<br>V <sub>(VDD18)</sub> | 0.472 ×<br>V <sub>(VDD18)</sub> | 0.794                             | 51.1                   | 40.2                | 1 | 1       | 1   |

| 4    | 0.526 ×<br>V <sub>(VDD18)</sub> | 0.556 ×<br>V <sub>(VDD18)</sub> | 0.590 ×<br>V <sub>(VDD18)</sub> | 1.001                             | 40.2                   | 51.1                | 0 | 0       | 0   |

| 5    | 0.643 ×<br>V <sub>(VDD18)</sub> | 0.673 ×<br>V <sub>(VDD18)</sub> | 0.708 ×<br>V <sub>(VDD18)</sub> | 1.211                             | 30.1                   | 61.9                | 0 | 0       | 1   |

| 6    | 0.763 ×<br>V <sub>(VDD18)</sub> | 0.790 ×<br>V <sub>(VDD18)</sub> | 0.825 ×<br>V <sub>(VDD18)</sub> | 1.421                             | 18.7                   | 71.5                | 0 | 1       | 0   |

| 7    | 0.880 ×<br>V <sub>(VDD18)</sub> | V <sub>(VDD18)</sub>            | V <sub>(VDD18)</sub>            | 1.8                               | 10.0                   | OPEN                | 0 | 1       | 1   |

Figure 6. DS90UB941AS-Q1 MODE SEL1

| NO. | V <sub>MODE</sub><br>VOLTAGE | V <sub>MODE</sub><br>TARGET<br>VOLTAGE | ET RESISTORS |         | MAP_SEL | OUTPUT_MOD<br>E [1:0] | OUTPUT MODE        |  |

|-----|------------------------------|----------------------------------------|--------------|---------|---------|-----------------------|--------------------|--|

|     | V (TYP)                      | VDD33 = 3.3 V                          | R1 (kΩ)      | R2 (kΩ) |         |                       |                    |  |

| 0   | 0                            | 0                                      | Open         | 10      | 0       | 00                    | Dual OLDI output   |  |

| 1   | 0.169 x V <sub>(VDD33)</sub> | 0.559                                  | 73.2         | 15      | 0       | 01                    | Dual SWAP output   |  |

| 2   | 0.230 x V <sub>(VDD33)</sub> | 0.757                                  | 66.5         | 20      | 0       | 10                    | Single OLDI output |  |

| 3   | 0.295 x V <sub>(VDD33)</sub> | 0.974                                  | 59           | 24.9    | 0       | 11                    | Replicate          |  |

| 4   | 0.376 x V <sub>(VDD33)</sub> | 1.241                                  | 49.9         | 30.1    | 1       | 00                    | Dual OLDI output   |  |

| 5   | 0.466 x V <sub>(VDD33)</sub> | 1.538                                  | 46.4         | 40.2    | 1       | 01                    | Dual SWAP output   |  |

| 6   | 0.556 x V <sub>(VDD33)</sub> | 1.835                                  | 40.2         | 49.9    | 1       | 10                    | Single OLDI output |  |

| 7   | 0.801 x V <sub>(VDD33)</sub> | 2.642                                  | 18.7         | 75      | 1       | 11                    | Replicate          |  |

Figure 7. DS90UB948-Q1 MODE\_SEL0

| NO. | V <sub>MODE</sub><br>VOLTAGE | V <sub>MODE</sub><br>TARGET<br>VOLTAGE | SUGGESTI<br>RESIS<br>(1% tole | TORS    | REPEATE<br>R | MODE | HIGH-SPEED<br>BACK<br>CHANNEL | INPUT<br>MODE |

|-----|------------------------------|----------------------------------------|-------------------------------|---------|--------------|------|-------------------------------|---------------|

|     | V (TYP)                      | VDD33 = 3.3 V                          | R1 (kΩ)                       | R2 (kΩ) |              |      |                               |               |

| 0   | 0                            | 0                                      | Open                          | 10      | 0            | 00   | 5 Mbps                        | STP           |

| 1   | 0.169 x V <sub>(VDD33)</sub> | 0.559                                  | 73.2                          | 15      | 0            | 01   | 5 Mbps                        | Coax          |

| 2   | 0.230 x V <sub>(VDD33)</sub> | 0.757                                  | 66.5                          | 20      | 0            | 10   | 20 Mbps                       | STP           |

| 3   | 0.295 x V <sub>(VDD33)</sub> | 0.974                                  | 59                            | 24.9    | 0            | 11   | 20 Mbps                       | Coax          |

| 4   | 0.376 x V <sub>(VDD33)</sub> | 1.241                                  | 49.9                          | 30.1    | 1            | 00   | 5 Mbps                        | STP           |

| 5   | 0.466 x V <sub>(VDD33)</sub> | 1.538                                  | 46.4                          | 40.2    | 1            | 01   | 5 Mbps                        | Coax          |

| 6   | 0.556 x V <sub>(VDD33)</sub> | 1.835                                  | 40.2                          | 49.9    | 1            | 10   | 20 Mbps                       | STP           |

| 7   | 0.801 x V <sub>(VDD33)</sub> | 2.642                                  | 18.7                          | 75      | 1            | 11   | 20 Mbps                       | Coax          |

Figure 8. DS90UB948-Q1 MODE\_SEL1

除了 MODE\_SEL PIN 以外,还有 IDx PIN 需要配置。IDx 主要是为了防止 I2C 总线上挂多个设备的时候地址冲突,通过配置 IDx PIN,给 DS90UB941AS-Q1 和 DS90UB948-Q1 配置不同的 I2C 地址。

### 2.3 Layout 注意事项

由于视频信号以及 FPD-link 信号都是高速差分信号,需要做阻抗匹配以及等长处理。

有关 DSI 信号和 FPD-link 差分信号的阻抗匹配,请做 100ohm 的阻抗匹配,并保证其差分线和不同组之间线路等长。如果 FPD-link 走单端信号,请做 50ohm 的阻抗匹配。

为了有更好的 EMI 性能表现,请尽可能将 FPD-Link 器件靠的离连接器近,尽量避免 FPD-Link 信号走线有过多的弯折以及经过过孔。

同时考虑到系统的稳定性,需要在 FPD-link 信号处添加 ESD 保护。推荐 <u>TPD1E01B04-Q1</u>作为 FPD-link 信号的 ESD 保护器件。为获得更好的保护效果,建议将 ESD 保护器件尽可能靠得离 FPD-link 连接器近。

如果使用外置晶振作为时钟源,请尽可能使得外置晶振离 DS90UB941AS-Q1 近,防止走线对时钟信号进行干扰。

## 3 软件设计

### 3.1 寄存器初始化

当器件上电以后,请检查 datasheet 中标了"STRAP"的寄存器是否与 MODE\_SEL PIN 选择的模式相同。在 DS90UB941AS-Q1 中,需要检查 Main Page 0x0、0x1、0x13、0x4F、0x55、0x5B。在 DS90UB948-Q1 中,需要检查 Main Page 0x0、0x23、0x49。如果不相同,有可能影响上电时序和系统稳定性。此时应检查 MODE\_SEL PIN 中对应的电压和上下拉电阻是否符合要求。在确定器件工作正常以后,请根据系统配置修改对应的配置寄存器。具体可以参考下方的示例代码。

除了视频传输,DS90UB941AS-Q1 和 DS90UB948-Q1 都分别有 4 个 GPIO,可以与各自的上下级器件连接。通过寄存器配置,可以让 DS90UB948-Q1 的 GPIO 口状态完全跟随 DS90UB941AS-Q1 对应 GPIO 口的状态,实现前向透传的功能,从而让 SoC 控制 DS90UB948-Q1 板上的背光驱动等其它器件。具体设置方法如下:

{0x18, 0x0E, 0x30}, V\*941 I2C 地址 0X18,对寄存器 0X0E 写入值 0X30,下列命令格式相同\*/\{0x58, 0x1E, 0x50}, V\*948 I2C 地址 0X58 \*/\

或者也可以让 DS90UB941AS-Q1 的 GPIO 口状态完全跟随 DS90UB948-Q1 对应 GPIO 口的状态,让 SoC 接收 DS90UB948-Q1 板上的一些反馈信号。具体设置方法如下:

{0x18, 0x0E, 0x50}, V\*941 I2C 地址 0X18 \*/\

{0x58, 0x1E, 0x30}, V\*948 I2C 地址 0X58 \*/\

需要注意的是, DS90UB941AS-Q1 和 DS90UB948-Q1 的 GPIO 是一一对应的。例如, DS90UB941AS-Q1 的 GPIO2 只能和 DS90UB948-Q1 的 GPIO2 实现透传功能。如果 DS90UB941AS-Q1 只有 PORT0 被使用, 那么 PORT0 对应的是 GPIO[0:3]。

如果 DS90UB941AS-Q1 有两个 PORT 被使用,那么 PORT0 对应的是 GPIO[0:3],PORT1 对应的是 D GPIO[0:3]

### 3.2DSI 设置

### 3.2.1 连续时钟设置

当使用 SoC 作为时钟源时,DS90UB941AS-Q1 要求前级 SoC 发送连续的时钟信号。如果把 DSI 时钟作为系统时钟,SoC 发送不连续的时钟信号,可能会导致屏幕黑屏,周期性掉 LOCK 或周期性抖屏。在 DS90UB941AS-Q1 中,可以通过 MODE\_SEL1 PIN 设置接收的时钟信号类型,也可以通过 BRIDGE\_CTL 寄存器 bit7 去改变时钟信号类型。

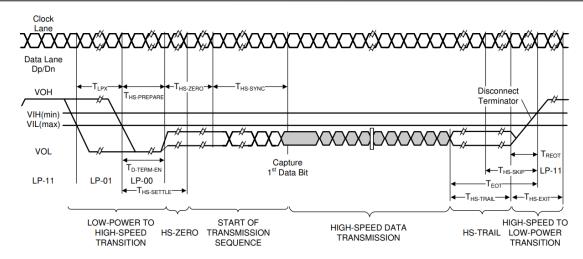

#### 3.2.2 LP-11 设置

DS90UB941AS-Q1 要求前级 SoC 在每一帧的结尾发送 LP-11 信号。如果没有 LP-11 信号,可能导致屏幕黑屏。如 Figure 9 右侧,是 LP-11 的波形。读取 DSI\_VC\_DTYPE 寄存器 bit[5:0],如果读数为 0,有可能是前级 SoC 没有发送 LP-11 信号。此时需要检查 SoC 中有关 LP-11 的配置。

Figure 9. DSI LP-11 波形

### 3.2.3 DSI packet timing 设置

DS90UB941AS-Q1 要求前级 SoC 发送符合 MIPI 要求的 DSI packet。如果 SoC 发送的是错误的 packet,可能导致屏幕黑屏/抖屏/上下翻转/左右翻转。该项可以通过专门的 MIPI 分析仪去解析 SoC 发送的信号。

### 3.2.4 T<sub>skip</sub> 设置

DS90UB941AS-Q1 要求根据下列公式计算  $T_{skip}$ 。如果  $T_{skip}$ 设置不对,可能导致屏幕抖屏。  $T_{SKIP\_CNT} = Round(65 \times f_{DSI} - 5)$

### 3.2.5 DSI Event Mode/Burst Mode 设置

请查询 SoC DSI 的输出模式,并对应设置 DS90UB941AS-Q1 的寄存器。如果 SoC 的输出模式为 Non Burst Mode,请将 DSI\_SYNC\_PULSES 设置为 1;如果 SoC 的输出模式为 Event Mode或者 Burst Mode,请将 DSI\_SYNC\_PULSES设置为 0,并根据视频 timing设置 DSI\_HSW\_CFG\_HI、 DSI\_HSW\_CFG\_LO、 DSI\_VSW\_CFG\_HI、 DSI\_VSW\_CFG\_LO 这四个寄存器。如果设置有误,可能会导致屏幕黑屏/抖屏/显示内容上下翻转。

## 4 问题诊断与调试

在系统调试中,有时会遇到一些不常见的问题,如不规律的抖屏和黑屏,在低温时出现显示问题等等。此时应按照从屏端到 SoC 的顺序来排查问题,如 Figure 10 所示。下面按照图中的顺序讲述调试思路。

Figure 10. DS90UB941AS-Q1 时钟信号要求

## 4.1 屏幕端

在系统出现异常的时候,通常能够在屏幕端见到异常画面。在保证测试条件一致的情况下,可以通过屏幕模组中的 Timing Controller(TCON)生成 Timing,做屏幕自身的检测实验。如果是屏幕模组有问题,此时可以看到异常画面。通过 ABA 交换屏幕的实验,即可排查出是否为屏幕的问题。

### 4.2解串器端

从屏幕到解串器,中间可能会有软排线以及其他的 Timing 修正芯片。在排查问题时,可以通过更换软排线以及禁用 Timing 修正芯片来去除它们的影响。

对于解串器本身的调试,请使用 Pattern 做对应的测试。上文 3.3 有对应的示例代码,或者也可以通过 ALP 生成对应的 Pattern。通过修改 0X65 寄存器 BIT3,可以改变时钟信号来源。通过不同信号时钟来源下的 Pattern 模式,对比屏幕画面结果,可以缩小问题范围。

如果不同时钟来源下的 Pattern 模式都有出现画面抖动或异常问题,问题应该集中在 948 输出端到屏幕输入端。可以排查 PCB 板的 LVDS 走线是否符合规范,是否有阻抗匹配或者电磁干扰等问题。Mode Sel Pin 是否配置正确,解串器上电是否符合时序要求。

如果只是外部 clock 的 Pattern 模式下出现问题,证明前级的 clock 信号不符合要求。应该在串行器端或者 SoC 端检查 clock。该问题在 SoC 端集中讨论。

如果不同模式下的 Pattern 模式都没有问题,说明解串器端到屏幕端能够正常运行,没有问题。

### 4.3 串行器端

对于串行器本身的调试,和解串器相似,请使用 Pattern 做对应的测试。下文附件中有对应的示例代码,或者也可以通过 ALP 生成对应的 Pattern。串行器端可以调整 Timing 来源和 Clock 来源,形成 3 种组合:串行器内部 Timing+串行器内部 Clock;外部 Timing+串行器内部 Clock;内部 Timing+外部 Clock。

通过不同的组合测试,可以看到具体是外部 Timing 和外部 Clock 的问题点。如果外部的 Timing/Clock 有问题,表明 SoC 端发送过来的 Timing/Clock 不符合串行器要求。该问题在 SoC 端集中讨论。

如果串行器内部 Timing+串行器内部 Clock 的组合也会出现异常问题,则问题集中在串行器端或者串行器和解串器的连接处。对于连接处的排查,需要注意连接器和 FPD-link 双绞线(同轴线)是否正常。此类器件的问题可以通过更换新线或交叉测试等实验进行排查。同时,FPD-Llink 线的长度受到插损/回损的限制。请注意线的长度不要超过限制值。针对串行器本身的排查,硬件上需要注意串行器输出端的走线是否有做等长和阻抗匹配处理,Mode\_Sel Pin 是否正确配置。在寄存器上可以查看串行器的运行状态,通过检查 STS 寄存器查看器件的工作状态。

如果不同模式下的 Pattern 模式都没有问题,说明串行器端到屏幕端能够正常运行,没有问题。

### 4.4SoC 端

如果串行器端到屏幕端的所有调试都做完了,而 SoC 的视频传输仍然有问题,此时问题锁定在 SoC 的视频输出或者 SoC 到串行器的链路问题。请根据以下步骤排查问题。

- 1. 需要先核对 SoC 和串行器的 DSI 设置配对问题,详情查看第 3.2 章节。

- 2. 如果 DSI Clock 来源是 SoC, 请查看 SoC 的数据手册并实测 Pin 59&60 的时钟信号, 串行器 对 SoC 端发过来的时钟有 jitter 要求。如果 DSI Clock 来源是晶振, 请查看晶振的数据手册并 实测 Pin 41 的时钟信号, 串行器对晶振发过来的时钟信号有 jitter, PPM, 高低电平值和占空 比要求。具体可以查看第 2.1 章节。

- 3. 如果 DSI 设置相互匹配,时钟信号实测满足要求,检查后视频显示仍然有问题,请查看 DSI 输 出时串行器的 STS 寄存器状态。通过查看 0x0C, 0x1F, 0x5A 寄存器可以知道串行器的状态 (如果是 Dual Port 的配置下,需要对 0x1E 写 0x02 以查看 Port1 的值)。

在正常的显示情况下,寄存器 0x0C 的值为 0x05。当出现异常情况导致 0x0C 的值不为 0x05,可以参考以下的问题分析。正常情况下 bit6 和 bit5 都是 0,若实际读数为 1,请根据第 3.2 章节检查 DSI 设置配对问题。正常情况下 bit4 LINK\_LOST 是 0,若实际读数为 1,请检查物理线束是否连接牢固,可以通过更换线束和连接器来排查问题。正常情况下 bit2 PCLK\_DETECT 是 1,若实际读数为 0,表明串行器没有读到稳定的时钟信号。请检查 0x4F bit7,0x56 bit[1:0]是否配置正确。硬件上需要排查时钟信号走线是否过长,可能晶振或 SoC 端的输出能够满足要求,但是信号传输到串行器 PIN 脚上会有衰减。正常情况下 bit1 DES\_ERROR 是 0,若实际读数为 1,可能是上电时没有自动清除信号,可以通过置位 0x04 bit5 来清除该信号。如果该位在清除后仍然为 1,表明解串器端持续接收到错误信号,此时需要排查连接器和线是否正常连接,以及解串器是否正常上电连接。正常情况下 bit0 LINK\_DETECT 是 1,若实际读数为 0,表明物理线连接无法识别。请检查物理线束是否连接牢固,可以通过更换线束和连接器来排查问题。

在正常的显示情况下,寄存器 0x1F 的值是一个不为 0 的值。当读数稳定为 0,表明串行器没有读到稳定的时钟信号。请检查 0x4F bit7, 0x56 bit[1:0]是否配置正确。

在正常的显示情况下,寄存器 0x5A 的值是 0xD9(Dual Port 的情况下是 0XC9)。0x5A 的读数值可以和 0x0C 寄存器相互对照,主要的区别是在 Dual Port 的配置下,可以通过配置 0x1E 寄存器和读 0x5A 寄存器,看具体是哪个 Port 出问题。

4. 时序问题:通常串行器和解串器的单独时序都能够被满足,但是互相之间的上电时序容易被 忽略。解串器需要等串行器有稳定的输出以后才可以拉高 PDB。

5. MAP\_SEL 问题:在解串器端有 MAP\_SEL 配置,不同的配置对应不同的 RGB 传输格式,屏幕数据手册中会写支持 OLDI/SPWG/VESA 格式或者是 JEIDA 格式。需要根据屏幕格式配置解串器。该问题会影响屏幕的颜色传输,因此在 Pattern mode 测试时看不出来。如果在视频传输时,屏幕画面稳定,但画面的整体颜色都有偏差,则很有可能是 MAP\_SEL 问题。解决方法是修改解串器 MODE\_SEL Pin 对应的电阻或者修改解串器 0x49 寄存器 bit[6:5]。

## 5 参考文献

- 1. DS90UB941AS-Q1 DSI to FPD-Link III Bridge Serializer datasheet (Rev. C)

- 2. DS90UB941AS-Q1 DSI Bringup Guide

- 3. Exploring the Int Test Pattern Generation Feature of FPD-Link III IVI Devices (Rev. G)

- 4. DS90UH941AS-Q1EVM User's Guide (Rev. A)

## 附件 示例代码

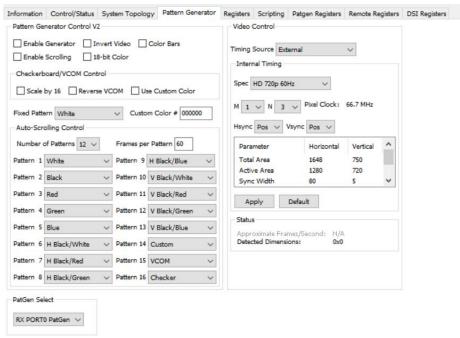

为方便调试,给出一个常用系统设置,并针对其给出 pattern 模式代码和视频传输模式代码。Pattern 模式有两种测试方法: 1. 将 FPD-link 器件的 I2C 接到 USB2ANY 设备上,使用 FPD-link 对应的驱动软件 ALP,在 ALP 中将对应的 timing 填好,使能 Pattern 模式,具体如 Figure 11 所示。2. 直接对寄存器写对应的 timing 值并在寄存器中使能 Pattern 模式。下面给出对应 720P 视频的 pattern 模式示例代码。在实际使用中,请根据对应的视频 timing 值以及系统配置修改对应的寄存器值。

Figure 11. ALP Pattern 模式示意图

### 系统配置:

720P 视频, 具体 timing 值如下图所示。

|           | •           | · - · · · · · · · · · · · · · · · · · · |             |

|-----------|-------------|-----------------------------------------|-------------|

| Parameter | Min(Pixels) | Typical(Pixels)                         | Max(Pixels) |

| Hactive   | 1920        | 1920                                    | 1920        |

| HBP       | 32          | 40                                      | 48          |

| HFP       | 20          | 20                                      | 20          |

| Hsync     | 12          | 12                                      | 12          |

| Htotal    | 1984        | 1992                                    | 2000        |

| Vactive   | 720         | 720                                     | 720         |

| VBP       | 20          | 20                                      | 20          |

表 3 720P 视频 timing 值

| VFP    | 12  | 12  | 12  |

|--------|-----|-----|-----|

| Vsync  | 4   | 4   | 4   |

| Vtotal | 756 | 756 | 756 |

### 系统框图:

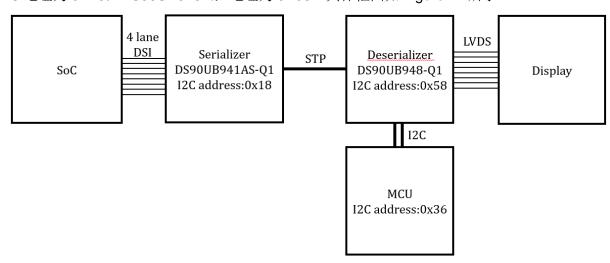

串行器为 DS90UB941AS-Q1,解串器为 DS90UB948-Q1,单 port 传输。DS90UB941AS-Q1 的 I2C 地址为 0X18, DS90UB948-Q1 地址为 0X58。具体框图如 Figure 12 所示。

Figure 12. 系统框图

### 1 DS90UB941AS-Q1 Pattern 模式代码

/\*\* DS90UB941A-PORT0 Configuration \*/ \

{0x18, 0x01, 0x02}, V\* 串行器 I2C 地址 0x18, 对寄存器 0x01 写入值 0x02, 下列命令格式相同\*/\

{0x18, 0x01, 0x08}, V\* disable DS90UB941AS-Q1 DSI\*/\

{0x18, 0x1E, 0x01}, V\* choose PORT0\*/\

{0x18, 0x06, 0x58}, V\* write DES I2C address\*/\

{0x18, 0x07, 0x36}, V\* write DES MCU I2C\*/\

{0x18, 0x08, 0x36}, V\* write DES MCU I2C alias\*/\

{0x18, 0x70, 0x58}, V\* write DES I2C address\*/\

{0x18, 0x77, 0x58}, V\* write DES I2C address alias\*/ \

/\* Device Configuration \*/ \

{0x18, 0x1E, 0x01}, V\* choose PORT0\*/\

{0x18, 0x03, 0xDA}, V\* 使能 I2C 透传 \*/\

{0x18, 0x4F, 0x8C}, V\* 配置 DSI 连续时钟, 4 DSI lanes\*/\

{0x18, 0x5B, 0x00}, V\* 配置为 STP cable, 自动 TX 模式\*/\

{0x18, 0x40, 0x08}, V\* 写入间接寄存器 DSI port0 表\*/\

{0x18, 0x41, 0x05}, V\* 间接寄存器地址为 0x05\*/\

{0x18, 0x42, 0x18}, V\* 间接寄存器写入值 0x18, 是 TSKIP 的写入值\*/\

#### /\* PATTERN MODE\*/ \

{0x18, 0x64, 0x00}, V\* RESET\*/\

{0x18, 0x66, 0x1A}, V\* CLOCK DIVIDER M,请根据实际的 PCLK 调整 0x1A 和 0x03 寄存器的值。示例中 PCLK = 1992\*756\*24 = 36.142MHz. 在 M 不为 1 的情况下,PCLK= 800\*M/N;在 M 为 1 的情况下,PCLK= 200/N,计算得到比较合适的组合:M=2,N=44\*/\

{0x18, 0x67, 0x02}, V\* CLOCK DIVIDER M\*/\

{0x18, 0x66, 0x03}, V\* CLOCK DIVIDER N\*/\

{0x18, 0x66, 0x04}, V\* Htotal\*/\

{0x18, 0x67, 0xC8}, V\* Htotal\*/\

{0x18, 0x66, 0x05}, V\* Htotal&Vtotal \*/\

{0x18, 0x67, 0x47}, V\* Htotal&Vtotal\*/\

{0x18, 0x66, 0x06}, V\* Vtotal \*/\

{0x18, 0x67, 0x2F}, V\* Vtotal\*/\

{0x18, 0x66, 0x07}, V\* Hactive&Vactive\*/ \

{0x18, 0x67, 0x80}, V\* Hactive&Vactive \*/\

{0x18, 0x66, 0x08}, V\* Hactive&Vactive \*/ \

{0x18, 0x67, 0x07}, V\* Hactive&Vactive \*/ \

{0x18, 0x66, 0x09}, V\* Hactive&Vactive \*/ \

{0x18, 0x67, 0x2D}, V\* Hactive&Vactive \*/\

{0x18, 0x66, 0x0A}, V\* HSYNC \*/\

{0x18, 0x67, 0x0C}, \/\* HSYNC\*/\

{0x18, 0x66, 0x0B}, V\* VSYNC \*/\

```

{0x18, 0x67, 0x04}, V* VSYNC*/\

{0x18, 0x66, 0x0C}, V* HBP */\

{0x18, 0x67, 0x28}, V* HBP */\

{0x18, 0x66, 0x0D}, V* VBP */\

{0x18, 0x67, 0x14}, V* VBP*/\

{0x18, 0x66, 0x0E}, V* Polarity */\

{0x18, 0x67, 0x03}, V* Polarity*/\

{0x18, 0x65, 0x04}, V* clock source & timing source */

{0x18, 0x64, 0x95}, V* enable PATTERN MODE*/\

```

## 2 DS90UB948-Q1 Pattern 模式代码

{0x58, 0x66, 0x09}, V\* Hactive&Vactive \*/ \

```

{0x58, 0x01, 0x01}, V* RESET*/\

/* PATTERN MODE*/\

{0x58, 0x64, 0x00}, V* RESET*/\

{0x58, 0x66, 0x1A}, V* CLOCK DIVIDER M, 948 只能为 1 且无法调整。948 的 CLK 为 140MHz*/\

{0x58, 0x67, 0x01}, V* CLOCK DIVIDER M*/\

{0x58, 0x66, 0x03}, V* CLOCK DIVIDER N*/\

{0x58, 0x67, 0x04}, V* CLOCK DIVIDER N,设置为 4*/\

{0x58, 0x66, 0x04}, V* Htotal */\

{0x58, 0x67, 0xC8}, V* Htotal*/\

{0x58, 0x66, 0x05}, V* Htotal&Vtotal */\

{0x58, 0x67, 0x47}, \/* Htotal&Vtotal*/\

{0x58, 0x66, 0x06}, V* Vtotal */\

{0x58, 0x67, 0x2F}, V* Vtotal*/\

{0x58, 0x66, 0x07}, \text{\* Hactive&Vactive*/\}

{0x58, 0x67, 0x80}, V* Hactive&Vactive */ \

{0x58, 0x66, 0x08}, V* Hactive&Vactive */ \

{0x58, 0x67, 0x07}, V* Hactive&Vactive */ \

```

```

{0x58, 0x67, 0x2D}, \/* Hactive&Vactive */\

{0x58, 0x66, 0x0A}, \/* HSYNC */\

{0x58, 0x67, 0x0C}, \/* HSYNC*/\

{0x58, 0x66, 0x0B}, \/* VSYNC */\

{0x58, 0x67, 0x04}, \/* VSYNC*/\

{0x58, 0x66, 0x0C}, \/* HBP */\

{0x58, 0x67, 0x28}, \/* HBP */\

{0x58, 0x66, 0x0D}, \/* VBP */\

{0x58, 0x67, 0x14}, \/* VBP*/\

{0x58, 0x66, 0x0E}, \/* Polarity */\

{0x58, 0x67, 0x03}, \/* Polarity*/\

{0x58, 0x65, 0x04}, \/* clock source & timing source */

{0x58, 0x64, 0x95}, \/* enable PATTERN MODE*/\

```

## 3 DS90UB941AS-Q1 视频传输模式代码

```

{0x18, 0x01, 0x02}, \

{0x18, 0x01, 0x08}, V* disable DS90UB941AS-Q1 DSI*/\

{0x18, 0x1E, 0x01}, V* choose PORT0*/\

{0x18, 0x06, 0x58}, V* DES I2C address*/\

{0x18, 0x07, 0x36}, V* DES MCU I2C*/\

{0x18, 0x08, 0x36}, V* DES MCU I2C*/\

{0x18, 0x70, 0x58}, V* DES I2C address*/\

{0x18, 0x77, 0x58}, V* DES I2C address*/\

{0x18, 0x77, 0x58}, V* DES I2C address*/\

/* Device Configuration */\

{0x18, 0x1E, 0x01}, V* choose PORT0, 在 dual port 运行模式下,应该要使 0x1E = 0x02,选择PORT1 并再次配置这部分代码。*/\

{0x18, 0x04, 0x10}, \

{0x18, 0x03, 0xDA}, \

{0x18, 0x04F, 0x8C}, V* 根据实际需求配置*/\

```

{0x18, 0x5B, 0x00}, V\* 根据实际需求配置\*/\

{0x18, 0x40, 0x08}, \

$\{0x18, 0x41, 0x05\}, \$

{0x18, 0x42, 0x18}, V\* TSKIP, 根据实际需求配置\*/\

/\* enable DS90UB941AS-Q1 DSI\*/\

{0x18, 0x01, 0x00}

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司