# Application Note

# MSPMO ADC 噪声分析和应用

#### 摘要

本文档提供模数转换器 (ADC) 噪声分析,并介绍了 MSPM0 MCU 的 ADC 应用。

# 内容

| 1 ADC 简介                              | 2  |

|---------------------------------------|----|

| 1.1 SAR ADC 工作原理                      | 2  |

| 1.2 ADC 参数                            | 2  |

| 2 ADC 噪声分析                            | 5  |

| 2.1 ADC 噪声分类                          | 5  |

| 2.2 如何降低噪声                            | 8  |

| 3 ADC 过采样                             | 10 |

| 3.1 采样速率                              | 10 |

| 3.2 提取法                               | 10 |

| 3.3 应用条件                              |    |

| 4 基于 MSPM0 的 ADC 应用                   | 11 |

| 4.1 MSPM0 的 ADC 配置                    |    |

| 4.2 基于 MSPM0G3507 ADC EVM 板的 ADC 直流测试 |    |

| 5 修订历史记录                              | 16 |

|                                       |    |

| 插图清单                                  |    |

| 图 1-1. 基于 CDAC 的 SAR ADC 原理方框图        | 2  |

| 图 1-2. ADC 交流测试示意图                    | 3  |

| 图 1-3. ADC 直流测试示意图                    | 4  |

| 图 2-1. ADC 噪声源示意图                     |    |

| 图 2-2. 具有不同分辨率的 ADC 的量化噪声和热噪声         | 7  |

| 图 4-1. ADC 时钟的 Sysconfig 配置           | 11 |

| 图 4-2. ADC 采样模式的 SysConfig 配置         |    |

| 图 4-3. ADC 转换存储器的 SysConfig 配置        | 12 |

| 图 4-4. MSPM0G3507 ADC EVM             |    |

| 图 4-5. ADC 直流测试软件配置                   | 15 |

|                                       |    |

| 表格清单                                  |    |

| 表 2-1. 不同 ADC 基准电压的优缺点                | 8  |

| 表 4-1. 测试结果                           | 16 |

| 商标                                    |    |

| POW                                   |    |

所有商标均为其各自所有者的财产。

#### 1 ADC 简介

#### 1.1 SAR ADC 工作原理

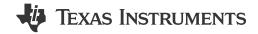

图 1-1 展示了 SAR ADC 的系统原理图。SAR ADC 通过控制多个开关(本例中为 12 个开关)的切换,对基准电压 (VREF) 进行电容分压,从而获得不同的模拟电压输出结果。将模拟电压与输入采样信号进行比较,而比较器的输出用于调整开关的开/关状态,最终使通过 VREF 分压获得的模拟电压尽可能接近输入电压。实际的比较过程是通过使用二进制逼近法将 VREF 分压值逼近 VIN,因此需要 12 个时钟周期完成一次数据转换。考虑到 ADC 的触发、信号采样和保持时间,实际的 SAR ADC 转换过程耗时多于 12 个周期(在 MSPM0 G 系列中为 14 个转换周期)。

图 1-1. 基于 CDAC 的 SAR ADC 原理方框图

#### 1.2 ADC 参数

#### 1.2.1 静态参数

• 微分非线性 (DNL) 误差

微分非线性误差指 ADC 模数转换过程中实际步长与理想步长之间的最大偏差,其中理想步长指的是 1LSB。若 DNL 超过 1LSB,则会在 ADC 数字输出中产生缺码,即某些数字码值将在输出结果中消失。

$$DNL = Actual Step - 1LSB$$

(1)

• 积分非线性 (INL) 误差

积分非线性误差指 ADC 转换过程中某一转换电压与理想转换电压之间的偏差,反映了 DNL 的累积效果。该值的测量是在补偿了失调电压误差和增益误差后进行的。通过测量每个数字代码的转换电压,可以获得各个代码点的 INL 值。ADC 数据手册中仅提供了最大 INL 值。

INL = the kth actual conversion voltage –

$$(k - 0.5)$$

LSB (2)

www.ti.com.cn ADC 简介

#### • 失调电压误差 (EO)

失调电压误差指 ADC 从低电压开始增加时,首个实际转换电压与首个理想转换电压之间的偏差。当 ADC 数字输出从 0 变为 1 时,发生第一次转换。对于理想 ADC,当模拟输入介于 0.5LSB 和 1.5LSB 之间时,数字输出应为 1,因此第一次理想转换发生在 0.5LSB。失调电压误差计算公式如下:

$$EO = the first actual conversion voltage - 0.5LSB$$

(3)

#### • 增益误差 (EG)

增益误差指最后一个实际转换电压和最后一个理想转换电压之间的偏差,此值在校正失调电压误差后测量。以 12 位 ADC 为例,当输出数字结果从 0xFFE 变为 0xFFF 时发生最后一次实际转换,对应电压为 *VREF+* - 0.5LSB。因此,增益误差的计算公式为:

$$EG = the last actual conversion voltage - (VREF_{+} - 0.5LSB)$$

(4)

#### 1.2.2 动态参数

#### 1.2.2.1 交流参数

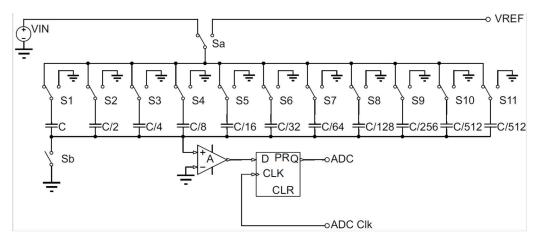

测量条件:在 ADC 的正负端子之间输入一个正弦交流电压,观察 ADC 的采样输出结果。通过对输出信号进行傅里叶变换的频谱分析,可以得到信号的基波、谐波以及噪声分量,从而计算 ADC 的动态交流参数。

图 1-2. ADC 交流测试示意图

#### • 总谐波失真 (THD)

总谐波失真指交流信号中所有谐波分量的总功率与基频信号功率的比值,其计算公式如下(分贝形式):

$$THD = 20log_{10} \left( \frac{\sum V_{\text{Harmonics}}}{V_{\text{Signal}(RMS)}} \right) \left( dB \right)$$

(5)

在 ADC 通信参数测量实验中,*THD* 由 ADC 传输特性曲线的非线性引起,即在采样范围内,ADC 的输出与输入不完全呈线性关系(由 ADC 的静态误差如 *DNL/INL/E O/E G* 引起),导致输出信号中出现谐波。通常在计算时选择 2 至 10 次谐波。

#### • 信噪比 (SNR)

信噪比指信号的有效值与噪声的有效值之间的比值。此处提到的噪声是 ADC 量化噪声、1/f 噪声等高频噪声,不包括谐波分量(这些谐波分量在 *THD* 计算中已计入)。信噪比的计算公式如下所示。

$$SNR = 20log_{10} \left( \frac{V_{Signal(RMS)}}{V_{Noise(RMS)}} \right) \left( dB \right)$$

(6)

# • 信噪比和失真 (SINAD)

信号失真通常由 ADC 内部误差引起,SINAD 用于衡量信号与谐波和噪声总和的比值,表示有效信号在 ADC 输出中所占的比例。

$$SINAD = 20log_{10} \left( \frac{v_{Signal(RMS)}}{\Sigma(v_{Harmonics}) + v_{Noise(RMS)})} \right) (dB)$$

(7)

#### • 有效位数 (ENOB)

ENOB 表示 ADC 的有效位数,代表 ADC 的实际分辨率及其识别小幅度信号的能力,可以通过 SINAD 直接计算得出。

上面的公式提供了当输入信号达到 ADC 最大范围时的 *ENOB* 计算方法。当输入信号小于最大范围时,*ENOB* 的计算公式相应调整为:

$$ENOB = \frac{SINAD_{MEASURED} - 1.76dB + 20log_{10} \left( \frac{Fullscale \ Amplitude}{(Input \ Amplitude} \right)}{6.02}$$

(8)

#### 1.2.2.2 直流参数

测量条件:在ADC输入的正负端子之间接入一个恒定的直流电压,观察输出数字结果的分布情况。

图 1-3. ADC 直流测试示意图

www.ti.com.cn ADC 噪声分析

理论上,当采样数据量足够大时,叠加在直流信号上的噪声近似于正态分布。噪声的有效值是数据样本的标准偏差  $\sigma$ 。数据分布在 u-3  $\sigma$ ~u+3  $\sigma$  范围内的概率为 99.73%,因此直流信号的峰峰值约为 6  $\sigma$ 。

#### • 有效分辨率

在直流输入下, ADC 的有效分辨率可以通过将 ADC 的满量程范围 (FSR) 除以噪声有效值, 再取 2 的对数得出。该分辨率在直流信号采样场景或低频信号采样场景中非常重要,可以反映出 ADC 数字结果在实际应用中的有效位数。

Effective resolution =

$$log_2 \left( \frac{FSR}{V_{N,RMS}} \right) \left( bits \right)$$

(9)

上面的公式表示直流输入为满量程时的有效分辨率计算方法。当输入不是满量程时,计算公式修改为:

Effective resolution =

$$log_2 \left( \frac{V_{IN}}{V_{N,RMS}} \right) \left( bits \right)$$

(10)

也就是说,有效分辨率与输入电压有关。理论上,输入电压越大,直流有效分辨率就越高。因此,对于小输入信号,通常会通过前置放大器将其放大到接近 FSR 的水平,从而获得更高的有效分辨率。需要注意的是,不应引入过多的放大噪声(如 1/f 噪声和宽带噪声)。

• 无噪声分辨率

通过将 ADC 的满量程除以噪声的峰峰值,并取 2 的对数,可以得到直流输入下 ADC 的无噪声分辨率。它反映了可在恒定输入下保持稳定的位数。

Noise free resolution =

$$log_2 \left( \frac{FSR}{V_{N,PP}} \right) \left( bits \right)$$

(11)

# 2 ADC 噪声分析

#### 2.1 ADC 噪声分类

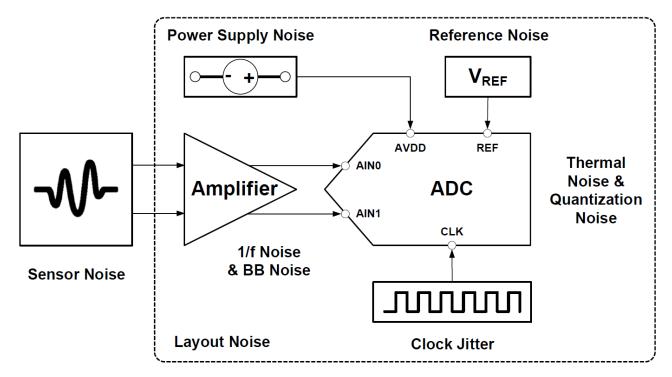

下图是 ADC 系统的方框图,显示了 ADC 采样数据的信号链和 ADC 模块运行所需的信号输入。每个链路都可能会引入噪声,因此 ADC 系统的噪声源包括传感器噪声、运算放大器噪声、ADC 噪声、电源噪声、基准电压噪声以及时钟抖动噪声。

传感器噪声和运算放大器的使用情况因应用场景的不同而存在较大差异,并且受布局影响较大。本文将这些分类为 ADC 的输入噪声。图 2-1 分别介绍了每级的噪声源。

图 2-1. ADC 噪声源示意图

#### 2.1.1 ADC 噪声

ADC 内部噪声包括量化噪声和热噪声。

• 量化噪声

ADC 的量化噪声指由输入模拟信号和输出数字信号之间的量化误差引起的噪声,其幅度由 ADC 的分辨率决定。量化噪声的峰峰值为 1LSB, ADC 的分辨率越高,量化误差越小。

• 热噪声

热噪声是所有电气元件的固有现象,即使没有 ADC 输入也依然存在。ADC 内除量化噪声外的所有噪声的总和通常被称为热噪声。热噪声通常呈现高斯分布,由于它与量化噪声无关,ADC 内的总噪声可通过和方根计算。

$$N_{ADC, Total} = \sqrt{N_{ADC, Thermal}^2 + N_{ADC, Quantization}^2}$$

(12)

从 ADC 内部总噪声的计算公式可以看出,ADC 噪声由量化噪声和热噪声中较大的那个决定。对于低分辨率 ADC,量化噪声远大于热噪声,在这种情况下,可以选择较小的基准电压来减小量化噪声,从而降低 ADC 噪声。对于高分辨率 ADC,由于其 LSB 低且量化噪声低,可以提高 ADC 的基准电压来增大满量程范围,减少信号中的热噪声比例,进而提高信噪比。

#### Lower-resolution ADCs

**Higher-resolution ADCs**

Resolution is limited by quantization noise Use smallest acceptable reference (to decrease quantization noise)

Resolution is limited by thermal noise Use largest acceptable reference (to increase dynamic range)

#### 图 2-2. 具有不同分辨率的 ADC 的量化噪声和热噪声

#### 2.1.2 基准噪声

ADC 输出的常用计算公式为:

因此,叠加在基准电压上的噪声将直接影响输出电压。基准电压噪声可以转换为累积在输出电压上的形式:

Output Code =

$$V_{IN(RMS)} * \frac{2^N}{V_{REF} + V_{N,REF(RMS)}}$$

(13)

将分子和分母除以 V<sub>REF</sub>,得到:

Output Code =

$$\frac{V_{IN(RMS)}}{V_{REF}} * \frac{2^{N}}{1 + \frac{V_{N,REF(RMS)}}{V_{RFF}}}$$

(14)

简化得出:

Output Code =

$$\frac{V_{IN(RMS)} * 2^{N}}{V_{REF}} * \left(1 - \frac{V_{N,REF(RMS)}}{V_{REF}}\right)$$

(15)

将上述公式分为求和形式,如下:

Output Code =

$$\frac{V_{IN(RMS)} * 2^{N}}{V_{REF}} - \frac{V_{IN(RMS)} * 2^{N} * V_{N,REF(RMS)}}{V_{RFF}^{2}}$$

(16)

因此,叠加在输出电压上的噪声电压形式为:

$$V_{N, REF} = \frac{V_{IN(RMS)}}{V_{REF}} * V_{N, REF(RMS)}$$

(17)

它与输入电压与基准电压之比(即满量程利用率)有关。输入的满量程利用率越高,叠加在 ADC 输出上的基 准电压噪声就越大。

考虑到噪声对 ADC 有效分辨率的影响,由于有效分辨率的 Vin 值比基准噪声中的 Vin 值低,且 ADC 的内部噪声通常是恒定的,与 ADC 输入无关,因此增大 ADC 输入电压可以提高 ADC 噪声影响下的有效分辨率,但不会影响基准电压噪声影响下的有效分辨率。

要降低基准电压噪声,可以在将基准电压添加到 ADC 之前添加一个 RC 滤波级,来滤除一些高频噪声。也可以选择适当的外部或内部基准电压来降低基准电压噪声的影响。

表 2-1 比较了几种不同基准电压的优缺点。

表 2-1. 不同 ADC 基准电压的优缺点

| 基准电压 | 优点                                                                                             | 缺点                                                                 |  |

|------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| 内部   | <ul><li>缩小 PCB 面积 + 降低功耗和成本</li><li>适用于多种应用</li></ul>                                          | <ul><li>噪声较高(相对)</li><li>漂移较高(相对)</li></ul>                        |  |

| 外部   | <ul> <li>基准噪声和漂移更低</li> <li>降低接地对电源电压和基准电压的影响<br/>(通过将 REFN 和 AIRN 直接连接以及单<br/>点接地)</li> </ul> | <ul><li>功耗一般较高</li><li>增加成本和布板空间</li><li>REF 和 ADC 噪声不相关</li></ul> |  |

#### 2.1.3 电源噪声

由于电源需要为系统的多个元件供电,ADC 和其他电路元件(例如 MCU)在运行过程中会导致电源出现电压波动,从而产生电源噪声。这些噪声可能会通过各种耦合方式影响 ADC 的输出结果。可以选择负载调节能力强的电源,并在电源输出端及 MCU 的电源端并联去耦电容器,来确保电源的稳定性。

#### 2.1.4 ADC 输入噪声

ADC 输入噪声指在信号采集、放大及传输到 ADC 模拟输入端子的过程中叠加在原始信号上的噪声。输入噪声可通过示波器进行测量。由于信号输入中涉及大量链路,因此很容易受到各种干扰。在输入链路的设计中,可以使用合理的布局和布线以及添加 RC 滤波,来更大限度地减少对输入信号的干扰,并尽可能滤除高频噪声。

#### 2.1.5 时钟抖动

时钟抖动会导致基于时钟边沿采样的输入信号采样点发生波动,从而导致采样的信号值发生抖动。信号频率越高,采样值因时钟抖动产生的抖动就越大。如果需要采样高频信号,则应选择具有更高电压摆率的时钟源,以缩短 ADC 采样时间,降低系统引入的均方根抖动。

### 2.2 如何降低噪声

通常认为, ADC 系统每个链路中的噪声互不相关, 因此 ADC 系统总噪声采用均方根法计算, 即先求每个链路中噪声的平方和再取平方根。

因此,ADC 系统的噪声取决于有效噪声值最高的链路。为了有效地降低系统噪声,需要测量或参考数据表来评估每个链路的噪声水平,然后尝试抑制最大噪声源,来降低系统噪声。

www.ti.com.cn ADC 噪声分析

#### 2.2.1 通过 RC 滤波降低输入噪声

RC 滤波器属于低通滤波器,可以通过选择适当的滤波器带宽滤除 ADC 输入中的高频噪声。一方面,为了截止高频噪声,带宽应尽可能低;另一方面,带宽过低会延长采样信号的建立时间,导致输入信号失真。因此,需要设计适当的 RC 值来滤除高频噪声,同时确保及时响应高频信号。具体参考:滤波器 RC 参数的理论计算方法

#### 2.2.2 布局建议

- 电源

- 使用负载调节率良好的 LDO 或开关电源,在输出端并联滤波电容器,为负载提供稳定的电源;

- 在 MCU/ADC 芯片的电源引脚并联一个大电容器 (10 μ F) 以滤除低频噪声,同时并联一个小电容器 (0.1 μ F) 以滤除高频噪声;

- 将数字电源与模拟电源隔离,将数字接地与模拟接地隔离,防止高频数字信号影响模拟信号输入。同时,建 议使用星形网络将模拟接地与数字接地连接,尽量减少相互干扰。

- 基准电压

- 建议将基准电压的负极端子直接连接到输入信号的负极端子,然后将其单点接地(星形网络连接);

- 使用外部基准电压时,并联小电容器以滤除基准电压上的高频噪声。

#### 2.2.3 提高信噪比

• 信号放大

对于具有固定分辨率和基准电压的 ADC, ADC 噪声是固定的,可以通过降低信号中的噪声比例来提高 ADC 的有效分辨率。可以将信号放大至接近 ADC 的满量程范围,从而提高有效分辨率。

• 降低基准电压值

提高信噪比的另一种方法是选择合适的基准电压(接近输入信号的最大值),从而通过减少量化噪声来降低 ADC 噪声,进而提高信噪比。

#### 2.2.4 选择合适的基准电压源

- 对于可使用比例式采样的应用场景,建议使用外部电压源作为基准电压。在这种情况下,理论上电压源上的噪声不会影响数字输出,并且可以实现非常低的基准电压噪声和偏差;

- 对于成本要求低、精度要求不高的应用,可以选择内部基准电压。

- 对于基准电压精度要求较高的情况,建议选择具有高精度和低温漂的外部基准电压。

#### 2.2.5 软件降噪法

提交文档反馈

通过软件降低信号噪声的最直接方法是增加采样频率以进行过采样,收集比所需更多的样本,并通过取平均值来减少信号中的噪声,从而提高有效分辨率和信噪比。均值处理也有助于消除 ADC 传递函数的 DNL 误差。对于 ADC 输出中因 DNL 误差较大而导致的代码丢失,均值处理可以使这些代码重新出现,因此过采样可以有效提升 ADC 的动态范围。关于过采样,需要注意以下几点:

ADC 过采样 www.ti.com.cn

• 如果要求的精度超过 1LSB,硬件均值计算无法对实际样本大小求平均值。例如,在过采样收集 16 个数据点时,不能在硬件上直接对 16 个点求平均,这将导致分辨率为 12 位,且最大量化误差为 ½LSB。可以将 16 个采样数据的每 4 个进行均值计算,从而得到 14 位的量化结果。然后再通过软件将其转换为 12 位的浮点数据,此时的最大量化误差为 1/8LSB。

- 适当的噪声可以增强硬件取平均值的降噪效果。如果输入信号的噪声非常低(噪声峰峰值小于 1LSB),由于 ADC 硬件分辨率仅为 12 位,即使增加过采样样本数,输出结果也保持不变,无法通过过采样达到更高分辨 率。因此,添加适量大于 1LSB 的噪声可以提高均值处理的有效性。

- 通常噪声越多,为了通过过采样获得高精度所需的样本数也越多,这样实际输入信号的有效采样频率就会降低。

## 3 ADC 过采样

#### 3.1 采样谏率

根据奈奎斯特采样定理,为了重构模拟输入信号,采样频率 **f** S 必须大于输入信号中最大频率分量的两倍。不符合奈奎斯特定理会导致频率混叠效应,使得模拟信号无法通过输入样本完全重构。因此,在大多数应用中,ADC 输入端需要使用低通滤波器来滤除小于采样频率一半的频率分量。过采样则是以高于奈奎斯特频率限值的速率对输入模拟信号进行采样,采样后再通过提取法来降低采样速率。

假设量化噪声以白噪声的形式叠加在信号上,且其功率密度在奈奎斯特频率限制范围内均匀分布,且该功率密度与采样频率无关。当采样频率高于奈奎斯特频率限值时,由于量化噪声功率保持不变而采样带宽增加,落入信号带宽内的噪声功率会大幅衰减,从而提升信噪比和 ADC 的有效位数。

#### 3.2 提取法

传统的均值计算方法是将 m 个样本相加后再除以 m。对使用低通滤波器(用于衰减信号的波动和噪声)的 ADC 测量中的多个数据进行均值计算。但需要注意的是,普通的均值计算并不能提高转换分辨率,因为 m 个 N 位样本的平均值依然表示为 N 位分辨率。提取法是一种求平均值的方法,它获取小于 m 的数字的平均值以获得比 N 位更大的分辨率。当提取法与过采样结合使用时,可以提高 ADC 的分辨率,具体原理参见软件降噪法。

#### 3.3 应用条件

为了成功采用过采样和提取法,需要满足以下条件:

- 输入信号中应适当存在噪声。噪声需近似为具有均匀功率频谱密度的白噪声。

- 噪声幅度必须足以随机切换输入信号,使其在不同量化位之间切换,即噪声的峰峰值应至少达到 1LSB,否则输入样本将得到相同的量化结果,无法通过求和与平均值运算提高 ADC 的有效分辨率。对于大多数应用来说,ADC 的内部热噪声和输入信号噪声都可以满足该条件。

# 4基于 MSPM0 的 ADC 应用

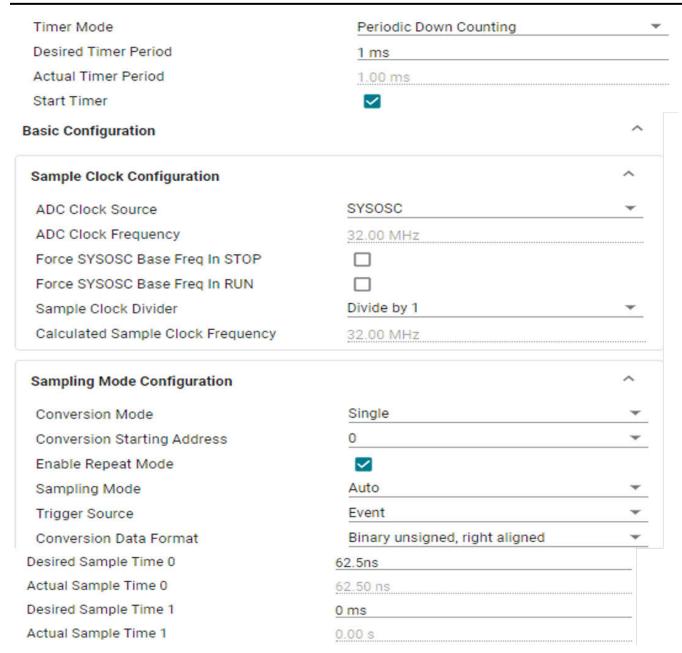

#### 4.1 MSPM0 的 ADC 配置

时钟

Sample Clock Configuration

LIPCLK

T

ADC Clock Source

32.00 MHz

T

ADC Clock Frequency

32.00 MHz

T

Sample Clock Divider

Divide by 8

T

Calculated Sample Clock Frequency

4.00 MHz

图 4-1. ADC 时钟的 Sysconfig 配置

- ADC 时钟 (ADCCLK)

- SYSOSC (最大 32MHz)

- HFCLK (最大 48MHz)

- ULPCLK (最大 40MHz、仅支持 PD0)

- ADC 采样时钟 (SAMPCLK):由 ADCCLK 分频产生

- 转换时钟: ADC IP 内部的 80MHz 晶体振荡器

- 12 位 ADC 数据的转换时间大约为 14 个转换时钟周期

- 采样模式

| Sampling Mode Configuration |                                | ^ |

|-----------------------------|--------------------------------|---|

| Conversion Mode             | Single                         | * |

| Conversion Starting Address | 0                              | ~ |

| Enable Repeat Mode          |                                |   |

| Sampling Mode               | Auto                           | ▼ |

| Trigger Source              | Software                       | ₩ |

| Conversion Data Format      | Binary unsigned, right aligned | ₩ |

|                             |                                |   |

# 图 4-2. ADC 采样模式的 SysConfig 配置

- 转换模式

- 单次转换:每次采样和转换过程仅转换单个点,通过配置起始地址 STARTADD,确定 MEMCTL 编号;

- *序列转换*:通过定义用于转换的 MEMCTL 编号的起始地址 STARTADD 和结束地址 ENDADD,可以定义数据转换序列(MEMCTL0-11 对应 MEMRES0-11),并且可以为每个 MEMCTLx 配备不同的 ADC 通道;

- 启用重复模式

- 非重复模式:每一轮转换完成后,转换使能位 (ENC) 自动复位为零。

- 重复模式:转换过程将继续启用,直到软件清除转换使能位(ENC);

- 采样触发源

- *软件*: 软件设置 CTL1.SC 位触发采样;

- 事件:事件上升沿触发采样;

- 采样模式

- *自动采样*:采样触发信号生成后,采样信号 SAMPLE 自动上升,采样时间由 SCOMP 定义的若干 SAMPCLK 时钟周期确定:

- *手动采样*(仅支持软件触发,不支持重复模式和序列转换,不支持硬件过采样):采样信号 SAMPLE 与软件触发信号 CTL1.SC 同步拉高。采样时间由 SC 的拉高时间确定,触发和采样同步完成;

- 触发模式

- 在重复和序列转换模式中,需要选择触发模式 (TRIG), 以确定下一轮转换是否需要触发信号。

| • 转换存储器配置                             |                                                      |   |

|---------------------------------------|------------------------------------------------------|---|

| ADC Conversion Memory 0 Configuration |                                                      | ^ |

| Name                                  | 0                                                    |   |

| Input Channel                         | Channel 2                                            | - |

| Device Pin Name                       | PA25                                                 |   |

| Reference Voltage                     | VREF                                                 | * |

| VREF Mode                             | Internal                                             | ~ |

| Calculated reference voltage          | 1.40 V                                               |   |

| Sample Period Source                  | Sampling Timer 0                                     | w |

| Optional Configuration                |                                                      | ^ |

| Averaging Mode                        |                                                      |   |

| Burn Out Current Source               |                                                      |   |

| Window Comparator Mode                |                                                      |   |

| Trigger Mode                          | Trigger will automatically step to next memory conve | - |

# 图 4-3. ADC 转换存储器的 SysConfig 配置

- 需要配置的转换存储器数量由转换模式中定义的 MEMCTL 起始和结束编号决定:

- 采样输入通道

- 基准电压

- VDDA:内部电源 (3.3V)

- VREF

- 内部:2.5V/1.4V - 外部:0~3.3V

采样计时器源:在自动采样模式下,选择用于采样计时的计时器。

- 其他

- 过采样

- 采样结果倍数 = 采样点数/平均分母

- 中断

- 不使用 DMA: 启用 MEMx 结果加载中断,每次采样结果生成后在中断中读取数据;

- 使用 DMA: 启用 DMA 完成中断,根据 ADC MEMx 结果加载触发 DMA 数据传输,并设置 DMA 传输的数据量。一旦 DMA 传输完成,输入 DMA 中断,即可立即处理 ADC 采样数据。

- CPU 轮询

- CPU 轮询 MEMx 结果加载寄存器,当 ADC 转换完成且结果载入 MEMx 时,相应的 CPU\_INT RIS 位将置为 1。

- CPU 轮询 ADC 状态寄存器,当 ADC 转换完成时,ADC 状态忙位将被清零。

#### 备注

对于下列器件,在 CTL1 寄存器中 ADC 启动转换位置位后,经过 14 个 ULPCLK 周期,忙位将被置位。这 14 个 ULPCLK 周期需要 CPU 延迟来等待忙位置位,之后 CPU 可轮询忙位以等待其清零。建议使用 MEMx 结果加载寄存器来轮询 ADC 转换完成状态。

MSPM0C110x、L1x0x、L111x、L134x、Lx22x、Gx10x、Gx50x、Gx51x 和 H321x。

基于 MSPMO 的 ADC 应用

# 4.2 基于 MSPM0G3507 ADC EVM 板的 ADC 直流测试

为了评估 MSPM0 G 系列的 ADC 性能,并比较直流输入下不同基准电压的精度,我们的团队基于 MSPM0G3507 设计了一款 ADC EVM 板,并进行了此次测试。

#### 4.2.1 软件/硬件配置

#### 4.2.1.1 硬件

MSPM0G3507 ADC EVM 板由以下四个部分组成:

· MCU 最小系统

MCU 为采用 28 引脚封装的 MSPM0G3507SDGS28。测试中, PA25 用于 ADC 输入, PA23 用于外部基准 VREF+ 输入, VREF- 通过 0 Ω 电阻接地。

• 2.5V 电压生成

使用高精度电压基准 REF7025QDGKR, 其输出电压为 2.5V, 用于提供 ADC 的外部基准电压。

• 1.25V 电压生成

使用 REF35125QDBVR 生成 1.25V 电压,为 MSPM0 ADC 提供稳定的直流输入。

• ADC 输入和基准电压选择

通过 0 Ω 电阻选择 ADC 输入 (1.25V、2.5V、VDD 和 GND) 以及外部基准电压 (VDD、2.5V、1.25V)。

图 4-4. MSPM0G3507 ADC EVM

#### 4.2.1.2 软件

测试方法如下:通过计时器事件每 1ms 触发 ADC 采样和转换,转换结果通过 DMA 自动传输至数组。DMA 传输大小设置为 1024。每次 DMA 传输完成后,进入 DMA 中断,对 ADC 结果进行分析并计算若干参数(如平均值、峰峰值、标准差等)。完成上述过程后,重复 1000 次,并获取每次的平均值或最大值。

图 4-5 展示了 ADC 的 sysconfig 基本配置。更改基准电压和过采样配置,以对比不同情况下的结果。

图 4-5. ADC 直流测试软件配置

以下是基于 ADC 结果计算的一些参数解释:

- ttlAveAnalog (V):基于 ADC 数字结果和以下公式计算的模拟平均值:  $N_{ADC} = \left(2^n 1\right) * \frac{(V_{IN} + 0.5LSB)}{V_{R} + 1}$

- *ttlDeltaSample* (LSB): ADC 1024 个样本的数字结果的峰峰值平均值;

- ttlMaxDelta (LSB): ADC 1024 个样本的数字结果的峰峰值最大值;

- ttlAveSample (LSB): ADC 1024 个样本的数字结果的平均值;

- *ttl/StdErr* (LSB): ADC 1024 个样本的数字结果的标准差平均值;

- NoiseStd (V): ADC 1024 个样本的数字结果的噪声 RMS 值的平均值,相当于电压标准差。

- SNR (1): ADC 1024 个样本的数字结果的信噪比平均值。

#### 4.2.2 测试结果

表 4-1 显示了测试结果的组织结构。请注意,关键参数是 *ttlDeltaSample* 和 SNR。前者表示 ADC 数据峰峰值的 平均值(表格中基于参考电压转化为 mV 单位),而后者则在相同输入电压下表示 ADC 整体精度。

表 4-1. 测试结果

| スマロ SIMAIA |          |                                |           |  |

|------------|----------|--------------------------------|-----------|--|

| 基准电压       | 过采样次数/分母 | 基于 ttlDeltaSample 的峰峰值<br>(mV) | 有效分辨率 (位) |  |

| 内部 VDDA    | 1/1      | 10.5                           | 10.598    |  |

|            | 4/2      | 4.8                            | 11.53     |  |

|            | 16/4     | 1.6                            | 12.935    |  |

|            | 128/8    | 0                              | 16.440    |  |

| 内部 2.5V    | 1/1      | 10.4                           | 10.526    |  |

| 内部 1.4V    | 1/1      | 11.3                           | 9.770     |  |

| 外部 VDD     | 1/1      | 11.3                           | 11.521    |  |

| 外部 2.5V    | 1/1      | 7.3                            | 10.925    |  |

#### 4.2.3 结果分析和结论

• 分析和结论

通过以下测试结果可以得出一些信息:

- 在不同基准电压且无过采样的情况下,观察 *ttlDeltaSample* 值的峰峰值,除了在"外部 2.5V"下的峰峰值明显较低外,在其他电压下的峰峰值相近。峰峰值主要由 ADC 输入端的尖峰引起。因为此尖峰远大于 ADC 内部噪声和基准噪声(也大于通过 6 倍标准差计算的峰峰值),所以在不同的基准电压下表现相似,无法反映不同基准电压的性能差异;

- 过采样可以有效地降低输入噪声,并提高 ADC 输出的 SNR。采集的样本越多,SNR 越大,但会导致有效采样频率降低。

- 通过比较不同基准电压的有效分辨率,我们可以得出在相同直流输入下的基准电压性能优劣顺序为:

#### 外部 VDD 3.3V > 外部 2.5V > 内部 VDDA > 内部 2.5V > 内部 1.4V

- 外部基准电压的性能通常优于内部基准电压,但会增加成本和 PCB 面积。

- 当"信号噪声>量化噪声"时,较高的基准电压可以提高分辨率,其中信号噪声包括基准噪声、热噪声和 其他输入信号中的噪声。

- 当"信号噪声 < 量化噪声"时,较低的基准电压会带来较低的量化噪声,从而提升分辨率和精度。ADC 的 LSB 决定了 ADC 精度的上限。

- 声明

- 上述测试结果仅反映了在 MSPM0G3507 ADC EVM 板上的测试结果。实际 ADC 应用性能与外部基准电压的精度及布局密切相关。以上结果并不保证在其他应用中完全复现,且在实际 ADC 应用中可能获得更好的结果。

- 上述结果仅反映了直流输入下的 ADC 测试结果,但有效分辨率的概念与 ENOB 不同,并且与器件数据表中的 交流参数不一致。

- 当选择精度较低的基准电压源,或者布局和布线不理想时,外部基准 ADC 的采样精度可能不如内部基准。

#### 5 修订历史记录

注:以前版本的页码可能与当前版本的页码不同

# Changes from OCTOBER 31, 2024 to NOVEMBER 30, 2025 (from Revision \* (October 2024) to Revision A (November 2025))

Page

添加了 ADC CPU 轮询方法。......1

#### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月