## Application Note

## 优化 FPD-Link ADAS 设计以提供系统级 ESD 抗扰度

Casey McCrea, Taylor Gage

## 摘要

FPD-Link 摄像头设计通常会在 OEM 认证期间经过严格的汽车 EMC 测试。随着摄像头系统在车辆安全架构中承担越来越重要的责任，这些认证的稳健性要求也变得更加苛刻。许多 OEM 客户要求摄像头系统在各种高应力电气条件下（包括传导干扰、辐射干扰、甚至是在模块、连接器或电缆受到 ESD 冲击期间）无差错运行。本应用手册概述了 FPD-Link 系统设计人员可以在硬件和软件设计中实施的关键设计指南，从而更大限度地提高系统级 ESD 性能。

## 内容

|                        |    |

|------------------------|----|

| <b>1 引言</b>            | 2  |

| <b>2 典型测试标准概述</b>      | 2  |

| 2.1 ISO 10605 标准       | 2  |

| 2.2 性能状态分类             | 3  |

| <b>3 FPD-Link 硬件优化</b> | 4  |

| 3.1 连接器接地              | 4  |

| 3.2 PCB 至外壳接地          | 4  |

| 3.3 模式选择               | 5  |

| <b>4 FPD-Link 软件优化</b> | 7  |

| 4.1 锁定检测调优             | 7  |

| 4.2 奇偶校验错误处理           | 8  |

| 4.3 正向纠错               | 9  |

| <b>5 优化测试数据</b>        | 11 |

| 5.1 基线硬件 - 无软件优化       | 11 |

| 5.2 优化的硬件 - 无软件优化      | 12 |

| 5.3 优化的硬件和软件           | 12 |

| <b>6 软件优化脚本示例</b>      | 13 |

| <b>7 其他系统级软件选项</b>     | 14 |

| <b>8 总结</b>            | 15 |

| <b>9 参考资料</b>          | 15 |

| <b>10 修订历史记录</b>       | 16 |

## 商标

所有商标均为其各自所有者的财产。

## 1 引言

系统级 ESD 测试是全球众多汽车 OEM 的共同要求。系统级 ESD 测试的目标通常有两个：确保模块内的电气元件不会受到损坏，以及评估 ESD 事件期间的应用级性能。关于系统级 ESD 测试，一个常见的误解是，应用级性能与元件数据表（例如 IEC 6100-4-2、HBM、CDM 等）数据表指定的 ESD 等级相关联。数据表中的 ESD 等级仅描述了 IC 在不受损的情况下承受器件引脚放电的能力。该等级主要用于了解芯片的处理和组装要求，但关键的是，该等级未考虑应用级性能的任何方面，例如数据丢失。需要注意的是，高速铜链路在 EMI/ESD 应力下的应用级性能与系统设计息息相关。本指南包含 TI 的建议，旨在通过强大的硬件设计实践和软件设置优化来更大限度地提高抗扰度性能。

## 2 典型测试标准概述

### 2.1 ISO 10605 标准

ISO 10605 标准是评估汽车环境中系统级 ESD 性能时最常用的测试标准之一。该标准专门用于模拟 ESD 对车辆电气系统的影响并评估系统性能。在 FPD-Link 系统中，测试设置通常包括从 ECU 到摄像头模块的端到端视频链路，以及实时评估系统性能的方法，例如用于显示摄像头数据的实时屏幕。

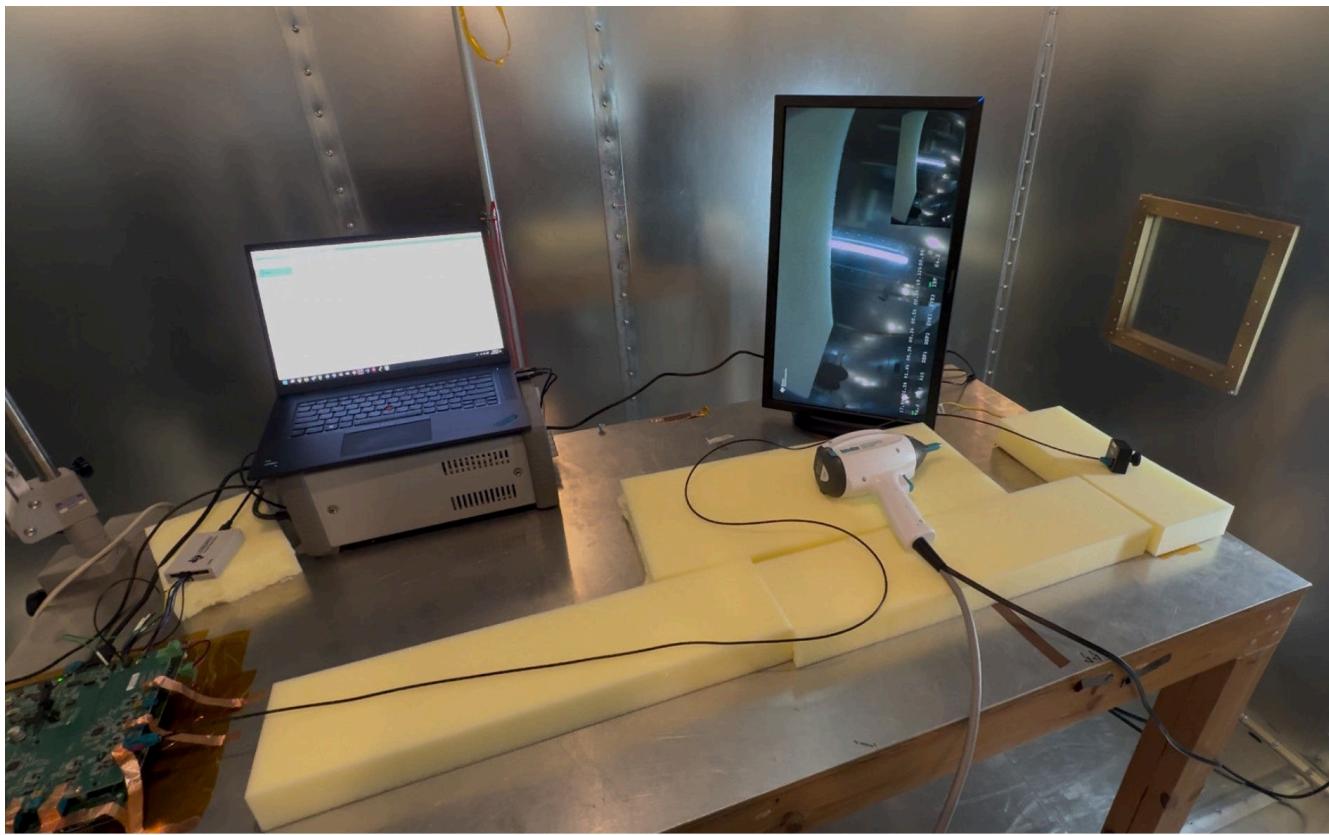

ISO 10605 测试设置可以采用直接（到 DUT）或间接（到 DUT 附近的耦合平面）放电方法进行，具体通常由 OEM 要求定义。ESD 能量通过具有指定 RC 网络和尖端形状的 ESD 发生器枪释放到测试设置。测试中规定了两种不同的放电类型：空气放电和接触放电。在这两者中，接触放电通常对系统施加的耦合能量更大，因为在放电过程中通过空气电离散发的能量较少。下面的示例设置根据 ISO 10605 附录 F 进行配置，其中在 FPD 电缆下方使用了耦合板。

图 2-1. ISO 10605 附录 F 示例设置

第二个图概述了 TI 内部用于评估摄像头模块性能的测试设置，其中包括一个处理器平台测试板、完整的摄像头模块以及通过 PC 监视器显示的实时视频。此设置用于收集节 5 部分中的示例数据。请注意，解串器系统并不像典型 ECU 平台那样具有外壳。因此，解串器系统的接地和屏蔽比预期弱，导致平均性能有所下降。

图 2-2. ISO 10605 示例设置

## 2.2 性能状态分类

系统级 ESD 性能在每个测试级别中使用字母分类系统进行分类。OEM 通常会不同级别的系统性能状态设定要求。

表 2-1. 性能状态表

| 状态 | 说明                                         |

|----|--------------------------------------------|

| A  | 无性能偏差 (通常表示摄像头系统没有出现可察觉的视频中断)              |

| B  | 临时中断, 自动恢复 (通常表示可察觉的瞬时视觉干扰)                |

| C  | 无法自动恢复的性能中断 (通常表示出现黑屏, 需要重启或重新初始化系统才能恢复视频) |

| D  | 对 DUT 造成永久损坏 (通常表示对包括 IC 或无源器件在内的系统造成物理损坏) |

## 3 FPD-Link 硬件优化

### 3.1 连接器接地

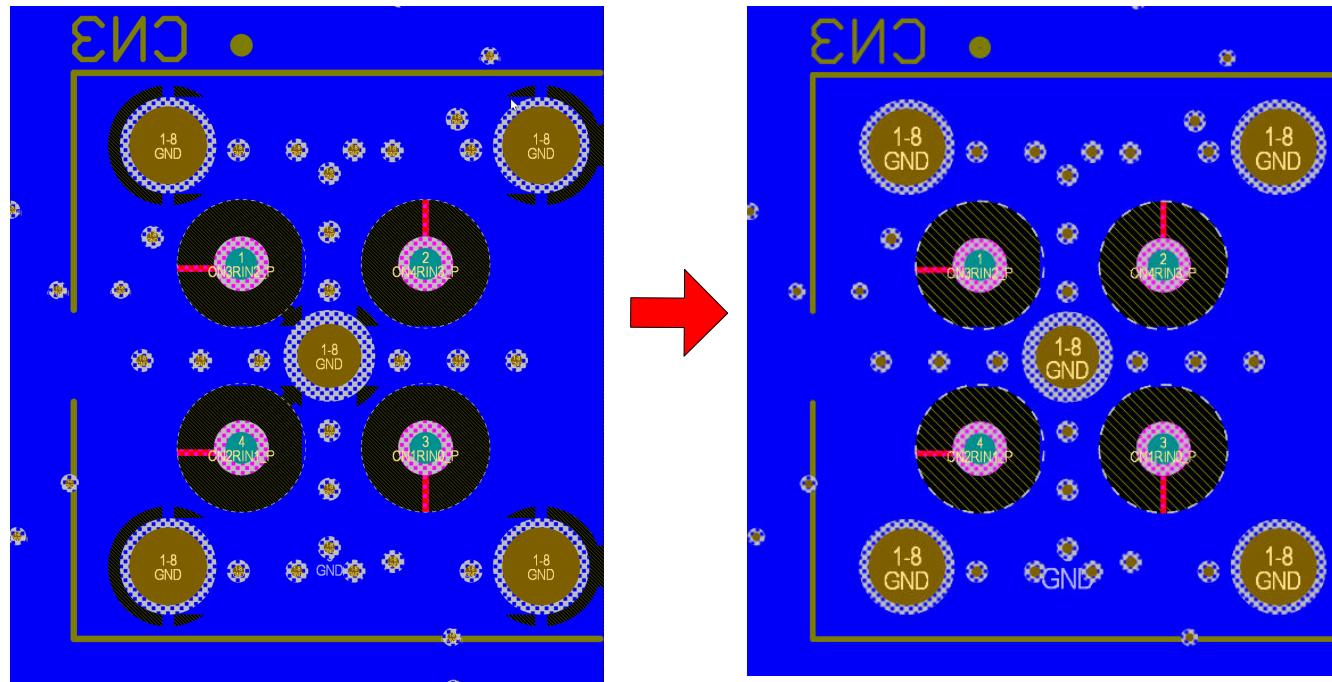

在使用 PoC 的 ADAS 应用中，电缆屏蔽层不仅作为远程摄像头的直流电源的返回路径，还用作两个系统之间的接地基准。高能干扰事件（包括 ESD 冲击和天线辐射发射）可能会导致串行器和解串器器件之间的系统接地基准出现瞬态中断，从而导致位错误。为减轻这种影响，应确保在 FPD 电缆的两侧将电缆屏蔽层连接到系统地并将电感降到最低。TI 建议确保通过可靠连接而非散热齿条将连接器接地引脚连接到多个层上的 PCB 接地平面。

请注意，建议的布局不仅提供了连接器 GND 引脚与大型实心 GND 平面之间的直接连接，而且还通过多个过孔将 GND 平面与其他电路板层上的 GND 平面相连。在此设计中，电路板的全部 8 层都在连接器下方包含一个 GND 平面。

图 3-1. 散热布局（左侧）、建议的实心 GND 布局（右侧）

### 3.2 PCB 至外壳接地

在系统设计中，减轻 ESD 对性能影响的一个关键方面是提供低电感的放电路径，以便将能量引导远离高速信号。为实现这一目标，其中一种有效方法是在 PCB 接地端和连接到机箱接地端的外壳之间提供良好的接触。通过在 PCB 周边实现外露接地环，可以通过弹簧连接或导电螺钉和紧固件为外壳提供多个与电路板接地端的接触点。PCB 的两侧需要通过低电感连接与外壳接地相连。这有助于防止电路板局部区域内的接地反弹。

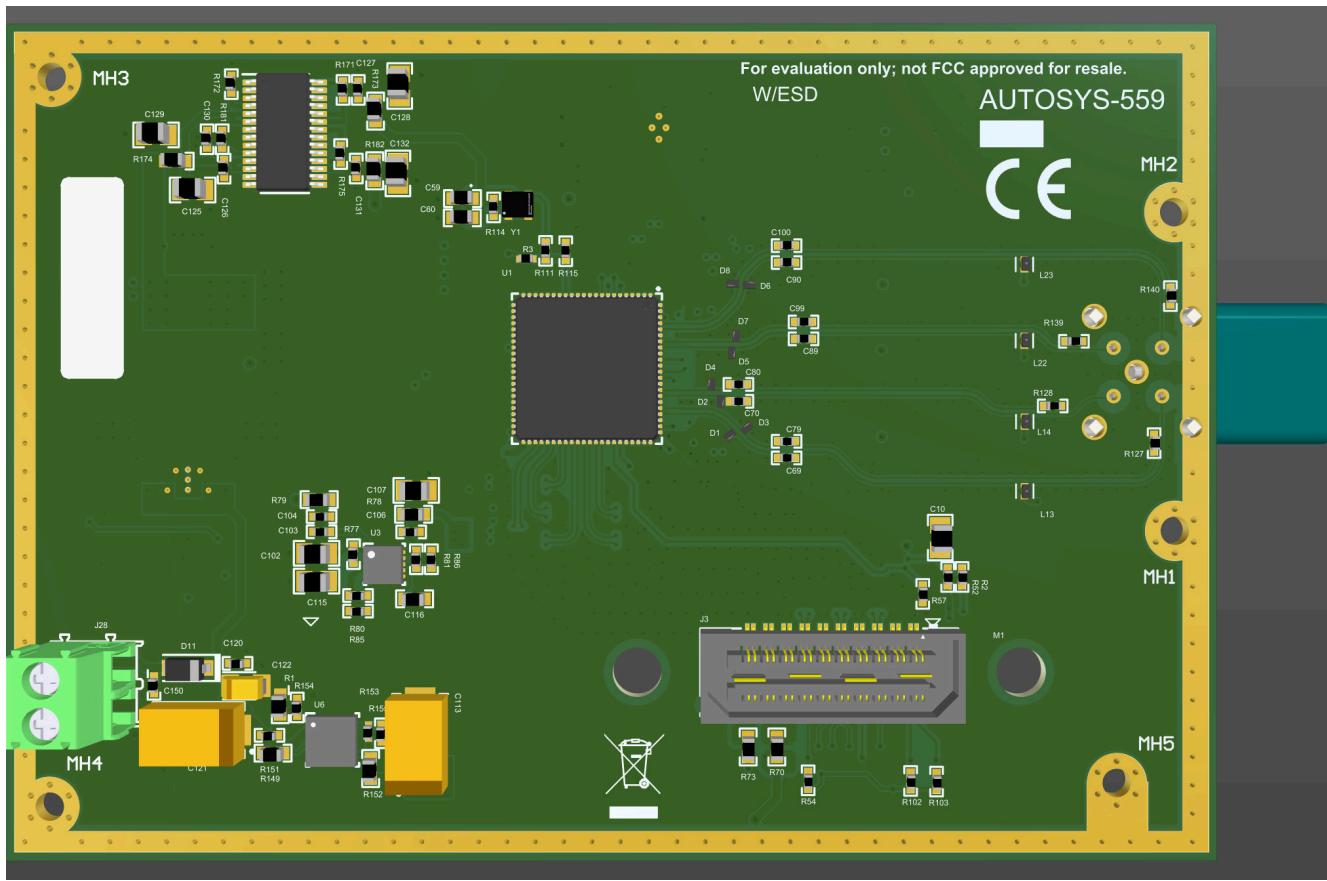

图 3-2. 外壳接地环示例

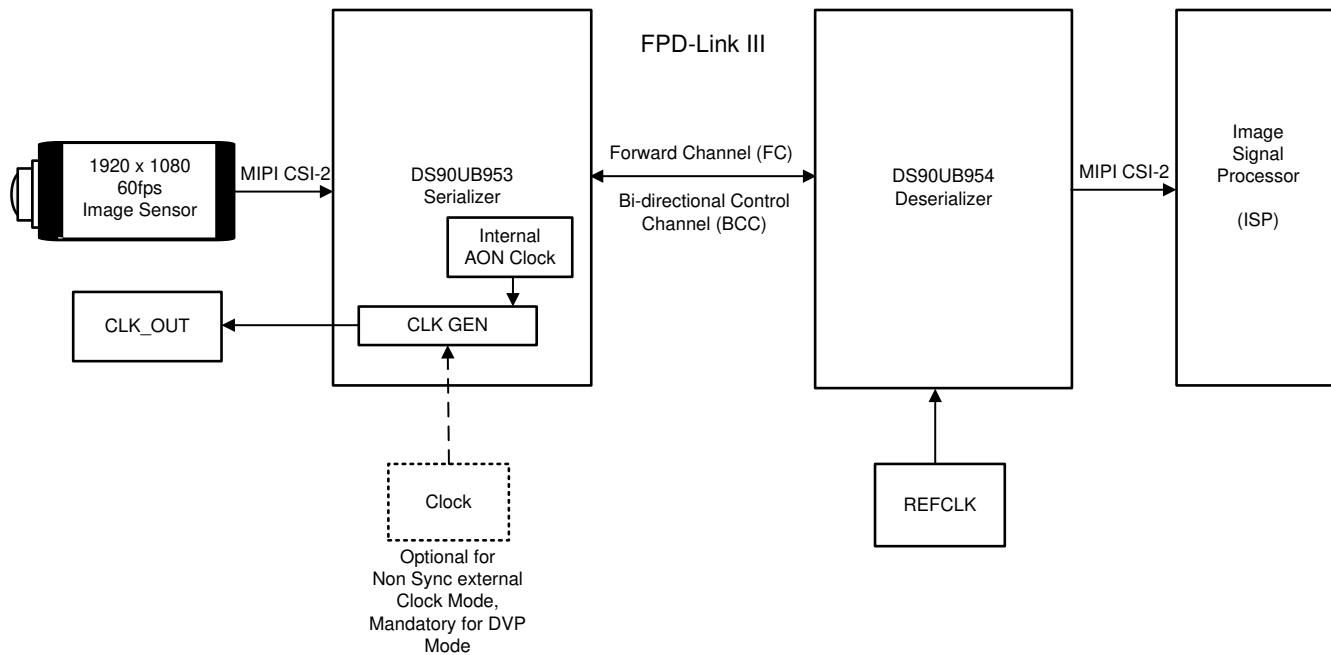

### 3.3 模式选择

FPD-Link III 和 IV CSI-2 ADAS 串行器支持多种工作模式，包括同步模式和非同步模式。在同步模式下，串行器使用来自解串器的反向通道信号作为时钟基准，以生成正向通道信号，以及提供传感器的可选时钟输出信号 (CLKOUT)。由于同步模式的架构，解串器和串行器之间的反向通道信号如果出现瞬态干扰，可能会导致串行器暂时丢失时钟基准。当发生这种情况时，解串器的正向通道信号可能相应地出现中断。相反，在非同步模式下，正向通道信号和反向通道信号之间没有关联。反向通道信号中的错误不会影响串行器发送有效正向通道信号的能力，该信号包含任务关键型视频数据。

图 3-3. FPD-Link ADAS 时钟架构

FPD-Link III/ADAS IV 串行器器件中存在两种不同的非同步模式：

- 使用外部 CLKIN 的非同步模式

- DS90UB953-Q1、DS90UB935-Q1、DS90UB635-Q1 和 DS90UB971-Q1 在所有支持的速率下提供

- CLKOUT 功能可用

- 使用内部 AON 时钟的非同步模式

- DS90UB953-Q1、DS90UB935-Q1 和 DS90UB635-Q1 上提供

- DS90UB971-Q1 仅在 FPD-Link III 模式 (4Gbps) 下提供

- CLKOUT 功能禁用

TI 建议配置摄像头模块设计以在硬件中支持任一模式，以便能够在 ESD 认证测试期间灵活地评估这两种模式。许多系统设计人员更倾向于使用同步模式，以减少元件数量，实现更快的反向通道 GPIO 速度，并允许扩频时钟。根据系统对数据速率和 CLKOUT 功能的需求，系统设计人员还可以向串行器中添加外部振荡器输入，以选择使用非同步外部 CLKIN 模式。这样，便可以在 ESD 认证测试期间在多种模式下评估系统性能。如果系统偏好使用同步模式，并且 ESD 性能满足系统设计人员在该模式下的需求，则可以在最终构建中从 BOM 中移除振荡器。

## 4 FPD-Link 软件优化

### 4.1 锁定检测调优

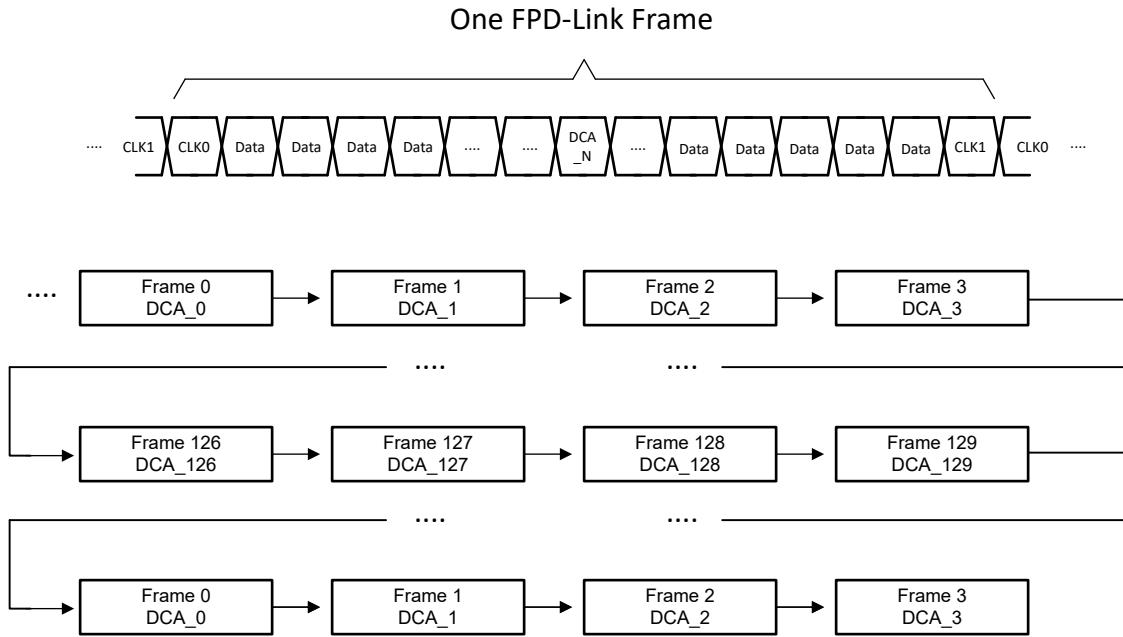

FPD-Link ADAS 正向通道协议将视频有效载荷数据以及其他信息（包括 GPIO、I2C、状态、时钟等）打包到串行帧，并发送到下游解串器。为了正确解码传入的数据帧，FPD-Link 接收器必须通过确定正确的数据转换率来锁定到传入的高速信号，并且接收器必须正确确定传入数据帧的对齐方式（例如，每个串行帧的开头和结尾）。为了完成对齐任务，FPD-Link ADAS 串行器会在正向通道数据流中插入一个称为解码周期数组 (DCA) 序列（长度为 130 个字符）的多帧同步数据模式，同时在每帧中添加两个专用时钟位 (CLK0/CLK1)。

图 4-1. FPD-Link ADAS 帧结构和序列

在初始锁定建立后，解串器会持续监控传入的串行帧，以检测每个帧内两个时钟位的预期位置以及 130 帧 DCA 编码位模式。默认情况下，当在 130 个传入帧范围内检测到时钟和编码位中存在三个错误时，FPD-Link 锁定信号会下降。虽然这种默认行为能有效指示链路中 BER 的增加，但也会导致链路对 ESD 冲击等瞬态错误事件非常敏感。此外，请注意，FPD 帧的时钟或编码位可能会出现瞬态错误，而不会影响任何应用级功能。只要这些错误是瞬态的，FPD-Link 接收器就会自动保持运行和对齐状态。

为了提高链路在 ESD 应力下的稳健性，TI 建议增加解串器内的 LINK\_ERR\_THRESH 设置，这将增加在每个 130 帧周期内必须检测到的错误数量，才能使解串器失锁并开始重新采集。这个阈值配置可以在寄存器 0xB9 (LINK\_ERROR\_COUNT) 中找到。为了使配置的阈值生效，还必须将 LINK\_ERR\_COUNT\_EN 设置为 1。

另一种可降低失锁算法灵敏度的优化方法是在链路错误计数器中禁用时钟位错误检测。通过配置寄存器 0xB6 = 0x1C，时钟位的检测将不再用作失锁的标记。在此设置下，仅使用重复的 130 帧 DCA 编码模式来检测失锁。

## 4.2 奇偶校验错误处理

除了 FPD-Link 正向通道帧中的多帧编码和时钟错误检查之外，每个 FPD-Link 帧还包括已知的奇偶校验位。这意味着，每个传入帧都有偶数个 1，并由解串器进行实时验证。如果解串器识别到传入的 FPD 帧中有奇数个 1，则解串器可以标记错误并递增奇偶校验错误计数器，以便用于诊断。

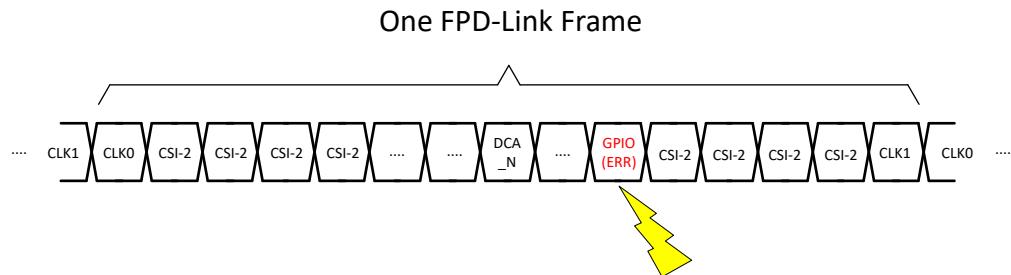

默认情况下，ADAS 解串器配置为丢弃包含奇偶校验错误的 FPD-Link 正向通道帧，这意味着该帧中包含的所有信息都不会转发到下游数据路径。虽然此默认行为可以防止错误传播，但也会让系统对可能不会影响应用的瞬态误差更为敏感。例如，当传入的 FPD-Link 帧具有一位错误时，则会标记出奇偶校验错误：

图 4-2. 奇偶校验错误示例

在这个例子中，一个位错误影响了 FPD-Link 帧内的某个正向通道 GPIO 时隙。因此，该帧中的 1 数量变为奇数，然后解串器将丢弃整个数据包。不过，这种在帧时钟位中的瞬态错误是可以接受的，而不会导致 LOCK 中断或帧边界丢失。此外，该特定错误也没有影响帧内的任何 CSI-2 视频数据。根据应用用例，这类错误可能对系统的任何方面都没有影响（例如，应用中没有使用正向通道 GPIO 时）。

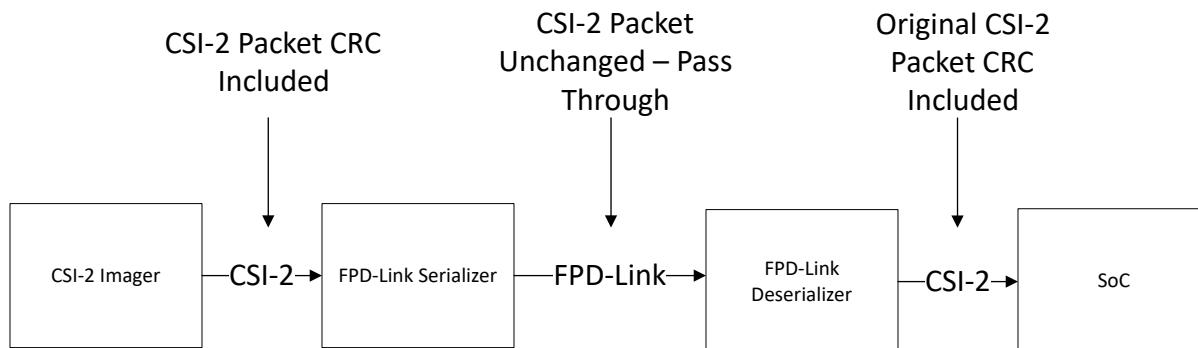

通过将 PORT\_CONFIG2 寄存器中的 DISCARD\_ON\_PAR\_ERR 设置为 0，可以将 FPD-Link III 和 IV CSI-2 ADAS 解串器产品配置为不丢弃含有奇偶校验错误的数据包。禁用此设置后，系统对瞬态错误事件的敏感度会降低，这有助于在抗扰度测试期间更容易达到 A 类性能要求。

允许处理含有奇偶校验错误的数据包而不是将其丢弃，并不意味着损坏的视频数据可以不被注意地通过解串器传输。这是因为 FPD-Link ADAS 器件通过端到端传输 CSI-2 数据包。在到达下游应用处理器之前，CSI-2 有效载荷和校验和都会通过串行器和解串器原封不动地进行传输。CSI-2 有效载荷校验和 (CRC) 也不会进行重新计算。因此，在 FPD-Link 通道中，如果位错误损坏了视频像素数据，相应的 CSI-2 数据包将在最终目的地无法通过 CRC 校验。然后，应用处理器可以根据应用需求决定如何更好地处理错误。

图 4-3. CSI-2 数据包传输

## 4.3 正向纠错

FPD-Link III 和 FPD-Link IV 产品系列中的部分 FPD-Link 器件在 FPD-Link 正向通道路径中包含正向纠错 (FEC) 功能。正向纠错功能利用未占用的通道带宽来随正向通道数据有效载荷一起发送纠错码字，从而使下游解串器能够纠正瞬态错误。以下器件上提供 FEC 功能：

- DS90UB971-Q1

- DS90UB971S-Q1

- DS90UB953-Q1

- DS90UB953A-Q1

- DS90UB935-Q1

- DS90UB635-Q1

- DS90UB960-Q1

- DS90UB962-Q1

- DS90UB662-Q1

- DS90UB9702-Q1

- DS90UB9722-Q1

- DS90UB9724-Q1

- DS90UB9724S-Q1

- DS90UB9742-Q1

以下器件上不提供 FEC 功能：

- DS90UB933-Q1

- DS90UB913A-Q1

- DS90UB913Q-Q1

- DS90UB934-Q1

- DS90UB954-Q1

- DS90UB936-Q1

- DS90UB638-Q1

- DS90UB964-Q1

要使用 FEC 功能，链路对中的串行器和解串器器件都必须支持 FEC。

有三种 FEC 模式可供选择，每种模式中插入的纠错码 (ECC) 具有不同的码大小：

- 6 位 FEC

- 7 位 FEC

- 8 位 FEC

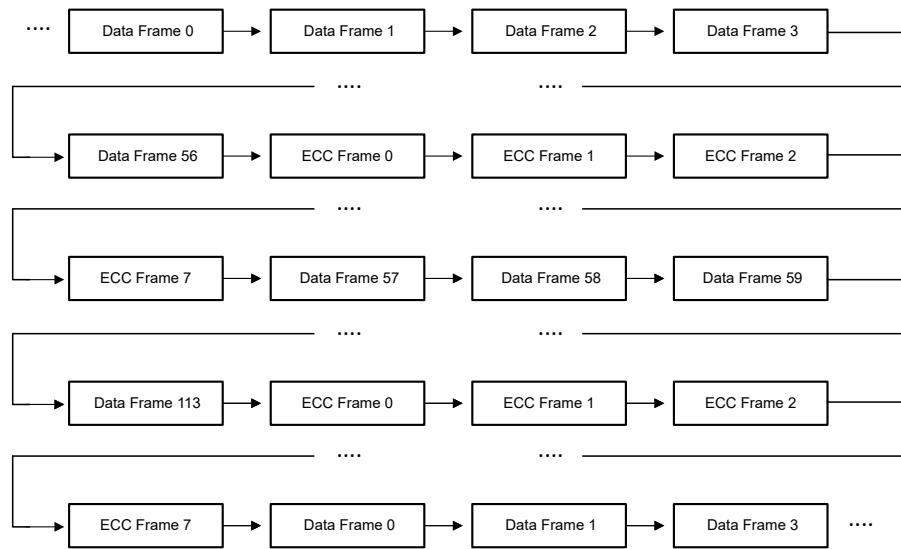

在启用 FEC 的情况下，串行器会依次发送多个 (X) 数据帧，然后发送多个包含纠错码 (ECC) 的 (Y) 帧。纠错码块 (Y) 能够帮助解串器检测 2 位错误并校正数据块 (X) 内的 1 位错误，从而保护 CSI-2 数据、GPIO 数据和 I2C 数据，这与 CSI-2 数据的数据包标头内的数据保护机制非常相似。

图 4-4. 8 位 FEC 序列示例

每种 FEC 模式都定义了在 130 帧 DCA 序列中发送的 (X) 数据帧与 (Y) ECC 帧之间的比例。6 位模式可以保护较小的数据块，但纠错码的发送频率更高。8 位模式可以保护更大的数据块，而纠错码的发送频率较低。该比例定义如下：

表 4-1. ECC 代码传输

| FEC 模式 | 数据帧数 (X) | ECC 帧数 (Y) | 每个 DCA 序列的 ECC 帧 | 每个 DCA 序列的数据帧 | FEC 开销 |

|--------|----------|------------|------------------|---------------|--------|

| 6 位    | 20       | 6          | 30               | 100           | 23%    |

| 7 位    | 36、37 交替 | 7          | 21               | 109           | 16%    |

| 8 位    | 57       | 8          | 16               | 114           | 12%    |

FEC 开销会降低 FPD-Link 正向通道流水线中视频允许的有效载荷能力。必须注意验证启用 FEC 后的链路视频带宽是否能满足应用需求。

表 4-2. FEC 开销影响示例

| 器件           | FPD-Link 速率 (Gbps) | 最大 CSI-2 带宽 (Gbps) | FEC 模式 | 启用 FEC 时的最大 CSI-2 带宽 (Gbps)                 |

|--------------|--------------------|--------------------|--------|---------------------------------------------|

| DS90UB971-Q1 | 7.55               | 6                  | 6 位    | 4.8                                         |

| DS90UB971-Q1 | 7.55               | 6                  | 7 位    | 5.1                                         |

| DS90UB971-Q1 | 7.55               | 6                  | 8 位    | 5.3                                         |

| DS90UB953-Q1 | 4                  | 3.2                | 6 位    | 2.6                                         |

| DS90UB953-Q1 | 4                  | 3.2                | 7 位    | 2.7                                         |

| DS90UB953-Q1 | 4                  | 3.2                | 8 位    | 2.8                                         |

| DS90UB935-Q1 | 4                  | 2.528              | 6 位    | 2.528<br>( 2.528Gbps 和 3.2Gbps/1.23 中的较小者 ) |

| DS90UB935-Q1 | 4                  | 2.528              | 7 位    | 2.528<br>( 2.528Gbps 和 3.2Gbps/1.16 中的较小者 ) |

| DS90UB935-Q1 | 4                  | 2.528              | 8 位    | 2.528<br>( 2.528Gbps 和 3.2Gbps/1.12 中的较小者 ) |

要启用 FEC 功能，请配置解串器寄存器 0x4A ( 特定于端口 ) :

- 6 位 FEC : 0x4A = 0x01

- 7 位 FEC : 0x4A = 0x02

- 8 位 FEC : 0x4A = 0x03

解串器通知串行器通过反向通道自动进入 FEC 模式。

#### 4.3.1 FEC 测试功能

支持的串行器和解串器器件包含验证功能，用于检查 FEC 功能是否正常运行。串行器可以通过寄存器命令注入 FEC 错误，而解串器则提供关于在 FPD-Link 通道中检测到的 ECC1/ECC2 FEC 错误数的诊断信息。需要注意的是，这些错误与 CSI\_RX\_STS 寄存器报告的 ECC1/ECC2 CSI-2 错误不同。

```

board.writeI2C(serAddr,0x76,0x01) # Force 1x FPD ECC1 error (Correctable)

board.writeI2C(serAddr,0x76,0x02) # Force 1x FPD ECC2 error (Detectable)

```

解串器的 FEC 错误诊断计数器是特定于端口的。在读取诊断信息之前，请使用寄存器 0x4C 选择所需的 RX 端口。

```

board.writeI2C(desAddr,0x4C,0x01) # Select RX port 0

board.readI2C(desAddr,0x48) # Read back count of FPD ECC1 Errors (Clear on Read)

board.readI2C(desAddr,0x49) # Read back count of FPD ECC2 Errors (Clear on Read)

```

## 5 优化测试数据

为了展示硬件和软件优化对系统级 ESD 性能的影响，TI 使用 FPD-Link IV DS90UB971-Q1 和 DS90UB9702-Q1 器件在多种解串器配置下进行了 ISO 10605 测试：

- 基本硬件设计/无软件优化

- 优化的硬件设计/无软件优化

- 优化的硬件设计 + 软件优化

这些测试使用了 DS90UB971-Q1 摄像头模块，该模块以 7.55Gbps 速率运行，并通过 1.5m Dacar 302 电缆连接到解串器硬件 (DS90UB9702-Q1)。解串器系统放在金属外壳内，以模拟典型的 ECU 子系统设计。解串器外壳连接到工作台 GND 平面，而电缆和摄像头模块则使用绝缘块悬挂在接地平面上方。

此 ISO 10605 测试的目标是模拟典型的 OEM EMC 批准环境，在该环境中，系统在 ESD 冲击事件中的性能分为 A、B、C 或 D 类。通过对三种系统进行逐步的硬件和软件优化测试，可以观察到典型的性能提升趋势。这个测试并未反映每种系统设计中所期望的具体结果，而是为了展示通过优化硬件和软件设计所能实现的相对性能改进。

### 5.1 基线硬件 - 无软件优化

第一轮测试使用基线 DS90UB9702-Q1 硬件设计执行，该设计不包含指南前面所述的优化。该系统配置为基本链路设置，不包括任何旨在提高瞬态抗扰度的软件优化。此测试的目的是建立 ESD 性能基准。该系统采用接触放电和空气放电方法，在摄像头模块和解串器盒周围的不同冲击点进行了测试。在每个应力水平后，都会记录诊断寄存器以识别测试期间是否存在任何 FPD-Link 失锁或无法纠正的 CSI-2 错误，这些可能导致视频源出现闪烁、黑屏或失真。

**表 5-1. 基线硬件 - 无软件优化 ESD 结果**

| 冲击类型 | 电平                | 典型的 OEM 要求 | 结果 |

|------|-------------------|------------|----|

| 空气   | $\pm 4\text{kV}$  | A 类        | B  |

| 接触放电 | $\pm 4\text{kV}$  | A 类        | B  |

| 空气   | $\pm 6\text{kV}$  | A 类        | B  |

| 接触放电 | $\pm 6\text{kV}$  | A 类        | B  |

| 空气   | $\pm 8\text{kV}$  | A 类        | C  |

| 接触放电 | $\pm 8\text{kV}$  | B 类        | C  |

| 空气   | $\pm 15\text{kV}$ | B 类        | C  |

| 接触放电 | $\pm 15\text{kV}$ | B 类        | C  |

- A 类 = 无失锁、无不可纠正的 CSI-2 错误。

- B 类 = 暂时失锁，或者出现 CSI-2 错误，但自动恢复

- C 类 = 需要软复位 SoC 才能重新启动视频

## 5.2 优化的硬件 - 无软件优化

第二轮测试采用了经过优化的解串器硬件版本，旨在将高速信号路径与 ESD 冲击噪声隔离开来。测试继续使用与前一轮测试相同的初始化软件，以展示硬件单独带来的相对性能提升。通过遵循良好的布局实践和物理设计注意事项，系统能够实现略高于基线示例的 A 类性能。

**表 5-2. 优化的硬件 - 无软件优化 ESD 结果**

| 冲击类型 | 电平                | 典型的 OEM 要求 | 结果 |

|------|-------------------|------------|----|

| 空气   | $\pm 4\text{kV}$  | A 类        | A  |

| 接触放电 | $\pm 4\text{kV}$  | A 类        | A  |

| 空气   | $\pm 6\text{kV}$  | A 类        | B  |

| 接触放电 | $\pm 6\text{kV}$  | A 类        | B  |

| 空气   | $\pm 8\text{kV}$  | A 类        | B  |

| 接触放电 | $\pm 8\text{kV}$  | B 类        | B  |

| 空气   | $\pm 15\text{kV}$ | B 类        | B  |

| 接触放电 | $\pm 15\text{kV}$ | B 类        | B  |

- A 类 = 无失锁、无不可纠正的 CSI-2 错误。

- B 类 = 暂时失锁，或者出现 CSI-2 错误，但自动恢复

## 5.3 优化的硬件和软件

最后一轮测试在解串器初始化中集成了软件优化，从而进一步提升性能。通过调整锁定灵敏度并向 FPD-Link 通道添加 FEC 功能，系统在瞬态 ESD 应力下的整体性能显著提升，并在更高强度的 ESD 噪声下也能实现 A 类性能。

**表 5-3. 优化的硬件和软件 ESD 结果**

| 冲击类型 | 电平                | 典型的 OEM 要求 | 结果 |

|------|-------------------|------------|----|

| 空气   | $\pm 4\text{kV}$  | A 类        | A  |

| 接触放电 | $\pm 4\text{kV}$  | A 类        | A  |

| 空气   | $\pm 6\text{kV}$  | A 类        | A  |

| 接触放电 | $\pm 6\text{kV}$  | A 类        | A  |

| 空气   | $\pm 8\text{kV}$  | A 类        | A  |

| 接触放电 | $\pm 8\text{kV}$  | B 类        | B  |

| 空气   | $\pm 15\text{kV}$ | B 类        | B  |

| 接触放电 | $\pm 15\text{kV}$ | B 类        | B  |

- A 类 = 无失锁、无不可纠正的 CSI-2 错误。

- B 类 = 暂时失锁，或者出现 CSI-2 错误，但自动恢复

## 6 软件优化脚本示例

### 1 级优化

以下脚本示例结合了建议的系统级 ESD 测试性能软件优化。这些设置通常适用于所有使用 FPD-Link III/IV ADAS 器件并具有 FEC 功能的系统。此示例使用 7 位 FEC，但用户可以根据系统需求和测试性能调整 FEC 设置。

```

board.writeI2C(desAddr,0x4C,0x0F) # Select all RX Ports

board.writeI2C(desAddr,0xB9,0x1F) # Increase LINK_ERR_THRESH

board.writeI2C(desAddr,0x4A,0x02) # Enable FPD FEC (7-bit)

board.writeI2C(desAddr,0x7C,0x00) # Disable FPD frame discard on parity error

```

### 2 级优化

在某些情况下，通过调整 FPD-Link AEQ 增益或将 FPD-Link AEQ 范围锁定到较小的值可以进一步提高性能。然而，AEQ 的调整应作为最后的选择，仅在所有其他硬件和 1 级软件优化措施都已用尽的情况下才可使用。将 AEQ 调整为极端值也可能会对链路性能产生意外的负面影响，建议在手动调整 AEQ 时联系 TI 寻求帮助。

对于 FPD-Link 器件（包括 DS90UB960-Q1、DS90UB962-Q1、DS90UB662-Q1、DS90UB954-Q1、DS90UB936-Q1、DS90UB934-Q1、DS90UB964-Q1 和 DS90UB638-Q1），可通过强制降低 AEQ 值来提高系统性能。在大多数情况下，对于电缆长度小于 2m 至 3m 的情况，强制将 AEQ 值设为 0 可以提高系统级 ESD 性能。

```

# 960, 962, 662 AEQ Force for short cable length

board.writeI2C(desAddr,0x4C,0x0F) # Select all RX Ports

board.writeI2C(desAddr,0xD4,0x01) # Force AEQ = 0

```

对于以 FPD-Link IV CDR 模式运行的 FPD-Link IV 解串器（包括 DS90UB9702-Q1、DS90UB9722-Q1、DS90UB9724-Q1 和 DS90UB9742-Q1），可通过增加 AEQ 值来提高性能。系统设计人员可以尝试将自动选定的 AEQ 值增加 +5 作为起始值。要增加 AEQ，请在 TI 初始化脚本中的 `en_AEQ_LMS()` 函数内进行以下带下划线的调整。

```

def en_AEQ_LMS(first_time_power_up=1):

if(first_time_power_up == 1):

board.writeI2C(devAddr,0xB1,0x2C)

read_aeq_init = board.ReadI2C(devAddr,0xB2)

board.writeI2C(devAddr,0xB1,0x27)

board.writeI2C(devAddr,0xB2,read_aeq_init + 5)

board.writeI2C(devAddr,0xB1,0x28)

board.writeI2C(devAddr,0xB2,read_aeq_init + 6)

...

...

```

## 7 其他系统级软件选项

为了在系统级别实现超过 6kV 至 8kV 的 A 类性能，可以在用于接收视频数据的 SoC/处理器内实施额外的选项。在更高 ESD 应力水平下实现 A 类性能的一种常见方法是实现帧缓冲方案，该方案可以丢弃有错误的帧或接收不完全的帧，从而防止视觉干扰。对于依赖人眼判断视频质量的系统而言，这种方法尤其有效，因为在 30Hz 或更高的帧率下，重复的单帧很难被察觉。此方法不需要用作强大系统设计实践的替代方法，因为低基线系统性能与此方法相结合时，可能会导致明显的视觉延迟。

### 步骤 1

配置解串器器件，使其在检测到其中一个 RX 端口发生错误时输出中断。以下示例假设使用的是四通道解串器，并且所有 4 个 RX 端口均处于活动状态。

```

board.writeI2C(desAddr,0x23,0x8F) # Enable interrupts for all RX ports

```

### 步骤 2

通过 SoC 监测中断引脚。当中断触发时，检查中断源以确定原因，并针对可能导致视频路径损坏的情况生成特定于端口的错误标志。请注意，一些错误不会直接影响视频质量，例如奇偶校验或 ECC1，因此它们不受监控。

```

ERR = [0, 0, 0, 0] # RX Port-specific error flags

INT_STS = board.ReadI2C(desAddr,0x24) # Check which RX port triggered the interrupt

if INT_STS & 0x01 != 0: # RX0 interrupt

board.writeI2C(desAddr,0x4C,0x01) # Select RX0

RX_PORT_STS1 = board.ReadI2C(desAddr,0x4D)

RX_PORT_STS2 = board.ReadI2C(desAddr,0x4E)

CSI_RX_STS = board.ReadI2C(desAddr,0x7A)

if RX_PORT_STS1 & 0x10 != 0: # LOCK_STS_CHG

ERR[0] = 1

if RX_PORT_STS2 & 0xC1 != 0: # LINE_LEN_CHG, LINE_CNT_CHG

ERR[0] = 1

IF CSI_RX_STS & 0XOE != 0: # LENGTH_ERR, CKSUM_ERR, ECC2_ERR

ERR[0] = 1

if INT_STS & 0x02 != 0: # RX1 interrupt

board.writeI2C(desAddr,0x4C,0x12) # Select RX1

RX_PORT_STS1 = board.ReadI2C(desAddr,0x4D)

RX_PORT_STS2 = board.ReadI2C(desAddr,0x4E)

CSI_RX_STS = board.ReadI2C(desAddr,0x7A)

if RX_PORT_STS1 & 0x10 != 0: # LOCK_STS_CHG

ERR[1] = 1

if RX_PORT_STS2 & 0xC1 != 0: # LINE_LEN_CHG, LINE_CNT_CHG

ERR[1] = 1

IF CSI_RX_STS & 0XOE != 0: # LENGTH_ERR, CKSUM_ERR, ECC2_ERR

ERR[1] = 1

if INT_STS & 0x04 != 0: # RX2 interrupt

board.writeI2C(desAddr,0x4C,0x24) # Select RX2

RX_PORT_STS1 = board.ReadI2C(desAddr,0x4D)

RX_PORT_STS2 = board.ReadI2C(desAddr,0x4E)

CSI_RX_STS = board.ReadI2C(desAddr,0x7A)

if RX_PORT_STS1 & 0x10 != 0: # LOCK_STS_CHG

ERR[2] = 1

if RX_PORT_STS2 & 0xC1 != 0: # LINE_LEN_CHG, LINE_CNT_CHG

ERR[2] = 1

IF CSI_RX_STS & 0XOE != 0: # LENGTH_ERR, CKSUM_ERR, ECC2_ERR

ERR[2] = 1

if INT_STS & 0x08 != 0: # RX3 interrupt

board.writeI2C(desAddr,0x4C,0x38) # Select RX3

RX_PORT_STS1 = board.ReadI2C(desAddr,0x4D)

RX_PORT_STS2 = board.ReadI2C(desAddr,0x4E)

CSI_RX_STS = board.ReadI2C(desAddr,0x7A)

if RX_PORT_STS1 & 0x10 != 0: # LOCK_STS_CHG

ERR[3] = 1

if RX_PORT_STS2 & 0xC1 != 0: # LINE_LEN_CHG, LINE_CNT_CHG

ERR[3] = 1

IF CSI_RX_STS & 0XOE != 0: # LENGTH_ERR, CKSUM_ERR, ECC2_ERR

ERR[3] = 1

```

### 步骤 3

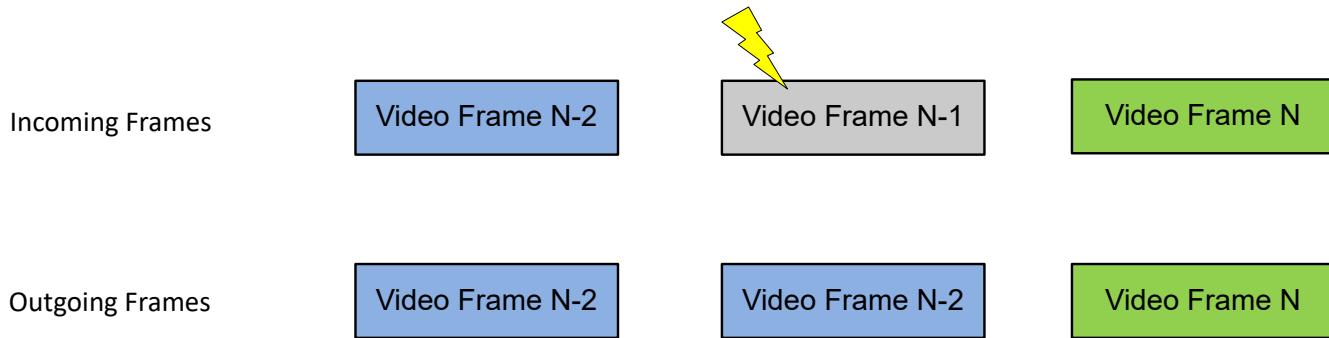

根据特定于端口的错误标志，触发 SoC 来丢弃发生错误的端口的当前视频帧，并将前一帧显示两次。

图 7-1. 帧丢弃和重复示例

## 8 总结

FPD-Link 的系统级 ESD 性能取决于硬件和软件的设计实践。在硬件方面，设计必须确保高速信号的屏蔽以及系统外壳与 PCB 之间的良好接地。在软件方面，可以使用 FEC 和锁定检测调优等工具来提高视频路径的有效 BER。本应用手册中介绍的技术针对的是系统级 ESD 测试，但相同的做法也适用于其他噪声注入 EMC 测试（包括 BCI 或辐射抗扰度），以提高性能。

## 9 参考资料

- ISO , [10605:2023 道路车辆 - 静电放电引起的电干扰的试验方法](#)

## 10 修订历史记录

| <b>Changes from Revision A (October 2024) to Revision B (October 2025)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • 向 FEC 支持的器件列表中添加了 DS90UB971S-Q1 和 DS90UB9724S-Q1.....                    | 9           |

| • 由于对 ESD 性能没有影响，从软件优化中删除了用于锁定检测的 CLK0/CLK1 禁用.....                        | 13          |

| <b>Changes from Revision * (October 2024) to Revision A (October 2024)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式.....                                             | 1           |

| • 添加了其他作者.....                                                             | 1           |

| • 更新了奇偶校验错误示例中的文本（偶校验与奇校验）.....                                            | 8           |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月