# Application Note 在可编程逻辑中使用查询表

#### Owen Westfall

#### 摘要

本应用手册介绍了什么是查询表 (LUT)。本文档还描述了如何在 InterConnect Studio 中使用查询表,该软件是为支持 TI 的 TPLD 系列器件而创建的。

# 内容

| 1 什么是查询表        | 2 |

|-----------------|---|

| 2 考虑将查询表视为多路复用器 | 3 |

| 3 如何配置查询表       | 4 |

| 4 使用查询表减少原理图    | 6 |

| 5 总结            | 8 |

| 6 参考资料          | 8 |

|                 |   |

### 商标

所有商标均为其各自所有者的财产。

## 1 什么是查询表

查询表 (LUT) 是一种执行数字逻辑功能的可编程方式。将 LUT 视为填充真值表的一种方法。例如,表 1-1 是一个空白 3 输入 LUT。这看起来与每 3 个输入真值表都非常相似,但输出由用户定义,而不是由预定义函数定义。

表 1-1.3 输入查询表

| С | В | Α | OUT   |

|---|---|---|-------|

| 0 | 0 | 0 | REG 0 |

| 0 | 0 | 1 | REG 1 |

| 0 | 1 | 0 | REG 2 |

| 0 | 1 | 1 | REG 3 |

| 1 | 0 | 0 | REG 4 |

| 1 | 0 | 1 | REG 5 |

| 1 | 1 | 0 | REG 6 |

| 1 | 1 | 1 | REG 7 |

在离散逻辑中,如果需要的功能是方程式 1,一个简单的离散逻辑设计是使用 3 输入与门,A 输入上有一个非门。使用 LUT,完成该功能只需将 REG 6 设置为 1(逻辑高电平),其余设置为 0(逻辑低电平),如表 1-2 所示

$$Q = \overline{A} \cdot B \cdot C \tag{1}$$

表 1-2. ABC 真值表

| С | В | Α | OUT |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 0   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 0   |

实施 LUT 可实现更灵活的设计,而使用 TPLD1201 等可编程逻辑可让设计人员快速更改逻辑功能,而无需更改电路板或物料清单。

# 2 考虑将查询表视为多路复用器

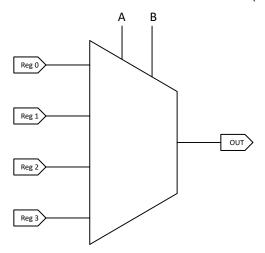

对于熟悉离散逻辑的许多人而言,该逻辑更容易将 LUT 视为存在多路复用器 (MUX)。

图 2-1. LUT 的多路复用器表示

表 2-1. MUX 真值表

| В | Α | OUT   |

|---|---|-------|

| 0 | 0 | 寄存器 0 |

| 0 | 1 | 寄存器 1 |

| 1 | 0 | 寄存器 2 |

| 1 | 1 | 寄存器 3 |

如图 2-1 所示,与逻辑门的实际输入相比,输入更像是选择引脚。当 A 和 B 都为低电平时,输出端存在寄存器 0。当 A 为高电平且 B 为低电平时,输出端存在寄存器 1。当 A 为低电平且 B 为高电平时,输出端存在寄存器 2。当 A 和 B 都为高电平时,输出端存在寄存器 3。这意味着用户在设置 LUT 时不会更改可编程逻辑内的路径,而是随时更改多路复用器推送的值

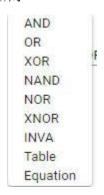

## 3 如何配置查询表

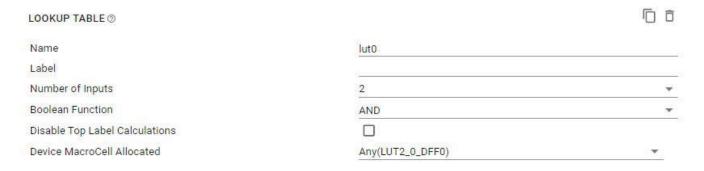

InterConnect Studio (ICS) 是用于配置 TPLD 的软件。ICS 启动后,会选择一个器件。图 3-1 展示了在设计中添加 LUT 时 LUT 的默认配置。可以使用字母数字字符将名称字段设置为任何值。该值随后始终出现在设计空间中块正下方的位置。标签字段是名称字段的多行版本。在该处输入的值始终存在于设计空间中块上方的位置。有关这些字段的更多信息,请参阅 ICS 用户指南。要更改可用输入的数量,请选择"Inputs"下拉菜单并选择所需的数量。可以在 InterConnect Studio 中将较高的输入硬件 LUT 分配给较低的输入计数 LUT。例如,当在设计中使用 2输入 LUT 时,可以分配 3 输入 LUT。在这种情况下,额外的输入在内部连接到接地端,公式/表计算器会自动使该输入始终为 0。

图 3-1. 默认 LUT 配置

#### 配置 LUT 的方法是

- 使用预定义的逻辑功能。这些选项是

- AND

- OR

- XOR

- NAND

- NOR

- XNOR

- INVA

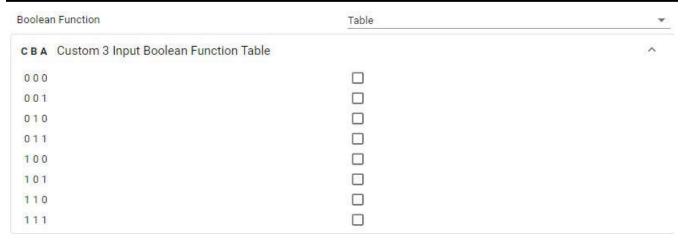

- 使用如图 3-3 中所示的表

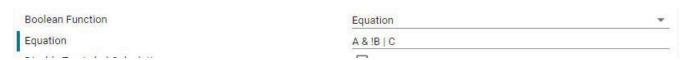

- 编写一个公式,如图 3-4 所示。有关允许使用的字符的详细信息,请参阅 ICS 用户指南。

可以从布尔函数字段中选择这些选项,如图 3-2 所示

图 3-2. LUT 可选选项

www.ti.com.cn 如何配置查询表

图 3-3. LUT 表选项

图 3-4. LUT 公式选项

# 4 使用查询表减少原理图

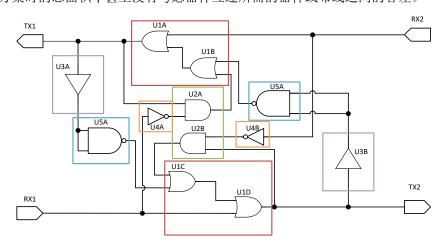

图 4-1 是一个总线仲裁逻辑的示例。这个逻辑电路的用途是确定在任意给定时间哪一个控制器在总线上具有优先级。如果两个 RX 都为低电平,则总线将保持高电平。每个颜色框代表一个不同的物理器件。表 4-1 展示了该设计采用分立式实施方案时的总面积,甚至没有考虑器件互连所需的器件或布线之间的容差。

图 4-1. 总线仲裁原理图

表 4-1. 分立式设计的面积

| v. retrivities |                  |       |    |          |

|----------------|------------------|-------|----|----------|

| 数量             | 器件               | 功能    | 颜色 | 面积 (mm²) |

| 1              | SN74LV32APWR     | 四路或门  | 红色 | 22.0     |

| 1              | SN74LVC2G08DCUR  | 双路与门  | 绿色 | 4.60     |

| 1              | SN74LVC2G07DBVR  | 双缓冲器  | 紫色 | 4.64     |

| 1              | SN74LVC2G04DBVR  | 双反向器  | 橙色 | 4.64     |

| 1              | SN74LVC2G132DCTR | 双路与非门 | 蓝色 | 8.26     |

| 5              | 总计               |       |    | 44.14    |

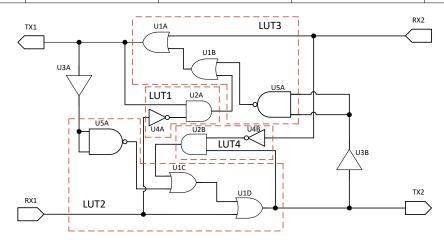

图 4-2. 将原理图分成多个组

www.ti.com.cn 使用查询表减少原理图

通过查看逻辑门某些分组的输入,我们可以将此设计分为 4 组。这些组中的每一个组都可以简化为一个 LUT, 如 图 4-2 所示。

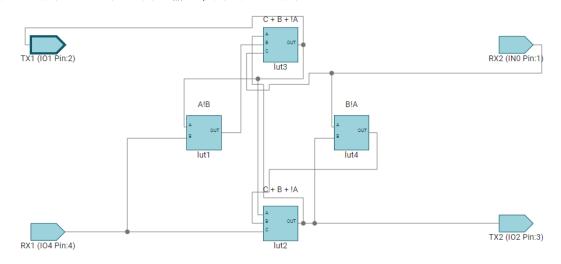

现在已经分离了原理图,因此我们可以将此设计引入 IC 中,我们可以创建一个具有 4 个引脚和 4 个 LUT 的配置,以完成此原理图,如图 4-3 所示。lut1 的配置为 2 个输入,表如表 4-2 所示。lut2 和 lut3 的配置为 3 输入,表如表 4-4 所示。lut4 的配置为 2 输入,表如表 4-3 所示。

图 4-3. 原理图已转换为 IC

表 4-2. lut1 配置表

| В | Α | OUT |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

表 4-3. lut4 配置表

| В | Α | OUT |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

表 4-4. lut2 和 lut3 配置表

| С | В | A | OUT |

|---|---|---|-----|

| 0 | 0 | 0 | 1   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 1   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

## 5总结

查询表是整合系统所需逻辑的一种很棒且灵活的方式。利用 TPLD 系列中提供的 LUT,意味着可以快速更改逻辑,而无需更改电路板。使用 InterConnect Studio 可轻松配置 LUT,并可将分立式逻辑设计精简为一个器件。

有关  $\mathsf{TPLD}$  系列器件的更多信息,请参阅  $\mathit{适用于军事应用的可编程阵列逻辑电路}$  ,有关部分可用器件和用于原型设计的评估模块,请参阅表 5-1。

表 5-1. 订购表

| 器件           | EVM              |

|--------------|------------------|

| 所有 TPLD      | TPLD-PROGRAM     |

| TPLD1201RWBR | TPLD1201-RWB-EVM |

# 6参考资料

• 德州仪器 (TI), ICS 用户指南。

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司