## Application Brief

# 通过 TI 的 TXV 电平转换器产品系列支持时间和偏斜敏感型接口

Joshua Salinas

### 引言

物理层器件 (PHY) 在以太网网络协议中发挥着重要作用,因为它们通过许多不同类型的转换介质对数据进行串行化和解串,从而充当来自外部世界的数据通信的桥梁。PHY 连接到通常集成在 FPGA 或 SoC 中的以太网媒体访问控制器 (MAC)。当 SoC、ASIC 和 FPGA 等大型数字器件切换到较低的内核电压时,接口设计通常会遇到挑战。当以低电压运行时,集成式和独立 MAC 通常无法支持更高的 I/O 电压。系统设计人员通常需要解决 MAC 和 PHY 之间的 I/O 电平不匹配问题,同时仍保持接口的信号完整性。此外,简化千兆位媒体独立接口 (RGMII)等以太网接口具有严格的时序要求,在较低电压下更难以满足这些要求。

本应用简报介绍了 RGMII 的时序要求,并展示了 TI 的高速 TXV 系列如何在克服 I/O 电压不匹配的同时满足 RGMII 时序要求。

## RGMII 时序要求

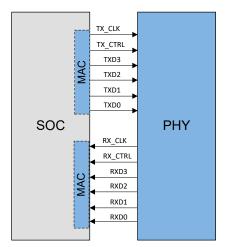

RGMII 是在 MAC 与 PHY 之间使用的接口,可支持 10Mbps、100Mbps 和 1000Mbps 的速度。图 1显示了 MAC 和 PHY 之间的连接。以 1000Mbps 速率运行时,由于数据以双数据速率 (DDR) 信令处理,而较低的速度使用单数据速率 (SDR),因此时序要求更严格。本应用简报中通篇使用 1000Mbps 时序,因为满足此时序要求也会满足 10Mbps 和 100Mbps 时序要求。

图 1. MAC 和 PHY 之间的 RGMII 接口

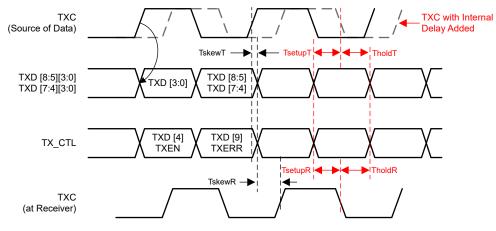

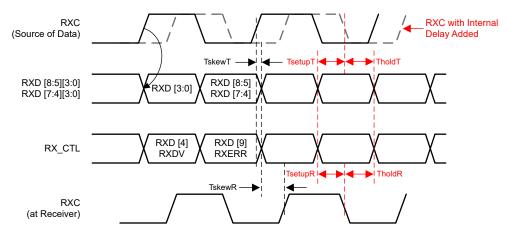

表 1、图 2 和图 3 显示了 RGMII 1.3 版和 2.0 版标准的时序要求。1.3 版规定必须在时钟和数据线之间引入偏斜,通常约为 1.5ns 至 2.0ns。在 2.0 版中,可由 MAC 或 PHY 生成偏斜,并通过  $T_{setupT}$  和  $T_{holdT}$  给出。RGMII 2.0 版时序以红色突出显示。

表 1. RGMII 1.3 版和 2.0 版时序规格

| 符号          | 参数                   | 最小值  | 典型 | 最大值 | 单位 |

|-------------|----------------------|------|----|-----|----|

| $T_{skewT}$ | 数据到时钟输出偏斜<br>(在变送器处) | -500 | 0  | 500 | ps |

## 表 1. RGMII 1.3 版和 2.0 版时序规格 (续)

| 700 11 11 0 11 11 10 10 10 10 10 10 10 10 |                      |     |     |      |    |  |  |  |

|-------------------------------------------|----------------------|-----|-----|------|----|--|--|--|

| 符号                                        | 参数                   | 最小值 | 典型  | 最大值  | 单位 |  |  |  |

| T <sub>skewR</sub>                        | 数据到时钟输入偏斜<br>(在接收器处) | 1   | 1.8 | 2.6  | ns |  |  |  |

| T <sub>setupT</sub>                       | 数据到时钟输出设置            | 1.2 | 2.0 |      | ns |  |  |  |

| $T_{holdT}$                               | 数据到时钟输出保持            | 1.2 | 2.0 |      | ns |  |  |  |

| T <sub>setupR</sub>                       | 数据到时钟输入保持            | 1.0 | 2.0 |      | ns |  |  |  |

| T <sub>holdR</sub>                        | 数据到时钟输入保持            | 1.0 | 2.0 |      | ns |  |  |  |

| T <sub>cyc</sub>                          | 时钟周期时长               | 7.2 | 8   | 8.8  | ns |  |  |  |

| D <sub>cyc</sub>                          | 千兆位的占空比              | 45  | 50  | 55   | %  |  |  |  |

| T <sub>R</sub> /T <sub>F</sub>            | 上升/下降时间<br>(20-80%)  |     |     | 0.75 | ns |  |  |  |

图 2. RGMII 1.3 和 2.0 版发送器时序图

图 3. RGMII 1.3 和 2.0 版接收器时序图

## TXV 输出偏斜测量

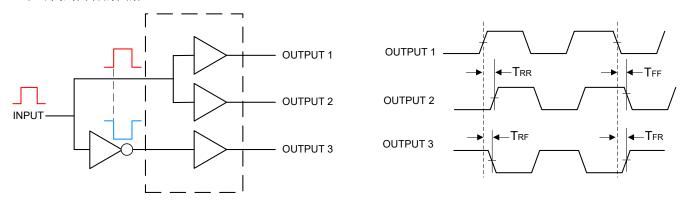

数据表中的输出通道间偏斜  $T_{sk(o)}$  值使用两种类型的偏斜测量值来捕获最坏情况下的偏斜、输出和反相偏斜。在图 4 中可找到两者的图解。

图 4. 输出偏斜 (T<sub>RR</sub>/T<sub>FF</sub>) 和反相偏斜 (T<sub>RF</sub>/T<sub>FR</sub>) 测量

输出偏斜是驱动相同的指定负载时,同一器件在相同转换条件下任意两个输出之间的偏斜差。输出偏斜测量值通过  $T_{RR}$  和  $T_{FF}$  给出。反相偏斜是驱动相同的指定负载时,同一器件在输入转换相反的情况下两个输出之间的偏斜差。反相偏斜测量值通过  $T_{RF}$  和  $T_{FR}$  给出。

### TXV 时序优势

表 2 给出了 TXV 系列和 RGMII 标准之间的时序差异。下面的比较显示,TXV 最坏情况下的时序不超过 RGMII 标准的最大时序参数。这给 MAC、PHY 和 PCB 留下了时序裕度,表明 TXV 产品系列适用于与 RGMII 连接,即使在 1000Mbps 的速率下也是如此。

| χ 2. 1χ το 100/1χ το 100/1χ το 1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/ |                  |                        |           |    |  |  |  |  |

|-----------------------------------------------------------------------|------------------|------------------------|-----------|----|--|--|--|--|

| 符号                                                                    | 参数               | TXV 最大值 <sup>1 2</sup> | RGMII 最大值 | 単位 |  |  |  |  |

| T <sub>sk(o)</sub>                                                    | 输出通道间偏斜          | ± 317                  | ±500      | ps |  |  |  |  |

| $T_R/T_F$                                                             | 上升/下降时间 (20-80%) | 0.48                   | 0.75      | ns |  |  |  |  |

| D <sub>cvc</sub>                                                      | 占空比              | ±4                     | ± 5       | %  |  |  |  |  |

表 2 TXV0106/TXV0108 和 RGMII 时序规格对比

### 结论

FPGA、SoC 和 ASIC 等处理器正朝着更低电压 I/O 发展,通过降低功耗而使客户受益。这会导致 I/O 电压不匹配,但许多电平转换器无法满足严格的时序要求(例如上升/下降时间、通道间偏斜和偏斜敏感接口的占空比失真)。本应用简报展示了 TXV 电平转换器系列如何弥合 I/O 电压差距,同时还提供优化的交流性能并满足 RGMII 等低偏斜接口的严格时序要求。

<sup>&</sup>lt;sup>'</sup> V<sub>CCA</sub> = 1.8V,V<sub>CCB</sub> = 3.3V,C<sub>Load</sub> = 5pF,在 125℃ 时每个数据通道为 250Mbps

<sup>&</sup>lt;sup>2</sup> 在 TXV0106 和 TXV0108 数据表的时序部分还可以找到不同的电压和负载条件

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司