#### Guy Yater

### 摘要

本应用手册介绍了静电放电 (ESD) 保护二极管在高速信号中呈现的容性负载。行业趋势是芯片组尺寸越来越小, 数据速率越来越高,芯片组对瞬态电压的耐受度也随之降低,这增加了对 ESD 保护二极管的需求。更高的数据速 率对寄生电容非常敏感,因为大电容会导致阻抗失配。大电容会使信号失真,并导致数据损坏或无法读取。对于 高速信号,ESD保护二极管需要具有超低电容,以免干扰信号传输。在这种动态情况下,了解高速信号可承受多 大的电容且仍然保持适当的信号完整性变得非常重要。

## 内容

| 1 引言                                            | <mark>2</mark> |

|-------------------------------------------------|----------------|

| 2 为什么阻抗失配事关重大                                   |                |

| 3 USB 3.0 第 1 代                                 |                |

| 4 USB 3.1 第 2 代                                 | 8              |

| 5 总结                                            |                |

| 6 参考文献                                          |                |

| 7 修订历史记录                                        | 10             |

|                                                 |                |

| 插图清单                                            |                |

| 图 1-1. 两线制传输线路的段                                |                |

| 图 1-2. 两线制传输线路的等效电路                             |                |

| 图 2-1. 眼图中的二进制代码                                | 3              |

| 图 2-2. TPD1E04U04DPY 的阻抗来自 192ps 上升时间 TDR       | 4              |

| 图 2-3. TPD4E02B04DQA 的阻抗来自 192ps 上升时间 TDR       | 4              |

| 图 3-1. 无 ESD 保护的 USB 3.0 第 1 代完全合规原理图           | 5              |

| 图 3-2. 无 ESD 保护的 USB 3.0 第 1 代眼图                | 5              |

| 图 3-3. 具有 TPD4E02B04DQA ESD 保护的 USB 3.0 第 1 代眼图 | 6              |

| 图 3-4. 具有 ESD 保护的 USB 3.0 第 1 代完全合规原理图          |                |

| 图 4-1. 无 ESD 保护的 USB 3.1 第 2 代眼图                |                |

| 图 4-2. 具有 TPD4E02B04DQA ESD 保护的 USB 3.1 第 2 代眼图 |                |

| 图 4-3. 具有 0.5pF ESD 保护的 USB 3.1 第 2 代眼图         | 9              |

| · · · · · · · · · · · · · · · · · · ·           |                |

|                                                 |                |

所有商标均为其各自所有者的财产。

引言 www.ti.com.cn

# 1 引言

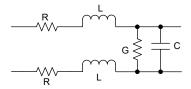

高速信号通常通过阻抗匹配的传输线路进行路由。这可以采用印刷电路板 (PCB) 上的布线或将源端连接到接收端 的电缆形式。ESD 保护二极管通常放置在非常靠近会发生 ESD 的连接器的 PCB 上。PCB 上大多数高速信号的 传输线路架构采用差分信号对的形式。图 1-1 展示了该传输线路的简化模型。传输线路的每个单位长度都由电感 器、电阻器和电容器组成。在单位长度足够小的等效电路中,损耗可以忽略不计,只考虑电感和电容,如图 1-2 所示。特性阻抗  $Z_0$  的公式便会变为:

$$Z_0 = \sqrt{\frac{L}{C}} \tag{1}$$

与差分线路串联的 ESD 保护二极管中通常不存在电感 (对于为每个受保护线路提供一个保护引脚的器件而言尤其 如此),而并联电容约为 0.1pF 至 1pF 量级。这种排列主要为传输线路的节点提供电容,因此这时的特性阻抗变 得更低。

图 1-1. 两线制传输线路的段

图 1-2. 两线制传输线路的等效电路

## 2 为什么阻抗失配事关重大

ESD 保护二极管连接到传输线路的节点处的阻抗出现任何失配都会对信号完整性产生影响。阻抗失配对沿传输线路传播的电压变化信号的影响是将一些电压反射回源极,如果阻抗发生其他变化,其中一些电压会再次反射回来。只要存在阻抗失配的情况,这种来回反射就会通过线路继续进行。根据阻抗失配之间的距离,由于来回反射的信号的任何部分都会被添加到沿线路传播的信号中,因此信号可能会衰减或放大。如果阻抗失配足够大,那么这些反射可能会改变信号的电压电平,使其超出接收器输入逻辑电平,从而导致数据丢失。

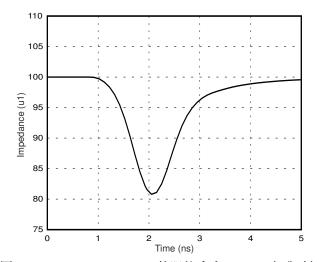

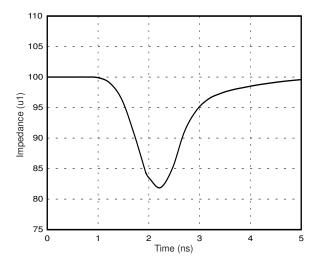

一些行业规范规定了源端或接收端可具有的总寄生电容量,不包括接收器芯片组中的电容。对于 USB 3.1 第 1 代,供电端的此值为 1.25pF;对于第 2 代,此值为 1.1pF。其他行业规格未按值指定电容,而是由时域反射计 (TDR) 使用指定的上升时间测量时对传输线路特性阻抗的影响指定。HDMI 2.0 规范规定,当在 TDR 上升时间小于 200ps 的情况下测量时,在 250ps 的持续时间内没有超过  $100\,\Omega$  ±25% 的单次偏移。图 2-2 和图 2-3 展示了一些德州仪器 (TI) ESD 二极管的阻抗。

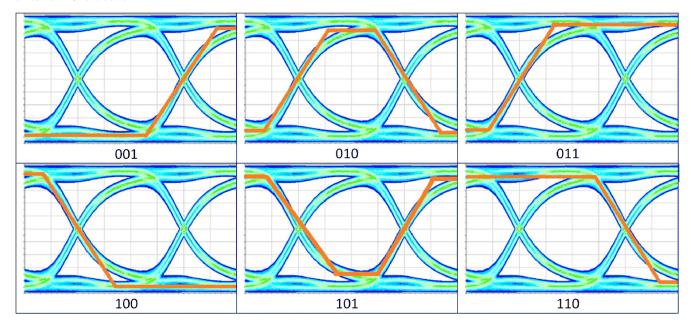

控制传输线路中的阻抗对于保持良好的信号完整性至关重要。数据眼图是一种用于验证良好信号完整性的非常有用的工具。数据眼图由彼此叠加的多位假随机位序列 (PRBS) 信号中的每个单位间隔组成。图 2-1 展示了由眼图映射的六个示例转换。

图 2-1. 眼图中的二进制代码

图 2-2. TPD1E04U04DPY 的阻抗来自 192ps 上升时间 TDR

图 2-3. TPD4E02B04DQA 的阻抗来自 192ps 上升时间 TDR

ww.ti.com.cn USB 3.0 第1代

## 3 USB 3.0 第 1 代

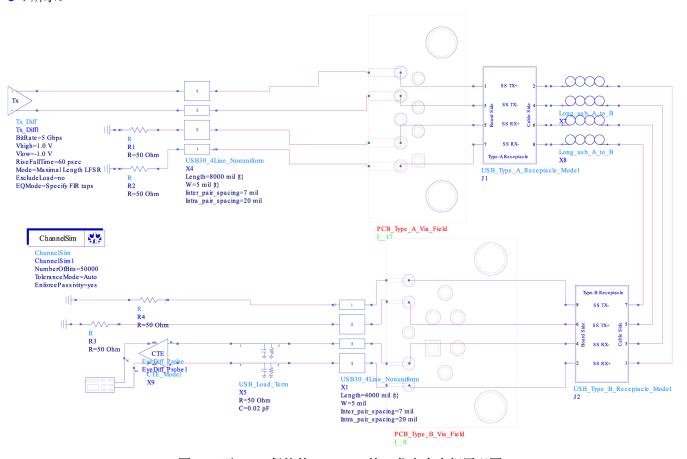

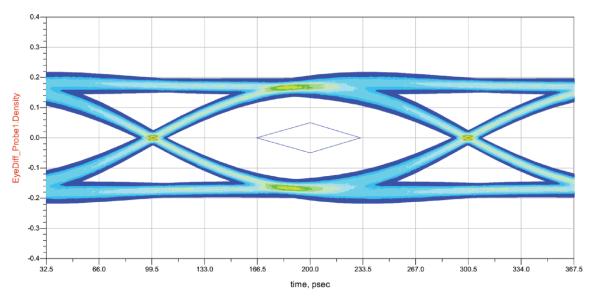

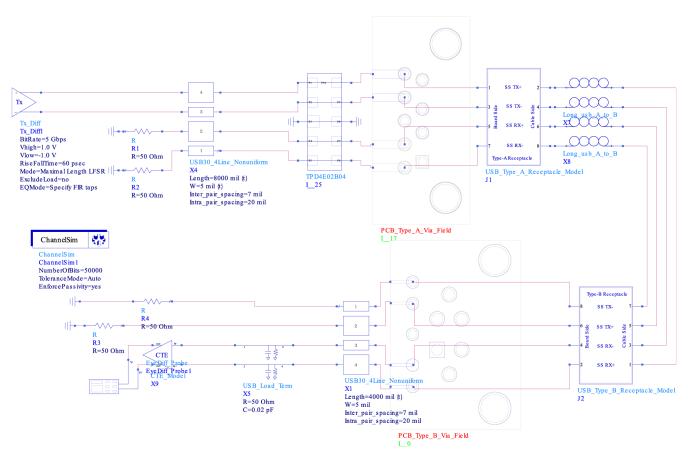

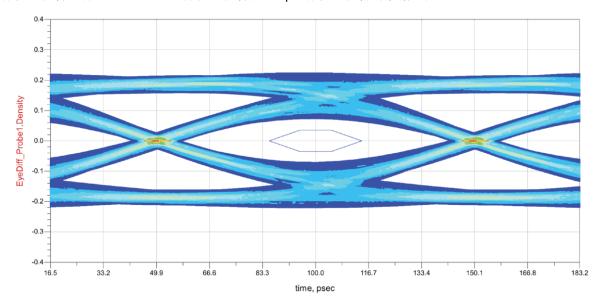

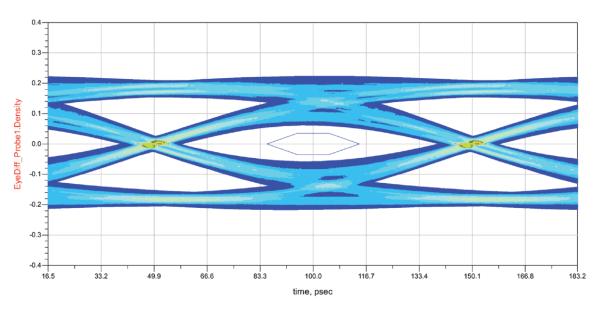

图 3-1 展示了符合 USB 3.1 第 1 代标准的全通道模型,未添加 ESD 保护二极管。产生的眼图如图 3-2 所示。图 3-3 展示了在源极连接器处使用德州仪器 (TI) TPD4E02B04 ESD 保护二极管的同一电路的眼图。原理图模型如图 3-4 所示。

图 3-1. 无 ESD 保护的 USB 3.0 第 1 代完全合规原理图

图 3-2. 无 ESD 保护的 USB 3.0 第 1 代眼图

图 3-3. 具有 TPD4E02B04DQA ESD 保护的 USB 3.0 第 1 代眼图

图 3-4. 具有 ESD 保护的 USB 3.0 第 1 代完全合规原理图

www.ti.com.cn USB 3.0 第1 代

#### 表 3-1 所示为有无 ESD 保护情况下的眼图测量结果:

表 3-1. 有无 ESD 保护的眼图测量结果

|          | 无 ESD 保护 | TPD4E02B04 | 更改       |

|----------|----------|------------|----------|

| 上升时间     | 81.96ps  | 86.18ps    | +4.22ps  |

| 下降时间     | 81.89ps  | 86.11ps    | +4.22ps  |

| 眼高       | 266mV    | 243mV      | -23mV    |

| 眼宽       | 182.8ps  | 177.7ps    | -5.1ps   |

| 抖动 (PP)  | 17.2ps   | 22.8ps     | +5.6ps   |

| 抖动 (RMS) | 2.969ps  | 3.836ps    | +0.867ps |

ESD 保护二极管的额外电容通过减慢上升和下降时间来对上升和下降时间产生影响。这也会对表中的其余值产生负面影响。然而,TPD4E02B04的低电容只会对眼图有细微影响,这使其成为 USB 3.0 第 1 代系统中 ESD 保护的理想选择。TPD4E02B04 在 USB 3.1 第 2 代应用中也取得显著成效。

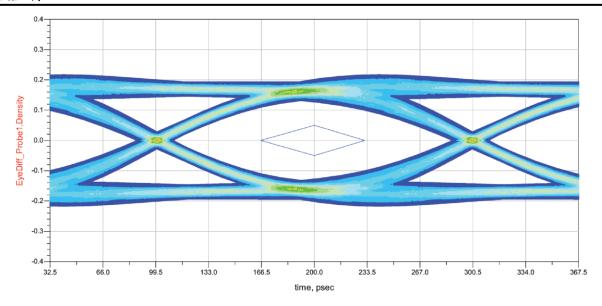

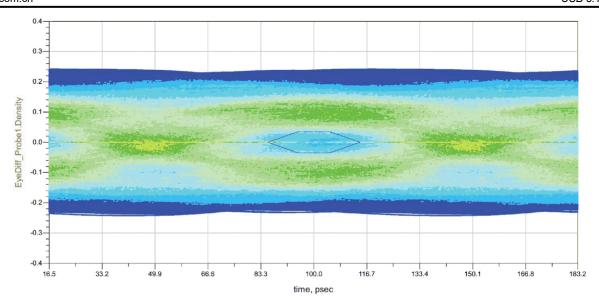

# 4 USB 3.1 第 2 代

虽然 USB 3.1 第 1 代支持 10Gbps 的数据速率,并要求 ESD 保护二极管的电容小于 0.5pF,但 USB 3.1 第 2 代支持 20Gbps 的数据速率,且要求 ESD 保护二极管的电容小于 0.3pF。图 4-1、图 4-2 和图 4-3 分别绘制了无 ESD 保护二极管、有 TPD4E02B04 保护二极管和 0.5pF 保护二极管的数据眼图。

图 4-1. 无 ESD 保护的 USB 3.1 第 2 代眼图

图 4-2. 具有 TPD4E02B04DQA ESD 保护的 USB 3.1 第 2 代眼图

ww.ti.com.cn USB 3.1 第 2 代

图 4-3. 具有 0.5pF ESD 保护的 USB 3.1 第 2 代眼图

表 4-1 列出了有无 ESD 保护情况下的眼图测量结果。

|          | 无 ESD 保护 | TPD4E02B04 | 0.5pF ESD 保护 |  |  |

|----------|----------|------------|--------------|--|--|

| 上升时间     | 63.55ps  | 67.11ps    | 不适用          |  |  |

| 下降时间     | 63.77ps  | 66.15ps    | 不适用          |  |  |

| 眼高       | 132.3mV  | 112mV      | 不适用          |  |  |

| 眼宽       | 84ps     | 81.93ps    | 不适用          |  |  |

| 抖动 (PP)  | 15.6ps   | 18.07ps    | 不适用          |  |  |

| 抖动 (RMS) | 2.725ps  | 3.167ps    | 不适用          |  |  |

表 4-1. 有无 ESD 保护的眼图测量结果

20Gbps 信号仍然能够在 TPD4E02B04 的低电容下保持信号完整性,同时为第 2 代 USB 3.1 发送器提供 ESD 保护。使用电容为 0.5pF 的 ESD 保护二极管时,结果显示了一个没有不同数据的眼图。这直观地展示了高电容对高速数据信号的影响。

各种 PCB 设计有许多不同的规格需求。下面列出了 TPD4E02B04 的一些额外器件,这些器件满足高速信号的超低电容需求,同时利用更少的 PCB 空间。更多的器件可以通过*产品选择工具* 在线找到。这些器件具有各种通道覆盖范围、封装尺寸、双向/单向功能、浪涌额定值和钳位电压。

| 衣 4-2. ESD 保护备件状坯选择   |            |                    |                 |  |  |

|-----------------------|------------|--------------------|-----------------|--|--|

|                       | TPD4E02B04 | TPD1E01B04         | TPD1E05U06      |  |  |

| Vrwm (V)              | 3.6        | 3.6                | 5.5             |  |  |

| 封装类型                  | USON       | DPL、DPY            | SOT-5X3、DPL     |  |  |

| 封装尺寸(长x宽)(mm)         | 2.5x 1     | 0.6x 0.3、1.0 x 0.6 | 1.6x0.8、1.0x0.6 |  |  |

| 双向/单向                 | 双向性        | 双向性                | 单向性             |  |  |

| 通道数量                  | 4          | 1                  | 1               |  |  |

| 钳位电压                  | 6.6        | 7.0                | 18              |  |  |

| IO 电容 ( 典型值 ) (pF)    | 0.25       | 0.18               | 0.4             |  |  |

| IEC61000-4-5 (A)      | 2.0        | 2.5                | 2.5             |  |  |

| IEC61000-4-2 接触 (±kV) | 12         | 15                 | 12              |  |  |

|                       |            |                    |                 |  |  |

表 4-2 FSD 保护器件快速选择

# 5总结

当今的高速信号突破了技术限制。德州仪器 (TI) ESD 保护器件有助于系统级设计人员紧跟趋势,同时提供 IEC 61000-4-2 4 级 ESD 保护。凭借易于在 PCB 上布局的多个超低电容 ESD 保护二极管系列,德州仪器 (TI) 可为高达 20Gbps 的各类应用提供正确的 ESD 保护。

# 6参考文献

- 德州仪器 (TI), 阅读并了解 ESD 保护数据表,应用手册。

- 德州仪器 (TI), ESD 保护布局指南,应用手册。

- 德州仪器 (TI), TI ESD 保护和 HDMI CTS, 应用手册。

ww.ti.com.cn 修订历史记录

# 7 修订历史记录

| Changes from Revision * (July 2016) to Revision A (August 2023) |                         |   |  |

|-----------------------------------------------------------------|-------------------------|---|--|

| •                                                               | 更新了整个文档中的表格、图和交叉参考的编号格式 | 1 |  |

| •                                                               | 更新了出版物以澄清技术方面的信息        | 1 |  |

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司