# TI降压转换器多功能引脚及其应用的简介

#### Stefano Panaro

#### 摘要

如今,越来越多的工程师在设计系统时要求使用更小的元件。本应用报告介绍了某些 TI 降压转换器中的多功能引脚 (TPS62864/6/8/9 中的 VSET/VID、TPS62865/7 和 TPSM82864/6A 中的 VSET/MODE、TPS62800/1/2/6/7/8 中的 VSEL/MODE)。多种应用可以从多功能引脚中受益;这些引脚使工程师能够在设计中引入额外的特性,同时确保尽可能减小解决方案尺寸。

# 内容

| 1 引言                                      |                |

|-------------------------------------------|----------------|

| 2 标准器件操作:电阻测量和数字输入                        |                |

| 3 TPS62864/6/8/9: VSET/VID 引脚             |                |

| 4 TPS62800/1/2/6/7/8:VSEL/MODE 引脚         |                |

| 5 TPS62865/7 和 TPSM82864/6A: VSET/MODE 引脚 |                |

| 6 总结                                      |                |

|                                           |                |

| 插图清单                                      |                |

| 图 1-1. TPS62864/6 典型应用原理图                 | <mark>2</mark> |

| 图 1-2. VSET/MODE 引脚时间多路复用                 | 3              |

| 图 2-1. VSET 引脚上的 R2D 转换                   |                |

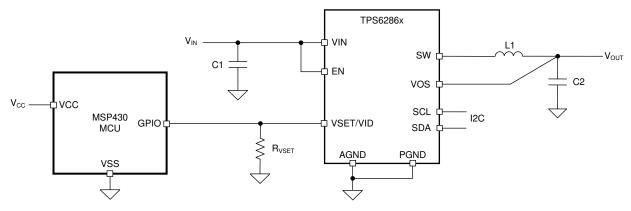

| 图 3-1. 典型应用原理图,包括使用 MCU 的 VSET/VID 驱动电路   | <mark>5</mark> |

| 图 4-1. TPS62801 典型应用原理图                   |                |

| 图 4-2. 典型应用原理图,包括使用 MCU 的 VSEL/MODE 驱动电路  |                |

| 图 5-1. 典型应用原理图 TPS62865/7 - 固定输出电压        |                |

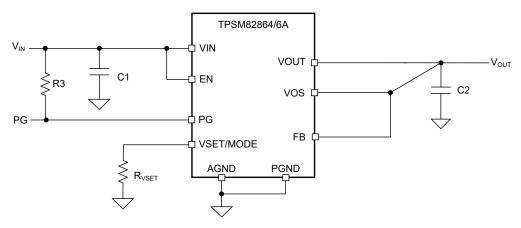

| 图 5-2. 典型应用原理图 TPSM82864/6A - 固定输出电压      |                |

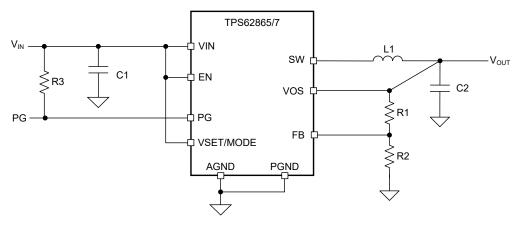

| 图 5-3. 典型应用原理图 TPS62865/7 - 强制 PWM 运行模式   |                |

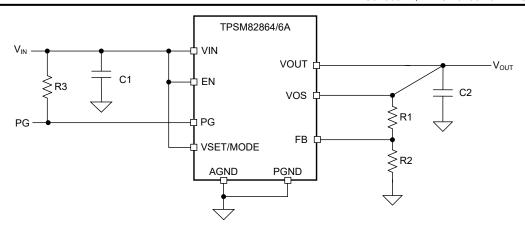

| 图 5-4. 典型应用原理图 TPSM82864/6A - 强制 PWM 运行模式 | 9              |

| 表格清单                                      |                |

| 表 3-1. 数字输入                               | 6              |

| 表 6-1. 摘要表                                | 10             |

| 表 6-2. 其他具有多功能引脚的 TI 降压转换器                | 10             |

| <b>商坛</b>                                 |                |

#### 췸称

所有商标均为其各自所有者的财产。

#### 1 引言

如今,越来越多的工程师在设计系统时要求使用更小的元件。

更小的器件有助于减小电路板尺寸,有益于空间受限的应用(可穿戴设备、个人电子产品等)并降低成本。此外,可以在同一块电路板上集成更多器件,从而提高复杂性并增加单位电路板面积的功能。

过去,电源管理直流/直流降压 IC 对于每个功能都有一个独立的引脚,如电源正常、输出电压设置、运行模式等。这种限制导致了内在的折衷:对于空间受限的应用,设计人员必须选择更简单的元件(不含任何其他特性)来确保尽可能小的封装。对于需要更多特性的更复杂的设计,唯一的选择是采用大封装和具有更多引脚的大型元件。为了克服这种折衷,引入了多功能引脚。多功能引脚就是集成了多种特性的单个引脚。

本应用手册中涉及的 TPS6280x、TPS6286x 和 TPSM8286xA 系列器件能够以小尺寸封装提供许多特性。

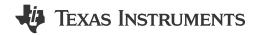

为此,对输入引脚进行了多路复用以提供两种不同的功能(TPS62864/6/8/9 中的 VSET/VID、TPS62865/7 和 TPSM82864/6A 的 VSET/MODE、TPS62800/1/2/6/7/8 的 VSEL/MODE),这些功能通常在时域中分离,如图 1-1 所示。

图 1-1. TPS62864/6 典型应用原理图

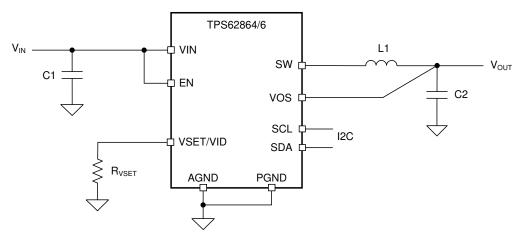

在开始时,即启动后 (t\_startup\_delay),这些 IC 立即使用多路复用引脚进行电阻测量 (R2D 转换,请参阅在超低电源中使用电阻至数字转换器的优势),得到的结果可用于正确设置输出电压值。在运行过程中,该引脚充当数字输入(如图 1-2 所示)以正确配置相应的设置。

图 1-2. VSET/MODE 引脚时间多路复用

本应用手册将介绍多功能引脚的行为,并建议使用一些可以在不同特性之间进行有效多路复用并避免测量误差的驱动电路。

## 2 标准器件操作:电阻测量和数字输入

在 t startup delay 期间,该 IC 需要在多功能引脚上执行电阻测量。

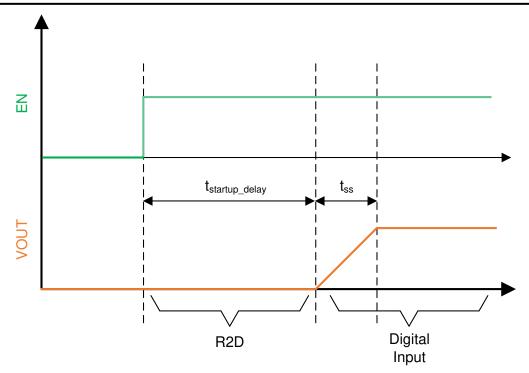

进行电阻测量的方法是在外部电阻 R<sub>VSET</sub> 中注入小电流 I<sub>MEAS</sub> 并读取相应电压 V<sub>MEAS</sub>, 如图 2-1 所示。R<sub>VSET</sub> 值的计算公式为:R<sub>VSET</sub> = V<sub>MEAS</sub> / I<sub>MEAS</sub>

图 2-1. VSET 引脚上的 R2D 转换

此操作必须尽可能精确,因为任何测量错误都可能导致错误的输出电压设置,并可能损坏负载。

例如,请参阅 TPS62864/6 具有 I2C 接口、采用 WCSP 封装的 2.4V 至 5.5V 输入、4A 和 6A 同步降压转换器数据表:R2D 转换器具有一个通过外部电阻施加电流的内部电流源,以及一个可回读电压电平结果的内部 ADC。根据电平设置正确的启动输出电压和 I2C 从器件地址....确保在 R2D 转换期间从该引脚到 GND 没有额外的电流路径或大于 30pF 的电容。否则会设置为错误的值。

设计驱动电路时必须考虑上述限制。

数据表中明确给出了电容限值,但并未具体定义最大额外电流。在大多数情况下,可以将 40nA 视为最大额外电流。

#### 3 TPS62864/6/8/9: VSET/VID 引脚

如前文所述,VSET/VID 引脚用作启动引脚,可以正确设置器件的输出电压和 I2C 地址。在运行期间,该引脚可用于为输出电压选择 VOUT 寄存器 (低电平 = VOUT 寄存器 1;高电平 = VOUT 寄存器 2) (请参阅 TPS62868x 具有 I2C 接口、采用 QFN 封装的 2.4V 至 5.5V 输入、4A/6A 同步降压转换器数据表和 TPS62864/6 具有 I2C 接口、采用 WCSP 封装的 2.4V 至 5.5V 输入、4A 和 6A 同步降压转换器数据表)。

如果设计人员希望将 VSET/VID 引脚设置为低电平,则可以采用标准配置,如图 3-1 所示:只需放置一个接地的电阻即可。在  $t_s$ tartup\_delay 期间,可以执行 R2D 转换而不产生额外寄生效应,而在运行期间会将引脚下拉至 GND。

相反,如果设计人员希望将 VSET/VID 引脚设置为高电平 ) ,则需要与电阻并联一个驱动电路以正确驱动输入。推荐的解决方案是使用一个外部数字电路 (例如 FPGA 或 MCU) 在运行期间正确驱动引脚,如图 3-1 所示。

图 3-1. 典型应用原理图,包括使用 MCU 的 VSET/VID 驱动电路

启动时,GPIO 应处于高阻抗状态: VSET/VID 引脚只能看到用于设置正确输出电压的电阻 (加上 GPIO 寄生效应)。在启动阶段之后,设计人员可以根据改变 GPIO 状态的推荐操作来决定将引脚拉至高电平还是低电平(也可以在运行期间切换引脚极化以适应任何特定需求)。

设计人员只需确保 GPIO 寄生效应低于节 2 中指出的最大寄生效应。

例如, MSP430FR2000 数据表指定了 20nA 的高阻抗漏电流和 5pF 的输入电容,符合上述规格。

### 表 3-1. 数字输入

|                        | 参数                                           | 测试条件                                                                                   | V <sub>cc</sub> | 最小值  | 典型值 | 最大值  | 单位        |

|------------------------|----------------------------------------------|----------------------------------------------------------------------------------------|-----------------|------|-----|------|-----------|

| V <sub>IT+</sub>       | 工与於入區传出口                                     |                                                                                        | 2V              | 0.90 |     | 1.50 | V         |

| VIT+                   | 正向输入阈值电压                                     |                                                                                        | 3V              | 1.35 |     | 2.25 | \ \ \ \ \ |

| V <sub>IT-</sub>       | <b>负向输入阈值电压</b>                              |                                                                                        | 2V              | 0.50 |     | 1.10 | V         |

| VIT-                   | 贝門制八國徂电压                                     |                                                                                        | 3V              | 0.75 |     | 1.65 | V         |

| V.                     | <b>給</b> 》中□濡戶 (/                            |                                                                                        | 2V              | 0.3  |     | 0.8  | V         |

| V <sub>hys</sub>       | 输入电压滞后 (V <sub>IT+</sub> -V <sub>IT-</sub> ) |                                                                                        | 3V              | 0.4  |     | 1.2  | V         |

| R <sub>Pull</sub>      | 上拉或下拉电阻                                      | 对于上拉电阻: V <sub>IN</sub> = V <sub>SS</sub><br>对于下拉电阻: V <sub>IN</sub> = V <sub>CC</sub> |                 | 20   | 35  | 50   | kΩ        |

| C <sub>I,dig</sub>     | 输入电容,仅数字端口引脚                                 | V <sub>IN</sub> = V <sub>SS</sub> 或 V <sub>CC</sub>                                    |                 |      | 3   |      | pF        |

| C <sub>I,ana</sub>     | 输入电容,共享模拟功能的端口引脚                             | V <sub>输入</sub> = V <sub>SS</sub> 或 V <sub>CC</sub>                                    |                 |      | 5   |      | pF        |

| I <sub>lkg(Px.y)</sub> | 高阻抗泄漏电流                                      |                                                                                        | 2V , 3V         | -20  |     | +20  | nA        |

| t <sub>(int)</sub>     | 外部中断时序(设置中断标志的外部触发脉冲<br>持续时间)                | 具有中断功能的端口(请参<br>见框图和引脚功能描述)                                                            | 2V , 3V         | 50   |     |      | ns        |

#### 4 TPS62800/1/2/6/7/8: VSEL/MODE 引脚

VSEL/MODE 引脚的结构与 VSET/VID 引脚类似,但用于不同的设置。在 t\_startup\_delay 期间,RVSEL 电阻可以设置输出电压值,而在运行期间,该引脚允许启用强制 PWM 模式(将其连接到高电平)或节电模式(将其连接到低电平)(请参阅 TPS6280x 采用 6 引脚 0.35mm 间距 WCSP 封装的 1.8V 至 5.5V、0.6A/1A、2.3μA IQ 降压转换器数据表)。

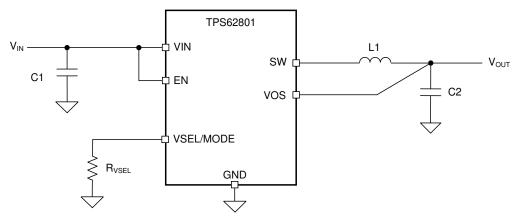

针对 VSET/VID 引脚的注意事项仍然适用。如果设计人员希望在 PSM 下运行器件,则可以采用标准配置,如图 4-1 所示:放置一个接地的电阻即可。在 t\_startup\_delay 期间,可以执行 R2D 转换而不产生额外寄生效应,而在运行期间会将引脚下拉至 GND。

图 4-1. TPS62801 典型应用原理图

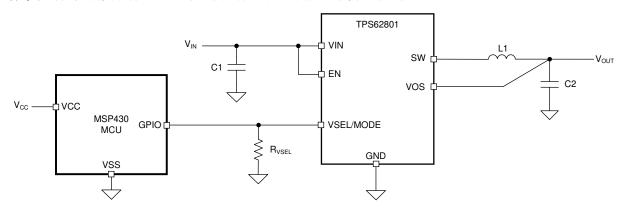

相反,如果设计人员希望将 VSEL/MODE 引脚设置为高电平 (强制 PWM 运行模式),则需要与电阻并联一个驱动电路以正确驱动输入。

推荐的解决方案是使用一个外部数字电路 (例如 FPGA 或 MCU) 在运行期间正确驱动引脚,如图 4-2 所示。与以前一样,设计人员需要确保 GPIO 寄生效应低于节 2 中指出的最大寄生效应。

图 4-2. 典型应用原理图,包括使用 MCU 的 VSEL/MODE 驱动电路

## 5 TPS62865/7 和 TPSM82864/6A: VSET/MODE 引脚

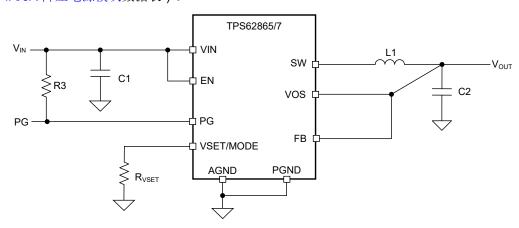

TPS62865/7 和 TPSM82864/6A IC 具有 VSET/MODE 引脚,该引脚在功能上与前面介绍的 VSEL/MODE 引脚相同(请参阅 TPS62865/TPS62867 采用 1.5mm × 2.5mm QFN 封装的 2.4V 至 5.5V 输入、4A 和 6A 同步降压转换器和 TPSM82864A/TPSM82866A 配备集成电感器并采用 3.5mm × 4.0mm 薄超模压塑料 QFN 封装的 2.4V 至 5.5V 输入、4A/6A 降压电源模块数据表)。

图 5-1. 典型应用原理图 TPS62865/7 - 固定输出电压

图 5-2. 典型应用原理图 TPSM82864/6A - 固定输出电压

与之前器件的主要区别在于此处存在额外的引脚 (FB)。当 VSET/MODE 引脚连接到逻辑高电平或逻辑低电平时,FB 引脚可用于通过传统反馈分压器正确选择输出电压。

图 5-3. 典型应用原理图 TPS62865/7 - 强制 PWM 运行模式

图 5-4. 典型应用原理图 TPSM82864/6A - 强制 PWM 运行模式

使用这些器件,选择强制 PWM 模式的较简单解决方案是将 VSET/MODE 引脚连接至高电位,然后使用 FB 分压器正确选择输出电压,如图 5-3 和图 5-4 所示。

最后一种配置的主要优势是可以对 VSET 和 MODE 功能进行去耦,使设计人员能够在不限制输出电压电平选择的情况下有效地选择运行模式。该解决方案无需额外的元件,也不会引入寄生效应,让设计过程简单而直接。

www.ti.com.cn

# 6 总结

表 6-1 汇总了所述的 IC 以及实现引脚辅助功能的推荐解决方案。在某些应用中不需要实现第二个功能。

表 6-1. 摘要表

| 器件                                 | 推荐解决方案                                                     |  |  |  |  |  |

|------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| TPS62864/6 和 TPS62868/9 (VSET/VID) | 通过 GPIO 驱动实现 VID 功能<br>(请参阅节 3):<br>VSET/VID = 低电平 → 高电平   |  |  |  |  |  |

| TPS62800/1/2/6/7/8 (VSEL/MODE)     | 通过 GPIO 驱动实现 MODE 功能<br>(请参阅节 4):<br>VSEL/MODE = 低电平 → 高电平 |  |  |  |  |  |

| TPS62865/7 (VSET/MODE)             | 设置 VSET/MODE = 高电平,实现强制 PWM<br>使用 FB 电阻分压器(请参阅节 5)         |  |  |  |  |  |

| TPSM82864/6A (VSET/MODE)           | 设置 VSET/MODE = 高电平,实现强制 PWM<br>使用 FB 电阻分压器(请参阅节 5)         |  |  |  |  |  |

| TPS62901/2/3 (MODE/S-CONF)         | 设置 MODE/S-CONF = 高电平,实现强制 PWM 使用 FB 电阻分压器(实现方式与节 5 相同)     |  |  |  |  |  |

纵观 TI 产品系列,多功能引脚不限于用于选择运行模式 (PFM/PWM 或强制 PWM),还用于各种特性。 表 6-2 列出了一些具有多功能引脚的其他 TI 降压转换器。

表 6-2. 其他具有多功能引脚的 TI 降压转换器

| な。 大心大 ロンの 配 川神山 ・・ |                                                                                                                            |  |  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 器件                  | 多功能引脚                                                                                                                      |  |  |  |  |  |  |

| TPS62810/1/2/3/6-Q1 | <ul> <li>MODE/SYNC: PFM/PWM(低电平)、强制 PWM(高电平);该引脚可用于与外部频率同步。</li> <li>COMP/FSET: 一个电阻定义了控制环路的补偿以及开关频率(如果未在外部同步)。</li> </ul> |  |  |  |  |  |  |

| TPSM82810/3         | <ul> <li>MODE/SYNC: PFM/PWM(低电平)、强制 PWM(高电平);该引脚可用于与外部频率同步。</li> <li>COMP/FSET: 一个电阻定义了控制环路的补偿以及开关频率(如果未在外部同步)。</li> </ul> |  |  |  |  |  |  |

| TPS62912/3          | <ul> <li>EN/SYNC:禁用(低电平)、启用(高电平);该引脚可用于与外部频率同步。</li> <li>S-CONF:该引脚用于选择开关频率、展频、输出放电和同步范围。</li> </ul>                       |  |  |  |  |  |  |

# 7 修订历史记录

| CI | hanges from Revision * (July 2021) to Revision A (November 2022) | Page |

|----|------------------------------------------------------------------|------|

| •  | 更新了整个文档中的表格、图和交叉参考的编号格式                                          | 1    |

| •  | 添加了 TPSM82864/6A                                                 | 1    |

| •  | 添加了 <i>典型应用原理图 TP</i> S62865/7 - 强制 PWM 运行模式 图像                  | 8    |

| •  | 添加了 <i>典型应用原理图 TPSM82864/6A - 强制 PWM 运行模式</i> 图像                 | 8    |

| •  | 向表添加了 TPSM82864/6A (VSET/MODE)                                   | 10   |

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司