# 基于TI AFE8092 的AAU TX 射频链路设计分析

Jason Ren

#### 摘要

5G AAU 的小尺寸,低功耗和低成本的趋势对 AAU TRX 板的器件提出了更高的集成化要求,对射频收发器件 Transceiver 来说,需要集成更多的射频通道。AFE8092 是 TI 高性能,大带宽的多通道射频收发器件。包括了 8 个发射通道,8 个接收通道,2 个反馈通道,所有通道均为射频直采架构。各个射频链路的大带宽,高性能使得 AFE8092 适用于大部分 4G/5G 基站 TRX 射频板应用场景。AFE8092 的发射(TX)链路包含了 12Gsps 采样速率的 DAC,包含了 DSA(Digital Step Attenuator)。每个发射通道数字部分包含功率检测模块,也可实现功放保护(PAP)功能。本文将在对 AFE8092 的发射链路基本功能介绍的基础上,对 AAU TX 链路的设计方法进行分析。

#### 目录

| 1     | 引言    |                                                   | 2                            |

|-------|-------|---------------------------------------------------|------------------------------|

|       |       | 8092 TX 链路介绍                                      |                              |

|       |       | 数控衰减控制模块                                          |                              |

| 4     | 2.2   | 功放保护模块                                            | 3                            |

|       |       | NCO 模块及数字插值模块                                     |                              |

|       |       | AFE8092 的 TX 链路设计方法分析                             |                              |

|       |       | 发射链路频率规划                                          |                              |

|       |       | 3.1.1 发射链路杂散说明                                    |                              |

|       |       | 3.1.2 发射链路频率规划举例                                  |                              |

| ;     |       | 发射链路射频指标分析                                        |                              |

|       |       | AFE8092 的 RX 链路预算分析                               |                              |

|       |       | 静态灵敏度分析                                           |                              |

| 4     |       | 灵敏度对交调特性影响分析                                      |                              |

|       |       | 文献                                                |                              |

| - ,   |       | <b>7-14</b> • • • • • • • • • • • • • • • • • • • |                              |

|       |       | 图/表                                               |                              |

| т.    | 4     |                                                   |                              |

| Figur |       | AFE8092 TX 链路示意图                                  |                              |

| Figur | re 2. | TX DSA 快速切换增益和 GPIO 映射关系表                         |                              |

| Figui | re 3. | PAP 模块功能框图                                        | 4                            |

| Figui | re 4. | 直流失调产生交织杂散机制                                      | 5                            |

| Figui | re 5. | 增益失衡产生交织杂散机制                                      | 6                            |

| Figui | re 6. | 高次谐波频率分布                                          | 7                            |

| Figur | re 7. | 静态灵敏度分析流程示意图                                      | Error! Bookmark not defined. |

## 1 引言

在 AAU 的 TRX 板射频部分设计过程中,需要考虑包括整个射频链路的各项射频指标是否能够达到协议要求,增益、噪声、线性度、EVM、ACPR 和是否满足 SEM 指标都在考量范围之内。TI 的 8T8R2FB 的射频直采收发器芯片 AFE8092 的各项指标优异,且射频直采架构相比于传统零中频架构去除了本振泄露以及镜像产物,降低滤波器设计压力;同时,射频直采架构使得各个通道配置中心频点灵活,方便平台化及多频段应用。

本文对 AFE8092 的 TX 链路部分功能进行了介绍,基于此介绍了涉及 AAU 的 TRX 板过程中需要进行的考量

## 2 AFE8092 TX 链路介绍

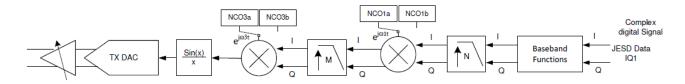

AFE8092 共包含 8 个 TX 链路,每个 TX 链路结构框图 Figure 1 所示。

Figure 1. AFE8092 TX 链路示意图

其中,模拟端包括 40db 可控范围的数控衰减器(DSA),支持到 12Gsps 采样率的 DAC;数字端包括一个 Sinc 滤波器,功放保护模块,两级数字混频器,两级 DUC 以及 JESD/SERDES 模块。

下面会重点对几个模块进行详细介绍。

### 2.1 数控衰减控制模块

每个TX链路DAC出口集成了DSA,其动态范围为40db,步进1db,校正后差分精度+/-0.1dB。该DSA在大部分场景下是用来做大信号防护或者批补/温补的链路增益补偿,一般在器件稳定运行后不会有太多的调整动作。AFE80xx支持两种控制DSA模式:SPI控制和GPIO控制。

在 SPI 控制模式中,TI 会为客户提供 API 进行区分通道控制或多通道一并控制。注意,在调用 API 进行多通道同时控制时,从底层电路的角度看,仍然是串行地单通道地进行 DSA 控制,控制 速度不取决于机器周期,取决于系统控制器件的 SPI 速率。更多的 API 实现及功能问题可参考 TI 的技术文档《AFE80xx 软件编程应用手册》。

在 GPIO 控制模式中,需要由客户在控制前通过 API 配置 GPIO 高低电平组合和切换 DSA 值的映射关系。这种控制模式相比于 SPI 控制模式增益切换步进较大,但是 GPIO 控制也带来了更快的切换速度,适合 DSA 快速控制的场景。在控制过程中,可支持最小颗粒单个 GPIO 控制单个 TX 通道在两个增益间切换,也可支持单通道切换 8 个 TX 通道的增益,映射关系对照表如图 2 所示。以第 7 种配置模式为例,2 个 GPIO 可同时控制 2 个 TX 通道。2 个 GPIO 共包含 4 种高低电平组合状态,使得器件在这种模式下,可在 4 组增益下快速切换。在进行切换时,用户可以根据实际增益控制需求进行在 00-01-10-11GPIO 值间的任意切换。同时,在启用 GPIO 控制模式后,增益会从 SPI 控制模式下自动切换到预设的 GPIO 对应增益上,覆盖掉 SPI 模式中设置的批补/温补 DSA 值。

| # GPIO pins | Description                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------|

| 1           | single GPIO pin for all 8 TX chains to select between main and one swap DSA state                    |

| 2           | two GPIO pins common to all 8 TX chains, to select among 4 DSA settings (main and 3 swap DSA states) |

| 2           | one GPIO pin every 4 TX chains to select between main and one swap DSA state                         |

| 4           | two GPIO pins every 4 TX chains to select among 4 DSA settings (main and 3 swap DSA states)          |

| 4           | one GPIO pin every 2 TX chains to select between main and one swap DSA state                         |

| 8           | separate GPIO pin for each TX chain o select between main and one swap DSA state                     |

| 8           | two GPIO pins every 2 TX chains to select among 4 DSA settings (main and 3 swap DSA states)          |

Figure 2. TX DSA 快速切换增益和 GPIO 映射关系表

#### 2.2 功放保护模块

在无线整机工作过程中,存在两种下行增益控制模式:前向反馈控制和反向反馈控制。一般情况下这两种反馈模式的思路都是基于功率检测结果,由 FPGA 控制数字域功率或者调整 AFE 内部的 DSA 增益。前向反馈控制是由 FPGA 进行数字域功率检测后,基于功率检测结果进行增益控制。该增益控制模式的增益控制范围较低,主要是做精确数字控制;反向反馈控制模式是由反馈链路的功率检测节点进行功率检测,该功率检测节点一般设置在 FPGA 数字域内,基于功率检测结果,通过控制 AFE 内部的 DSA 增益来进行温补/批补控制,通过控制 FPGA 内数字增益进行频补控制。

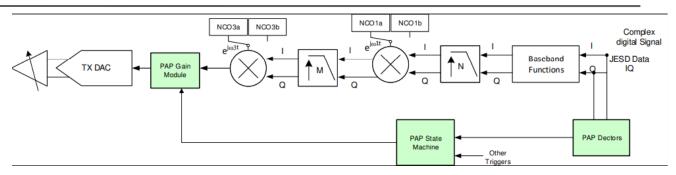

以上两种控制模式的模式都是针对整机工作在正常的链路增益下的情况,所进行的控制模式设计。但是在整机工作不正常时,可能会发射链路出现异常大功率信号,甚至烧毁后级功放。整机设计需要对这种异常进行快速响应。但是对于异常事件,如 PLL 失锁及 204 告警,系统难以通过反向反馈进行快速响应,同时难以通过前向反馈检测到异常事件。所以 AFE 内部集成了功放保护模块,基于异常事件告警和大功率检测结果进行快速通道关断,防止烧毁系统功放。其功能框图如下图所示。

Figure 3. PAP 模块功能框图

在此不对该模块进行详细描述,详细内容可参考 TI 技术文档《基于特定信号选择 TI AFE79xx 的 PAP 参数方法》。

## 2.3 NCO 模块及数字插值模块

AFE8092 是射频直采架构的收发器,进入 DAC 的信号是射频信号,因此在 DAC 前配置了数字混频器(Mixer),用来将等效低通基带信号搬移到射频上去。Figure 3 中有级联的两个混频器及NCO,用户不需要对这两个模块进行单独操作,器件内部的 Firmware 会自动对这两个模块进行配置,保证最终进入 DAC 的信号频率为配置的 NCO 频率。AFE8092 的 NCO 支持两种步进配置模式,分别为(1)1kHz 步进模式和(2)2949.12M/2^32 步进配置模式。

一般来说,对于系统要求的频率步进大于 1kHz 的情况下,我们一般用配置模式 1,方便系统频率设计。在系统要求的频率步进小于 1kHz 的情况下,则需要我们使用 NCO 工作在步进模式 2。在这种步进模式下,我们需要将 NCO 可工作频率适配到系统需求频率上。如下面例子所示,在系统要求频率步进(由 BBU 侧基带决定)为 25kHz 时,同时也要保证 NCO 工作在步进小于 1kHz 模式下,我们要将 NCO 配置在 3500M 附近,则可以用数据处理工具按照下面的伪代码进行频点选取。该工具是对系统要求支持的频率和 AFE8092 支持的 NCO 频率进行穷举并配对,选取合适的NCO。最终,选择矩阵中为"True"的频点为 NCO 工作频点:

```

for M=min_M:step:max_M

for N=min_N:step:max_N

res=M*25-N*2949120/2^32;

if rem(res,1)=0

flag(M,N)="True";

else

flag(M,N)="False"

end

end

```

在数字链路上,DAC 速率较高,为了降低后级的 JESD 模块和 DAC 之间的交互速率,在变频前会用数字插值模块进行数字插值处理,将 JESD 出口的数据速率(Data Rate)插值为 DAC 采样速率。AFE8092 的插值模块非常灵活,可适配不同的 DAC 采样率和 Data Rate 组合,组合配置模式会在器件手册中进行详细说明。

## 3 基于 AFE8092 的 TX 链路设计方法分析

射频发射链路设计时需要进行频率规划及射频性能考量。其中,频率规划会针对工作频带内可能存在的杂散进行分析,并通过选取合适的采样率和参考钟频率来规避或减小杂散;射频性能带外主要关注频谱辐射模板,带内主要关注 EVM 系统指标,将二者分解为链路各个器件的指标,进行单器件单指标分析。本节将基于 AFE8092 针对这两方面设计考量进行分析。

#### 3.1 发射链路频率规划

#### 3.1.1 发射链路杂散说明

发射机的频谱中,除了有用信号外,还存在着不想要的杂散,3GPP协议会对基站发射频谱进行约束。除开硬件电路设计产生的杂散外,部分杂散是可预测的,因此我们会进行频率规划防止这部分可预测的杂散落入感兴趣频带内。一般来说,可预测的杂散包括参考钟谐波杂散,交织杂散,主信号谐波杂散,交调杂散及截位直流分量。

参考钟频率(REF)的 N 次谐波的杂散频率为 N\*REF,该杂散可能落入感兴趣频段内。表现为固定位置杂散,不会随主信号频率更改而更改。这种 N 次谐波杂散在设计时容易规避,AFE8092 支持多种参考钟频率选择,可以通过修改参考钟频率规避该杂散。

AFE8092 的交织杂散分布位置和采样率及信号频率相关性较大,且分布较为明确,可大致分为三种。一种是由于交织 DAC 的直流失调导致的 Fs/2 的固定位置杂散,如下图所示,对 AFE8092 的一个发射链路进行举例。由于每个交织 DAC 存在直流失调,在单独的交织 DAC 的频域表现上是直流分量,但是经过交织模块后,会调制到 Fs/2 的频率上。同时,由于 AFE8092 内部的数字部分分路传输,也会带来部分 Fs/4 杂散。

Figure 4. 直流失调产生交织杂散机制

另一种是由于交织 DAC 间的增益失衡带来的 Fs/2±Fout 交织镜像杂散。如下图所示,单个 DAC 采样结果是无法观测到交织镜像杂散的。由于各个交织 DAC 的增益可能存在失衡的情况,单个 DAC 上叠加的乘性因素,经过交织模块会导致在输出位置出现交织镜像杂散。

#### Figure 5. 增益失衡产生交织杂散机制

第三种是交织杂散和主信号谐波 HDn 相关的杂散,HDn 一部分是由非线性产生,也有可能由差分布线失衡产生。杂散分布位置和 Fs 及 HDn 都相关,位于 n/4\*Fs±HDn 位置。可通过对主信号进行频率搬移,观察该杂散移动方向及移动频率大小进行定位。

主信号谐波杂散 HDn 主要是由链路上的 DAC 非线性产生,分布在 Fout\*N 的位置,一般来说谐波阶次越高,谐波杂散功率越低。另外高次谐波也会被后级滤波器抑制掉且也不会落在感兴趣带宽内,因此,一般不会对过高次的 HDn 进行考察。HDn 谐波杂散较容易定位,移动输出信号频率可以明显观测到。

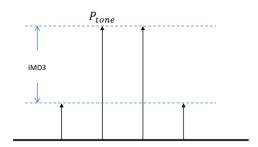

交调杂散也是由 DAC 的非线性特性产生,在 DAC 输出双音时可以观测到。该杂散分布于 2\*F1-F2 和 2\*F2-F1 的位置。DAC 类器件是硬限幅器件,OIP3 和 IMD3 不会按照传统非线性器件的计算方法计算,因此,TI 在器件手册中会对 IMD3 进行测试条件约束,不会声明 OIP3 指标。

截位直流分量是由于 AFE8092 在进行链路组帧时,部分应用场景会将采样数据部分低位 bit 进行截位,截位运算在时域中存在取余操作,该截位会带来一部分直流分量,经过 NCO 搬移后,射频口会在 NCO 位置观测到该杂散。一般会通过在截位后,将所有采样点进行减法操作,减法操作相当于在时域上添加窗长较长的矩形窗,在频域上表现为负向的 Sinc 函数,对该直流杂散进行抑制。

#### 3.1.2 发射链路频率规划举例

基于上文对杂散位置的说明,下面对实际应用场景进行发射链路频率规划举例分析。进行分析时,设计者需要基于两个参数进行考察:信号 DPD 带宽和信号中心频率。设计者会根据这两个参数对其它频率参数进行推算,看是否满足系统要求。先根据信号 DPD 带宽确定可使用的数据速率。而采样率和可支持的数据速率相关,在数据速率确定后,可以确定可支持的采样率。确定采样率,信号带宽及信号频率后,可对 3.1.1 节中描述的杂散进行考察,原则上尽量防止杂散落入带内或频谱模板要求严格的位置。

以信号带宽为 100MHz, 信号频率为 3500MHz 的系统举例。信号带宽为 100MHz, DPD 带宽 300MHz 足够, 因此可以选择 368.64Msps 的数据速率, 8847.36Msps 的采样率。

接下来开始考察带内杂散。首先考察最容易定位的参考钟谐波杂散,当选取 491.52MHz 的参考钟频率时,参考钟 7 阶杂散会落入信号带内。因此,可选择 368.64MHz 的参考钟频率,防止谐波落入带内;或者可以选择 184.32M 的参考钟频率,尽管谐波也会落入带内,但是由于谐波阶次较高,在系统指标要求不高的情况下也可以接受。

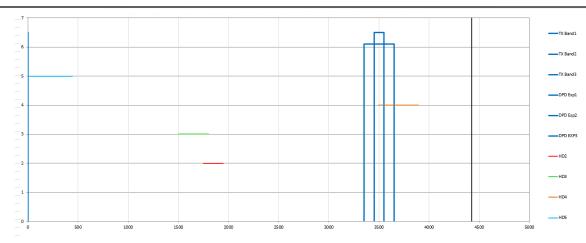

其次,考察交织杂散及 HDn 被混叠出的杂散。单独的交织杂散由于离主信号较远,一般对后级的滤波器参数挑战不大。而 HDn 混叠出的杂散可能落入带内,无法通过滤波器抑制掉,因此需要重点考察。TI 提供了方便的杂散计算工具可以,如下图所示,工具标明了主信号频带,DPD 信号频带以及 HDn 谐波位置。可以看到,低次谐波均落入 DPD 带外,落入带内的仅有 HD4,功率较低可以忽略。

Figure 6. 高次谐波频率分布

带外杂散分析思路和带内杂散一致,分析方法相同,只是杂散抑制指标有所差异,在此不进行赘述。

#### 3.2 发射链路 EVM 指标分析

在设计发射射频系统时,我们主要关注带内的矢量调制误差(EVM)指标和带外的频谱辐射模板 (SEM)。其中,尽管 SEM 也会受各个器件射频指标影响,但是分析较为简单,因此,在本节重点介绍将 EVM 指标分解到射频器件的指标的分析方法。

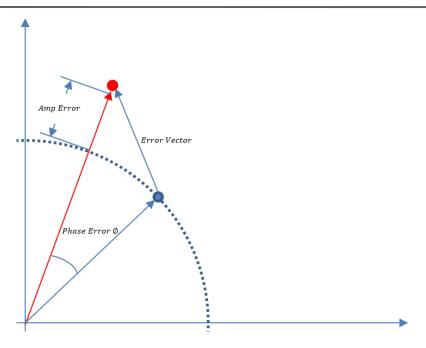

在系统指标分解到射频部分时,系统侧不会再关注 BER 等指标,而是会重点考察 EVM 指标,再将 EVM 指标分解到各个射频器件上。EVM 指标一般计算方法是将单帧内调制信号的每个星座点偏移理想星座点的偏差值做均方根计算,计算公式如下:

$$\text{EVM}_{frame} = \sqrt{\frac{\sum_{j=1}^{L_p} \sum_{i=1}^{N_c} (R_{i,j} - S_{i,j})^2}{N_c L_p P_0}}$$

式中, $L_p$ 是帧数, $N_c$ 是子载波个数, $R_{i,j}$ 是实际发射符号星座图位置, $S_{i,j}$ 是理想符号星座图位置。

从图 7 的说明可能更容易理解,实际符号和理想符号星座图位置可能存在一定的偏差,该偏差在帧内做均方根则是系统定义的 EVM 指标。从该图中也可以看出,实际发射信号的幅值误差和相位误差都有可能对 EVM 产生恶化的影响。

Figure 7. EVM 计量方法示意图

如上文所说,实际符号点的幅值误差和相位误差都会对 EVM 有恶化影响。从幅值误差的角度考虑,带内的白噪声和子载波间的非线性产物会对 EVM 产生影响;从相位误差的角度考虑,输出信号的相位噪声会对 EVM 产生影响,这几类影响会叠加到综合 EVM 指标上,公式如下:

$$EVM_{total} = \sqrt{EVM_{WN}^2 + EVM_{PN}^2 + EVM_{nonlinearity}^2}$$

下面对这几类影响因素进行详细描述。

### 3.2.1 带内白噪声对 EVM 的贡献

带内的白噪声较容易理解,白噪声叠加到业务信号幅值上会产生幅值误差。白噪声的产生途径有很多,在此列举几个:

- (1)链路上有源器件本身的热噪,这部分热噪在 PA 端贡献最大;

- (2) DAC 的量化噪声带来的底噪,这部分噪声已经包含在 AFE80xx 手册描述的 NSD 指标中,AFE80xx 的 NSD 指标为-156dbFs/Hz,业界领先。AFE80xx 的噪声在整个链路器件中对 EVM 恶化贡献最低;

- (3) CFR 削峰噪声,在几种主流的削峰算法中,都会带来带内均匀噪声,无法避免。

白噪声对 EVM 影响公式如下:

$$EVM_{WN} = NSD + 10logBW + PAPR + P_{backoff} + 3$$

其中NSD+10logBW为噪声积分带宽内功率,PAPR 为信号峰均比, $P_{backoff}$ 为数字信号回退值, $EVM_{WN}$ 为 dB 值,需转换为常用的百分比值:

$$EVM_{percentage} = 100 * 10^{(EVM_{dB}/20)}$$

一般在实际系统中,我们会考虑数字信号回退和峰均比,防止在高峰均比情况下出现数据溢出的情况。以 AFE80xx 为例,在 245.76Msps 数据速率,输出信号峰均比 7dB,13dB 满功率回退的情况下,均匀噪声对 EVM 的贡献为 0.28%左右。

#### 3.2.2 信号相噪对 EVM 的贡献

如图 7 所示,相位噪声会对输出信号在星座图上的位置产生相位信息偏移,贡献 EVM 恶化指标。工程经验上来讲,对相噪功率谱密度在 0.1 倍子载波间隔值到总信号带宽进行积分,得出的值为相噪对 EVM 的贡献:

$$EVM_{PN} = \int_{0.1f_{SC}}^{BW} PNdf + 3$$

式中,BW 为信号带宽, $f_{sc}$ 为子载波间隔,PN 为相噪功率密度曲线。AFE8092 的 DEMO 板进行测试时,会使用干净的外供参考钟,尽量减小参考钟相噪对 EVM 的恶化贡献。

#### 3.2.3 非线性产物对 EVM 的贡献

在射频下行链路中,包含如 DAC,放大器,混频器等非线性器件,这些非线性器件无法避免地产生非线性产物,对于双音测试来讲,非线性产物会分布在双音两侧,如下图所示,非线性产物功率 IM3 和单音功率及输出 $OIP_3$ 关系为 $IM3 = 3P_{tone} - 2OIP_3$ 。

Figure 8. 双音非线性产物示意图

在多子载波系统中,信号交调产物会落入不同子载波的带内,对受影响的子载波而言,这部分非 线性产物被看作是干扰信号,影响幅值和相位进而影响 EVM。

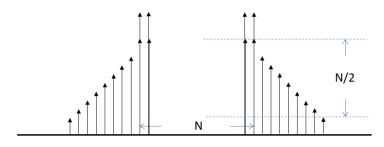

下面分析非线性产物对多载波系统 EVM 的影响,以下图作为示意图进行举例说明:

Figure 9. 多载波系统非线性产物示意图

在N载波OFDM系统中,第i组载波间产生的非线性产物功率和单音功率及器件 $OIP_3$ 关系为

$$IM3_i = 3P_{tone} - 20logN - 20IP_3$$

每个子载波位置存在 N/2 个非线性产物,基于上式可以推算出该子载波位置的非线性产物功率为

$$E_{sc,j} = \sum_{i=1}^{N/2} IM3_i = IM_3 + 10log \frac{N}{2}$$

统计所有子载波的非线性产物总功率则为

$$E_{total} = \sum_{j=1}^{N} E_{sc,j} = IM_3 + 10\log N/2 + 10\log N$$

结合双音 IMD3 计算公式,可得出载波带内非线性产物总功率和 OIP3 及载波功率关系为

$$E_{total} = 3P_{rms} - 20\log N - 20IP_3 + 10\log\frac{N}{2} + 10\log N$$

在有用信号看来,非线性产物直接叠加在带内影响信噪比,因此非线性产物对 EVM 的影响为

$$EVM_{nonlinearity} = 3P_{rms} - 20IP_3 + C$$

式中,C取值为 0-3 之间的常数,取决于基带信号特性。从上式中可以看出,*EVM*<sub>nonlinearity</sub>和信号功率成正比,和 OIP3 成反比。TI 的 Transceiver 器件不会对 OIP3 进行标注,而是对 IMD3 进行标注,因此针对 Transceiver 的 EVM 贡献分析可表达为

$$EVM_{nonlinearity} = P_{rms} + IMD_3 + C$$

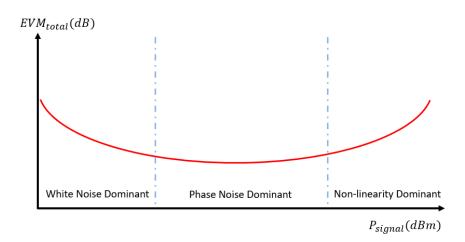

上面三部分分析了白噪声、相噪和非线性特性对输出 EVM 的贡献。可以看到,白噪声贡献是随着信号功率增大而减小,相噪贡献随着信号功率增大而增大,非线性贡献随着信号功率增大而增大,三部分对整体 EVM 的贡献为均方根关系。一般来说,信号功率和 EVM 的关系呈现浴盆曲线特性,如下图所示。

Figure 10. 输出信号功率和 EVM 关系示意图

在信号功率较低时,带内均匀噪声对 EVM 贡献较大,相噪和非线性产物的贡献埋在均匀噪声下; 当信号功率增高时,带内均匀噪声贡献降低,同时非线性产物功率还不高,此时 EVM 最低,大部 分由相噪贡献;当信号功率再次上升,此时非线性产物功率最高,EVM 大部分由非线性产物贡献。

如下图所示,为 AFE8092 实测 EVM 数据,100M NR 源输出功率-9.6dbm,输出 EVM 可达到0.33%水平。

Figure 11. AFE8092 EVM 实测数据

## 4 总结

本文介绍了 TI Transceiver AFE8092 的下行链路架构及基本功能。基于 AFE8092 的射频指标,在下行链路频率规划和 EVM 考量方法两方面进行了详细介绍。下行链路频率规划列举了下行链路可能存在的杂散位置,产生机制及定位方法。EVM 考量方法定量介绍了链路中各个因素对 EVM 产生的影响,定性介绍了不同输出功率条件下 EVM 的变化。

## 5 参考文献

AFE80xx 器件手册: AFE8092\_RTM\_MAY2021\_datasheet

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司