# 双 TDA4x 系统解决方案

Neo Wang, Mahmut Ciftci, and Linjun Meng

#### 摘要

Jacinto TDA4x SoC 系列提供具有高能效架构的高度集成、高性能处理器,实现优化的高级驾驶辅助系统 (ADAS)解决方案。根据对性能、安全性、功耗和应用的要求,在某些情况下可能需要双 TDA4x 解决方案来实现系统目标。本应用报告介绍了基于 TDA4x 片上系统 (SoC) 的双 SoC 解决方案的动机和高级系统注意事项。

## 内容

| 1 引言                       |  |  |  |  |  |  |  |  |

|----------------------------|--|--|--|--|--|--|--|--|

| 2 双 TDA4 系统                |  |  |  |  |  |  |  |  |

| 2.1 双 TDA4x SoC 系统图        |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

| 0                          |  |  |  |  |  |  |  |  |

| <b>在</b> 图净                |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

| 图 2-1. 典型双 TDA4 级联系统图      |  |  |  |  |  |  |  |  |

| 图 3-1. 典型的摄像头复制解决方案        |  |  |  |  |  |  |  |  |

| 图 3-2. 典型的摄像头系列解决方案        |  |  |  |  |  |  |  |  |

| 图 4-1. 使用第二闪存的引导流程         |  |  |  |  |  |  |  |  |

| 图 4-2. 仅使用第一闪存的引导流程        |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

| 2.2 系统注意事项和 BOM 优化 3 摄像头连接 |  |  |  |  |  |  |  |  |

|                            |  |  |  |  |  |  |  |  |

| 表格清里<br>表 1-1_TDA4VM 典型配置  |  |  |  |  |  |  |  |  |

#### 商标

所有商标均为其各自所有者的财产。

### 1引言

Jacinto TDA4x 处理器系列是一个包含软件兼容产品的可扩展平台。根据系统要求,TDA4x SoC 系列提供不同性能、功率和特性集的不同产品,以供客户选择。当前,TDA4VM 已量产,详情可参见 TDA4VM 产品页面 [1]。表1-1 显示 TDA4VM 的典型 IP 配置。有关更多信息,请参阅 *DRA829/TDA4VM 技术参考手册* [2]。

表 1-1. TDA4VM 典型配置

|        |    | 处理器/加速器                  |                                   |                  |                           |                  | 接口                |                   |                         |                                  |

|--------|----|--------------------------|-----------------------------------|------------------|---------------------------|------------------|-------------------|-------------------|-------------------------|----------------------------------|

| TDA4VM | IP | Arm                      | Arm-R5F                           | DSP              | GPU                       | MMA              | DDR               | 捕捉                | PCle                    | 以太网                              |

|        | 特性 | 2xA72<br>(~25K<br>DMIPS) | 3x 双 R5F<br>(3x<br>~12KDMIP<br>S) | 1xC7x+<br>2xC66x | GE8430<br>(100<br>GFLOPs) | 1xMMAv1<br>8TOPs | 1x32b@42<br>66Mhz | 2x CSI-Rx<br>(4L) | PCIe 第 3<br>代:4x<br>2DL | 8p 交换机<br>+<br>1x RGMII<br>(MCU) |

以下情况中可能需要双 TDA4x 级联解决方案:

- 性能要求

- MPU 上运行的一般处理、深度学习和客户应用的性能要求对于单个 SoC 来说可能过高。

- 功能安全

- 为满足功能安全要求,可能需要第二个 TDA4x SoC 作为冗余 SoC, 在主 TDA4x 器件异常时成为备用系统。

- 功率和散热考虑

- 双 SoC 解决方案改善了功率和热分布,系统负荷可以在 SoC 间分配,以更好地管理功率和热量。

- IO 接口

- 在高度集成的系统解决方案中,单个 SoC 可能无法提供足够的外设接口,包括摄像头、PCle、以太网、CAN、LIN 接口。为满足系统接口要求,可能需要双 SoC 解决方案。

所有 Jacinto TDA4VM SoC 都配置有以太网和 PCle 接口。这意味着,所有 TDA4x 系列处理器都可以通过以太网和 PCle 互连,以实现双 SoC 系统要求。后面部分将讨论此类解决方案的系统考虑事项。

#### 2 双 TDA4 系统

#### 2.1 双 TDA4x SoC 系统图

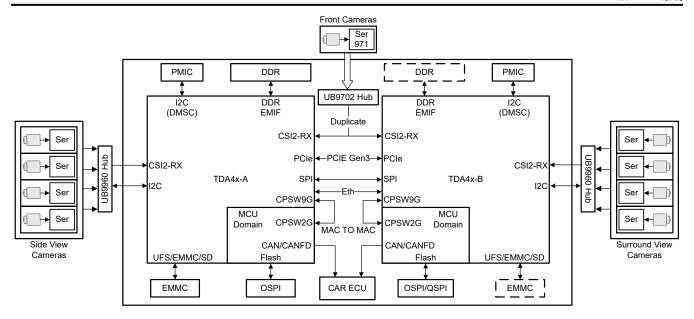

图 1 是一个基于双 TDA4VM SoC 的高度集成 ADAS 系统的示例。此 ADAS 系统在一块 PCB 上集成了前置摄像 头、4 个环视摄像头和 4 个侧视摄像头,支持以下主要功能:

- 摄像头通过 MIPI CSI2-RX 接口连接

- 每个 CSI2-RX 端口支持 4 通道,每通道的数据速率高达 2.5Gbps,每个 CSI2-RX 端口总计高达 10Gbps。

- 每个 TDA4x SOC 需要一个专用电源 (PMIC) 解决方案,但次级 TDA4x PMIC 可连接到主 TDA4x 以实现唤醒功能。

- 前置摄像头系统通常需要高分辨率传感器,以实现复杂的功能,例如物体检测、泊车辅助等。在这些场景下,需要多个深度学习模型协同工作。摄像头原始数据可通过 FPDLink 等解串器分别复制到两个 TDA4x。

- 4个侧视摄像头和 4个环视摄像头可分别部署在两个 TDA4x 上,以平衡功能、处理负载、功率和热分布。

www.ti.com.cn 双 TDA4 系统

图 2-1. 典型双 TDA4 级联系统图

- 两个 TDA4x SoC 可以通过 PCIe 和以太网等各种高速接口连接。两个 TDA4x SoC 之间的 PCIe、以太网和 SPI 互连不需要 PHY 芯片,引脚可以通过 PCB 直接连接。例如,两个 TDA4x SoC 之间的以太网交换机 (CPSW9G) 互连、或者同一芯片中的 CPSW9G 和 CPSW2G 互连,都是采用 MAC 到 MAC 的支持,而不需要以太网 PHY。

- PCIe 控制器支持第 3 代,每通道 8Gbps,每个 PCIe 控制器最多 4 通道,总吞吐量为 32Gbps。

- 8端口以太网交换机支持:

- 所有端口均支持 2.5Gb HSGMII、1GB SGMII/RGMII

- 两个端口支持 5Gb/10Gb XFI/USXGMII

- 每个 TDA4 需要 eMMC、OSPI/QSPI 等外部 DDR 存储器和闪存,才能发挥出色的性能。然而,在某些情况下,可以进一步优化,以平衡成本和系统设计。

#### 2.2 系统注意事项和 BOM 优化

基于双 TDA4x 的系统可利用 TDA4x SoC 特性,节省系统成本。TDA4X SoC 集成 ADAS 系统所需的许多关键处理器和 IP,包括图像信号处理 (ISP)、提供 ASIL-D 安全支持的 MCU/安全岛、以太网交换机等。这种集成尽可能减少了所需的外部元件。引导和存储用的 PMIC、DDR、闪存是 TDA4 需要的主要外围器件。此外,双 SoC 解决方案还可以进一步节省成本,包括:

外部存储和闪存,包括 DDR、EMMC 和闪存。

- 每个 TDA4 都需要外部 DDR 存储器。

- MMC 通常用于存储高级 OS 系统映像和文件系统。如果次级 TDA4x 上高级操作系统 (HLOS) 的引导时间没有严格限制,那么这些引导映像可以通过 PCIe 或以太网从主 TDA4x SoC 进行传输。因此,在此情况下可优化次级 eMMC。

- 为了实现更快启动,引导映像通常保存在 NOR 闪存 (OSPI/QSPI)中,不过 OSPI 比 QSPI 更快,也更昂贵。

- 如果要求次级 TDA4x SoC 与主 TDA4 同时启动,那么需要两个引导闪存,因此可以对主 TDA4x SoC 使用 OSPI 并对次级 TDA4x SoC 使用 QSPI,以提供具有成本效益的解决方案。

- 如果次级 TDA4x SoC 可以在主 TDA4 启动后引导,那么可以优化次级引导闪存,因为次级 TDA4x 引导映像可以通过 PCIe 或以太网从主 TDA4x SoC 传输。

但是,有关系统 BOM 的最终决定要基于系统要求,以优化性能和系统成本。

# 3 摄像头连接

一般在两个 TDA4x SoC 上连接和处理侧视摄像头和环视摄像头。但是,前置摄像头通常需要实现更多 L2、L2+功能,例如物体检测、语义分割、车道保持/变道辅助等。当一个 TDA4x SoC 的算力无法支持这样的多功能的实现时,前置摄像头输入需要传送到第二个 TDA4x SoC 进行额外处理。此部分介绍将前置摄像头连接到 TDA4x SoC 的两种方法。

## 3.1 将前置摄像头输入复制到两个 TDA4x SoC

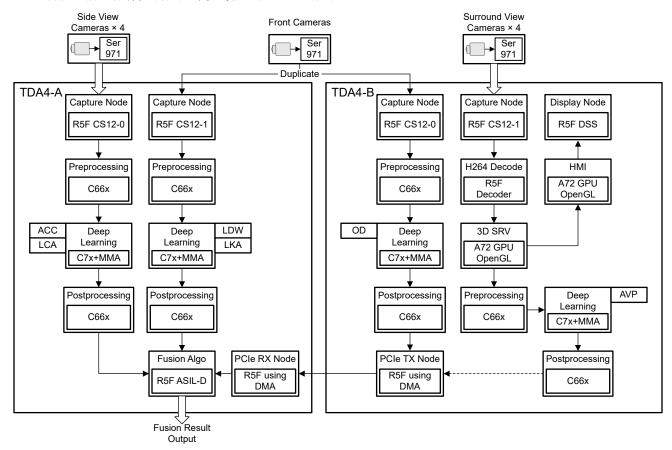

此解决方案将摄像头源数据复制到两个 TDA4x SoC (TDA4-A、TDA4-B),每个 TDA4x 处理器实现不同的 ADAS 功能。前置摄像头功能分布参考实施如图 3-1 所示。

图 3-1. 典型的摄像头复制解决方案

#### 主 TDA4-A 中的摄像头:

- 前置摄像头用于监控前置摄像头对象:

- 摄像头数据通过 CSI2-1 端口输入

- C66x DSP 进行预处理(例如格式/灰度转换、ROI设置)

- 对深度学习模型进行推理,在 C7x+MMA 深度学习加速器中实现车道偏离预警 (LDW) 和车道保持辅助 (LKA) 功能

- C66x DSP 进行后处理(例如画线和内插)并将结果输出到融合节点

- 侧视摄像头用于监控从侧面来的车辆和物体:

- 摄像头数据通过 CSI2-0 端口输入

- C66x DSP 进行预处理/后处理

- 在 C7x+MMA 中对变道辅助 (LCA) 和自适应巡航控制 (ACC) 的深度学习模型进行推理

- 将结果输出到融合节点

## 次级 TDA4-B 中的摄像头:

- 前置摄像头用于监控前方物体:

- 摄像头数据通过 CSI2-0 端口输入

- C66x DSP 完成预处理/后处理

- 对深度学习模型进行推理,在 C7x+MMA 中实现物体检测 (OD) 功能,例如交通灯辨识 (TLR)、交通标志辨识 (TSR)

- 将结果输出到 PCIe TX 节点

- 环视摄像头用于检测汽车低速行驶时周围的环境:

- 摄像头数据通过 CSI2-1 端口输入

- 编解码器节点对于录制是可选的 (DVR)

- 用于 3D 渲染的 GPU 节点

- C66x DSP 进行预处理/后处理

- 对深度学习模型进行推理,在 C7x+MMA 中实现自动代客泊车 (AVP) 和自动泊车辅助 (APA) 功能

- 将结果输出到 PCle TX 节点

#### 融合:

- 来自 TDA4-B 的所有结果通过 PCIe TX/RX 节点传输到 TDA4-A, 然后输入到融合节点。

- 所有结果无论来自 TDA4-A 或 TDA4-B 都在融合节点中进行装配,然后输出最终的结果。

# 3.2 仅将前置摄像头连接到一个 TDA4x

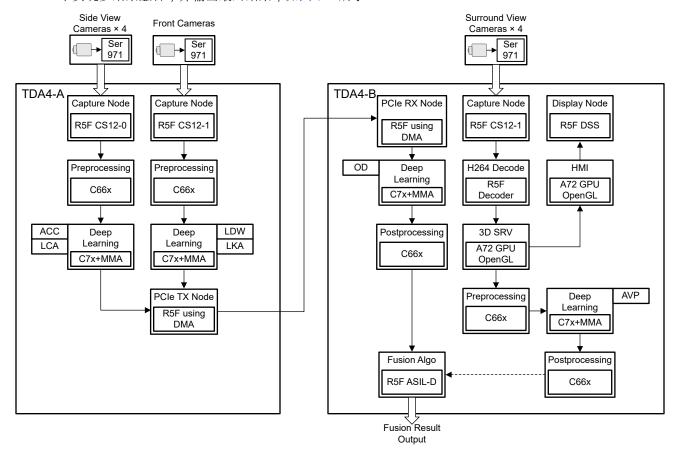

此解决方案将前置摄像头和侧视摄像头连接到 TDA4-A,并将中间结果传输给 TDA4-B 进一步处理。然后在 TDA4-B 中实现多结果融合,并输出最终结果,如图 3-2 所示。

图 3-2. 典型的摄像头系列解决方案

此场景与前一场景的不同之处在于,TDA4-A 的结果通过 PCIe TX 节点传输。深度学习推理中间结果由 TDA4-B 节点中的 PCIe RX 节点接收,这些结果作为源数据交给 TDA4-B 进一步处理。环视摄像头结果与深度学习结果一起被输入到融合节点。最终结果从 TDA4-B 输出。

## 4 引导顺序解决方案

如节 2.2 所示,根据系统 BOM,可能需要不同的外围设备和引导模式,这会导致不同的引导流程和引导时间。根据具体的硬件设计,需要使用软件来处理引导流程。此部分介绍两种典型的引导顺序解决方案,以供参考。

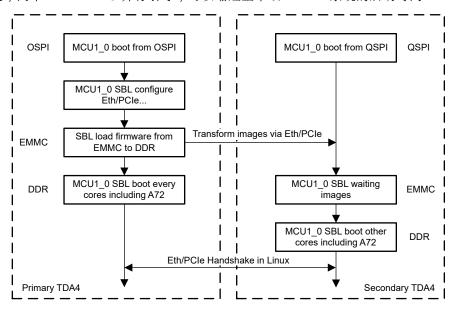

# 4.1 基于双闪存的引导解决方案

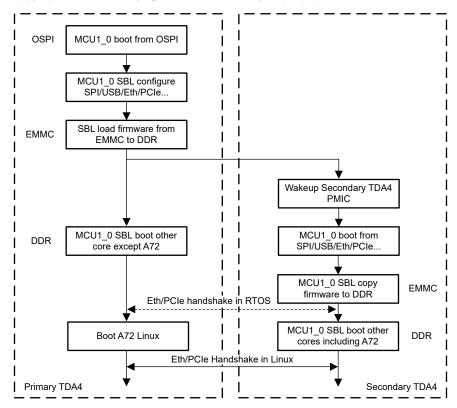

在这种情况下,两个 TDA4x SoC 都有自己的闪存用于系统引导。图 4-1 显示双 TDA4x 的引导顺序。此引导顺序解决方案的优势是,两个 TDA4x SoC 并行引导,可以缩短整个双 TDA4x 系统的启动时间。

图 4-1. 使用第二闪存的引导流程

#### 主要特性和过程如下:

- 主和次级 TDA4 应使用 OSPI/QSPI 引导模式。

- 引导映像存储在 OSPI(针对主 TDA4x)或 QSPI(针对次级 TDA4x)中,以加快引导速度。此外,MCU2\_x/MCU3 x 内核的系统映像也可以存储在闪存中,可进一步缩短启动时间。

- 主 TDA4x SoC 需要初始化和配置一些硬件接口,例如以太网和 PCle。这些硬件配置需要负责将映像随后传输 到次级 TDA4x SoC。

- 主 TDA4x SoC 继续引导流程,在传输次级 TDA4x 的映像后唤醒其他内核。次级 TDA4x SoC 首先从它的 QSPI 引导,然后从主 TDA4x SoC 接收映像后引导其他内核。

- 主 TDA4x SoC 继续引导流程,在传输次级 TDA4x 的映像后唤醒其他内核。次级 TDA4x SoC 将首先从它的 QSPI 引导,然后从主 TDA4x SoC 接收映像后引导其他内核。

# 4.2 基于单闪存的引导解决方案

在这种情况下,主 TDA4 只使用一个引导闪存,如图 4-2 所示。这种引导顺序的优点是系统成本较低,缺点是系统引导时间较长,因为次级 TDA4x SoC 依赖主 TDA4x SoC 来启动引导。

图 4-2. 仅使用第一闪存的引导流程

#### 主要特性和过程如下:

- 主 TDA4x SoC 使用 OSPI/QSPI 引导模式,同时次级 TDA4x SoC 引导根据硬件支持使用 SPI/USB/Eth/PCIe 模式。

- 主 TDA4x SoC 将从自己的 OSPI 引导,然后通过 I2C 连接唤醒次级 TDA4x PMIC,再初始化和配置用于引导 次级 TDA4x SoC 的硬件接口。同时,它会将其他内核(A72 除外)的引导映像从 EMMC 加载到 DDR。

- PMIC 启用后,次级 TDA4x SoC 将首先从主 TDA4x SoC 接收引导映像,并开始引导。此后,它会将所有内核映像从 EMMC 加载到 DDR,以引导整个系统。

- 两个 TDA4x SoC 引导都完成后,可通过以太网/PCIe 进行后续的数据传输。

#### 5 基于 PCIe 的多 SoC 演示

Jacinto 7 SDK [3] 提供一个参考应用来展示多 SoC 概念。在本例中,使用 PCle 接口连接了三个 TDA4x EVM [4]。首先,EVM 捕捉摄像头画面,这些画面通过 PCle 上的第二个 EVM 传输到第三个 EVM。第三个 EVM 驱动显示屏,在屏幕上显示摄像头画面。

如需了解更多详情,请参阅 https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/06\_02\_00\_21/exports/docs/vision\_apps/docs/user\_guide/APP\_PCIE\_VIDEO.html

有关 PCIe 和以太网连接的更多详细信息,请参阅[5]和[6]。

www.ti.com.cn 参考文献

# 6 参考文献

- 1. TDA4VM 产品页面

- 2. 德州仪器 (TI): DRA829/TDA4VM 技术参考手册

- 3. 适用于 TDA4VM/DRA829 Jacinto 处理器的软件开发套件

- 4. TDA4VM/DRA829 评估模块

- 5. PCle 互连解决方案

- 6. 基于 DRA829 EVM 的 MAC2MAC 解决方案

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司