## Application Note

# BQ77915 功能安全时基故障率、FMD 和引脚 FMA

### Sandy Xu

#### 内容

| ,                  |   |

|--------------------|---|

| 1 概述               | 2 |

| 2 功能安全时基故障 (FIT) 率 |   |

| 3 故障模式分布 (FMD)     |   |

| 4 引脚故障模式分析(引脚 FMA) |   |

| ,                  |   |

| 商标                 |   |

所有商标均为其各自所有者的财产。

### 1 概述

本文档包含有关 BQ77915 (PW [TSSOP] 封装)的信息,可为设计功能安全系统提供帮助。所提供的信息包括:

- 根据业内可靠性标准估算的半导体元件的功能安全时基故障 (FIT) 率

- 基于器件主要功能的元件故障模式及其分布 (FMD)

- 引脚故障模式分析(引脚 FMA)

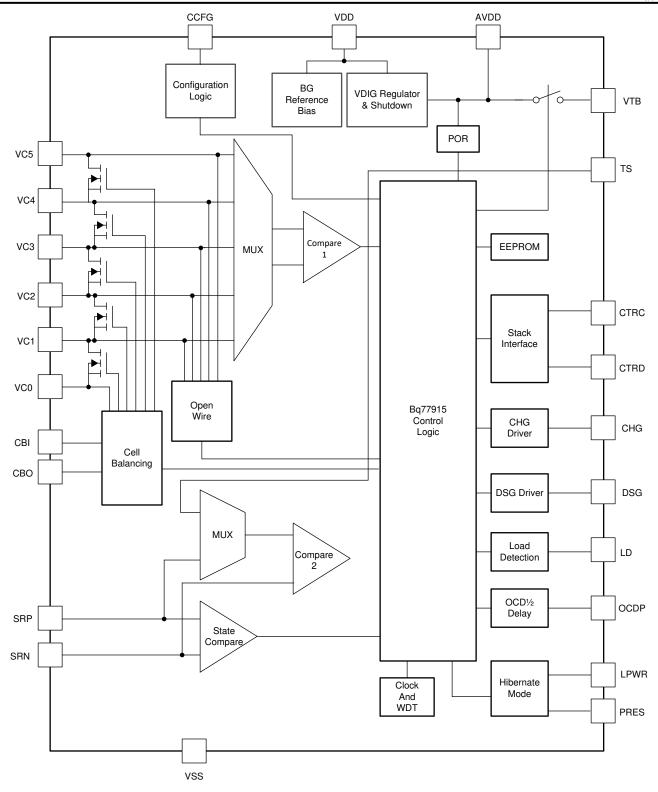

图 1-1 所示为可供参考的器件功能方框图。

图 1-1. 功能方框图

BQ77915 器件是通过质量管理开发流程开发的,但未遵循 IEC 61508 或 ISO 26262 标准。

### 2 功能安全时基故障 (FIT) 率

本部分根据业内广泛使用的两种不同的可靠性标准,提供了BQ77915的功能安全时基故障 (FIT)率:

- 表 2-1 提供了符合 IEC TR 62380/ISO 26262 第 11 部分要求的时基故障率

- 表 2-2 提供了符合 Siemens Norm SN 29500-2 要求的时基故障率

表 2-1. 元件故障率符合 IEC TR 62380/ISO 26262 第 11 部分的要求

| 时基故障 IEC TR 62380/ISO 26262 | 时基故障(每 10 <sup>9</sup> 小时的故障次数) |

|-----------------------------|---------------------------------|

| 元件的总时基故障率                   | 17                              |

| 芯片时基故障率                     | 3                               |

| 封装时基故障率                     | 4                               |

表 2-1 中的故障率和任务剖面信息摘自可靠性数据手册 IEC TR 62380/ISO 26262 第 11 部分:

• 任务剖面:表 11 中的电机控制

功耗: 1.0mW TBD mW气候类型: 全球范围表 8

• 封装因子 (lambda 3):表 17b:

• 基板材料: FR4

• 假设的 EOS 时基故障率: 0 时基故障

表 2-2. 符合 Siemens Norm SN 29500-2 要求的元件故障率

| 表 | 类别                              | 基准时基故障率 | 基准虚拟 T」 |

|---|---------------------------------|---------|---------|

| 5 | CMOS/BICMOS ASIC 模拟和混合 ≤ 50V 电源 | 60 时基故障 | 70°C    |

表 2-2 中的基准时基故障率和基准虚拟  $T_J$  (结温)摘自 Siemens Norm SN 29500-2 表 1 至表 5。工作条件下的故障率是基于 SN 29500-2 第 4 节中的转换信息,并利用基准故障率和虚拟结温计算出的。

### 3 故障模式分布 (FMD)

表 3-1 中针对 BQ77915 的故障模式分布估算综合考虑了 IEC 61508 和 ISO 26262 等标准列出的常见失效模式、子电路功能重要性和复杂性比率以及优秀工程设计评价。

本部分列出的故障模式为随机故障事件,且不包括因滥用或过压而导致的故障。

#### 表 3-1. 芯片故障模式及分布

| 芯片故障模式 | 故障模式分布 (%) |

|--------|------------|

| 安全的故障  | 50%        |

| 不安全的故障 | 50%        |

### 4 引脚故障模式分析(引脚 FMA)

本部分介绍了 BQ77915 引脚的故障模式分析 (FMA)。本文档介绍的故障模式包括各个引脚的典型故障场景:

- 引脚对地短路(请参阅表 4-2)

- 引脚开路(请参阅表 4-3)

- 引脚对邻近引脚短路(请参阅表 4-4)

- 引脚对电源短路(请参阅表 4-5)

表 4-2 至表 4-5 还根据表 4-1 中的故障影响类别,说明了这些引脚状况对器件有何影响。

表 4-1. TI 对故障影响的分类

| 类别 | 故障影响              |

|----|-------------------|

| Α  | 器件可能会损坏,并使功能受损    |

| В  | 器件未损坏,但功能丧失       |

| С  | 器件未损坏,但性能下降       |

| D  | 器件未损坏,功能和性能也未受到影响 |

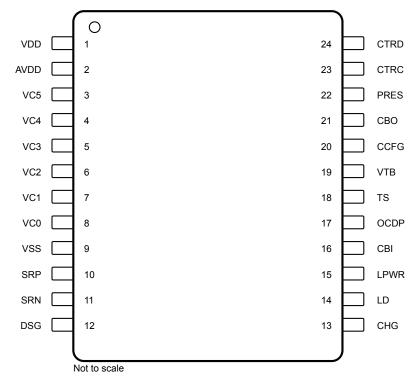

*引脚图* 表示 BQ779154 器件引脚排列。有关器件引脚的详细说明,请参阅 BQ77915 数据表中的*引脚配置和功能* 部分。

图 4-1. 引脚图

表 4-2. 器件引脚对地短路的引脚 FMA

| 引脚名称 | 引脚编号 | 对潜在故障影响的说明                                              | 故障影<br>响的类<br>别 |

|------|------|---------------------------------------------------------|-----------------|

| VDD  | 1    | 由于主电源接地,器件将无法通电。器件将保持在 UVLO 状态,而 CHG/DSG FET 将保持关断。     | В               |

| AVDD | 2    | DPOR_Z 将升高,关闭器件并关断 CHG/DSG FET。                         | В               |

| VC5  | 3    | 电芯 5 的 UV 比较器将跳闸,导致 DSG FET 关断,电池将不再放电。                 | В               |

| VC4  | 4    | 该电芯的 UV 比较器将跳闸,或将对上述电芯触发 OV 事件,CHG/DSG FET 将关断,电池将停止充电。 | В               |

### 表 4-2. 器件引脚对地短路的引脚 FMA (continued)

|       |      | スペーン、 右げ T J JAPA J J B A J J J J J J P W A (CONTINUED)            |                 |

|-------|------|--------------------------------------------------------------------|-----------------|

| 引脚名称  | 引脚编号 | 对潜在故障影响的说明                                                         | 故障影<br>响的类<br>别 |

| VC3   | 5    | 该电芯的 UV 比较器将跳闸,或将对上述电芯触发 OV 事件,CHG/DSG FET 将关断,电池将停止充电。            | В               |

| VC2   | 6    | 该电芯的 UV 比较器将跳闸,或将对上述电芯触发 OV 事件,CHG/DSG FET 将关断,电池将停止充电。            | В               |

| VC1   | 7    | 该电芯的 UV 比较器将跳闸,或将对上述电芯触发 OV 事件,CHG/DSG FET 将关断,电池将停止充电。            | В               |

| VC0   | 8    | VC0 通常通过电阻器接地。没有影响                                                 | D               |

| VSS   | 9    | 没有影响                                                               | D               |

| SRP   | 10   | SRP 通常都会连接到接地节点,因此这不会产生任何影响。                                       | D               |

| SRN   | 11   | SRN 将接地,保持电压与 SRP 处于相同电位。无过流检测功能。                                  | В               |

| DSG   | 12   | DSG FET 将始终处于关断状态,此外,当启用 DSG 驱动器时,将有大电流进入 DSG 引脚,这可能会损坏电流路径中的某些元件。 | Α               |

| CHG   | 13   | CHG FET 将始终处于关断状态,此外,当启用 CHG 驱动器时,将有大电流进入 CHG 引脚,这可能会损坏电流路径中的某些元件。 | А               |

| LD    | 14   | 负载检测功能将无法正常工作;即使仍有负载,也会检测到负载移除。                                    | В               |

| LWPWR | 15   | 如果堆叠,将保持休眠状态。在非堆叠情况下,AVDD 与接地之间会发生短路,导致 AVDD 崩溃和器件执行 POR。          | В               |

| CBI   | 16   | 电芯平衡将始终启用且无法关闭。                                                    | В               |

| OCDP  | 17   | OCD 延迟编程将无法正确配置,将始终检测到 100K $\Omega$ 电阻器,这意味着延迟将由 EEPROM 延迟选项确定。   | С               |

| TS    | 18   | 过压 (OT) 故障将触发,导致 CHG/DSG FET 关断。                                   | В               |

| VTB   | 19   | 过压 (OT) 故障将触发,导致 CHG/DSG FET 关断。                                   | В               |

| CCFG  | 20   | 器件将始终处于 4 芯串联配置下,电池组中的任何不同电芯配置将导致 UV 和 DSG FET 关断。                 | В               |

| СВО   | 21   | 对于非堆叠配置,没有变化。如果采用堆叠配置,顶部电芯将始终认为电芯平衡已启用,将无法禁用电芯平衡。                  | В               |

| PRES  | 22   | 器件将一直处于休眠模式,而无法通电进入正常模式。                                           | В               |

| CTRC  | 23   | CHG FET 将正常工作。                                                     | D               |

| CTRD  | 24   | 放电 FET 将正常工作。                                                      | D               |

|       | _    |                                                                    |                 |

### 表 4-3. 器件引脚开路的引脚 FMA

| 引脚名称 | 引脚编号 | 对潜在故障影响的说明                                               | 故障影<br>响的类<br>别 |

|------|------|----------------------------------------------------------|-----------------|

| VDD  | 1    | 器件将不会通电,因为没有电压进入内部 VDD,器件将一直处于 UVLO 状态,CHG/DSG FET 将保持关断 | В               |

| AVDD | 2    | 电源仍将连接到所有模拟块,但如果没有 1uF 上限,电源将更容易因负载瞬态或任何其他干扰而崩溃          | С               |

| VC5  | 3    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VC4  | 4    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VC3  | 5    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VC2  | 6    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VC1  | 7    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VC0  | 8    | 器件将失去对该电芯进行 OV/UV 检测的能力                                  | В               |

| VSS  | 9    | 基板悬空时,器件的电源将丢失,器件将无法正常工作。                                | В               |

| SRP  | 10   | SRP 处的电压将浮动,并将随机测量电流,可能会发生一些错误的 OCD 触发,这将关断 CHG/DSG FET。 | В               |

| SRN  | 11   | SRP 处的电压将浮动,并将随机测量电流,可能会发生一些错误的 OCD 触发,这将关断 CHG/DSG FET。 | В               |

### 表 4-3. 器件引脚开路的引脚 FMA (continued)

| 引脚名称  | 引脚编号 | 对潜在故障影响的说明                                                                       | 故障影<br>响的类<br>别 |  |

|-------|------|----------------------------------------------------------------------------------|-----------------|--|

| DSG   | 12   | DSG Fet 将被禁用。                                                                    | В               |  |

| CHG   | 13   | 充电 FET 将被禁用。                                                                     | В               |  |

| LD    | 14   | 负载检测功能将不起作用,因为 LD 引脚没有连接来自负载的分压器。当故障发生时,LD 引脚将下拉至地并保持。                           | В               |  |

| LWPWR | 15   | 对于单个器件,没有性能差异。对于可堆叠接口,休眠功能将无法正常使用。                                               | В               |  |

| CBI   | 16   | 将启用 CBI,对于堆叠器件,顶部和底部器件之间的电芯平衡启用通信功能将不起作用。                                        | В               |  |

| OCDP  | 17   | CD1/2 延迟设置将始终读取为最高电阻器选项 (750K), OCD 延迟将设置为最高数字。                                  |                 |  |

| TS    | 18   | 在过热/欠温检查期间,TS 引脚悬空将产生不良结果。可能的错误触发会导致 CHG/DSG FET 关<br>所,电池停止充电/放电。               |                 |  |

| VTB   | 19   | 从 VTB 到 gnd 的分配器(通过 TS 引脚)将不会连接。TS 引脚将始终接地,导致出现过热故障。CHG/DSG FET 将被关断。            | В               |  |

| CCFG  | 20   | 当该引脚悬空时,内部偏置将器件设置为 5 芯配置。如果电池组实际未配置为 5 芯串联 模式(4 芯串联或 3 芯串联),则会检测到 UV,DSG Fet 将关断 | В               |  |

| СВО   | 21   | 对于非堆叠配置,没有性能差异。对于堆叠配置,顶部器件将始终禁用电芯平衡。                                             | В               |  |

| PRES  | 22   | 器件将保持处于休眠模式,而无法通电进入正常模式。                                                         | В               |  |

| CTRC  | 23   | 电压引脚将悬空,如果它上升到 0.6V (VMIN) 以上,将导致 CHG FET 关断,器件将无法工作。                            | В               |  |

| CTRD  | 24   | 电压引脚将悬空,如果它上升到 0.6V (VMIN) 以上,将导致 DSCHG FET 关断,器件将无法放电。                          | В               |  |

### 表 4-4. 器件引脚对邻近引脚短路的引脚 FMA

| 引脚名称 | 引脚编号 | 短路至   | 对潜在故障影响的说明                                                                                        | 故障影<br>响的类<br>别 |

|------|------|-------|---------------------------------------------------------------------------------------------------|-----------------|

| VDD  | 1    | AVDD  | 短接至 AVDD: VDD 高压将施加到 AVDD 引脚,导致连接至 AVDD 的所有低压元件上产生过压应力。                                           | А               |

| AVDD | 2    | VC5   | 短接至 VC5: VC5 高压将施加到 AVDD 引脚(来自 VDD 或 VC5),导致连接到 AVDD 的所有低压元件上产生过压应力。                              | А               |

| VC5  | 3    | VC4   | 短接至 VC4:电芯 5 的 UV 比较器将跳闸,导致 DSG FET 关断,电池将停止放电。                                                   | В               |

| VC4  | 4    | VC3   | 短接至 VC3: 此电芯或上/下电芯将触发 OV/UV。CHG/DSG FET 将关断,电池将停止充电。                                              | В               |

| VC3  | 5    | VC2   | 短接至 VC2:此电芯或上/下电芯将触发 OV/UV。CHG/DSG FET 将关断,电池将停止充电。                                               | В               |

| VC2  | 6    | VC1   | 短接至 VC1: 此电芯或上/下电芯将触发 OV/UV。CHG/DSG FET 将关断,电池将停止充电。                                              | В               |

| VC1  | 7    | VC0   | 短接至 VC0: 此电芯或上/下电芯将触发 OV/UV。CHG/DSG FET 将关断,电池将停止充电。                                              | В               |

| VC0  | 8    | VSS   | 短接至 VSS: VC0 通过 RIN 电阻器接地,因此无变化。                                                                  | D               |

| VSS  | 9    | SRP   | 短接至 SRP: SRP 通常都会连接到接地节点,因此这不会产生任何影响。                                                             | D               |

| SRP  | 10   | SRN   | 短接至 SRN: SPR 和 SRN 将短接在一起,所有过流保护功能均不起作用。                                                          | В               |

| SRN  | 11   | DSG   | SRN 将产生高压,导致 ESD 钳被激活,保持引脚约为 4V,SRN 路径中的元件可能会受损。                                                  | А               |

| DSG  | 12   | CHG   | 如果发生仅一个 DSG/CHG 关断的故障,这将导致直通电流通过 NMOS 和 PMOS 器件驱动器。大电流将从 CHG/DSG 轨流向地面,导致电源崩溃并关断所有 FET,或因大电流造成损坏。 | A               |

| CHG  | 13   | LD    | 短接至 LD:负载检测功能将不工作,因为 CHG 引脚将干扰 RLD 分压器。将不会检测到负载移除。                                                | В               |

| LD   | 14   | LWPWR | 在负载检测过程中,LPWR 引脚可能产生高压,导致 ESD 产生火花;大电流灌入 LPWR 引脚,可能使 LPWR 引脚上的低压元件受损。                             | А               |

### 表 4-4. 器件引脚对邻近引脚短路的引脚 FMA (continued)

| 引脚名称  | 引脚编号 | 短路至  | 对潜在故障影响的说明                                                                                                     | 故障影<br>响的类<br>别 |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|-----------------|

| LWPWR | 15   | СВІ  | 短接至 CBI: 如果 CBI 被驱动为低电平(电芯平衡已启用),短接至 CBI 将导致 AVDD 崩溃,因为 AVDD 通过 LPWR-CBI 引脚对地短路。                               | В               |

| СВІ   | 16   | OCDP | 短接至 OCDP:OCDP 通过电阻器对地短路,CBI 将接地,将始终启用电芯平衡功能。将失去关闭电芯平衡的能力。                                                      | В               |

| OCDP  | 17   | TS   | 短接至 TS:由于电流源将电流倾入 OCDP 引脚,温度测量将发生偏差。器件的测量温度将始终较低。                                                              | С               |

| TS    | 18   | VTB  | 短接至 VTB:将始终在 VTB 处测量 TS 引脚,这将触发欠温故障。CHG FET 将被关断。                                                              | В               |

| VTB   | 19   | CCFG | 短接至 CCFG:在正常运行期间,VTB 将在 AVDD 和地面之间切换,因此 CCFG 将从 3 芯串联配置更改为 4 芯串联配置(取决于 VTB 的当前状态)。 这将导致 UV 保护错误地启动和关断 DSG FET。 | В               |

| CCFG  | 20   | СВО  | 短接至 CBO:如果电芯平衡功能启用,CCFG将被拉至低电平,使器件进入3 芯配置,并导致电芯4和5出现 UV 故障。                                                    | В               |

| СВО   | 21   | PRES | 短接至 PRES: CBO 将强制 PRES 接地,器件将进入休眠模式并停留在此模式下。                                                                   | В               |

| PRES  | 22   | CTRC | 短接至 CTRC:如果休眠结束,则 PRES 引脚保持在 VDD。如果 CTRC 产生此高压,将禁用 FET 驱动器,不再充电。                                               | В               |

| CTRC  | 23   | CTRD | 短接至 CTRD:CHG 和 DSG FET 都将遵循 CTRD/C 中指示的内容,器件将不再能够独立控制 CHG/DSG。                                                 | В               |

| CTRD  | 24   | CTRC | 短接至 CTRD:CHG 和 DSG FET 都将遵循 CTRD/C 中指示的内容,器件将不再能够独立控制 CHG/DSG。                                                 | В               |

### 表 4-5. 器件引脚对电源短路的引脚 FMA

| 引脚名称  | 引脚编号 | 对潜在故障影响的说明                                                              | 故障影<br>响的类<br>别 |

|-------|------|-------------------------------------------------------------------------|-----------------|

| VDD   | 1    | 正常操作,因为该引脚是电源。                                                          | D               |

| AVDD  | 2    | AVDD 将对高压短路,导致 ESD 钳位开始发挥作用,钳位引脚电压达到约 4V,并导致大电流从 VDD 流向 AVDD,可能因过热导致损坏。 | А               |

| VC5   | 3    | VC5 的正常工作电压与 VDD (TOPSTACK) 的电压相同。                                      | D               |

| VC4   | 4    | 连接电源将触发上述电芯的 OV 事件或 UV 事件,CHG/DSG FET 将关断,电池将停止充电。                      | В               |

| VC3   | 5    | 连接电源将触发上述电芯的 OV 事件或 UV 事件,CHG/DSG FET 将关断,电池将停止充电。                      | В               |

| VC2   | 6    | 连接电源将触发上述电芯的 OV 事件或 UV 事件,CHG/DSG FET 将关断,电池将停止充电。                      | В               |

| VC1   | 7    | 连接电源将触发上述电芯的 OV 事件或 UV 事件,CHG/DSG FET 将关断,电池将停止充电。                      | В               |

| VC0   | 8    | 由于 VC0 与接地相连,器件将不会通电,器件将保持为 UVLO 状态,CHG/DSG FET 将保持关断状态。                | В               |

| VSS   | 9    | 由于主电源接地,器件将无法通电。器件将保持在 UVLO 状态,而 CHG/DSG FET 将保持关断。                     | В               |

| SRP   | 10   | 将向 SRP 施加高压,导致 ESD 触发并将该引脚钳制在 4V 左右。大电流将从 VDD 流向 SRP,可能导致损坏/过热。         | Α               |

| SRN   | 11   | 将向 SRN 施加高压,导致 ESD 触发并将该引脚钳制在 4V 左右。大电流将从 VDD 流向 SRN,可能导致损坏/过热。         | А               |

| DSG   | 12   | 当 EN_DSG 变为低电平时,将有大电流从 VDD 流向 GND,可能对电流路径中的元件造成损坏。                      | Α               |

| CHG   | 13   | CHG 引脚将 (在内部)钳制在 20V,如果发生会拉低 CHG 电平的故障,大电流将从 CHG 流向地面,可能损坏电流路径中的元件。     | А               |

| LD    | 14   | 负载检测引脚将(在内部)钳制在 18V,将通过 LD 从 VDD 引出约 450 μ A。负载检测功能将无法正常工作。             | В               |

| LWPWR | 15   | 将向 LPWR 引脚施加高压,导致 ESD 触发并将该引脚钳制在 4V 左右。大电流将从 VDD 流向 LPWR,可能导致损坏/过热。     | А               |

| СВІ   | 16   | 将向 CBI 引脚施加高压,导致 ESD 触发并将该引脚钳制在 4V 左右。大电流将从 VDD 流向 CBI,可能导致损坏/过热。       | А               |

### 表 4-5. 器件引脚对电源短路的引脚 FMA (continued)

| 引脚名称 | 引脚编号 | 对潜在故障影响的说明                                                                             | 故障影<br>响的类<br>别 |

|------|------|----------------------------------------------------------------------------------------|-----------------|

| OCDP | 17   | 将向 OCDP 引脚施加高压,导致 ESD 触发并将该引脚钳制在 4V 左右。大电流将从 VDD 流向 OCDP,可能导致损坏/过热。                    | Α               |

| TS   | 18   | 引脚上的过压将导致 ESD 保护被激活,将电压钳制在约 5V。大电流将从 VDD 流过 TS 引脚,可能导致元件损坏和应力过大。                       | Α               |

| VTB  | 19   | 引脚上的过压将导致 ESD 保护被激活,将电压钳制在约 5V。大电流将从 VDD 流过 VTB 引脚,可能导致元件损坏和应力过大。TS 引脚也可能通过分压器电阻器出现高压。 | Α               |

| CCFG | 20   | 引脚上的过压将导致 ESD 保护被激活,将电压钳制在约 5V。大电流将从 VDD 流过 CCFG 引脚,可能导致元件损坏和应力过大。                     | Α               |

| СВО  | 21   | 在堆叠配置中,顶部器件将无法驱动到低位以实现电芯平衡。顶部器件的电芯平衡将保持禁用状态。                                           | В               |

| PRES | 22   | 由于引脚对电源短路,器件将无法进入休眠模式。                                                                 | В               |

| CTRC | 23   | 充电 FET 将被禁用;器件将不会运行。                                                                   | В               |

| CTRD | 24   | 放电 FET 将被禁用;器件将不会运行。                                                                   | В               |

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司