# 基于TIAFE8092 的AAURX 射频链路预算分析

Jason Ren

#### 摘要

RF Transceiver 芯片的集成度越来越高,AAU 的射频链路的功能前移,AAU 的射频链路设计者需要更多了解 RF Transceiver 的应用方法及原理。AFE8092 是 TI 高性能,大带宽的多通道射频收发器件。包括了 8 个发射通道,8 个接收通道,2 个反馈通道,所有通道均为射频直采架构。各个射频链路的大带宽,高性能使得 AFE8092 适用于大部分 4G/5G 基站 TRX 射频板应用场景。AFE8092 的接收(RX)链路包含了 4Gsps 直采 ADC,包含了 DSA(Digital Step Attenuator)。每个接收通道数字部分包含功率监测,可以支持内部或外部的 AGC 控制,同时也包含 RF overload 功率监测,保证可靠性。本文将在对 AFE8092 基本功能介绍的基础上,基于 AFE8092 的射频特性分析射频链路预算的问题。

#### 目录

| 1         | 引言. |                                         | 2 |  |  |  |  |  |  |  |

|-----------|-----|-----------------------------------------|---|--|--|--|--|--|--|--|

| 2         |     | 8092 RX链路介绍                             |   |  |  |  |  |  |  |  |

|           |     | 数控衰减控制模块                                |   |  |  |  |  |  |  |  |

|           |     | 自动增益控制模块(AGC)自动增益控制模块(AGC)              |   |  |  |  |  |  |  |  |

| 3         |     | AFE8092的 RX链路预算分析                       |   |  |  |  |  |  |  |  |

|           |     | 静态灵敏度分析                                 |   |  |  |  |  |  |  |  |

|           |     | ··· _ · · · · · · · · · · · · · · · · · |   |  |  |  |  |  |  |  |

| 4         |     | 文献                                      |   |  |  |  |  |  |  |  |

|           |     |                                         |   |  |  |  |  |  |  |  |

| 图/表       |     |                                         |   |  |  |  |  |  |  |  |

| Figure 1. |     | AFE8092 RX链路框图                          | 2 |  |  |  |  |  |  |  |

| Figu      |     | Fast Gain Swap 模式GPIO配置方法               |   |  |  |  |  |  |  |  |

| Figure 3. |     | AGC功能模块示意框图                             |   |  |  |  |  |  |  |  |

| Figure 4. |     | 数字峰值功率检测器工作机制示意图                        |   |  |  |  |  |  |  |  |

| Figu      |     | Internal AGC控制逻辑示意图                     |   |  |  |  |  |  |  |  |

| Figu      |     | Internal AGC各参数关系示例                     |   |  |  |  |  |  |  |  |

| Figu      |     | 静态灵敏度分析流程示意图                            |   |  |  |  |  |  |  |  |

| 0         |     |                                         |   |  |  |  |  |  |  |  |

## 1 引言

随着 RF Transceiver 芯片的集成度越来越高,在 RRU 的 TRX 链路的各个芯片功能更多地前移到 RF Transceiver 中。TI 的 AFE8092 集成了 8T8R8FB 的 RF Transceiver 芯片,所有信号基于射频直 采架构,各个通道的高信号带宽特性使得 AFE8092 支持更多的应用场景,在大带宽场景下有独特的优势。同时,各个通道的射频直采架构也规避了零中频架构中可能出现的直流分量和 IQ 失衡问题,更方便射频链路的性能调试。各项优势使得 AFE8092 在更多的客户产品中实现商用。

本文基于 AFE8092, 介绍了射频链路中的上行指标分解方法以及设计时需要注意的要点。

## 2 AFE8092 RX 链路介绍

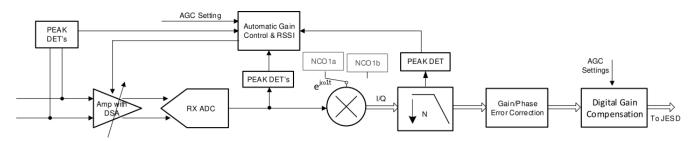

AFE8092的 RX 链路框图如下图所示。

Figure 1. AFE8092 RX 链路框图

RX 链路模拟端包括 RF 功率检测器,数控衰减控制模块(DSA),4Gsps 采样率的 ADC;数字端包括数字功率检测器,自动增益控制(AGC)模块,数字混频器,抽值器(DDC),以及数字增益补偿模块;高速接口侧包括 JESD 模块以及 SERDES 模块,在此不进行赘述。

下面会重点对几个模块进行详细介绍。

#### 2.1 数控衰减控制模块

RX 链路入口处集成了数控增益控制模块 DSA,用来扩宽 RX 链路的动态范围。该 DSA 可通过 SPI 接口写寄存器控制,通过 GPIO 控制,或者通过 AGC 自动进行控制,这三者的 控制优先级可以通过静态寄存器配置或者 API 接口进行修改。

- 1. SPI接口寄存器控制:通过 SPI访问读写 DSA 页内的寄存器,来配置/回读 DSA 值。

- 2. GPIO 控制方法: 分为两种, 为 external DSA control 和 fast gain swap。

External DSA control 通过 3bit GPIO 信息以 8 个档位对 DSA 进行控制,DSA 衰减值的初始 状态和步进大小通过寄存器进行配置。最终的衰减值计算方法如下。其中,B[2..0]为 GPIO 高低电平状态,ATT $_{min}$ 是初始最小衰减值,ATT $_{step}$ 是 GPIO 控制模式下的各档位间 的步进,ATT $_{max}$ 是 RX 链路最大可支持的衰减值。

DSA\_ATT<sub>actual</sub>=min(ATT<sub>min</sub>+B[2..0]\*ATT<sub>step</sub>, ATT<sub>max</sub>)

Fast gain swap 是使用特定的 GPIO 来触发 DSA 快速跳到提前配置好的 DSA 档位上。每个 RX 链路都可以配置除了初始状态下的 main DSA 以外的三个 DSA 档位,具体配置 GPIO 方法如下表所示:

| # GPIO pins | Description                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------|

| 1           | single GPIO pin for all 8 RX chains to select between main and one swap DSA state                    |

| 2           | two GPIO pins common to all 8 RX chains, to select among 4 DSA settings (main and 3 swap DSA states) |

| 2           | one GPIO pin every 4 RX chains to select between main and one swap DSA state                         |

| 4           | two GPIO pins every 4 RX chains to select among 4 DSA settings (main and 3 swap DSA states)          |

| 4           | one GPIO pin every 2 RX chains to select between main and one swap DSA state                         |

| 8           | separate GPIO pin for each RX chain o select between main and one swap DSA state                     |

| 8           | two GPIO pins every 2 RX chains to select among 4 DSA settings (main and 3 swap DSA states)          |

Figure 2. Fast Gain Swap 模式 GPIO 配置方法

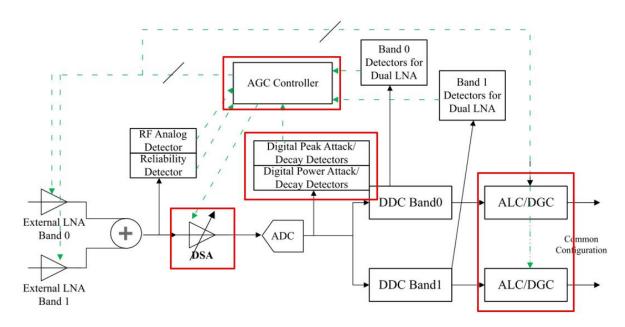

#### 2.2 自动增益控制模块(AGC)

自动增益控制模块由下图部分组成,主要包括数字功率峰值检测器,AGC Controller, DSA,ALC。其中,峰值功率检测器将输入 ADC 的信号功率信息交付给 AGC Controller,AGC Controller 由特定的 AGC 逻辑控制 DSA 档位和 ALC 档位及增益控制字 SLICER,后面会对这些模块进行详细描述

Figure 3. AGC 功能模块示意框图

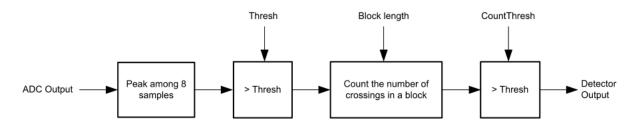

相比于 power detector 检测均值 rms 功率,数字峰值功率检测器的作用是检测输入 ADC 的信号功率,在一定的检测窗长内统计峰值功率点超过门限的次数,如果次数超过次数门限,则判断信号功率过大且需要衰减上调(Big/Small Step Attack);如果次数低于次数门限,则判断信号功率过低的且需要进行衰减回调(Big/Small Step Decay)。功能示意图如下所示,检测器会在每 8 个 ADC 未经过 DDC 的采样点内取到一个信号峰值,如果该峰值超过设定的 Attack/Decay 门限,计数器累加1,如果在规定的时间内计数器触发了特定的计数器门限,数字峰值功率检测器会上报触发事件,AGC Controller 开始工作。

Figure 4. 数字峰值功率检测器工作机制示意图

AGC Controller 的作用是接收数字峰值功率检测器上报的 Attack/Decay 事件,控制 AGC 模块的状态机,状态机会对 DSA 和 ALC 进行控制。功能框图如下图所示,控制逻辑是将输入到 FPGA 侧的信号功率稳定在一定的范围内,该范围是 attack 门限和 decay 门限之间。

#### Figure 5. Internal AGC 控制逻辑示意图

ALC 的作用是在不同的输入信号功率等级和 DSA 的场景下,配置自身的增益以及传递给 FPGA 的 SLICER 因子,同时,也要保证整个链路的增益保持不变。ALC 中,又包含三部分增益:粗调增益 Coarse Gain,根据 DSA 档位进行小于 6dB 以下的粗调;细调增益 Fain Gain,根据 DSA 档位和 Coarse Gain 值进行 1dB 档位的细调;FineGainOffset,固定的 ALC 衰减,防止在部分场景下出现数字域饱和的情况。所以,ALC 的总增益为:

Applied Gain= FineGain(dB)+FineGainOffset(dB)+CoarseGain(dB)

Coarse Gain 只与 DSA 档位相关,计算方法如下。其中,CoarseStep 可配置成 2,3,4,6,8。

CoarseGain=CoarseStep\*(floor(DSA/CoarseStep))

Fine Gain 与 DSA 档位及 CoarseGain 相关, 计算方法如下。

#### FineGain=DSA-CoarseGain

由于在 ALC 前级进行了包括模拟 DSA,数字粗调/细调增益,导致在 FPGA 侧的数字功率在一定范围内变化,因此需要通过 SLICER 将前级增益信息传递给 FPGA 侧,通过 FPGA 内部增益对这部分增益进行补偿。

为了便于理解,举个简单例子如下表所示。可以看到,DSA 会保证 ADC 输出数字功率始终维持在一个功率等级。经过 ALC 后,数字功率会在某一个功率等级范围内变化。FPGA 在得到了 SLICER 信息后,会将数字功率补偿一部分,最终的输出功率会随着 ADC 输入功率线性变化。

| ADC<br>Input/dBm | ADC<br>Output/dBFs | DSA/dB | Fine<br>Gain/dB | Coarse Index<br>(LSB)/bit | Output (without<br>Coarse Index)/dBfs | Output with<br>Coarse<br>Index/dBFs |

|------------------|--------------------|--------|-----------------|---------------------------|---------------------------------------|-------------------------------------|

| -14              | -1                 | 0      | 0               | 0                         | -7                                    | -7                                  |

| -13              | -1                 | 1      | 1               | 0                         | -6                                    | -6                                  |

| -12              | -1                 | 2      | 2               | 0                         | -5                                    | -5                                  |

| -11              | -1                 | 3      | 3               | 0                         | -4                                    | -4                                  |

| -10              | -1                 | 4      | 4               | 0                         | -3                                    | -3                                  |

| -9               | -1                 | 5      | 5               | 0                         | -2                                    | -2                                  |

| -8               | -1                 | 6      | 0               | 1                         | -7                                    | -1                                  |

| -7               | -1                 | 7      | 1               | 1                         | -6                                    | 0                                   |

| -6               | -1                 | 8      | 2               | 1                         | -5                                    | 1                                   |

| -5               | -1                 | 9      | 3               | 1                         | -4                                    | 2                                   |

| -4               | -1                 | 10     | 4               | 1                         | -3                                    | 3                                   |

| -3               | -1                 | 11     | 5               | 1                         | -2                                    | 4                                   |

Figure 6. Internal AGC 各参数关系示例

## 3 基于 AFE8092 的 RX 链路预算分析

射频接收链路指标为灵敏度,主要分为静态灵敏度,阻塞灵敏度,临道选择性以及交调特性。 RFIC 的射频性能会对静态灵敏度和交调特性有一定影响,而临道选择性及阻塞灵敏度主要由链 路上的滤波器进行保证。因此本节对静态灵敏度和交调特性进行详尽分析。

#### 3.1 静态灵敏度分析

静态灵敏度指的是针对带内静态信号,接收机可正确解调的信号功率。静态灵敏度指标分解到 RFIC上,会对 RFIC 的 NSD 产生要求。

静态灵敏度计算公式如下,其中-174dBm/Hz为白噪功率谱密度,NF为整个链路包括RFIC的噪声系数,BW为链路带宽,Gain<sub>Ale</sub>为信道编码带来的处理增益,SNR为协议要求的解调信噪比。

对在固定了灵敏度、带宽需求、处理增益和解调信噪比的前提下,我们可以利用上面的公式将指标分解到整个系统的噪声系数上,而 TI 的 RFIC 描述噪声表现是通过器件输出底噪 NSD 来进行描述的,需要我们进行一次换算。AFE8092 NSD 为-146dBfs/Hz,满量程-13dBm,换算为噪声系数-146dBfs/Hz-13+174dBm/hz=15dB。根据级联噪声系数公式,可以容易推算出 AFE8092 的 NSD 是否满足系统噪声系数要求。在一般的 5G MIMO 应用中,前级射频链路的噪声功率一般都会高于 AFE8092 的底噪较多,因此 AFE8092 的底噪基本可以满足大多数应用场景的静态灵敏度需求。

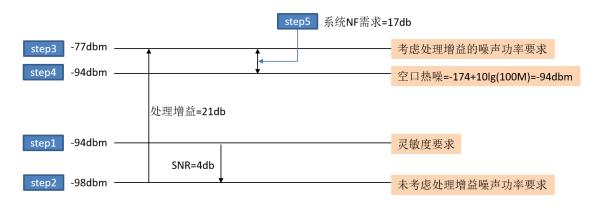

上面的分析过程举例如下,不涉及任何系统的实际指标:

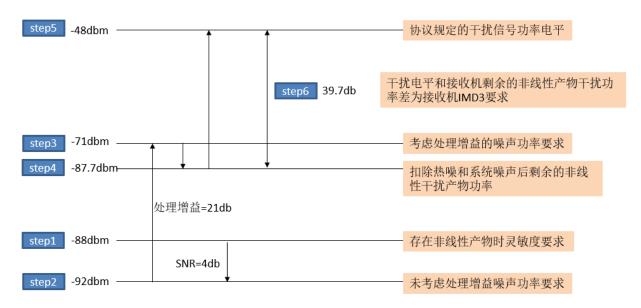

Figure 7. 静态灵敏度分析流程示意图

Step1: 确定灵敏度 SEN 为-94dBm。

Step2: 基带解调信噪比 SNR 为 4dB, 在不考虑信道编码处理增益 Gain<sub>Alg</sub>时, 带内噪声功率-94-4=-98dBm。

Step3: 处理增益导致带内噪声功率放宽 21dB,考虑处理增益后的带内噪声功率为-77dBm。

Step4-5: 空口在 100M 带宽内的热噪积分为-94dBm,与噪声功率要求差 17dB 则为系统噪声系数。

根据下面的级联系统噪声系数公式容易计算出对 RFIC 的噪声系数要求。

$$NF = NF_0 + \sum_{i=1}^{n} \frac{NF_i - 1}{\prod_{j=0}^{n-1} G_j}$$

#### 3.2 灵敏度对交调特性影响分析

在空口出现两个干扰信号,它们的交调产物落在业务频带内会对接收机的灵敏度产生影响,因此需要考察接收机交调特性。接收机的交调特性指标分解到 RFIC 上,会对 RFIC 的 IMD3 性能指标做出要求。

接收机的交调特性分析举例如下。

Step1:协议规定干扰信号使接收机灵敏度恶化 6dB。在静态灵敏度为-94dBm 的系统中,我们可以推论在存在非线性产物时,灵敏度恶化到-88dBm。

Step2: 基带解调信噪比 4dB, 在不考虑信道编码处理增益时, 带内噪声功率-88-4=-92dBm。

Step3: 处理增益导致带内噪声功率放宽 21dB, 考虑处理增益后的带内噪声功率为-71dBm。

Step4: 此时的噪声+干扰需求是考虑了非线性产物的功率,则该功率和计算静态灵敏度时的噪声功率之差为非线性产物功率大小。-71dBm-(-77dBm)=-87.7dBm,允许的最大非线性产物功率大小为-87.7dBm。

Step5-6: 协议规定的场景下,产生非线性产物的信号功率为-48dBm,则 IMD3 为-48-(-87.7) =39.7dB。根据 IMD3 和 IIP3 的关系定义公式,系统 IIP3=0.5\*IMD3+P<sub>in</sub>=39.7/2-48=28.15dBm

经过以上分析后,我们可以得出在空口的 IIP3 指标。而根据级联 IIP3 定义公式及前级的 IIP3 指标,可以得出 RFIC 是否满足非线性指标的结论。注意,由于 ADC 是硬限幅器件,因此 IIP3 对 ADC 来说会随着输入信号的大小变化,因此 TI 对 ADC 的非线性特性描述是通过特定输入信号下的 IMD3 大小定义的,所以需要再做一次 IMD3 计算的转换。

$$\frac{1}{\mathit{IIP3}} = \frac{1}{\mathit{IIP3}_1} + \sum_{i=0}^{n} \frac{\prod_{j=1}^{n-1} \mathit{Gj}}{\mathit{IIP3}_n}$$

## 4 参考文献

AFE80xx 器件手册: AFE8092\_RTM\_MAY2021\_datasheet

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021,德州仪器 (TI) 公司