# TEXAS INSTRUMENTS

基于现场可编程门阵列 (FPGA) 的设计需要具有高效的存储器,以便能够运行各种应用。尽管 FPGA 具有内置存储器,但高性能系统(例如服务器、以太网交换机、SSD 和硬件加速器等)会需要额外存储器以满足其最低存储容量要求。该外部存储器可以是易失性或非易失性存储器,具体取决于断电时是否需要储存数据。非易失性存储器(例如闪存)在断电时也能保存数据,因而非常适合储存开机启动代码和 FPGA 配置数据。FPGA 通过由多路复用器 (mux) 进行路由的串行外设接口 (SPI) 协议与外部存储器通信。

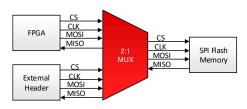

图 1 显示了多路复用器如何路由 SPI 信号,让用户可以通过 FPGA 或外部标头等多种方式访问闪存。标头允许外部访问闪存,以调试开机启动代码及更新其他储存的固件。

图 1. 外部访问闪存

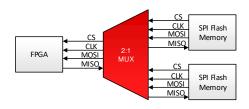

图 2 显示了 FPGA 如何通过扩展多路复用器存储器访问多个外部存储器。尽管 SPI 协议允许主器件与多个从器件直接连接,但多路复用器对于降低总线容量以及当仅有一个主器件片选位时为连接提供方便至关重要。多路复用器具有双向功能,因而一个多路复用器可以同时应对图 1 和图 2 中的用例情景。

图 2. FPGA 访问多个闪存

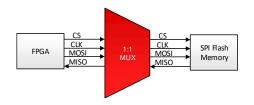

图 3 除了提供一条替代的内存访问路径外,关断保护 多路复用器还对 FPGA 和外部存储器进行隔离 (如 所示),防止系统出现电源时序问题。要了解有关此应用 的更多信息,请参阅《利用关断保护信号开关消除电源 排序》。

图 3. 隔离 FPGA 和外部存储器

#### SPI 协议

SPI 是 FPGA 和 MCU 与各种外设(例如闪存、传感器、ADC 和 SD 卡)进行近距离通信的一种同步串行接口。SPI 总线使用的是推挽驱动器。与 I2C 和 SMBus 使用的开漏驱动器相比,它支持更高的时钟频率 (>75MHz),并具有更低的功耗 (<1mA)。与使用两个通道(一个数据通道、一个时钟信号通道)的 I2C 相比,SPI 协议通常使用四个通道(两条数据线路、一个时钟信号通道和一个片选位)。为了提高吞吐量,四通道 SPI(四个数据通道)和八通道 SPI(八个数据通道)协议在使用外部存储器的高性能系统中越来越常见。有关 SPI 总线的更多信息,请参阅《模拟工程师口袋参考书》中从第 111 页开始的内容。

#### 选择适合 SPI 应用的多路复用器

对 SPI 数字信号而言最重要的多路复用器参数是电压、通道数和带宽。要选择合适的多路复用器电压,只需使 FPGA 或 MCU I/O 电压与推荐的多路复用器 I/O 电压一致即可。多路复用器通道数由 SPI 协议决定;常规 SPI 协议需要四个通道(两条数据线路、一条时钟信号线路和一条片选线路)。带宽是基于接通状态电容 (CoN) 计算多路复用器对时钟信号的寄生效应的一种简单方法。对于大多数系统而言,足够多路复用器带宽的计算方法是用最大基础时钟频率乘以三倍。例如,如果最大 SPI 时钟信号是 75MHz,则建议使用具有三倍带宽 (225MHz) 的多路复用器。

推荐的多路复用器带宽 = 时钟频率 x 3

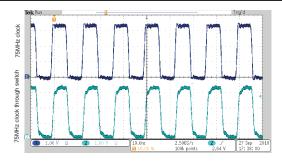

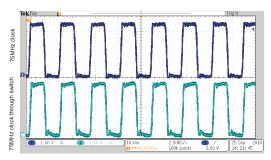

图 4 展示了 SN74CBTLV3257 (200MHz 带宽)如何传递 75MHz SPI 时钟信号。顶部波形显示供参参照的时钟信号,而底部波形显示经由多路复用器进行传递后的输出时钟信号。如上图所示,寄生多路复用器 C<sub>ON</sub>使时钟上升沿和下降沿平缓。虽然大多数 SPI 应用不大受这一延迟的影响,但它显示了多路复用器带宽对 SPI 时钟信号的影响。

商标 www.ti.com.cn

### 图 4. 通过 SN74CBTLV3257 传递 75MHz 时钟信号

要缩短上升和下降时间,可以在同一个 SPI 应用中使 用引脚对引脚 TMUX1574 (2GHz 带宽)。图 5 展示 了 TMUX1574 如何使用相同的 75MHz SPI 时钟信号 运行。如底部波形所示,多路复用器对输出 SPI 时钟 信号几乎没有影响。其原因在于 Con 能够使 75MHz 时钟信号在传递过程中几乎不产生失真。使用具有较低 CON 的多路复用器会导致带宽增加,这对于电路板布 局或连接器会额外增加电容的系统至关重要。

图 5. 通过 TMUX1574 传递 75MHz 时钟信号

### TI SPI 多路复用器解决方案

在高性能系统中, FPGA和 MCU会需要借助外部存储 器扩展存储容量。该外部存储器可以是易失性或非易失 性存储器(例如闪存),用于在断电时储存数据。该功 能使得闪存非常适合储存开机启动代码、FPGA 配置数 据和媒体文件。FPGA 和 MCU 通过由多路复用器路由 的 SPI 协议与这些闪存进行通信。该多路复用器为用 户提供多种访问闪存的方法,而且都具有关断保护功 能,能够在电源时序控制期间保护 FPGA 和 MCU。根 据 SPI 协议、信号电压和带宽要求,选择适合应用的 多路复用器。为了适用于各种各样的 SPI 应用, TI 高 带宽多路复用器产品组合支持广泛的信号电压,以获得 理想的 SPI 性能。

表 1. 备选器件建议

| 器件         | 配置       | 主要特性                                                                           |

|------------|----------|--------------------------------------------------------------------------------|

| TMUX1574   | 2:1,4 通道 | $2\text{GHz}$ 带宽,低导通电容 (7.5pF),低导通电阻 ( $2\Omega$ ),关断保护,1.8V 逻辑兼容              |

| TMUX1575   | 2:1,4 通道 | 1.3mm x 1.3mm 封装,1.2V 兼容控制输入,关断保护,低导通电容 (10pF),低导通电阻 (1.7 $\Omega$ ),1.8GHz 带宽 |

| TMUX1511   | 1:1,4 通道 | $3GHz$ 带宽,低导通电容 $(3.3pF)$ ,低导通电阻 $(2\Omega)$ ,关断保护,1.8V 逻辑兼容                   |

| TS3A27518E | 2:1,6 通道 | 240MHz 带宽,低导通电阻 (4.4Ω),<br>关断保护,1.8V 逻辑兼容                                      |

#### 参考文献

- 德州仪器 (TI):《模拟工程师口袋参考指南》(第 五版)

- 德州仪器 (TI):《利用关断保护信号开关消除电源 时序》

- 德州仪器 (TI):《使用低导通电容多路复用器改善 稳定性问题》

- 德州仪器 (TI):《1.8V 逻辑多路复用器和信号》

所有商标均为其各自所有者的财产。

## 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司