# Giga ADC 介绍及杂散分析

Anjin Du

**China Telecom Application Team**

# 摘要

Giga ADC 是 TI 推出的采样率大于 1GHz 的数据转换产品系列,主要应用于微波通信、卫星通信以及 仪器仪表。本文介绍了 Giga ADC 的主要架构以及 ADC 输出杂散的成因分析,以及优化性能的主要措施。

# 目录

| 1 | Gig                  | a ADC | 架构及 TI 的 Giga ADC                       |    |  |

|---|----------------------|-------|-----------------------------------------|----|--|

|   | _                    |       | ADC 架构演进                                |    |  |

|   |                      |       | ya ADC 产品介绍                             |    |  |

| 2 | TI Giga ADC 架构介绍     |       |                                         |    |  |

|   | 2.1 Input mux        |       |                                         |    |  |

|   | 2.2 Interleaved T/H  |       |                                         |    |  |

|   | 2.3 Preamplifier     |       |                                         |    |  |

|   |                      | 2.3.1 | ·<br>第二级输入 buffer                       | 8  |  |

|   |                      | 2.3.2 | 折叠电路                                    | 8  |  |

|   |                      | 2.3.3 | 内插电路                                    | 9  |  |

|   |                      | 2.3.4 | 平均电路                                    | 10 |  |

|   | 2.4 校准电路             |       |                                         | 11 |  |

| 3 | Giga ADC 杂散的分析       |       |                                         |    |  |

|   | 3.1 Interleave 相关的杂散 |       |                                         |    |  |

|   |                      | 3.1.1 | 输入偏置误差                                  | 12 |  |

|   |                      | 3.1.2 | 输入增益误差                                  | 13 |  |

|   |                      | 3.1.3 | 采样时钟的相位误差                               | 14 |  |

|   | 3.2 固定频点杂散           |       |                                         |    |  |

|   |                      | 3.2.1 | 采样时钟杂散                                  | 15 |  |

|   |                      | 3.2.2 | 数据输出的随路时钟                               |    |  |

|   | 3.3                  | 和输入   | 相关的杂散                                   |    |  |

|   | 3.4 杂散信号的优化          |       |                                         |    |  |

| 4 | 结论                   |       | 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |    |  |

| 5 | • ,,, • •            | ·洛料   |                                         | 19 |  |

# 图

| Figure 1 ADC 架构与输出精度关系                          | 3  |

|-------------------------------------------------|----|

| Figure 2 折叠 ADC 简化架构                            | 4  |

| Figure 3 折叠 ADC 原理                              |    |

| Figure 4TI Giga ADC 产品系列                        |    |

| Figure 5ADC08D1520 内部架构                         | 6  |

| Figure 6Giga ADC 输入开关                           |    |

| Figure 7 Interleaved ADC 采保电路示意图                | 7  |

| Figure 8 差分折叠电路                                 | 8  |

| Figure 9 双折叠电路输出波形                              | g  |

| Figure 10 级联折叠电路示意图                             |    |

| Figure 11 内插电路示意图                               | 10 |

| Figure 12 内插电路输出波形                              | 10 |

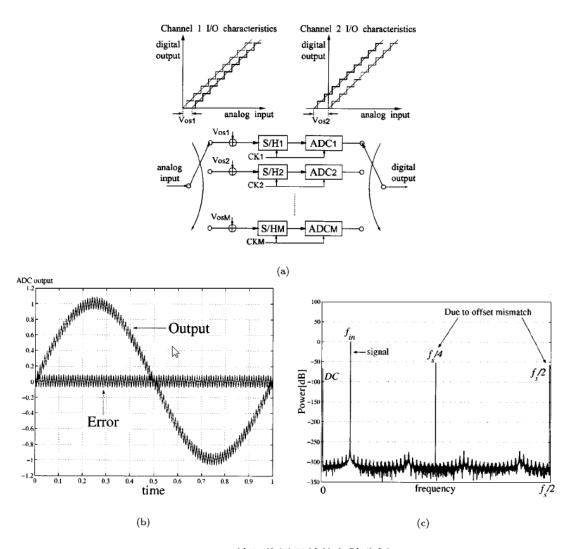

| Figure 13 输入偏置误差的杂散分析                           | 12 |

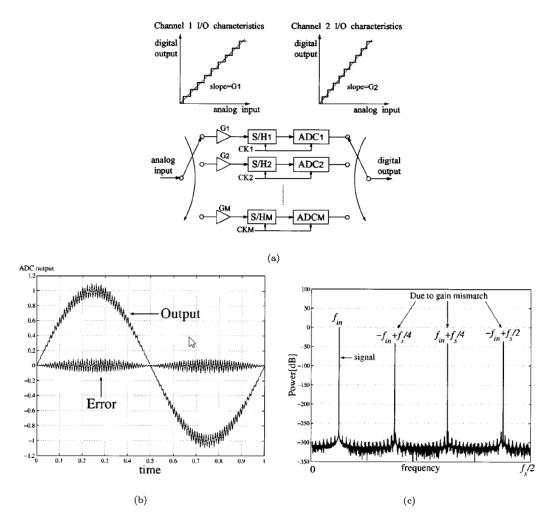

| Figure 14 输入增益误差的杂散分析                           | 13 |

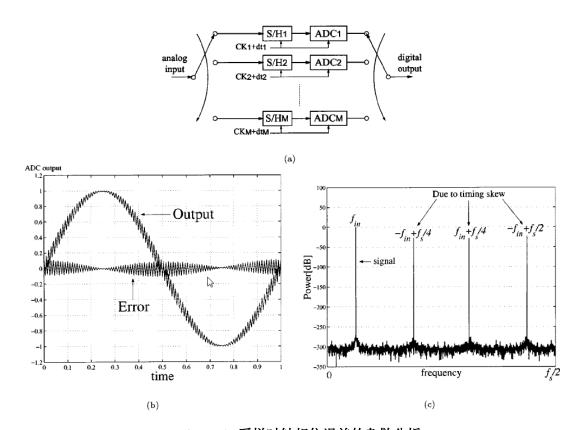

| Figure 15                                       | 14 |

| Figure 16 4 路 ADC interleave 示意                 | 15 |

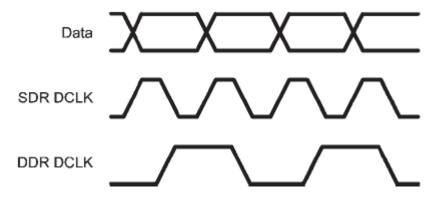

| Figure 17Giga ADC 数据输出时序                        | 16 |

| Figure 18ADC performance before the calibration |    |

| Figure 19 ADC performance after the calibration |    |

| Figure 20Before DES timing skew adjustment      |    |

| Figure 21After the DES timing skew ajustment    |    |

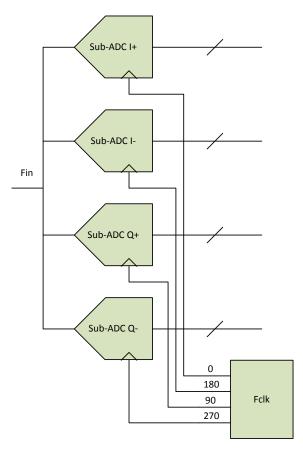

| Figure 22DESIQ 输入推荐架构                           | 18 |

# 1 Giga ADC 架构及 TI 的 Giga ADC

# 1.1 Giga ADC 架构演进

Giga ADC 目前已经广泛的应用于数据采集、仪器仪表、雷达和卫星通信系统;随着采样速率和精度的进一步提高,越来越多的无线通信厂商开始考虑使用 Giga ADC 实现真正的软件无线电。软件无线电不仅可以简化接收通道设计,同时可以方便不同平台的移植和升级,从而降低开发成本和周期。

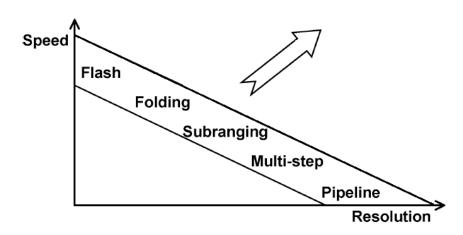

Figure 1 ADC 架构与输出精度关系

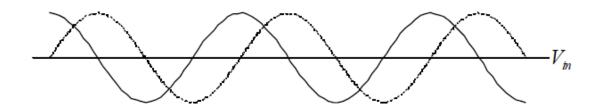

Figure 1 列出了在使用各种采样架构下,采样精度和采样速率之间关系。随着技术和工艺的发展,各种架构可以支持的采速率在不断的提升,但就目前的水平来看,要实现 1Gpbs 以上的采样率,必须采用 Flash 或者折叠 (Folding) 架构。

这主要是因为在其它架构中,都采用了反馈环路;这些反馈环路的传输延时限制了 ADC 速率的进一步提升。例如在 pipeline 中,每一级都有一个 DAC,用于把本级的数据输出转换成模拟信号,反馈给本级的模拟输入,取差以后放大输出给下一级。类似的限制也存在于 Subranging 或者 multi-step 架构中,都需要一个反馈环路辅助判决。

另一方面,虽然目前业界最快的 ADC 架构是 Flash 架构,但一个 N bit 的 flash ADC 需要 $2^{N}$ -1 个比较器,当 N>= 8 时,比较器的数量将会非常庞大;而且随着转换精度的增加,后端的译码逻辑也会变得异常复杂;这些都会对芯片的体积和功耗造成很大的影响。

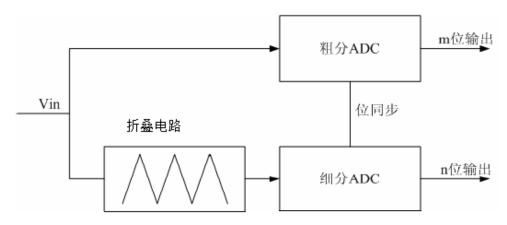

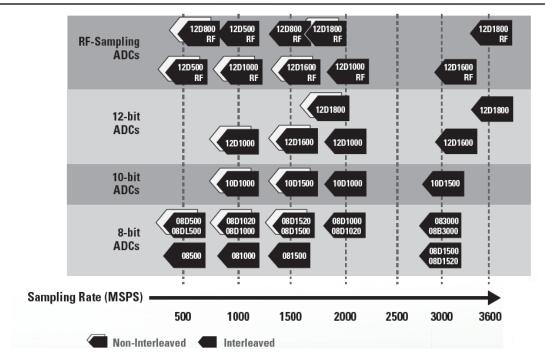

所以在 TI 的 Giga ADC 中,采用了折中的折叠(folding)架构。事实上,折叠是和 flash 类似的架构,不同的是,在折叠架构中,输入信号分别通过了粗分 ADC 和折叠电路+细分 ADC; 折叠电路的理想传输特性为三角状循环的折叠信号。以一个 8bit ADC 为例,粗分 ADC 输出 3bit,细分 ADC 输出5bit。如 Figure 2 和 Figure 3 所示,折叠电路共折叠了 8 次,将满量程的输入范围等分为 8 段,分别对应 3 位粗分 ADC 转换产生的高位 bit (MSB);同时对上述折叠电路输出信号进行 5 位细化转换得到低位 bit (LSB);最后高、低位数字码合起来组成 8 位的数字输出。

对于一个 8bit ADC,采用折叠电路架构所需要的比较器个数为 $2^m-1+2^n-1=38$ (m=3, n=5);如果采用 flash 架构,则需要比较器的个数为 $2^n-1=255$ (N=8)。显而易见,采用折叠架构大大降低了比较器的个数。

Figure 2 折叠 ADC 简化架构

Figure 3 折叠 ADC 原理

## 1.2 TI Giga ADC 产品介绍

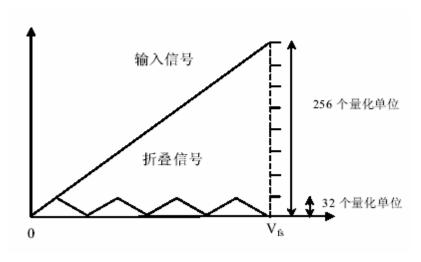

TI 在过去的十年当中,利用创新的 ADC 架构和工艺技术,不断的刷新业界 Giga ADC 的采样速率和转换精度,最新的产品已经可以达到 5Gbps @ 7.6bit (LM97600) 和 4Gpbs @ 12bit (ADC12D2000RF)。Figure 4 是目前 TI 全系列的 Giga ADC 产品:

Figure 4TI Giga ADC 产品系列

# 2 TI Giga ADC 架构介绍

本章节中将详细讨论 Giga ADC 的各个功能模块。在实际应用中,设计者一般都会采用 Folding + interpolation + calibration 的架构,用于进一步简化设计,降低功耗和提高精度。

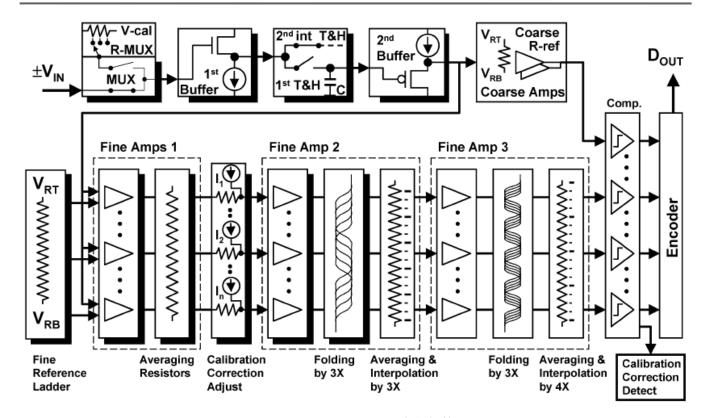

Figure 5 - ADC08D1520 内部架构

上图是一个典型的 folding-interpolation 架构的 Giga ADC 框图。在这类 ADC 中,为了解决模拟输入端的匹配误差和输入偏置误差,集成了一个校准信号源,在不需要外部输入的情况下,实现芯片的前台校准,使芯片达到最大性能。除此之外,还包括输入的 buffer,采保电路,folding-interpolation 电路以及比较器、encoder 和 LVDS 输出电路。

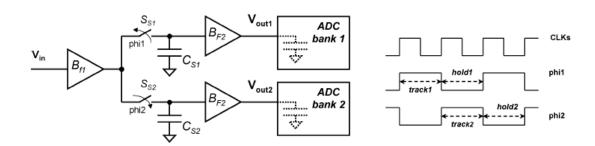

#### 2.1 Input mux

在 Figure 5 中可以看到,为了尽可能的把输入链路上所有器件包含到校准环路中,校准信号的输入 开关加在了输入电路的最 F 前端。这对开关电路的线性和带宽提出了很高的要求。在 TI 的 Giga ADC 电路中,采用了 constant Vgst NMOS pass-gate 电路,这种电路不仅宽频带内导通电阻稳定不变,失真小,而且功耗低。

电路校准只在器件上电或者器件工作温度发生明显变化的时候才会发起,输入校准开关也只在这个时候才会导通。

Figure 6Giga ADC 输入开关

#### 2.2 Interleaved T/H

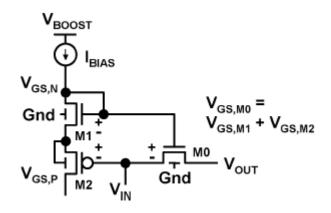

在高速 ADC 设计中,为了达到更高的采样速率,采用了 interleaved 的架构,即一个模拟输入,输入到两个相同的 ADC 中,但这两个 ADC 的采样速率相同,相位相反;最后芯片的数字部分把两路 ADC 的输出信号重新整合,达到了相对于每路 ADC 两倍的采样速率。将采样保持电路放在第一级 buffer 之后,主要是因为这一级 buffer 降低了输入信号的负载和 kickback 噪声,方便宽带匹配;同时降低了采保电路的工作频率,使得采保电路和第二级 buffer 的设计和功耗大大简化。

需要注意的是,在 interleaved 架构中,两路采样保持电路和 buffer 的偏置和增益误差,以及两路 采样时钟之间的相位误差,都会给整个 ADC 系统 SNR 带来很大的影响。在设计中,两路电路采用了完 全镜像的设计,同时两路电路都在校准环路里,有效的降低了这些误差带来的性能恶化。

Figure 7 Interleaved ADC 采保电路示意图

### 2.3 Preamplifier

预放大电路处于采保电路之后,比较器之前,包括第二级输入 buffer,折叠内插电路等。预放大电路的主要功能包括:输入信号的放大,以降低电路偏置误差对性能的影响;输入信号的折叠处理,将

输入信号通过折叠电路分成若干部分,从而降低比较器的个数;通过内插电路增加信号过零点,减少折叠电路模块。

#### **2.3.1** 第二级输入 buffer

第二级输入 buffer 的主要作用就是要把采保电路输出的伪差分信号通过差分放大器转换成真正的差分信号,以达到更好的电源抑制比和方便后级处理。第二级 buffer 输出的差分信号分成两路,一路输出给粗分转换电路,用于判决输入信号处于那一个折叠区;一路输出给细分转换电路,输出具体的转换数据。

#### 2.3.2 折叠电路

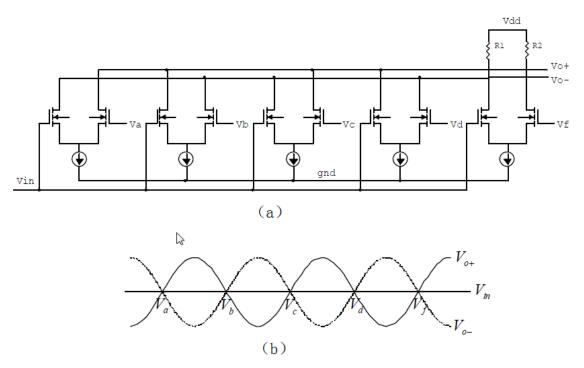

Figure 8 差分折叠电路

Figure 8 为一种实际折叠电路及其直流传输特性。Figure 8 (a) 中,输入信号 Vin 和 5 个量化参考电平 Va 、Vb 、Vc 、Vd 和 Vf ; 5 个源极耦合对的漏极交替连接,通过负载电阻 R1 和 R2 的 I/V 变换,形成一对 5 倍折叠(折叠率 F = 5)的差分折叠信号 Vo + 与 Vo - ,如 Figure 8 (b) 所示。Figure 8 (b) 中,直流传输特性上差分输出为零的点称为过零点。可见,除了过零点附近,实际折叠电路的传输特性存在着一定的非线性区域。为解决非线性区域上输入信号的量化问题,可采用两个具有一定相位差的折叠信号,如 Figure 9 所示。它们之间的相位差保证了各自的非线性区域相互错开。

Figure 9 双折叠电路输出波形

当一个折叠输出信号不是在线性区域范围内时,另一个折叠输出信号恰好在线性区域内,反之亦然。这种方法可以推广到相位差更小的一组折叠信号的情况,以减小非线性区域的影响。直至,相邻折叠信号的过零点只相距一个量化单位(LSB)时,每个与折叠电路连接的比较器只需检出过零点。此时,折叠结构 ADC 不再要求折叠信号的线性区域范围,只要求过零点的精度。

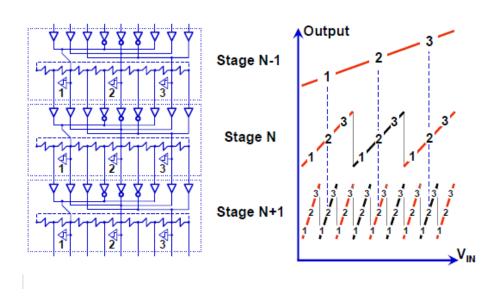

在折叠电路设计中,一级折叠电路折叠率不宜过高,这主要是因为,如果一级折叠率过高,那么这么多输出通过长的走线连接到一起输出给下一级比较器,寄生电容对于后级的影响变得不可忽略。在TI的 Giga ADC中,一般采用多级折叠电路级连的方式,例如,如果要实现一个折叠率为9的电路,采用了两级折叠级连,每级的折叠率是3,如 figure10 所示。

Figure 10 级联折叠电路示意图

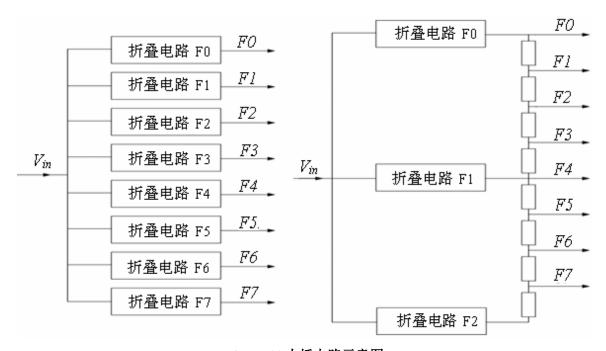

#### 2.3.3 内插电路

直接利用折叠电路来产生所有2<sup>N</sup>个过零点,ADC 的功耗与输入电容都很大。通常的解决办法是采用折叠一内插结构,如 Figure11 所示。每两个折叠电路的输出之间连接一个插值电阻串,利用插值电

阻的分压作用得到两个折叠电压信号之间的插值电压。每个插值节点作为输出,插值的数目称为内插率 I; Figure11 是当 I=4 的内插结果,两侧为原始的由折叠电路产生的折叠信号,夹在其间的 3 个信号是被节省的、由内插电路产生的折叠信号。这样,通过 4 倍的内插,每 4 个折叠信号可以节省 3 个折叠电路。

Figure 11 内插电路示意图

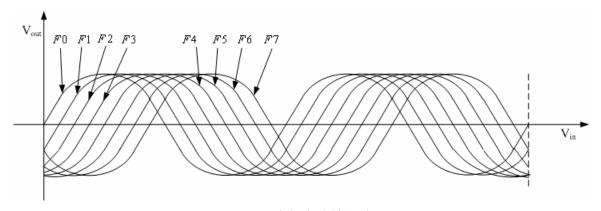

通过折叠内插电路的波形如下图所示:

Figure 12 内插电路输出波形

## 2.3.4 平均电路

前面提到,影响电路精度的主要误差是差分信号的偏置误差。降低差分电路的偏置误差可以增加晶体管的面积。但由于在折叠电路中,偏置误差不仅仅来自于差分电路,折叠电路中其它饱和支路的输出

电流也增加了整个电路的偏置误差,简单的增加电路晶体管面积并不能有效的降低误差。由于各个放 大电路的偏置误差是不相关的,这里采用了迭代的技术,使某一输出节点的偏置误差不仅仅取决于本 身放大电路,还和相邻其它并行放大电路输出有关,偏置误差通过放大电路输出的迭代而随机化,降 低了整个电路的偏置误差。

#### 2.4 校准电路

前面提到的各种设计电路有效的提高了 ADC 的线性性能和带宽,但在 TI Giga ADC,仍然集成了校准电路,用以进一步优化 ADC 的性能。这部分校准电路包括 27 个高精度校准电压,采用轮询的方式依次输入到输入级的开关,并根据校准信号的输出结果通过 DAC 调整预放大电路的偏置电流,达到校准修正的结果。

通过 Figure5 可以看到,输入级的 MUX 开关,采保电路,输入 buffer 的偏置误差以及折叠电路的偏置误差等包括在校准环路里,通过校准不仅仅提高了放大电路的线性,而且提高了系统在 interleave 模式下两路 ADC 之间的一致性,改善了系统的杂散性能。

## 3 Giga ADC 杂散的分析

ADC 应用中,输出的杂散信号决定了 ADC 的动态范围。在传统的流水线 ADC 中,起决定作用的主要是谐波杂散,即输入信号的二次、三次或更高次谐波混叠进入第一个 Nyquist 区。除此以外, Giga ADC 的 interleave 架构带来了其它杂散。如前文说提到的,为了达到更高的采样速率,每路 ADC 实际包括两个子 ADC, 这两个子 ADC 工作在 interleave 模式下。在这种情况下,两路子 ADC 之间的失配将会产生新的杂散信号。总体来说,Giga ADC 的杂散主要分为三类杂散信号: 1) interleave 杂散; 2) 固定频点杂散; 3) 和输入信号相关的杂散。

### 3.1 Interleave 相关的杂散

Interleave 模式,如 Figure 7 所示,就是相同的输入信号,输入到两个(或 N 个)采样率相同,但 采样时钟相位相反(或相差  $2\pi/N$ )的 ADC 中,从而达到采样率增倍的目的。但由于两路 ADC 不可能 完全一致,存在一些失配,从而导致了一些输出杂散的生成。这些失配包括偏置误差、增益误差以及 采样时钟的相位误差。

这里假定:

N: 一路 ADC 中包含的子 ADC 个数

Fin: 输入有用信号

Fnoise: 输出的杂散信号

Fs: ADC 采样时钟

### 3.1.1 输入偏置误差

Figure 13 输入偏置误差的杂散分析

假定 ADC 其它参数都是理想的,只考虑输入偏置误差。通过数学分析可以得到,输入偏置误差带来的 杂散主要分布在

## Fnoise = K\*Fs/N, K = 1, 2, 3...

#### Equation 1

从 Figure13 可以看出,输入偏置误差带来的杂散和输入信号的幅度和频率没有关系,从频域上看,均匀的分布在第一 Nyquist 区。由输入偏置带来的杂散固定的分布在公式一给出的各个频点。

## 3.1.2 输入增益误差

Figure 14 输入增益误差的杂散分析

假定输入电路除增益误差以外,其它参数都是理想的,可以看出当输入信号幅度增大时,增益误差也随之变大。输出的误差信号类似于输入信号的一个调幅输出,可以得到,增益误差导致的杂散信号出现位置如下:

## Fnoise =+/-Fin+ K\*Fs/N, K = 1, 2, 3... Equation 2

从分析可以看出,由于增益误差导致的输出杂散幅度和输入信号的频率无关,但和输入信号的幅度有关,输入信号幅度变大时,杂散幅度增加;反之亦然。

### 3.1.3 采样时钟的相位误差

Figure 15 采样时钟相位误差的杂散分析

如果两个或多个采样时钟之间存在相位误差(skew),同样会带来杂散。由于相位误差带来的误差最大出现在输入信号压摆率最大的地方,即过零点,即这类杂散类似于输入信号的调频输出。杂散信号出现的位置在:

Fnoise =+/-Fin+

$$K*Fs/N$$

,  $K = 1$ , 2, 3...

#### **Equation 3**

采样时钟的相位误差和输入增益误差带来的杂散位置相同,但相位误差输出的杂散和输入频率有关, 当输入频率越高,误差越大;而偏置误差和增益误差带来的杂散和输入频率无关。

#### 3.2 固定频点杂散

相对于 interleave 杂散,固定频点杂散和输入信号的频点无关,主要取决与系统时钟,ADC 及子 ADC 的采样时钟,数据输出的随路时钟以及系统中其他时钟源的耦合干扰。固定频点杂散因为位置固定,应用中很容易预判这些杂散,从而在系统设计中规避这些杂散存在的频点。

#### 3.2.1 采样时钟杂散

如 Figure 16 所示,当四个 ADC 工作在 interleave 模式下,四个 ADC 的采样率都是 Fclk,但相位相差 90 度,这样整个 ADC 通道的实际采样率为 4\*Fclk;输出的频谱中,在 Fclk 频点处有一个固定的采样时钟杂散。这个主要是时钟的泄露,采样时钟从芯片内部或板上耦合到数据的输出。

Figure 16 4 路 ADC interleave 示意

#### 3.2.2 数据输出的随路时钟

在 Giga ADC 中,数据的输出是并行 LVDS 总线;同时这些总线可以 1:2 Demux 或者 Non-demux;在 Non-demux,数据速率和采样速率是一致的;在 Demux 模式下,数据速率降低一倍,但数据总线增加一倍。同时,Giga ADC 数据输出的随路时钟可以是 DDR 或 SDR,如下图所示。在 Demux 和 DDR 同时使能的情况下,随路时钟 DCLK 只是采样时钟的 1/4,这个时钟杂散可能出现在 Fs/4 的地方。

Figure 17Giga ADC 数据输出时序

### 3.3 和输入相关的杂散

前面提到,和输入相关的杂散主要是输入信号的奇偶次谐波混叠进入 ADC 的第一 Nyquist 区。这类杂散主要通过外部的抗混叠滤波器加以滤除以及信号输入端的匹配,差分两端的平衡来优化。这类杂散在传统的 ADC 中已经讨论很多,这里就不再赘述。

## 3.4 杂散信号的优化

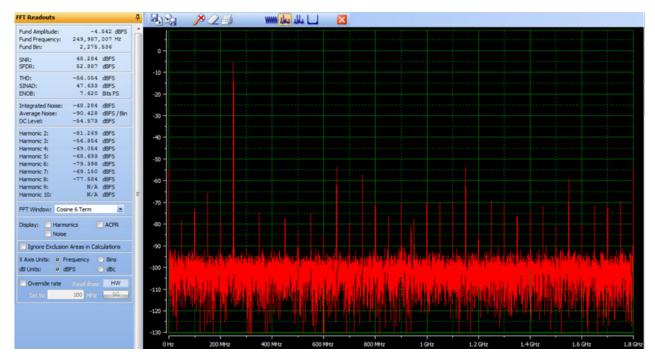

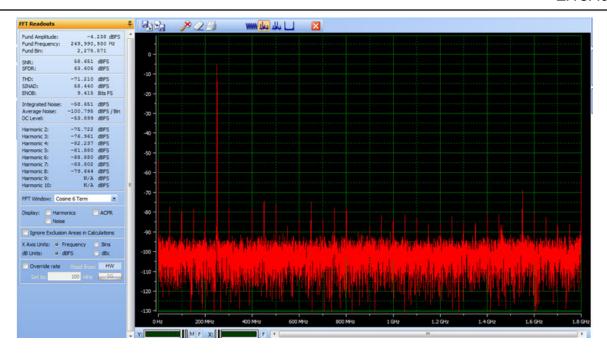

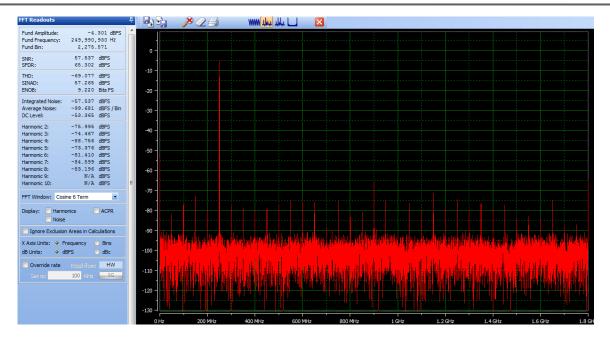

为了达到最佳的输出杂散性能,在 Giga ADC,主要采用了校准环路,来优化输入电路的偏置误差、增益误差。如下图所示,在校准前后,ADC 的性能可以优化 10dBc 以上。

Figure 18ADC performance before the calibration

Figure 19 ADC performance after the calibration

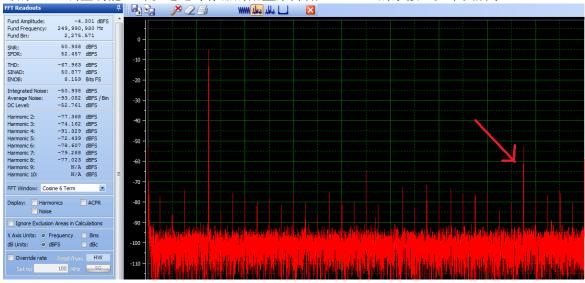

同时,当 Giga ADC 工作在 DES mode,两路采样时钟间的 skew 对于 Fs/2- fin 的杂散非常重要;芯片提供了两路采样时钟的 skew 调整功能,可以通过寄存器的配置来降低 Fs/2 – fin 的杂散,如下图所示。

Figure 20Before DES timing skew adjustment

Figure 21After the DES timing skew ajustment

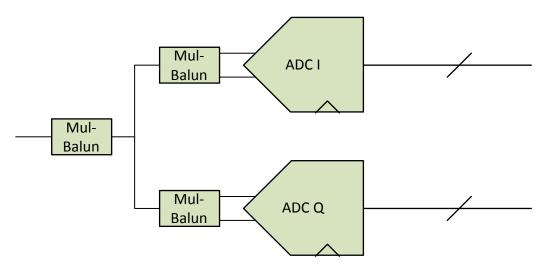

除此之外,ADC 的外部输入电路设计也需要尽量优化,确保两路差分电路的平衡一致,阻抗的匹配。 Giga ADC 提供了 DESI, DESQ, DESIQ, DESCLKIQ 等几种 DES 模式下输入结构;综合输入平坦度,插入损耗和最终的 ADC 性能测试结果,DESIQ 模式的性能最佳,并且推荐采用多层 Balun 和以下的输入电路。

Figure 22DESIQ 输入推荐架构

# 4 结论

本文主要介绍了 TI Giga ADC 采用的架构,通过这一先进的架构,TI 实现了业界最高采样率的 12bit/10bit ADC,并被广泛使用到了卫星、雷达、微波等通信领域。同时本文也分析介绍了 Giga ADC 中的输出杂散的形成原因,以及相应的优化措施。

# 5 参考资料

- 1. ADC08D1520 Datasheet

- 2. "Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems", Naoki Kurosawa, etc. 2001, IEEE

- 3. "A 1.8-V 1.6-GSample/s 8-b Self-Calibrating Folding ADC With 7.26 ENOB at Nyquist Frequency", Robert C. Taft, etc. 2004, IEEE

#### 重要声明

德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

|               |                                    |              |                          |

邮寄地址: 上海市浦东新区世纪大道 1568 号,中建大厦 32 楼 邮政编码: 200122 Copyright © 2013 德州仪器 半导体技术(上海)有限公司