# TI Designs High Speed: Verified Design TSW1266 Wideband RF-to-Digital Complex Receiver-Feedback Signal Chain

# 🔱 Texas Instruments

# **TI Designs High Speed**

TI Designs High Speed designs are analog solutions created by TI's analog experts. Verified Designs offer the theory, part selection, simulation, complete PCB schematic & layout, bill of materials, and measured performance of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed.

# **Design Resources**

| Design Zip File |  |

|-----------------|--|

| ADS5402         |  |

| LMH6521         |  |

| TSW1400EVM      |  |

| LMK04800        |  |

Simulations, PCB, Gerber, BOM Product Folder Product Folder Tool Folder LMK0480x Family Datasheet

# **Design Description**

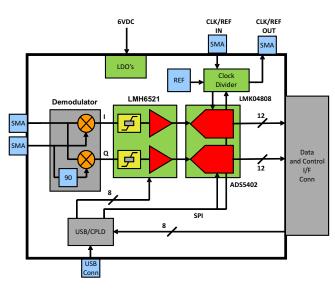

The TSW1266EVM is a wideband complex-receiver reference design and evaluation platform that is ideally suited for use as a feedback receiver for transmitter digital predistortion. The EVM signal chain is ideal for high intermediate-frequency (IF) complex-feedback applications and contains a complex demodulator, TI's LMH6521 dual-channel DVGA and ADS5402 12-bit 800-MSPS dual-channel ADC. By modifying the onboard filter components, the signal chain is configurable for a variety of frequency plans. The EVM also includes TI's LMK04808 dual-PLL clock jitter cleaner and generator to provide an onboard low-noise clocking solution. The LMH6521 DVGA gain is controlled through the GUI or alternatively through the high speed connector with an FPGA.

ASK Our Analog Experts WebBench Calculator Tools TI Designs Precision Library

1

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

Windows is a registered trademark of Microsoft Corporation. All other trademarks are the property of their respective owners.

2

# 1 Introduction

### 1.1 Overview

The TSW1266EVM evaluation module is a wideband, complex receiver reference design and evaluation platform. The signal chain is ideal for high intermediate frequency (IF) complex feedback applications. The signal chain has a wideband complex demodulator, the LMH6521 dual-channel, digitally controlled variable gain amplifier (DVGA), and the ADS5402 12-bit 800-MSPS analog-to-digital converter (ADC). The TSW1266EVM also includes the LMK04800 dual-PLL clock jitter cleaner and generator to provide an onboard low-noise clocking solution. A provided software GUI allows for configuration of the ADS5402 and LMK04800. Either the GUI or an FPGA using the high-speed connector can control the gain of the LMH6521 DVGA. The EVM mates with the TSW1400 pattern capture and generation card to capture data from the ADS5402. Then, the High Speed Data Converter Pro software tool can perform signal analysis. The TSW1266EVM product folder on the TI web site contains the EVM schematic, bill of materials, and layout files (http://www.ti.com/tool/tsw1266evm).

The default configuration of the board allows for an RF frequency of 1880 MHz to 2390 MHz and an LO frequency around 2600 MHz. The IF portion of the board, starting at the output of the demodulator to the ADC input, is set for a center frequency of 460.8 MHz and a 3-dB bandwidth of 500 MHz. Modification of both the RF and IF frequency ranges is possible.

A software GUI allows for configuring the ADS5402 and LMK04800. The GUI, or alternatively through the high-speed connector with an FPGA, can control the gain of the LMH6521 DVGA. The EVM mates with the TSW1400 pattern capture and generation board to capture data from the ADS5402. The High Speed Data Converter Pro software tool then can perform signal analysis. The TSW1400 and High Speed Data Converter Pro greatly simplify the evaluation process by providing the hardware and software necessary for pattern capture and analysis.

3

# 1.2 Block Diagram

Figure 1 shows the block diagram of the TSW1266EVM.

### 2 Software Control

This section provides installation instructions and explanations of the TSW1266 GUI.

### 2.1 Installation Instructions

- 1. The software can be downloaded from the TSW1266EVM production page on www.ti.com. Find the page by searching for *TSW1266EVM*. The software appears under the *Related Products* section on the *TI Software* tab.

- 2. Extract the files from the zip file named *TSW1266 GUI vXpY Installer.zip* where *XpY* represents the version number.

- 3. Run setup.exe, and follow the installation prompts.

- Start the GUI by going to Start Menu → All Programs → Texas Instruments ADCs → TSW1266 GUI.

- 5. When plugging the board into the computer for the first time through the USB cable, you are prompted to install the USB drivers.

- Windows® XP: If Windows XP does not automatically install the drivers, follow the prompts on the screen to do so. Do not let Windows XP search Microsoft Update for the drivers, but do let Windows XP install the drivers automatically.

- Windows 7: After installing the TSW1266 GUI, Windows 7 should automatically be able to install the drivers for the TSW1266EVM with no input from the user.

# 2.2 Software Operation

4

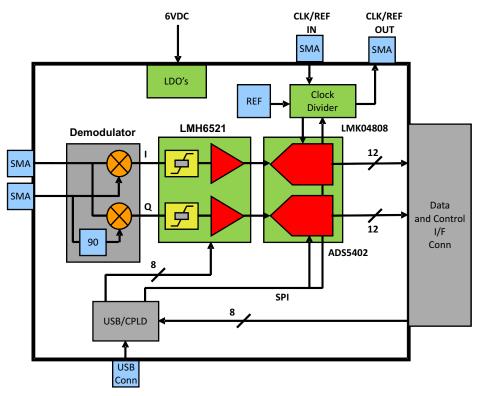

The TSW1266 GUI allows the user to program the ADS5402, LMH6521, and LMK04800 for proper operation. The controls for each device are split between different tabs for a simplified interface. Detailed descriptions for each tab are below.

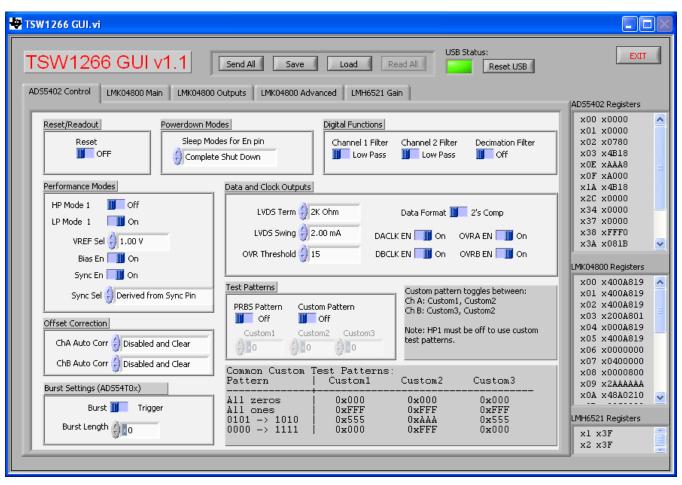

#### 2.2.1 ADS5402 Control Tab

# Figure 2. ADS5402 Control Tab

| Table 1. ADS5402 Control | <b>Tab Section Descriptions</b> |

|--------------------------|---------------------------------|

|--------------------------|---------------------------------|

| Section                | Description                                                                            |

|------------------------|----------------------------------------------------------------------------------------|

| Reset/Readout          | Allows software reset of the ADS5402 registers. The device should be reset on startup. |

| Powerdown Modes        | Control the Enable pin functionality.                                                  |

| Digital Functions      | Enable the decimation filters and set the filter type.                                 |

| Performance Modes      | Control performance modes of the ADS5402. HP Mode 1 should be on for proper operation. |

| Data and Clock Outputs | Control the LVDS data lines and data format, also control the overrange functionality. |

| Offset Correction      | Enable or disable automatic interleaving correction.                                   |

| Burst Settings         | Configure the high resolution burst mode. Only applicable to the ADS54T0x family.      |

| Test Patterns          | Enable and set test patterns to verify the digital interface.                          |

Software Control

www.ti.com

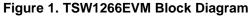

#### 2.2.2 LMK04800 Main Tab

| SW1266 GUI v1.1                                                                                                                                                                                                                                                                               | end All Save Load R                                                                                                                                                                                                                                                                                                                                       | USB Status:<br>ead All Reset USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EXI                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS5402 Control LMK04800 Main LMK04800 Output   Power Down, Reset, Mode Select Mode Select   Power Down Reset Mode Select   CLKin Settings CLKin_SELECT_MODE EN CLKin0   Pin Select Mode CLKin0 BUF Type Bipolar   CLKin1 BUF Type Bipolar O   CLKin0 PreR Div CLKin1 PreR Div CLKin1 PreR Div | Dual PLL, Internal VCO   VCO Divider   VCO Divider   VCO Divider   VCO Divider   Preedback MUX   CLKout0                                                                                                                                                                                                                                                  | ain<br>DSCout<br>PD OSCin Divider<br>EN OSCout0 Divider<br>EN OSCout1 Divider<br>DSCout1 Divider<br>B OSCout1 Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divider<br>Divi | AD55402 Registers<br>x00 x0000<br>x01 x0000<br>x02 x0780<br>x03 x4B18<br>x0E xAAA8<br>x0F xA000<br>x1A x4B18<br>x2C x0000<br>x34 x0000<br>x37 x0000<br>x36 xFFF0<br>x3A x081B<br>LMK04800 Registers                                  |

| 1   1     PLL 1 Settings   CP Tri-state     SYNC PLL1   CP Pol     P Divider   CP Pol     96   192     96   192     Window Size   DLD Count     CP Gain   100 uA     PLL1 N Delay   PLL1 R Delay     D ps   0 ps     0 ps   0 ps                                                              | PLL 2 Settings     EN XTAL   SYNC PLL2     Prescalar   R Divider   N Divider     2   1   4   1   48     PLL2 Fast PDF   N Cal Divider   1   48     PLL2 Fast PDF   N Cal Divider   1   48     Ref Frequency   XTAL Level   1   1     Normal (1x)   1   1   1   5     OSCin Frequency   \$255 MHz to 400 MHz   \$255 MHz to 400 MHz   \$255 MHz to 400 MHz | 3.7 ns 🖌 Neg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | x00 x400A819<br>x01 x400A819<br>x02 x400A819<br>x03 x200A801<br>x04 x000A819<br>x05 x400A819<br>x06 x0000000<br>x07 x0400000<br>x07 x0400000<br>x08 x0000800<br>x09 x2AAAAA<br>x0A x48A0210<br>LMH6521 Registers<br>x1 x3F<br>x2 x3F |

Figure 3. LMK04800 Main Tab

| Section                        | Description                                                                                                            |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Power Down, Reset, Mode Select | Allows for powering down and resetting the part, also controls the mode of the LMK04800.                               |

| CLKin Settings                 | Enabled and select the input clock source, input buffer types, and dividers.                                           |

| VCO Divider                    | Set the VCO divider to reduce the frequency on the clock distribution path. It is recommended to use the VCO directly. |

| OSCout                         | Control power to the OSCin port, also enable and change parameters of the OSCout pins.                                 |

| PLL 1 Settings                 | Configure PLL 1 settings when using the dual PLL mode.                                                                 |

| PLL 2 Settings                 | Configure PLL 2 settings for both dual and single PLL mode.                                                            |

Copyright © 2013, Texas Instruments Incorporated

# Table 2. LMK04800 Main Tab Section Descriptions

6

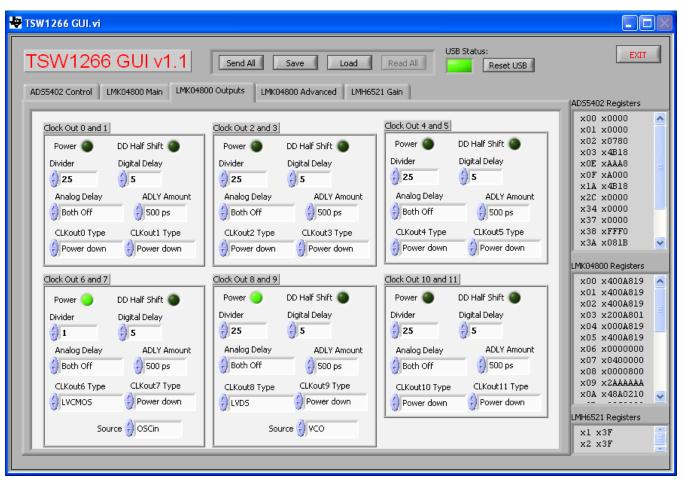

#### 2.2.3 LMK04800 Outputs Tab

Figure 4. LMK04800 Outputs Tab

| Section             | Description                                                                                                                                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Out 0 and 1   | Configure Clock Out 0 and 1 outputs. Enable the outputs and set the divider, delay, and output buffer.                                        |

| Clock Out 2 and 3   | Configure Clock Out 2 and 3 outputs. Enable the outputs and set the divider, delay, and output buffer.                                        |

| Clock Out 4 and 5   | Configure Clock Out 4 and 5 outputs. Enable the outputs and set the divider, delay, and output buffer.                                        |

| Clock Out 6 and 7   | Configure Clock Out 6 and 7 outputs. Enable the outputs and set the divider, delay, and output buffer, also select the source for the output. |

| Clock Out 8 and 9   | Configure Clock Out 8 and 9 outputs. Enable the outputs and set the divider, delay, and output buffer, also select the source for the output. |

| Clock Out 10 and 11 | Configure Clock Out 10 and 11 outputs. Enable the outputs and set the divider, delay and output buffer.                                       |

Copyright © 2013, Texas Instruments Incorporated

### Table 3. LMK04800 Outputs Tab Section Descriptions

Software Control

🖶 TSW1266 GUI.vi USB Status: EXIT TSW1266 GUI v1.1 Send All Save Load Read All Reset USB AD55402 Control LMK04800 Main LMK04800 Outputs LMK04800 Advanced LMH6521 Gain ADS5402 Registers x00 x0000 ^ DAC Vtune Rail Detection SYNC Status Pins Setup x01 x0000 Status\_CLKin0\_MUX x02 x0780 SYNC\_QUAL 🔘 Status\_CLKin0\_TYPE EN\_SYNC 😑 EN\_VTUNE\_RAIL\_DET x03 x4B18 \ominus Input w/ pull-down 쉬 Logic Low SYNC\_EN\_AUTO EN MAN DAC XOE XAAA8 SYNC Polarity xOF xA000 DAC High Trip Status\_CLKin1\_TYPE Status\_CLKin1\_MUX x1A x4B18 🗧 Active Low 쉬 1 x Vcc / 64 😓 Input w/ pull-down 🗧 Logic Low x2C x0000 SYNC Type x34 x0000 LD TYPE DAC Low Trip x37 x0000 싉 Input w/ pull-up EN LOS 🙆 쉬 1 x Vcc / 64 🗧 Output (push-pull) x38 xFFF0 SYNC MUX x3A x081B ¥ Manual DAC LD MUX LOS\_TIMEOUT 🗧 Logic Low 🗧 PLL1 & 2 DLD 쉬 1200 ns, 420 kHz LMK04800 Registers 쉬 512 x Vcc / 1023 NO\_SYNC\_CLKoutX\_Y x00 x400A819 ^ 0\_1 2\_3 4\_5 6\_7 8\_9 10\_11 DISABLE\_DLD1\_DET CLKin\_Sel\_INV x01 x400A819 x02 x400A819 Readback LE uWire Lock x03 x200A801 Holdover Mode 🗧 LE Low 쉬 Registers Unlocked x04 x000A819 x05 x400A819 EN\_TRACK HOLDOVER MODE HOLDOVER TYPE x06 x0000000 🗧 Enabled 😸 Output (push-pull) 🗧 Enabled x07 x0400000 x08 x0000800 HOLDOVER MUX HOLDOVER DLD CNT FORCE HOLDOVER х09 х2АААААА 🗧 uWire Readback 쉬 512 x0A x48A0210 ~ LMH6521 Registers x1 x3F x2 x3F

# Figure 5. LMK04800 Advanced Tab

| Table 4. LMK04800 Advanced Tab Section Description |

|----------------------------------------------------|

|----------------------------------------------------|

| Section                  | Description                                                                                |

|--------------------------|--------------------------------------------------------------------------------------------|

| SYNC                     | Enable and configure the sync functionality.                                               |

| DAC Vtune Rail Detection | Enable and control the internal DAC settings.                                              |

| Status Pins Setup        | Setup the status pins for various outputs as well as control some miscellaneous functions. |

| Holdover Mode            | Enable and configure holdover mode.                                                        |

8

2.2.5

LMH6521 Gain Tab

| 🖶 TSW1266 GUI.vi                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSW1266 GUI v1.1 Send All Save Load Read All Reset USB                        | EXIT                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADS5402 Control LMK04800 Main LMK04800 Outputs LMK04800 Advanced LMH6521 Gain | AD55402 Registers     x00 x0000     x01 x0000     x02 x0780     x03 x4B18     x0F xAA00     x1A x4B18     x2C x0000     x34 x0000     x34 x0000     x37 x0000     x38 xFF0     x34 x0018     x00 x400A819     x01 x400A819     x01 x400A819     x01 x400A819     x04 x400A819     x05 x400A819     x05 x400A819     x06 x000000     x07 x0400000     x08 x000800     x09 x20AAAAA     x0A x48A0210     X1 x3F     x2 x3F |

Figure 6. LMH6521 Gain Tab

# Table 5. LMH6521 Gain Tab Section Descriptions

| Section   | Description                                |

|-----------|--------------------------------------------|

| Channel A | Set the gain for channel A of the LMH6521. |

| Channel B | Set the gain for channel B of the LMH6521. |

9

# 2.2.6 Send All, Save, Load, Read All

Figure 7. Send All, Save, Load, and Read All

#### Table 6. Send All, Save, Load, and Read All Descriptions

| Section  | Description                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| Send All | Click to send all the registers for all devices. Press a few times if the board does not seem to be responding correctly. |

| Save     | Save the register settings in a text file. Can be reloaded later to set the GUI and devices to a known state.             |

| Load     | Load a saved configuration.                                                                                               |

| Read All | This function is not currently enabled on the TSW1265 GUI.                                                                |

#### 2.2.7 USB Status

The indicator shows the status of the USB connection. The indicator is lit when the USB connection is valid. If the computer is not connected to the board, click the **Reset USB** button.

# 2.2.8 Exit

Click to exit the GUI. Note that the X in the upper right corner of the window has been disabled to ensure that the USB connection is closed properly.

### 3 Basic Test Procedure

### 3.1 TSW1400 Setup

See the TSW1400 User's Guide (<u>SLWU079</u>) for a more detailed explanation of the TSW1400 setup and its features. This document assumes that the High Speed Data Converter Pro software and the TSW1400 pattern capture and generation board are both installed and functioning properly. This information can be found at <u>http://www.ti.com/tool/tsw1400evm</u>.

### 3.2 Quick-Start Procedure

#### 3.2.1 TSW1400 Data Capture Card

- 1. Connect a 5-V power supply to connector J12 of the TSW1400. Flip switch SW7 to the ON position.

- 2. Insert a USB cable into the USB port on the TSW1400. Connect the other end to the PC.

# 3.2.2 TSW1266EVM

1. Connect a 6-V power supply to either the banana jacks or the barrel connector. If using the banana jacks, connect the positive end to J17 and the negative end to J16.

Basic Test Procedure

- 2. Connect a USB cable between the TSW1266 board and the PC.

- 3. Connect a 10-MHz reference (such as the one from the back of the signal generator) to the CLKIN SMA connector on the TSW1266. If a 10-MHz reference is not available, it is still possible to use the onboard clocking solution.

- 4. Connect an LO source to the SMA connector labeled LO. Set the LO source to 2600 MHz and 0 dBm.

- 5. Connect an RF source to the SMA connector labeled *RF*. Because the DVGA may come up with an unknown gain, set the amplitude of the RF input to –30 dBm to prevent overdriving the ADC on startup. Set the frequency to 2140.9 MHz.

- 6. Connect the TSW1266 to the TSW1400 by connecting J1 on the TSW1266 to the ADC Interface connector on the bottom of the TSW1400.

# 3.2.3 TSW1266 GUI

- Start the TSW1266 GUI by going to Start Menu → All Programs → Texas Instruments ADCs → TSW1266 GUI.

- Make sure the green indicator is lit indicating that the TSW1266 board has been successfully connected to the PC. If not, click the **Reset USB** button. If it still is not lit, check the USB connection. If the USB connection is correct, unplug the USB cable, wait five seconds and then plug it back in. Repeat these steps if necessary.

- 3. Click on the ADS5402 tab and toggle the *RESET* switch a few times. Repeat this step for the LMK04800 tab as well. The LMK04800 and ADS5402 need to be RESET for proper operation.

- 4. Click the **Load** button. If a 10-MHz reference was plugged into the CLKIN connector, select the file named *LMK04808\_614p4M\_Dual\_Loop\_10M\_Ref.txt*. If a 10-MHz reference was not available, select the file named *LMK04808\_614p4M\_Single\_Loop.txt*. Click *Ok*. The file is located in the TSW1266 GUI installation directory in the folder named *Configuration Files*.

- 5. Click Send All. At this point, the LED labeled D1 on the TSW1266 should be lit indicating a PLL lock. If it is not lit, click Send All again.

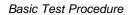

### 3.2.4 High Speed Data Converter Pro

- 1. Start the High Speed Data Convert Pro software tool by going to Start Menu  $\rightarrow$  All Programs  $\rightarrow$  Texas Instruments ADCs  $\rightarrow$  High Speed Data Converter Pro.

- 2. When it prompts for the serial number of the board, select the serial number that represents the TSW1400 that has been connected to the TSW1266. This number should be on a sticker on the TSW1400.

- 3. In the *Select ADC* drop-down box select *ADS5402*. If it asks to download the firmware select *Yes*. Multiple LEDs will light up on the TSW1400 once the firmware has finished downloading.

- 4. Select Single Tone from the Test Selection drop-down menu.

- 5. At the bottom left corner, enter 614.4M into the ADC Sampling Rate (Fs) box. Enter 459.1M into the ADC Input Target Frequency box. Press the Enter key.

- All boards and software are now set up. Click the Capture button. Once the capture is complete, adjust the input source amplitude and LMH6521 gain as needed. The LMH6521 gain can be changed on the LMH6521 Gain tab of the TSW1266 GUI. An example of a –1-dBFS plot is shown in the figure below.

Figure 8. TSW1266 Sample Capture using the TSW1400

# 3.3 **Optional Features and Configurations**

### 3.3.1 Clocking

The TSW1266EVM allows for multiple clocking configurations by using the LMK04800 clock jitter cleaner and generation chip. The board comes preinstalled with a 122.88-MHz VCXO which can be used to generate the sampling clock. A 10-MHz reference can be applied to the CLKIN connector to synchronize the onboard clock with the signal sources. Otherwise, the onboard VCXO can be used to generate a non-synchronous clock or clock distribution mode can be used.

The TSW1266 board comes preinstalled with the LMK04808 which has an internal VCO frequency range of 2750 MHz to 3072 MHz. If the desired clock cannot be derived from this frequency range using integer dividers, then this device can be swapped out for another LMK04800 with a different VCO range. Consult the LMK04800 datasheet (SNAS489) to determine which LMK04800 will provide the correct VCO range for the needed clocking frequency.

The LMK04800 can be setup in clock distribution mode or as a clock generator using single or dual PLL mode. The different modes of operation are discussed below.

• External Clock Mode: The LMK04800 can be setup in clock distribution mode to allow the use of an external clock source. This can be used for coherent sampling by provided a clock that is synchronized to the RF and LO signal sources. The TSW1266 GUI includes a configuration file for the external clock mode. This file is located in the TSW1266 GUI installation directory in the folder *Configuration Files* and is named *external\_clock.txt*. The file can be loaded by clicking the Load button, navigating to the correct folder, selecting the file, and clicking *Ok*. Click *Send All* a few times to make sure the board is configured properly. The user provides an external clock through the *CLKIN1* SMA connector on the TSW1266 board.

- Onboard Clock using Single PLL Mode: In this mode, the 122.88-MHz VCXO is used to generate other frequencies by using the single PLL mode of the LMK04800. The 122.88-MHz VCXO acts as the reference for the PLL and the divided down internal VCO acts as the clock source. There is an included configuration file that will setup the LMK04800 in single PLL mode and generate a 614.4-MHz sampling clock for the ADS5402. This file is located in the TSW1266 GUI installation directory in the folder *Configuration Files* and is named *LMK04808\_614p4M\_Single\_Loop.txt*. The file can be loaded by clicking the Load button, navigating to the correct folder, selecting the file, and clicking *Ok*. Click *Send All* a few times to make sure the board is configured properly. The LED labeled *D1* on the board will light up indicating that the PLL is locked.

- Onboard Clock using Dual PLL Mode: This mode of operation allows the user to provide a low frequency reference through the CLKIN1 connector to generate a synchronized sampling clock. The reference can come from any source, such as a 10-MHz reference from a piece of test equipment. This allows for synchronization between all signal sources and for coherent sampling. There is an included configuration file that will setup the LMK04800 in dual PLL mode and generate a 614.4-MHz sampling clock for the ADS5402. This file is located in the TSW1266 GUI installation directory in the folder *Configuration Files* and is named *LMK04808\_614p4M\_Dual\_Loop\_10M\_Ref.txt*. The file can be loaded by clicking the Load button, navigating to the correct folder, selecting the file, and clicking *Ok*. Click *Send All* a few times to make sure the board is configured properly. The LED labeled *D1* on the board will light up indicating that both PLLs are locked. For other output or reference frequencies, use the Clock Design Tool (http://www.ti.com/tool/clockdesigntool) to design the PLL settings.

# 3.3.2 Changing the RF and LO Frequencies

The default RF frequency range is 1880 MHz to 2390 MHz. The default LO frequency range is around 2600 MHz. These ranges are set by the matching networks on the RF and LO inputs of the demodulator. These matching networks can be changed based on the data sheet of the part.

# 3.3.3 Changing the IF Frequency

The IF frequency of the TSW1266 is fixed due to the LC filters on the board. There is a filter between the demodulator and the LMH6521 and a filter between the LMH6521 and the ADS5402. These filters provide an overall 3-dB bandwidth of 500 MHz centered at 460.8 MHz. To change the IF frequency of the TSW1266, the user must change the filters that are implemented on the board. There are many tools available for download online that will calculate a filter design based on frequency and ripple requirements. Use these tools to get a starting point for the filter design. Due to parasitic capacitance and inductance on the board, the user must interactively tune the filter to achieve the desired response. Once the filter has been designed for one channel, it can be implemented on the other channel as well.

# 3.3.4 Using the High-Speed Connector to Set the DVGA Gain

The high-speed connector (J1) on the TSW1266 board has connections that allow a user to change the gain of the LMH6521 quickly. Pins 105, 107, 109, 111, 113, 115, 117, and 119 on the connector can be used to pass the gain and latch signals from an FPGA to the DVGA. To use this feature, the jumper JP9 needs to be moved between pins 2 and 3. This configures the CPLD to route the gain from the connector rather than from the USB connection.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated