## SimpleLink™ Wi-Fi® CC323x

### Technical Reference Manual

Literature Number: SWRU543B JANUARY 2019 – REVISED JUNE 2025

## **Table of Contents**

| Read This First                                          | 25 |

|----------------------------------------------------------|----|

| Audience                                                 | 25 |

| About This Manual                                        | 25 |

| Register Bit Conventions                                 | 25 |

| Glossary                                                 |    |

| Related Documentation                                    | 26 |

| Community Resources                                      |    |

| Trademarks                                               |    |

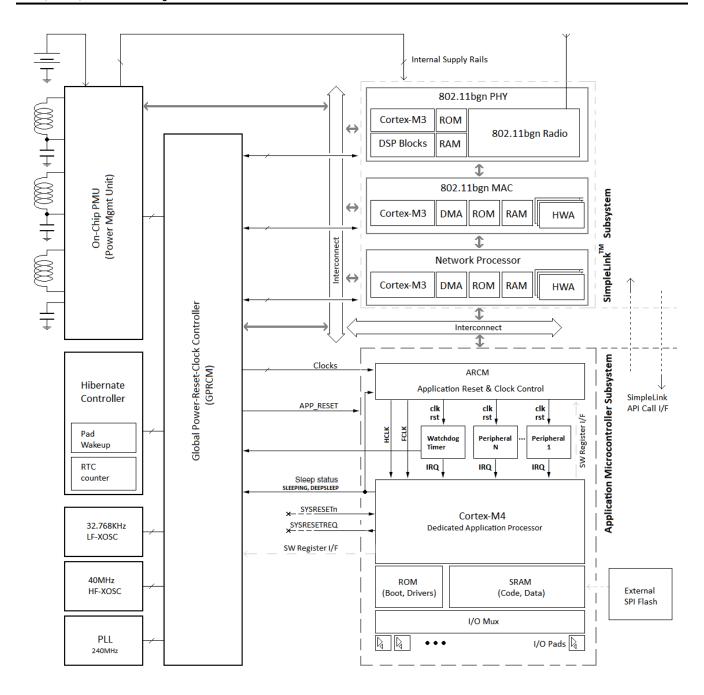

| 1 Architecture Overview                                  |    |

| 1.1 Introduction                                         |    |

| 1.2 Architecture Overview                                | 30 |

| 1.3 Functional Overview                                  |    |

| 1.3.1 Processor Core                                     |    |

| 1.3.2 Memory                                             |    |

| 1.3.3 Micro-Direct Memory Access Controller (µDMA)       |    |

| 1.3.4 General-Purpose Timer (GPT)                        |    |

| 1.3.5 Watchdog Timer (WDT)                               |    |

| 1.3.6 Multichannel Audio Serial Port (McASP)             |    |

| 1.3.7 Serial Peripheral Interface (SPI)                  |    |

| 1.3.8 Inter-Integrated Circuit (I2C) Interface           |    |

| 1.3.9 Universal Asynchronous Receiver/Transmitter (UART) |    |

| 1.3.10 General-Purpose Input/Output (GPIO)               |    |

| 1.3.11 Analog-to-Digital Converter (ADC)                 |    |

| 1.3.12 SD Card Host                                      |    |

| 1.3.13 Parallel Camera Interface                         |    |

| 1.3.14 Debug Interface                                   |    |

| 1.3.15 Hardware Cryptography Accelerator                 |    |

| 1.3.16 Clock, Reset, and Power Management                |    |

| 1.3.17 SimpleLink™ Subsystem                             |    |

| 1.3.18 I/O Pads and Pin Multiplexing                     |    |

| 2 Cortex®-M4 Processor                                   |    |

| 2.1 Overview                                             |    |

| 2.1.1 Block Diagram                                      |    |

| 2.1.2 System-Level Interface                             |    |

| 2.1.3 Integrated Configurable Debug                      |    |

| 2.1.4 Trace Port Interface Unit (TPIU)                   |    |

| 2.1.5 Cortex®-M4 System Component Details                |    |

| 2.2 Functional Description                               |    |

| 2.2.1 Programming Model                                  |    |

| 2.2.2 Register Description                               |    |

| 2.2.3 Memory Model                                       |    |

| 2.2.4 Exception Model                                    | 52 |

| 2.2.5 Fault Handling                                     |    |

| 2.2.6 Power Management.                                  |    |

| 2.2.7 Instruction Set Summary                            |    |

| 3 Cortex®-M4 Peripherals                                 |    |

| 3.1 Overview                                             |    |

| 3.2 Functional Description                               |    |

| 3.2.1 System Timer (SysTick)                             |    |

| 3.2.2 Nested Vectored Interrupt Controller (NVIC)       |     |

|---------------------------------------------------------|-----|

| 3.2.3 System Control Block (SCB)                        |     |

| 3.3 Register Map                                        |     |

| 3.3.1 Cortex Registers                                  |     |

| 4 Direct Memory Access (DMA)                            |     |

| 4.1 Overview                                            |     |

| 4.2 Functional Description                              |     |

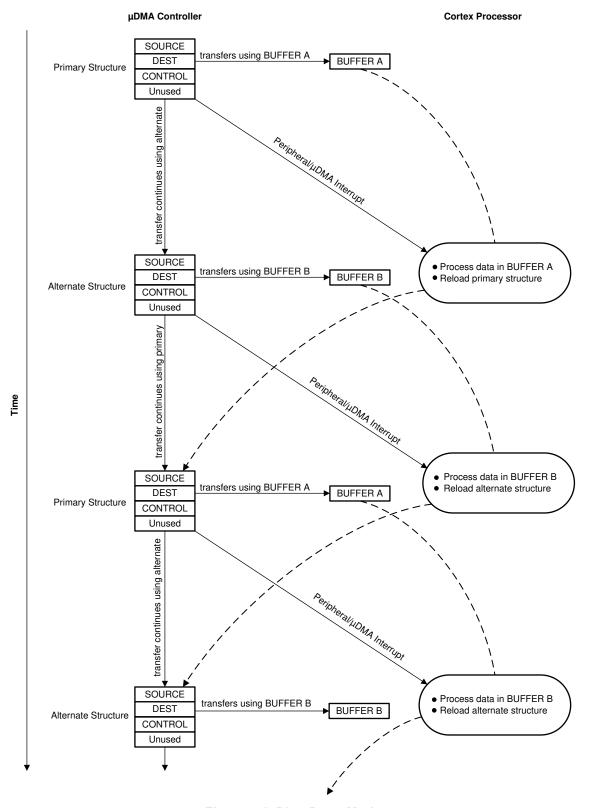

| 4.2.1 Channel Assignment                                |     |

| 4.2.2 Priority                                          |     |

| 4.2.3 Arbitration Size                                  |     |

| 4.2.4 Channel Configuration                             |     |

| 4.2.5 Transfer Mode                                     |     |

| 4.2.6 Transfer Size and Increment                       |     |

| 4.2.7 Peripheral Interface                              |     |

| 4.2.8 Interrupts and Errors.                            |     |

| 4.3 Register Description                                |     |

| 4.3.1 DMA Register Map                                  |     |

| 4.3.2 pDMA Channel Control Structure                    |     |

| 4.3.3 DMA Registers                                     | 123 |

| 4.3.4 DMA_(OFFSET_FROM_DMA_BASE_ADDRESS) Registers      | 127 |

| 5 General-Purpose Input/Outputs (GPIOs)                 |     |

| 5.1 Overview                                            |     |

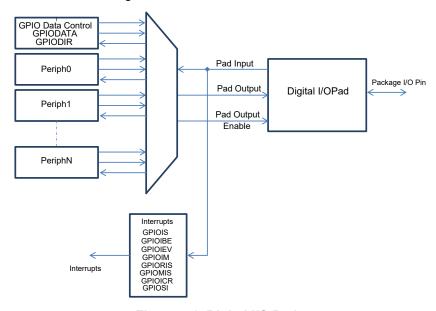

| 5.2.1 Data Control                                      |     |

| 5.2.1 Data Control                                      |     |

| 5.3.1 µDMA Trigger Source                               |     |

| 5.3.1 µDIVIA Trigger Source                             |     |

| 5.5 GPIO Registers                                      |     |

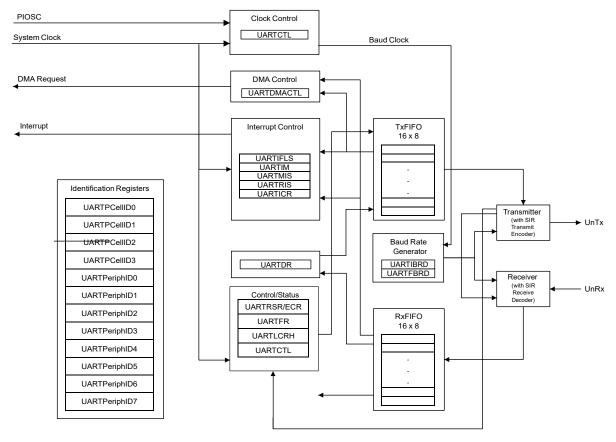

| 6 Universal Asynchronous Receivers/Transmitters (UARTs) |     |

| 6.1 Overview                                            |     |

| 6.1.1 Block Diagram.                                    |     |

| 6.2 Functional Description                              |     |

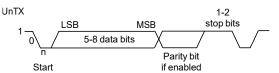

| 6.2.1 Transmit and Receive Logic.                       |     |

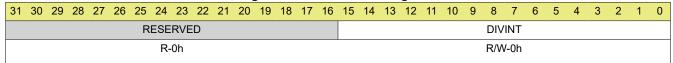

| 6.2.2 Baud-Rate Generation                              |     |

| 6.2.3 Data Transmission.                                |     |

| 6.2.4 Initialization and Configuration.                 |     |

| 6.3 UART Registers                                      |     |

| 7 Inter-Integrated Circuit (I2C) Interface              |     |

| 7.1 Overview                                            |     |

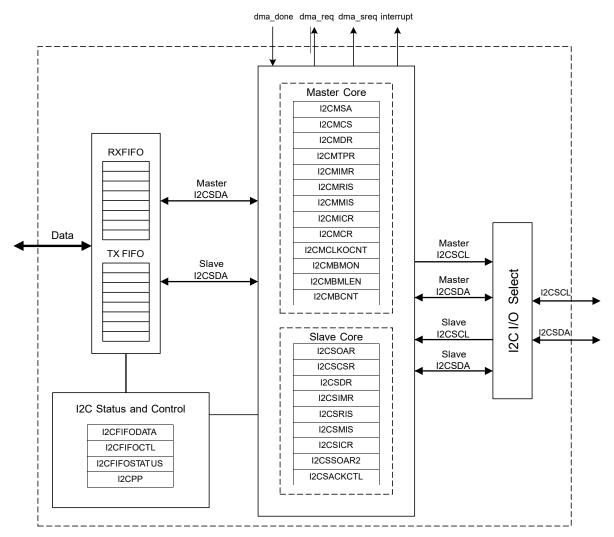

| 7.1.1 Block Diagram                                     |     |

| 7.1.2 Signal Description                                |     |

| 7.2 Functional Description                              |     |

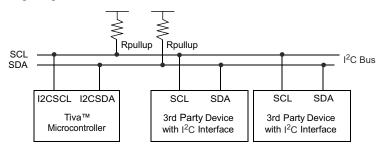

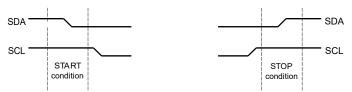

| 7.2.1 I2C Bus Functional Overview                       |     |

| 7.2.2 Supported Speed Modes                             | 206 |

| 7.2.3 Interrupts                                        |     |

| 7.2.4 Loopback Operation                                | 207 |

| 7.2.5 FIFO and µDMA Operation                           | 207 |

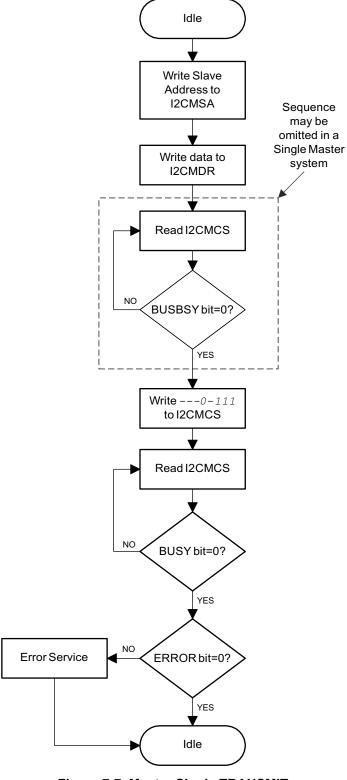

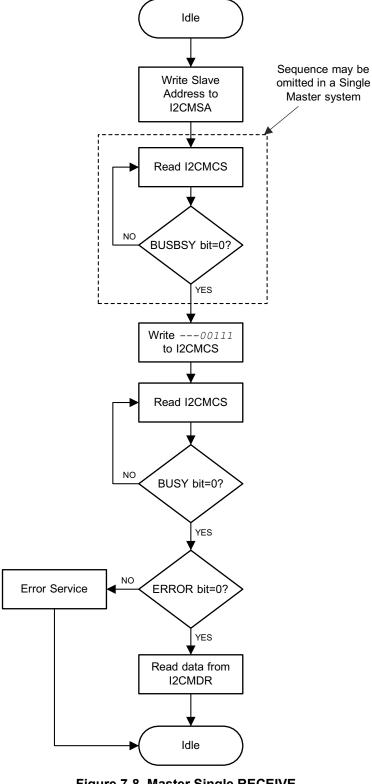

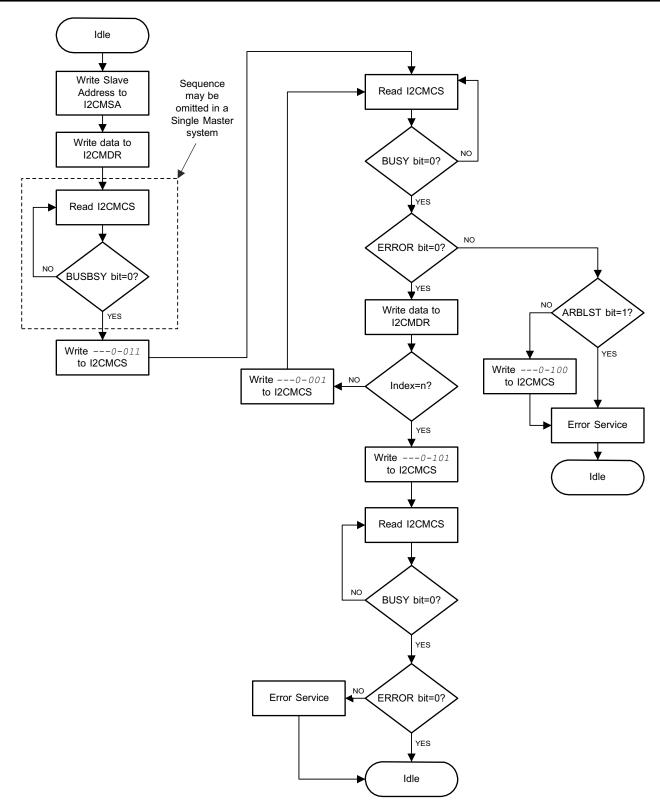

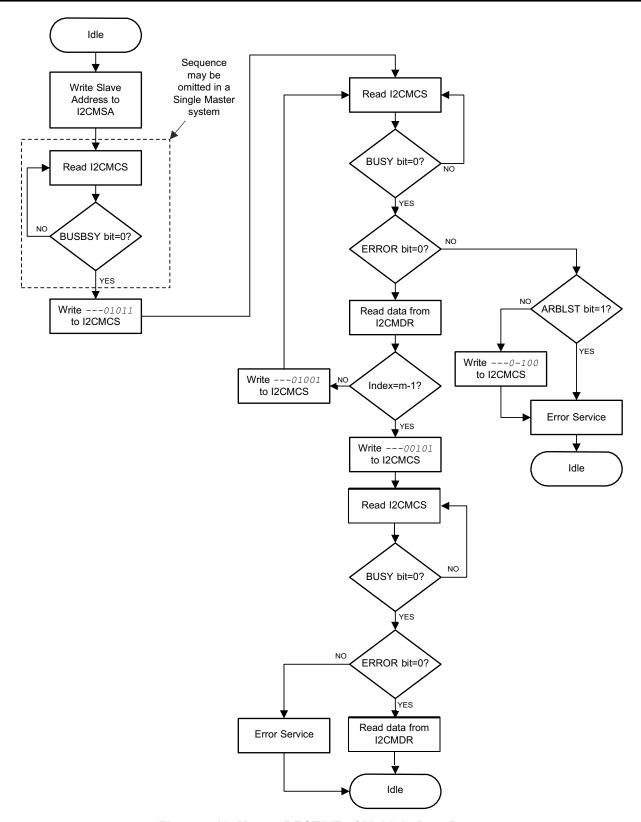

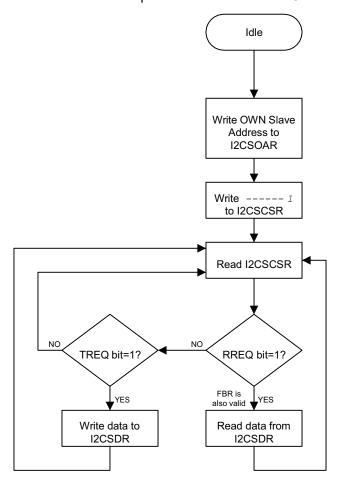

| 7.2.6 Command Sequence Flow Charts                      | 209 |

| 7.2.7 Initialization and Configuration                  | 216 |

| 7.3 I2C Registers                                       | 217 |

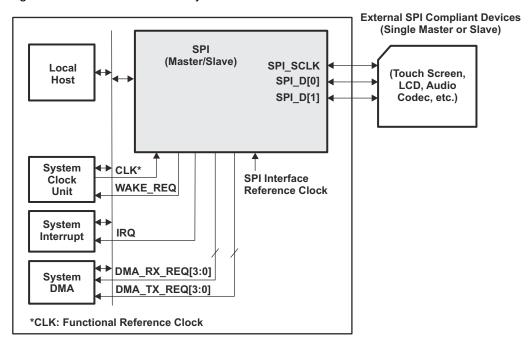

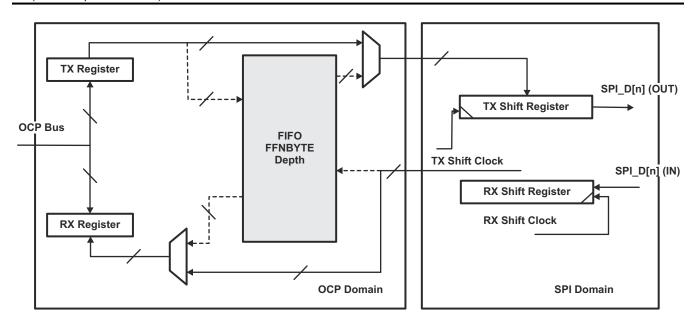

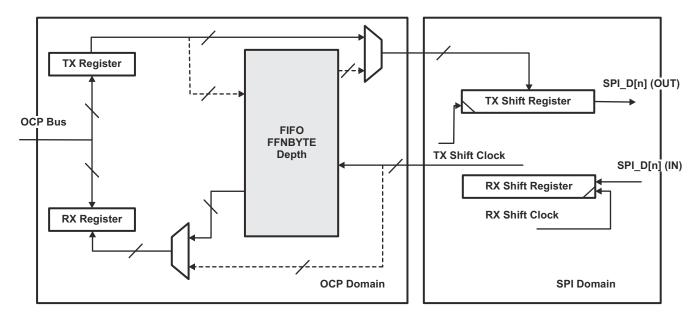

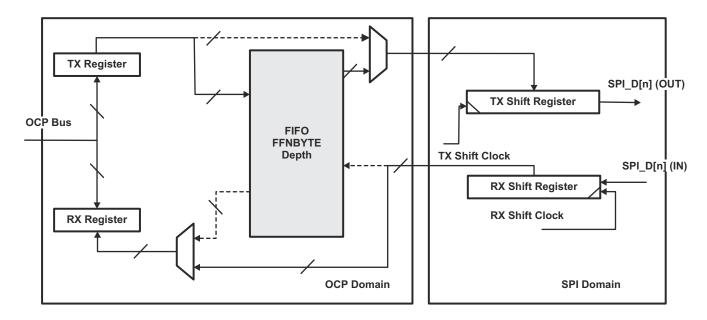

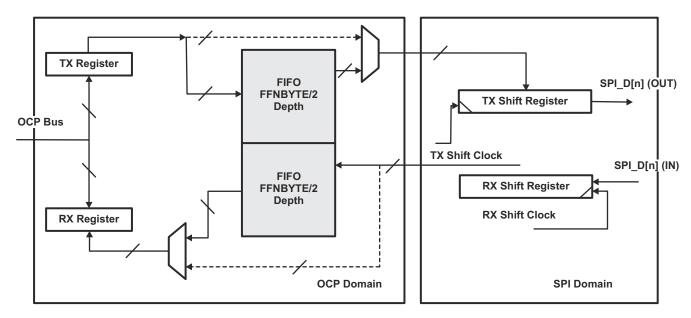

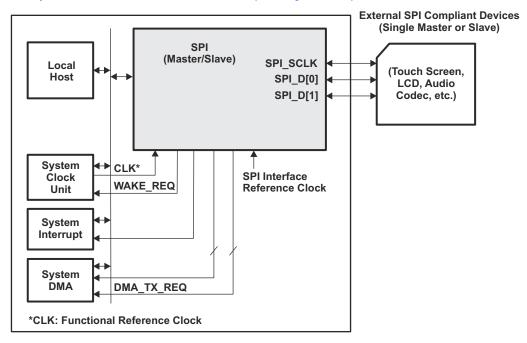

| 8 SPI (Serial Peripheral Interface)                     | 260 |

| 8.1 Overview                                            | 261 |

| 8.1.1 Features                                          |     |

| 8.2 Functional Description                              | 262 |

| 8.2.1 SPI                                               | 262 |

| 8.2.2 SPI Transmission                                  | 262 |

| 8.2.3 Master Mode                                       |     |

| 8.2.4 Slave Mode                                        |     |

| 8.2.5 Interrupts                                        |     |

| 8.2.6 DMA Requests                                      |     |

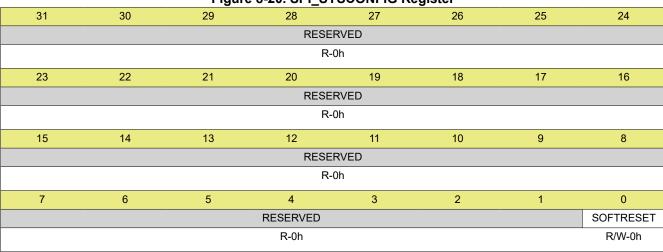

| 8.2.7 Reset                                             | 277 |

| 8.3 Initialization and Configuration                                                   | 277 |

|----------------------------------------------------------------------------------------|-----|

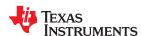

| 8.3.1 Basic Initialization                                                             | 277 |

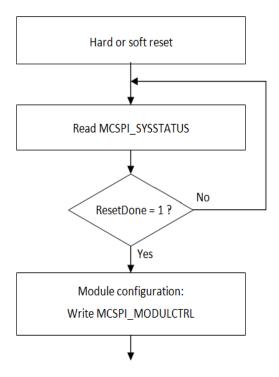

| 8.3.2 Master Mode Operation Without Interrupt (Polling)                                | 277 |

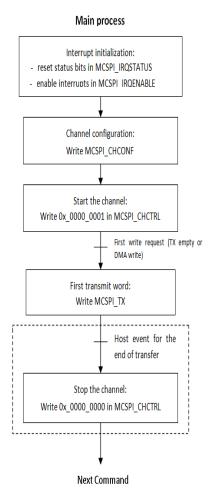

| 8.3.3 Slave Mode Operation With Interrupt                                              | 278 |

| 8.3.4 Generic Interrupt Handler Implementation                                         | 278 |

| 8.4 Access to Data Registers                                                           | 278 |

| 8.5 Module Initialization                                                              | 279 |

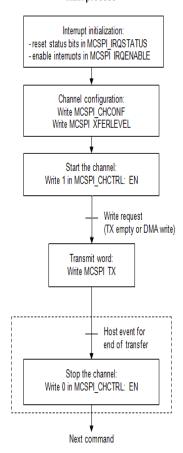

| 8.5.1 Common Transfer Sequence                                                         | 279 |

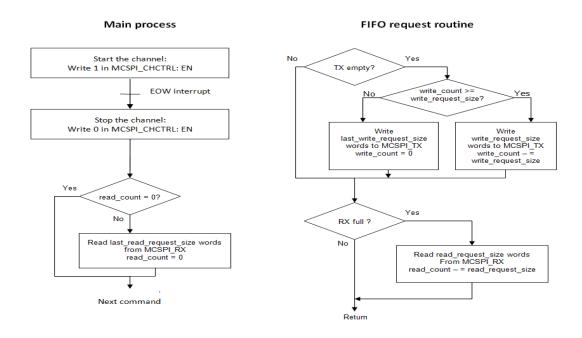

| 8.5.2 End-of-Transfer Sequences                                                        | 280 |

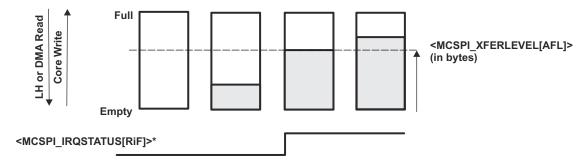

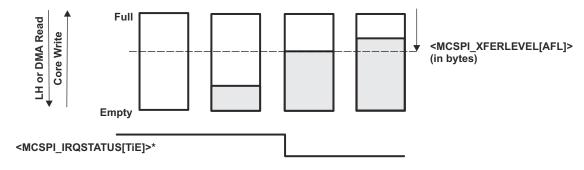

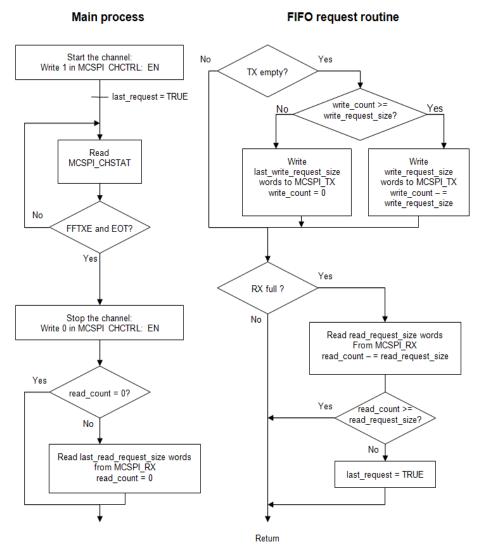

| 8.5.3 FIFO Mode                                                                        | 281 |

| 8.6 SPI Registers                                                                      | 285 |

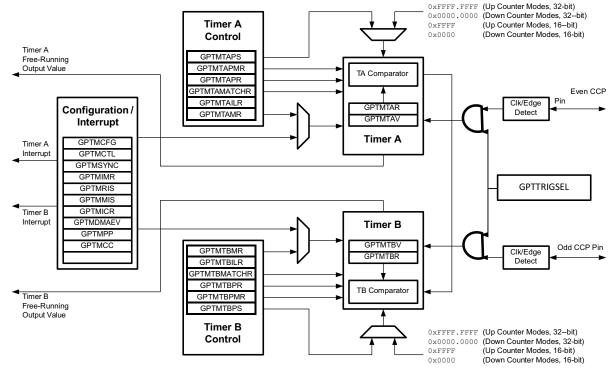

| 9 General-Purpose Timers                                                               | 301 |

| 9.1 Overview                                                                           | 302 |

| 9.2 Block Diagram                                                                      | 302 |

| 9.3 Functional Description                                                             |     |

| 9.3.1 GPTM Reset Conditions                                                            |     |

| 9.3.2 Timer Modes                                                                      | 304 |

| 9.3.3 DMA Operation                                                                    |     |

| 9.3.4 Accessing Concatenated 16/32-Bit GPTM Register Values                            | 310 |

| 9.4 Initialization and Configuration                                                   | 310 |

| 9.4.1 One-Shot and Periodic Timer Mode                                                 | 310 |

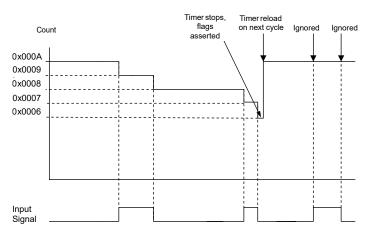

| 9.4.2 Input Edge-Count Mode                                                            | 311 |

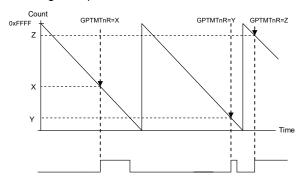

| 9.4.3 Input Edge-Time Mode                                                             | 311 |

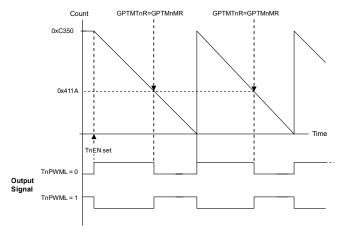

| 9.4.4 PWM Mode                                                                         | 311 |

| 9.5 Timer Registers                                                                    | 313 |

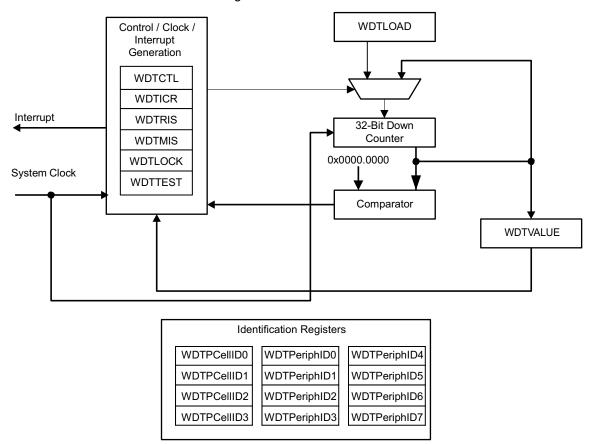

| 10 Watchdog Timer                                                                      | 343 |

| 10.1 Overview                                                                          | 344 |

| 10.1.1 Block Diagram                                                                   | 344 |

| 10.2 Functional Description                                                            | 344 |

| 10.2.1 Initialization and Configuration                                                | 345 |

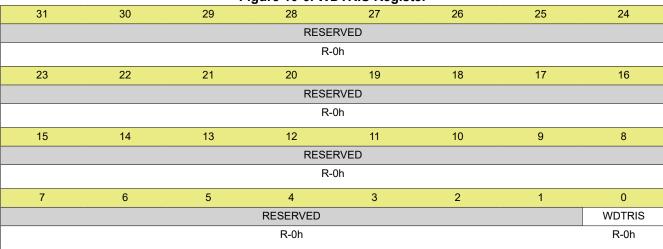

| 10.3 WATCHDOG Registers                                                                |     |

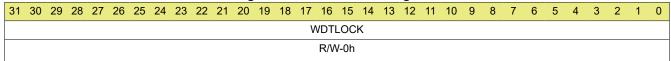

| 10.4 MCU Watchdog Controller Usage Caveats                                             | 354 |

| 10.4.1 System Watchdog                                                                 | 354 |

| 10.4.2 System Watchdog Recovery Sequence                                               | 356 |

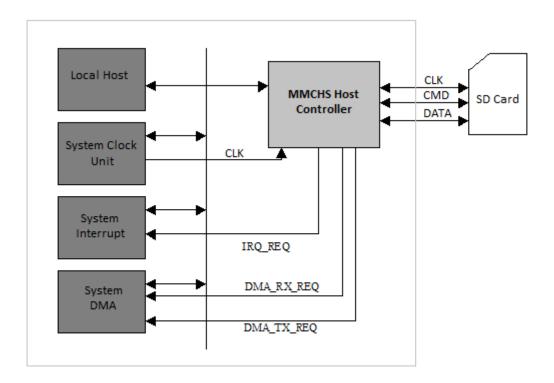

| 11 SD Host Controller Interface                                                        | 357 |

| 11.1 Overview                                                                          | 358 |

| 11.2 SD Host Features                                                                  | 358 |

| 11.3 1-Bit SD Interface                                                                | 358 |

| 11.3.1 Clock and Reset Management                                                      | 360 |

| 11.4 Initialization and Configuration Using Peripheral APIs                            | 360 |

| 11.4.1 Basic Initialization and Configuration                                          |     |

| 11.4.2 Sending Command                                                                 | 361 |

| 11.4.3 Card Detection and Initialization                                               | 362 |

| 11.4.4 Block Read                                                                      | 363 |

| 11.4.5 Block Write                                                                     | 364 |

| 11.5 Performance and Testing                                                           | 365 |

| 11.6 Peripheral Library APIs                                                           | 365 |

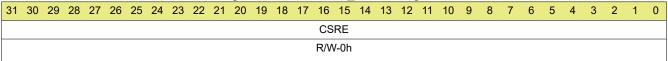

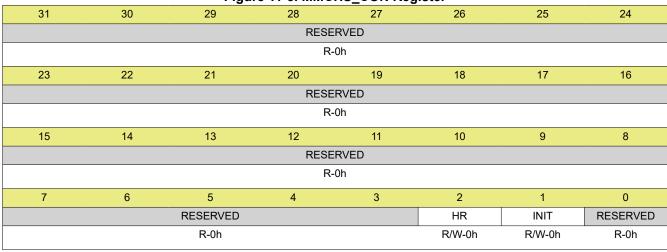

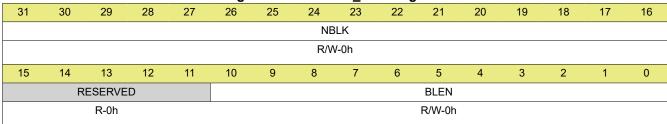

| 11.7 SD-HOST Registers                                                                 | 370 |

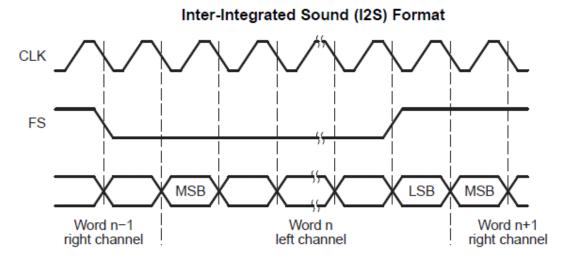

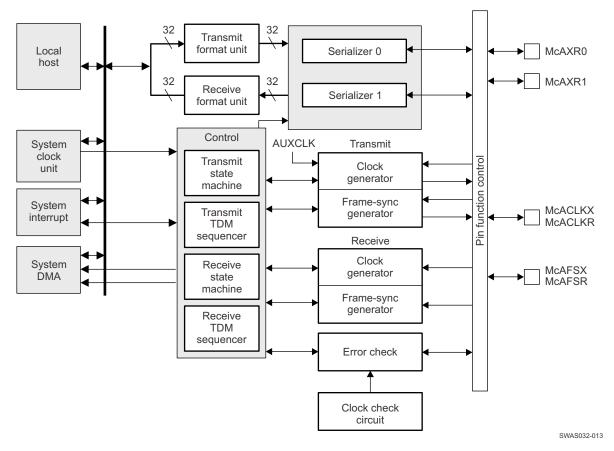

| 12 Inter-Integrated Sound (I2S) Multichannel Audio Serial Port                         | 399 |

| 12.1 Overview                                                                          | 400 |

| 12.1.1 I2S Format                                                                      | 400 |

| 12.2 Functional Description                                                            | 401 |

| 12.3 Programming Model                                                                 | 401 |

| 12.3.1 Clock and Reset Management                                                      | 401 |

| 12.3.2 I2S Data Port Interface                                                         | 402 |

| 12.3.3 Initialization and Configuration                                                | 402 |

| 12.4 Peripheral Library APIs for I2S Configuration                                     | 404 |

| 12.4.1 Basic APIs for Enabling and Configuring the Interface                           |     |

| 12.4.2 APIs for Data Access if DMA is Not Used                                         |     |

| 12.4.3 APIs for Setting Up, Handling Interrupts, or Getting Status from I2S Peripheral |     |

| 12.4.4 APIs to Control FIFO Structures Associated With I2S Peripheral                  |     |

| 12.5 I2S Registers                                                       |            |

|--------------------------------------------------------------------------|------------|

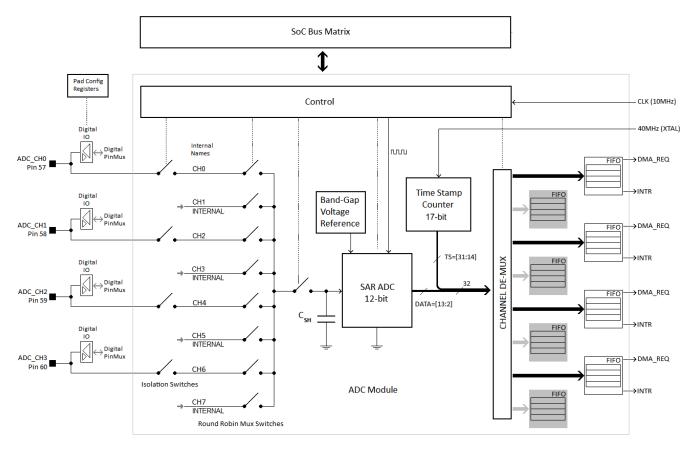

| 13 Analog-to-Digital Converter (ADC)                                     |            |

| 13.1 Overview                                                            |            |

| 13.2 Key Features                                                        |            |

| 13.3 ADC Register Mapping                                                |            |

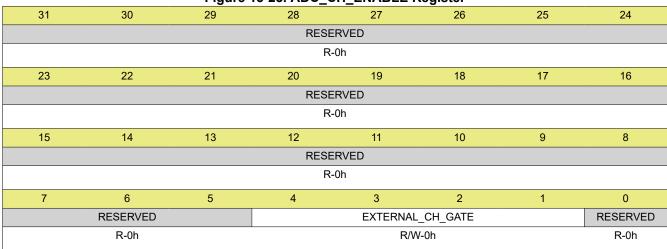

| 13.4 ADC_MODULE Registers                                                |            |

| 13.5 Initialization and Configuration                                    |            |

| 13.6 Peripheral Library APIs for ADC Operation                           |            |

| 13.6.1 Overview                                                          |            |

| 13.6.2 Configuring the ADC Channels                                      | 481        |

| 13.6.3 Basic APIs for Enabling and Configuring the Interface             |            |

| 13.6.4 APIs for Data Transfer [Direct Access to FIFO and DMA Setup]      |            |

| 13.6.5 APIs for Interrupt Usage                                          | 484        |

| 13.6.6 APIs for Setting Up ADC Timer for Time-Stamping the Samples       |            |

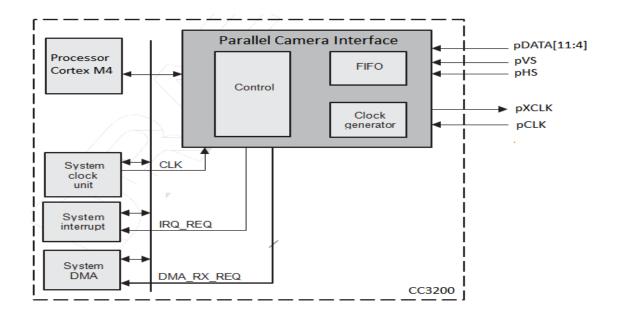

| 14 Parallel Camera Interface Module                                      | 489        |

| 14.1 Overview                                                            |            |

| 14.2 Image Sensor Interface                                              |            |

| 14.3 Functional Description                                              |            |

| 14.3.1 Modes of Operation                                                |            |

| 14.3.2 FIFO Buffer                                                       |            |

| 14.3.3 Reset                                                             | 493        |

| 14.3.4 Clock Generation                                                  |            |

| 14.3.5 Interrupt Generation                                              |            |

| 14.3.6 DMA Interface                                                     |            |

| 14.4 Programming Model                                                   | 496        |

| 14.4.1 Camera Core Reset                                                 | 496        |

| 14.4.2 Enable the Picture Acquisition                                    |            |

| 14.4.3 Disable the Picture Acquisition                                   | 497        |

| 14.5 Interrupt Handling                                                  | 497        |

| 14.5.1 FIFO_OF_IRQ (FIFO Overflow)                                       |            |

| 14.5.2 FIFO_UF_IRQ (FIFO Underflow)                                      |            |

| 14.6 Camera Registers                                                    |            |

| 14.7 Peripheral Library APIs                                             |            |

| 14.8 Developer's Guide                                                   | 513        |

| 14.8.1 Using Peripheral Driver APIs for Capturing an Image               | 513        |

| 14.8.2 Using Peripheral Driver APIs for Communicating With Image Sensors | 517        |

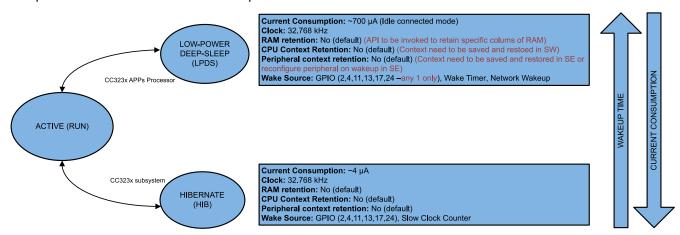

| 15 Power, Reset, and Clock Management                                    |            |

| 15.1 Overview                                                            |            |

| 15.1.1 Power Management Unit (PMU)                                       |            |

| 15.1.2 VBAT Wide-Voltage Connection                                      |            |

| 15.1.3 Supply Brownout and Blackout                                      |            |

| 15.1.4 Application Processor Power Modes                                 |            |

| 15.2 Power Management Control Architecture                               |            |

| 15.2.1 Global Power-Reset-Clock Manager (GPRCM)                          |            |

| 15.2.2 Application Reset-Clock Manager (ARCM)                            |            |

| 15.3 PRCM APIs                                                           |            |

| 15.3.1 MCU Initialization                                                | 525        |

| 15.3.2 Reset Control                                                     |            |

| 15.3.3 Peripheral Reset                                                  | 525        |

| 15.3.4 Reset Cause                                                       |            |

| 15.3.5 Clock Control                                                     |            |

| 15.3.6 Low-Power Modes                                                   |            |

| 15.3.7 Sleep (SLEEP)                                                     |            |

| 15.3.8 Low-Power Deep Sleep (LPDS)                                       |            |

| 15.3.9 Hibernate (HIB)                                                   |            |

| 15.3.10 Slow Clock Counter                                               |            |

| 15.4 Peripheral Macros.                                                  |            |

| 15.5 Power Management Framework                                          |            |

| 15.6 PRCM Registers                                                      |            |

| 16 I/O Pads and Pin Multiplexing                                         |            |

| 16.1 Overview                                                            | <u>586</u> |

| 16.2 I/O Pad Electrical Specifications                                                   |            |

|------------------------------------------------------------------------------------------|------------|

| 16.3 Analog and Digital Pin Multiplexing                                                 |            |

| 16.4 Special Analog/Digital Pins                                                         |            |

| 16.4.1 Pins 45 and 52                                                                    |            |

| 16.4.3 Pins 57, 58, 59, and 60                                                           |            |

| 16.5 Analog Mux Control Registers.                                                       |            |

| 16.6 Pins Available for Applications                                                     |            |

| 16.7 Functional Pin Mux Configurations                                                   |            |

| 16.8 Pin Mapping Recommendations                                                         |            |

| 16.8.1 Pad Configuration Registers for Application Pins                                  |            |

| 16.8.2 PAD Behavior During Reset and Hibernate                                           |            |

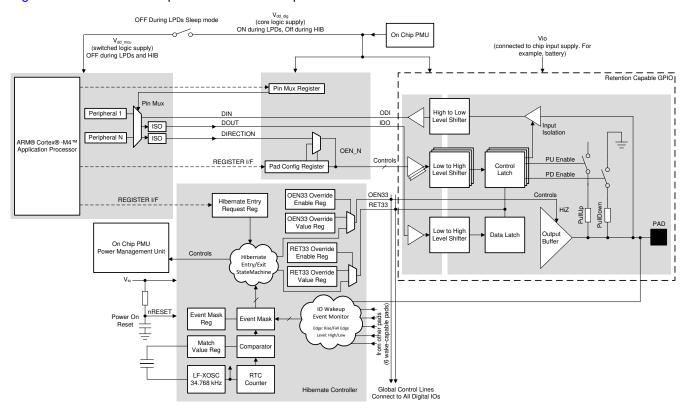

| 16.8.3 Control Architecture                                                              |            |

| 16.8.4 CC32xx Pin-mux Examples.                                                          |            |

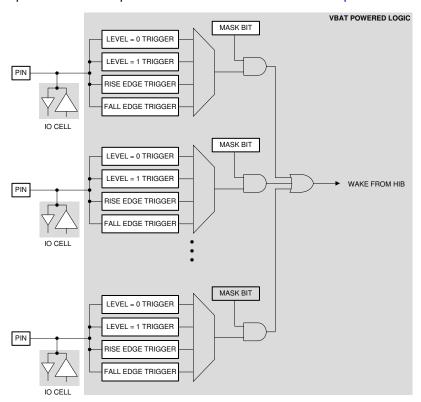

| 16.8.5 Wake on Pad                                                                       |            |

| 16.8.6 Sense on Power                                                                    |            |

| 17 Advance Encryption Standard Accelerator (AES)                                         |            |

| 17.1 AES Overview                                                                        |            |

| 17.2 AES Functional Description                                                          |            |

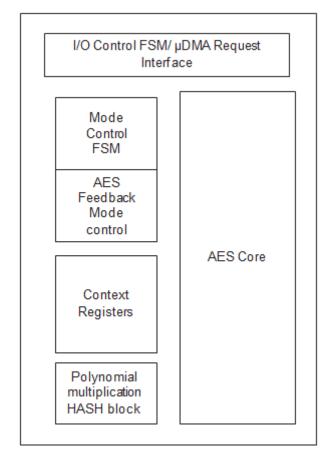

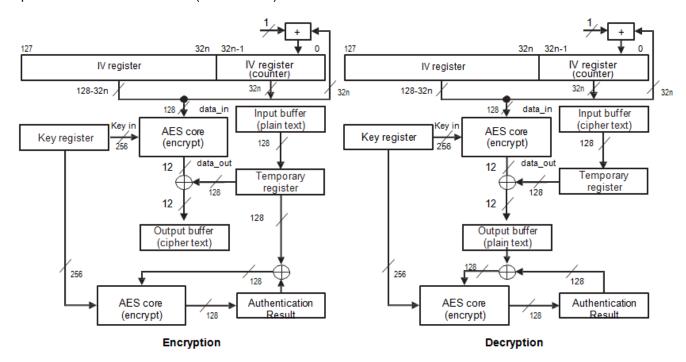

| 17.2.1 AES Block Diagram                                                                 |            |

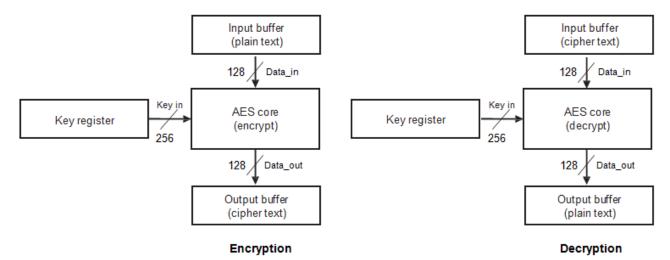

| 17.2.2 AES Algorithm                                                                     |            |

| 17.2.3 AES Operating Modes                                                               | 620        |

| 17.2.4 Hardware Requests                                                                 | 630        |

| 17.3 AES Module Programming Guide                                                        | 631        |

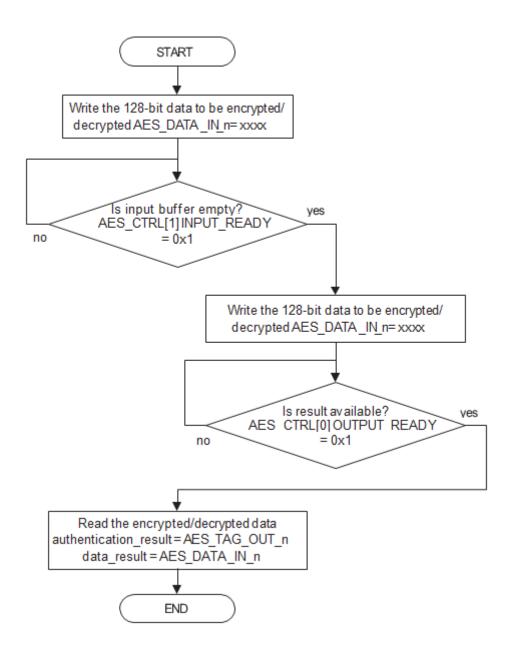

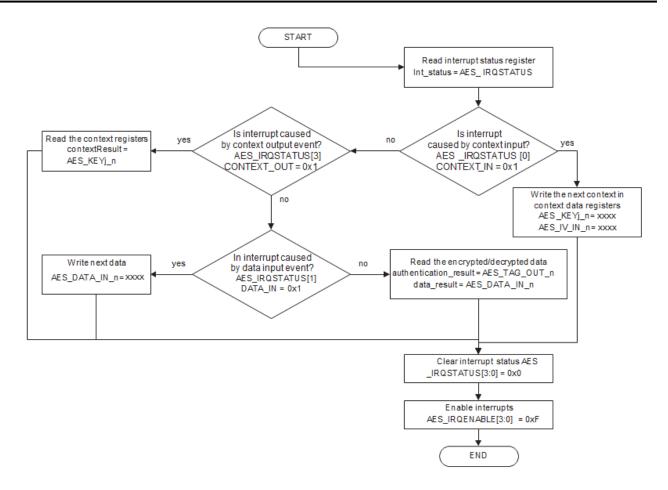

| 17.3.1 AES Low-Level Programming Models                                                  | 631        |

| 17.4 AES Registers                                                                       |            |

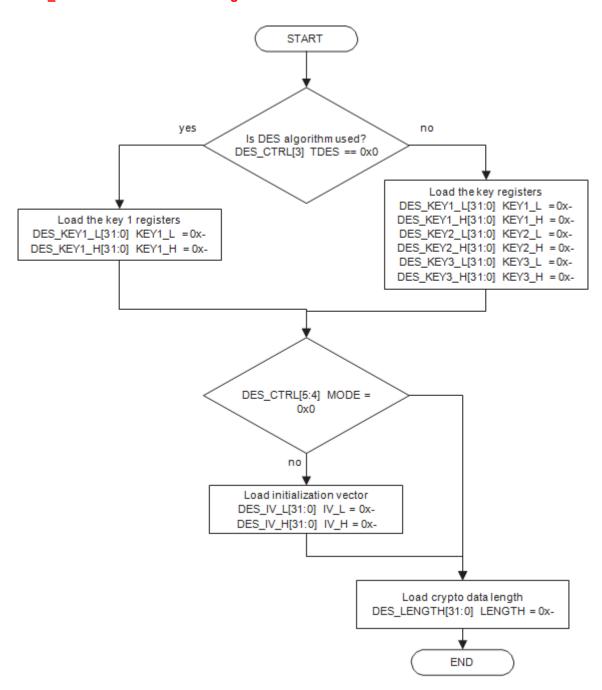

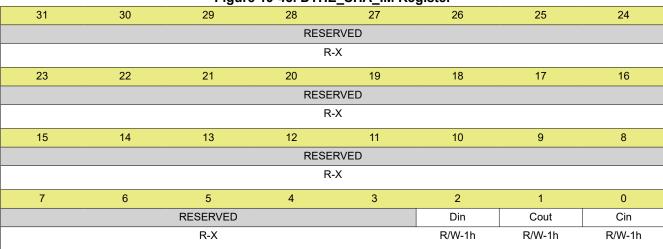

| 18 Data Encryption Standard Accelerator (DES)                                            |            |

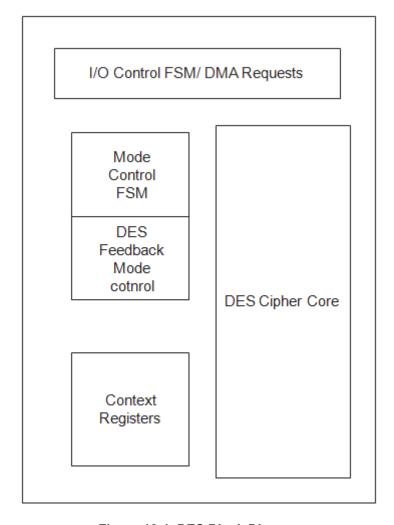

| 18.1 DES Functional Description                                                          |            |

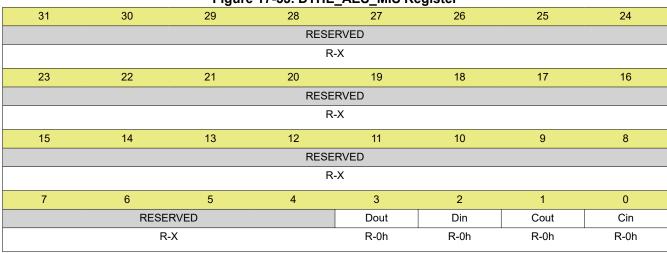

| 18.2 DES Block Diagram                                                                   |            |

| 18.2.1 µDMA Control                                                                      |            |

| 18.2.2 Interrupt Control                                                                 |            |

| 18.2.3 Register Interface                                                                |            |

| 18.2.4 DES Enginer                                                                       |            |

| 18.3 DES-Supported Modes of Operation                                                    |            |

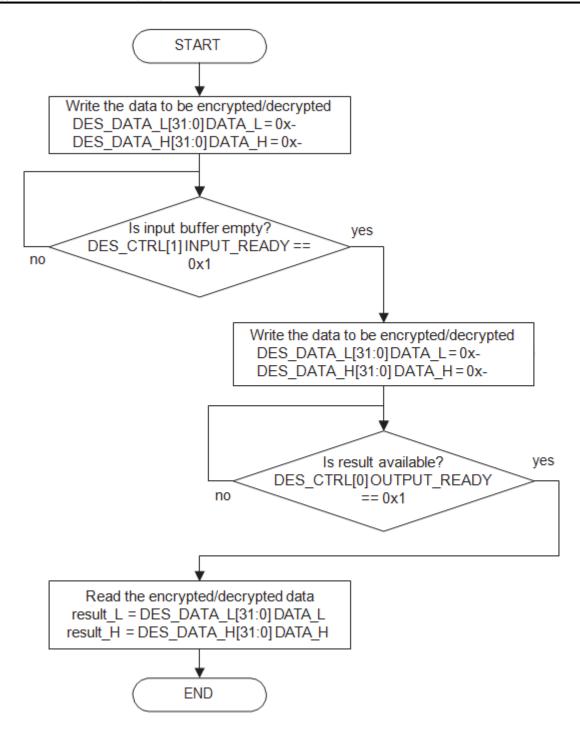

| 18.3.1 ECB Feedback Mode18.4 DES Module Programming Guide – Low-Level Programming Models |            |

| 18.4.1 Surrounding Modules Global Initialization                                         |            |

| 18.4.2 Operational Modes Configuration                                                   |            |

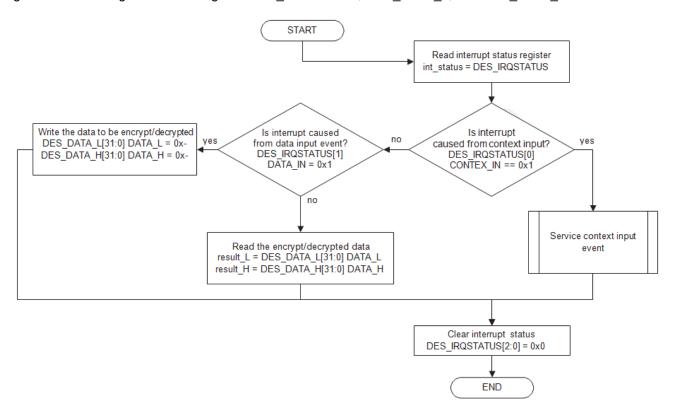

| 18.4.3 DES Events Servicing                                                              |            |

| 18.5 DES Registers                                                                       |            |

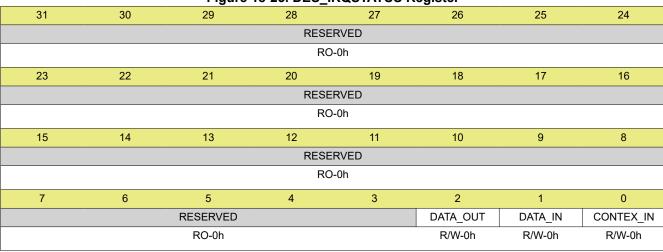

| 19 SHA/MD5 Accelerator                                                                   |            |

| 19.1 SHA/MD5 Functional Description                                                      |            |

| 19.1.1 SHA/MD5 Block Diagram                                                             |            |

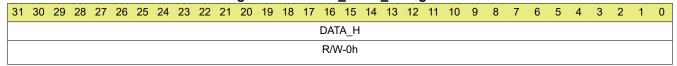

| 19.1.2 μDMA and Interrupt Requests                                                       |            |

| 19.1.3 Operation Description                                                             |            |

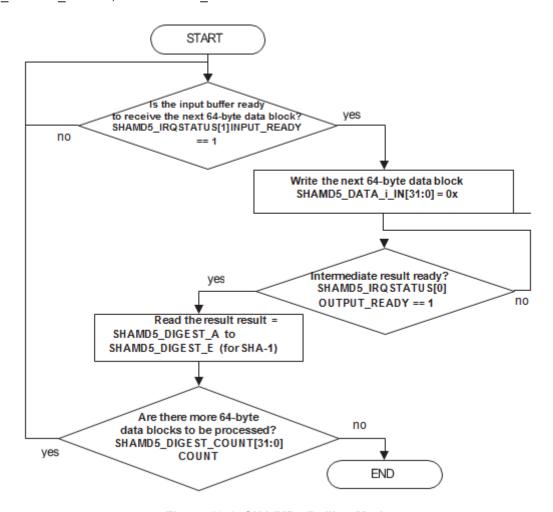

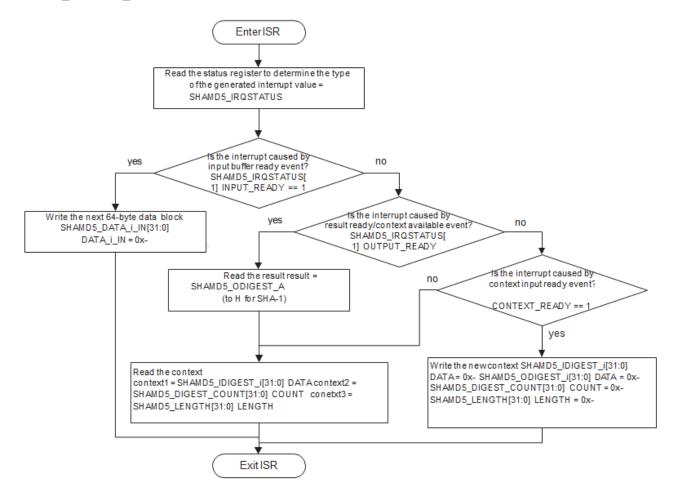

| 19.1.4 SHA/MD5 Programming Guide                                                         |            |

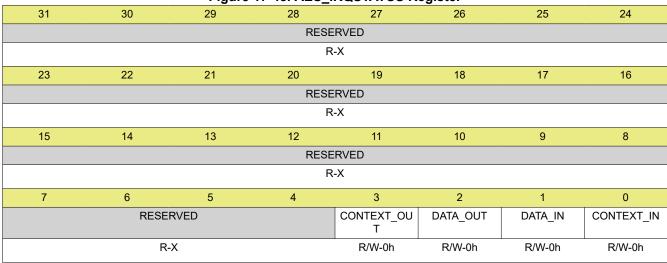

| 19.2 SHA-MD5 Registers                                                                   | 709        |

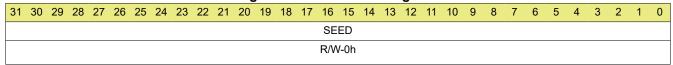

| 20 Cyclical Redundancy Check (CRC)                                                       | 758        |

| 20.1 Functional Description                                                              | 759        |

| 20.1.1 CRC Support                                                                       |            |

| 20.2 Initialization and Configuration                                                    |            |

| 20.2.1 CRC Initialization and Configuration                                              |            |

| 20.3 CRC Registers                                                                       |            |

| 21 On-Chip Parallel Flash                                                                |            |

| 21.1 Flash Memory Configuration                                                          |            |

| 21.2 Interrupts                                                                          |            |

| 21.3 Flash Memory Programming                                                            |            |

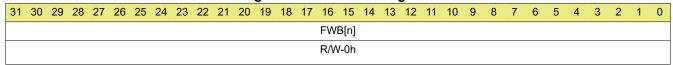

| 21.4 32-Word Flash Memory Write Buffer                                                   |            |

| 21.5 Flash Registers                                                                     |            |

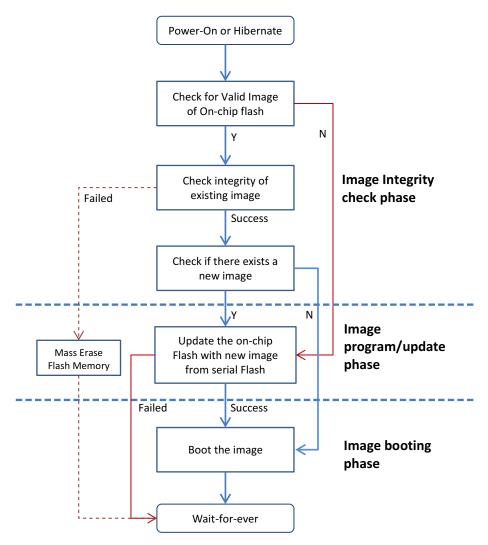

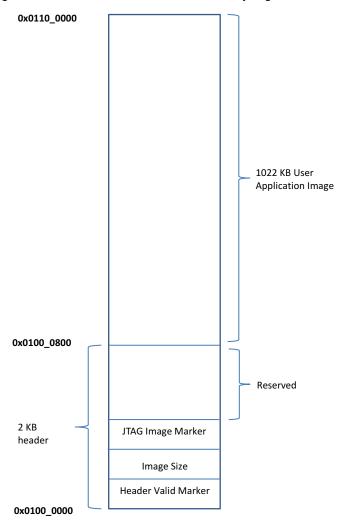

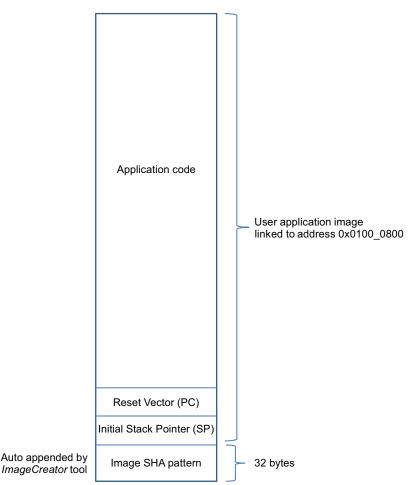

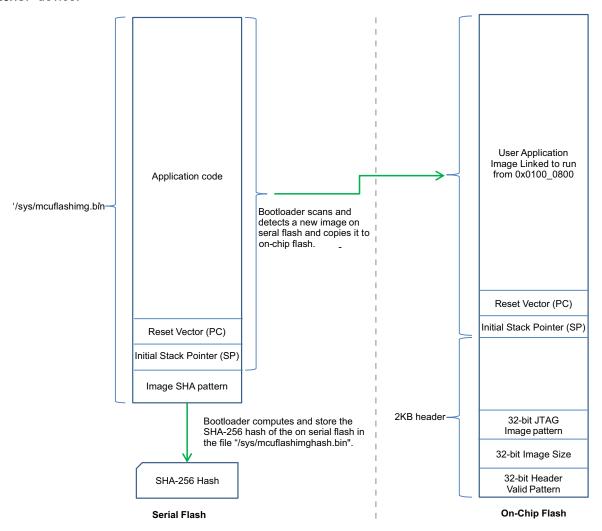

| 21.7 Flash User Application and Memory Partition                                         | 764<br>785 |

| 21.8 Programming, Bootstrapping, and Updating the Flash User Application | 787 |

|--------------------------------------------------------------------------|-----|

| 21.9 Image Authentication and Integrity Check                            |     |

| 21.10 Debugging Flash User Application Using JTAG                        |     |

| 22 Revision History                                                      |     |

| A Software Development Kit Examples.                                     |     |

| B CC323x Device Miscellaneous Registers                                  |     |

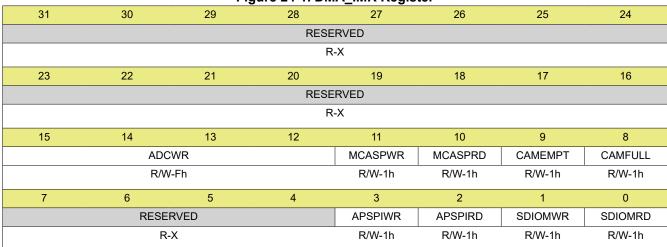

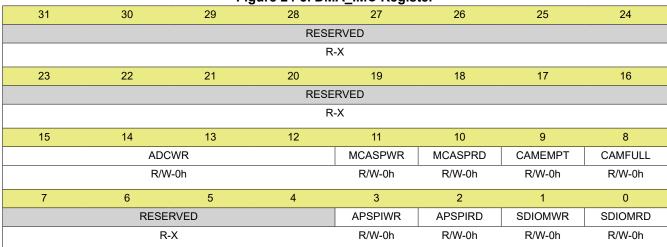

| 24.1 DMA IMR Register (offset = 8Ch) [reset = FF0Fh]                     |     |

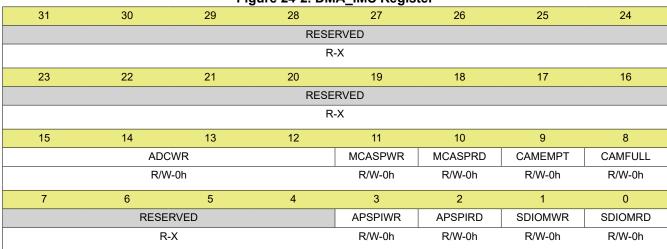

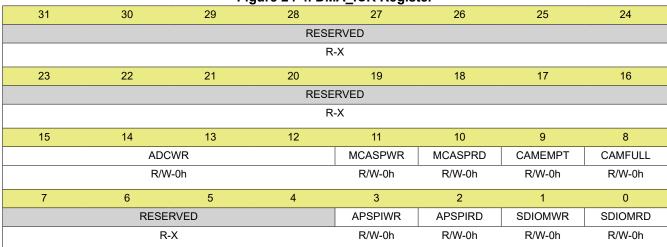

| 24.2 DMA_IMS Register (offset = 90h) [reset = 0h]                        |     |

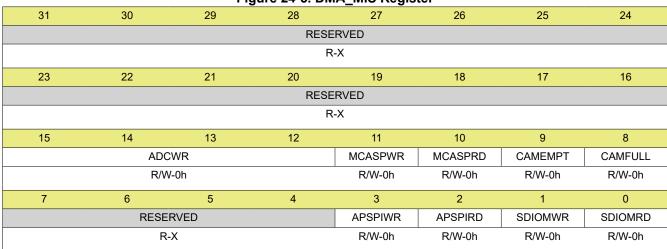

| 24.3 DMA_IMC Register (offset = 94h) [reset = 0h]                        |     |

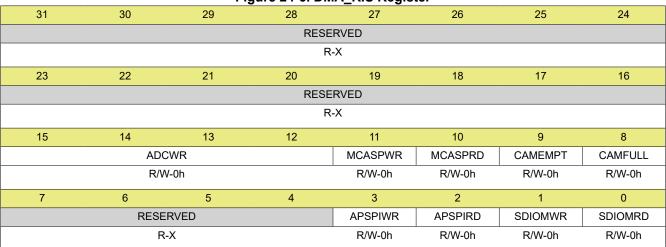

| 24.4 DMA_ICR Register (offset = 9Ch) [reset = 0h]                        |     |

| 24.5 DMA_MIS Register (offset = A0h) [reset = 0h]                        |     |

| 24.6 DMA RIS Register (offset = A4h) [reset = 0h]                        |     |

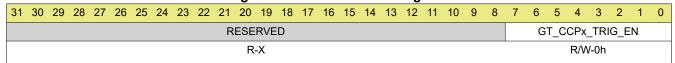

| 24.7 GPTTRIGSEL Register (offset = B0h) [reset = 0h]                     |     |

|                                                                          |     |

| List of Figures                                                          |     |

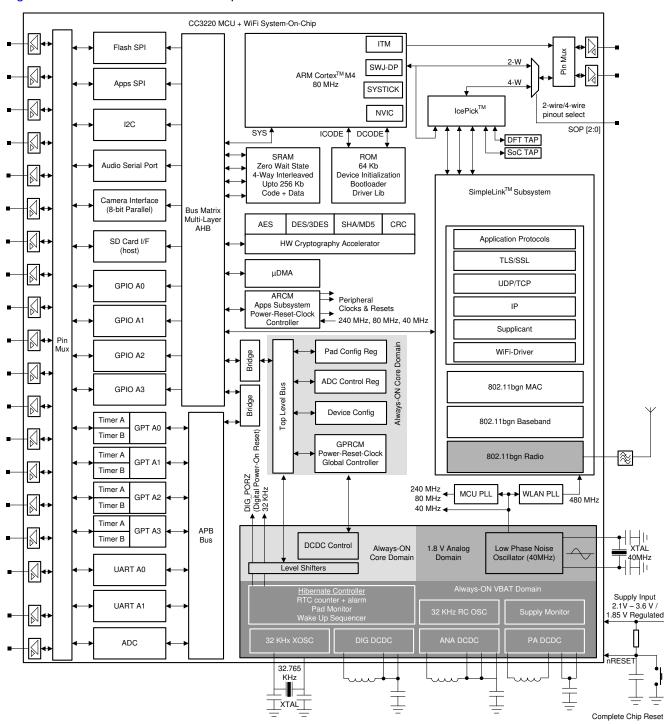

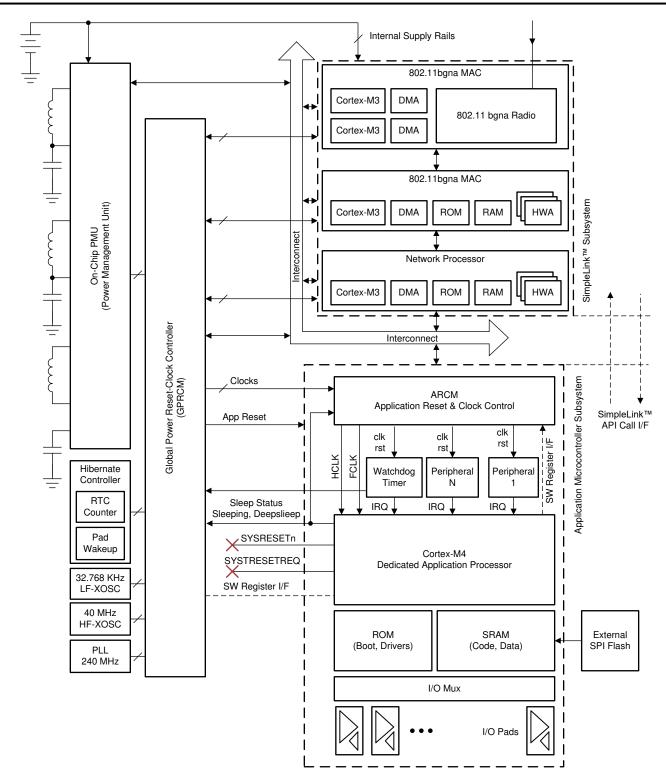

| Figure 1-1. CC32xx MCU and Wi-Fi® System-on-Chip                         | 30  |

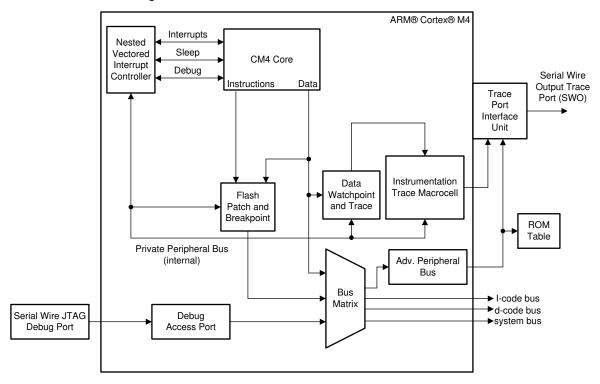

| Figure 2-1. Application CPU Block Diagram                                | 42  |

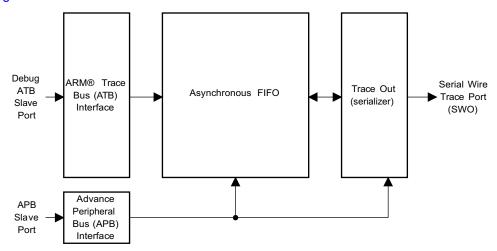

| Figure 2-2. TPIU Block Diagram                                           | 43  |

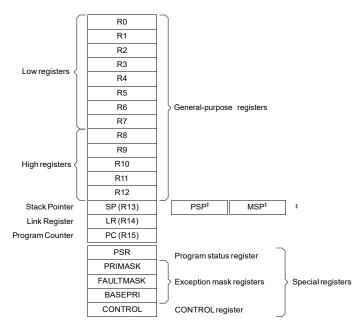

| Figure 2-3. Cortex®-M4 Register Set                                      | 45  |

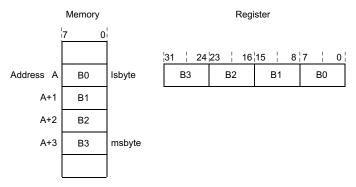

| Figure 2-4. Data Storage                                                 | 51  |

| Figure 2-5. Vector Table                                                 |     |

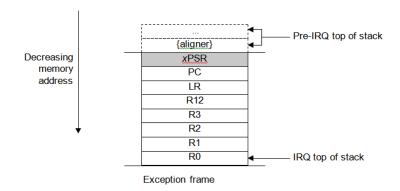

| Figure 2-6. Exception Stack Frame                                        |     |

| Figure 2-7. Power-Management Architecture in CC32xx SoC                  |     |

| Figure 3-1. ACTLR Register                                               |     |

| Figure 3-2. STCTRL Register                                              |     |

| Figure 3-3. STRELOAD Register                                            |     |

| Figure 3-4. STCURRENT Register                                           |     |

| Figure 3-5. EN_0 to EN_6 Register                                        |     |

| Figure 3-6. DIS_0 to DIS_6 Register                                      |     |

| Figure 3-7. PEND_0 to PEND_6 Register                                    |     |

| Figure 3-8. UNPEND_0 to UNPEND_6 Register                                |     |

| Figure 3-9. ACTIVE_0 to ACTIVE_6 Register                                |     |

| Figure 3-10. PRI_0 to PRI_49 Register                                    |     |

| Figure 3-11. CPUID Register                                              |     |

| Figure 3-12. INTCTRL Register                                            |     |

| Figure 3-13. VTABLE Register                                             |     |

| Figure 3-14. APINT Register                                              |     |

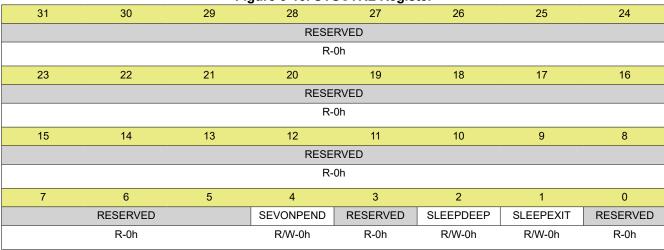

| Figure 3-15. SYSCTRL Register                                            |     |

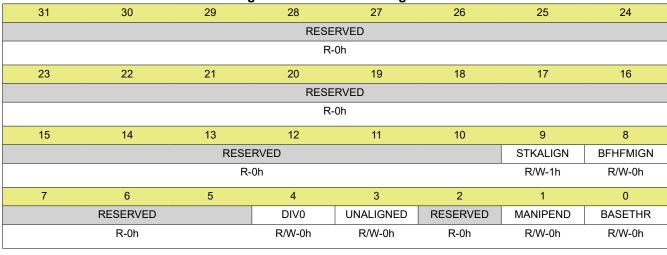

| Figure 3-16. CFGCTRL Register                                            |     |

| Figure 3-17. SYSPRI1 Register                                            |     |

| Figure 3-18. SYSPRI2 RegisterFigure 3-19. SYSPRI3 Register               |     |

| Figure 3-20. SYSHNDCTRL Register                                         |     |

| Figure 3-21. FAULTSTAT Register                                          |     |

| Figure 3-22. HFAULTSTAT Register                                         |     |

| Figure 3-23. FAULTDDR Register                                           |     |

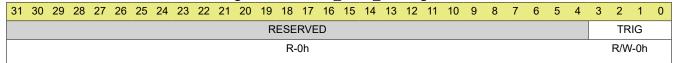

| Figure 3-24. SWTRIG Register                                             |     |

| Figure 4-1. Ping-Pong Mode                                               |     |

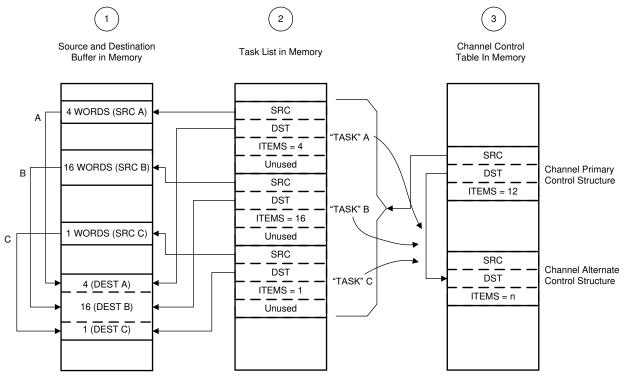

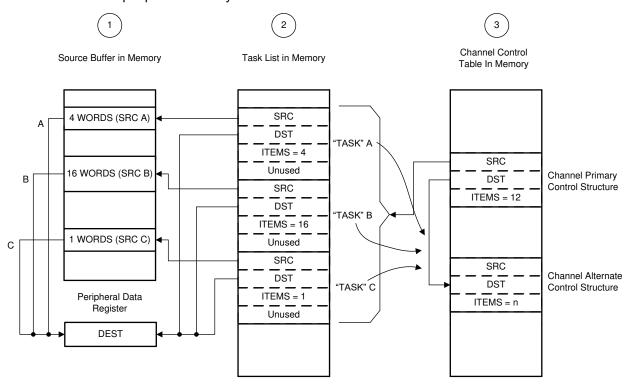

| Figure 4-2. Memory Scatter-Gather Mode                                   |     |

| Figure 4-3. Peripheral Scatter-Gather Mode                               |     |

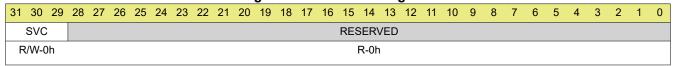

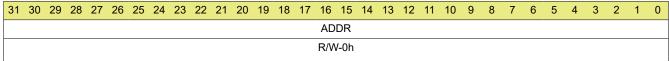

| Figure 4-4. DMA SRCENDP Register                                         |     |

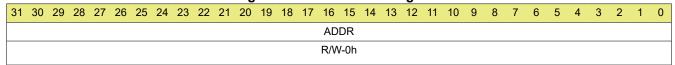

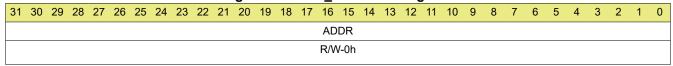

| Figure 4-5. DMA_DSTENDP Register                                         |     |

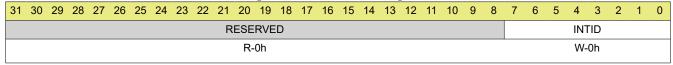

| Figure 4-6. DMA CHCTL Register                                           |     |

| Figure 4-7. DMA STAT Register                                            |     |

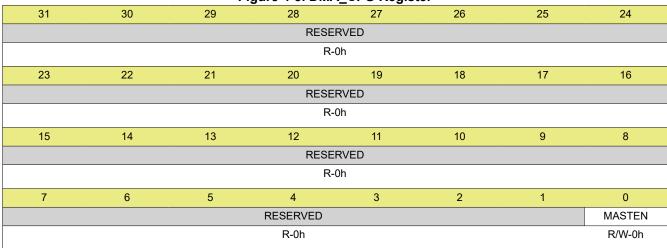

| Figure 4-8. DMA_CFG Register                                             |     |

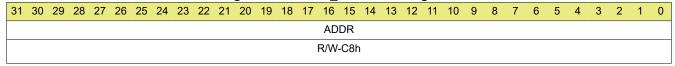

| Figure 4-9. DMA CTLBASE Register                                         |     |

| Figure 4-10. DMA_ALTBASE Register                                        |     |

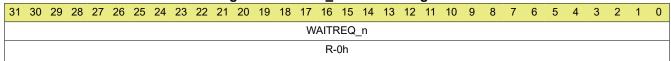

| Figure 4-11. DMA WAITSTAT Register                                       |     |

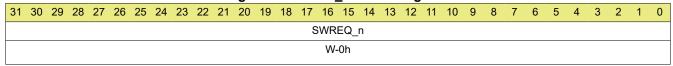

| Figure 4-12. DMA SWREQ Register                                          |     |

| Figure 4-13. DMA_USEBURSTSET Register                                    |     |

|                                                                          |     |

| Figure 4-14. DMA_USEBURSTCLR Register                                 |     |

|-----------------------------------------------------------------------|-----|

| Figure 4-15. DMA_REQMASKSET Register                                  |     |

| Figure 4-16. DMA_REQMASKCLR Register                                  |     |

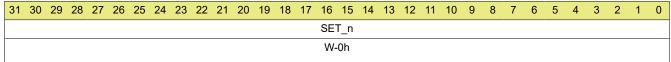

| Figure 4-17. DMA_ENASET Register                                      |     |

| Figure 4-18. DMA_ENACLR Register                                      |     |

| Figure 4-19. DMA_ALTSET Register                                      |     |

| Figure 4-20. DMA_ALTCLR Register                                      |     |

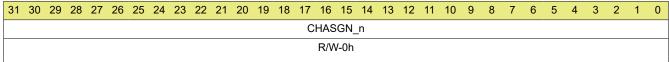

| Figure 4-21. DMA_PRIOSET Register                                     |     |

| Figure 4-22. DMA_PRIOCLR Register                                     |     |

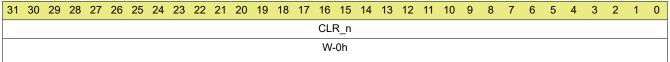

| Figure 4-23. DMA_ERRCLR Register                                      |     |

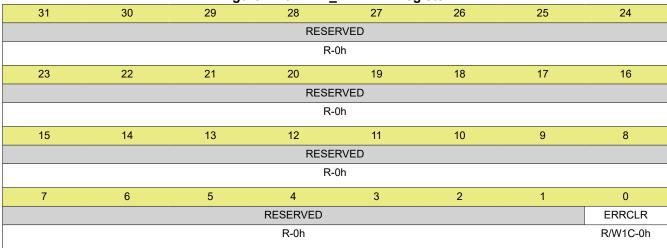

| Figure 4-24. DMA_CHASGN Register                                      |     |

| Figure 4-25. DMA_CHMAP0 Register                                      |     |

| Figure 4-26. DMA_CHMAP1 Register                                      | 147 |

| Figure 4-27. DMA_CHMAP2 Register                                      |     |

| Figure 4-28. DMA_CHMAP3 Register                                      |     |

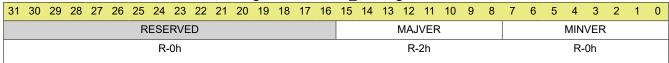

| Figure 4-29. DMA_PV Register                                          |     |

| Figure 5-1. Digital I/O Pads                                          |     |

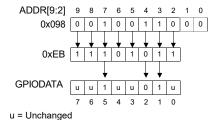

| Figure 5-2. GPIODATA Write Example                                    |     |

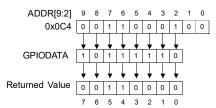

| Figure 5-3. GPIODATA Read Example                                     |     |

| Figure 5-4. GPIODATA Register                                         |     |

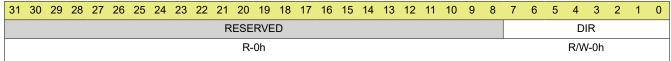

| Figure 5-5. GPIODIR Register                                          |     |

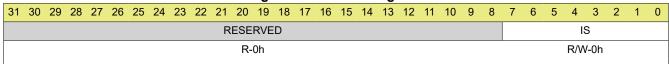

| Figure 5-6. GPIOIS Register                                           |     |

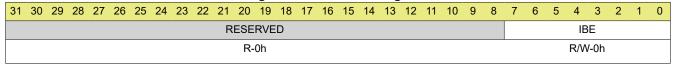

| Figure 5-7. GPIOIBE Register                                          |     |

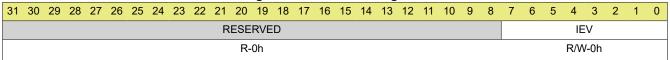

| Figure 5-8. GPIOIEV Register                                          |     |

| Figure 5-9. GPIOIM Register                                           |     |

| Figure 5-10. GPIORIS Register                                         |     |

| Figure 5-11. GPIOMIS Register                                         |     |

| Figure 5-12. GPIOICR Register                                         |     |

| Figure 5-13. GPIO_TRIG_EN Register                                    |     |

| Figure 6-1. UART Module Block Diagram                                 |     |

| Figure 6-2. UART Character Frame                                      |     |

| Figure 6-3. UARTDR Register                                           |     |

| Figure 6-4. UARTRSR_UARTECR Register                                  | 1/9 |

|                                                                       |     |

| Figure 6-6. UARTIBRD Register                                         |     |

| Figure 6-8. UARTFBRD Register                                         |     |

| Figure 6-9. UARTCTL Register                                          |     |

| Figure 6-10. UARTIFLS Register                                        |     |

| Figure 6-11. UARTIM Register                                          |     |

| Figure 6-12. UARTRIS Register                                         |     |

| Figure 6-13. UARTMIS Register                                         |     |

| Figure 6-14. UARTICR Register                                         |     |

| Figure 6-15. UARTDMACTL Register                                      |     |

| Figure 7-1. I2C Block Diagram                                         |     |

| Figure 7-2. I2C Bus Configuration                                     |     |

| Figure 7-3. START and STOP Conditions                                 |     |

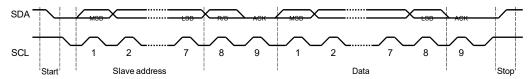

| Figure 7-4. Complete Data Transfer With a 7-Bit Address.              |     |

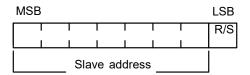

| Figure 7-5. R/S Bit in First Byte                                     |     |

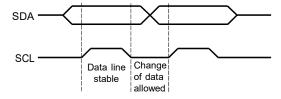

| Figure 7-6. Data Validity During Bit Transfer on the I2C Bus          |     |

| Figure 7-7. Master Single TRANSMIT                                    |     |

| Figure 7-8. Master Single RECEIVE                                     |     |

| Figure 7-9. Master TRANSMIT of Multiple Data Bytes                    |     |

| Figure 7-10. Master RECEIVE of Multiple Data Bytes                    |     |

| Figure 7-11. Master RECEIVE with Repeated START after Master TRANSMIT |     |

| Figure 7-12. Master TRANSMIT with Repeated START after Master RECEIVE |     |

| Figure 7-13. Slave Command Sequence                                   |     |

| Figure 7-14. I2CMSA Register                                          |     |

| Figure 7-15. I2CMCS Register                                          |     |

| Figure 7-16. I2CMDR Register                                          |     |

| Figure 7-17. I2CMTPR Register                                         |     |

| F: 7 40       | IOOMIND Designer                                                           | 000 |

|---------------|----------------------------------------------------------------------------|-----|

| •             | I2CMIMR Register                                                           |     |

| •             | I2CMRIS Register                                                           |     |

|               | I2CMMIS Register                                                           |     |

|               | I2CMICR Register                                                           |     |

|               | I2CMCR Register                                                            |     |

| •             | I2CMCLKOCNT Register                                                       |     |

| •             | I2CMBMON Register                                                          |     |

|               | I2CMBLEN Register                                                          |     |

| -             | I2CMBCNT Register                                                          |     |

| •             | I2CSOAR Register                                                           |     |

| •             | I2CSCSR Register                                                           |     |

| •             | I2CSDR Register                                                            |     |

| •             | I2CSIMR Register                                                           |     |

| •             | I2CSRIS Register                                                           |     |

|               | I2CSMIS Register                                                           |     |

| Figure 7-33.  | I2CSICR Register                                                           | 250 |

|               | I2CSOAR2 Register                                                          |     |

| Figure 7-35.  | I2CSACKCTL Register                                                        | 253 |

| Figure 7-36.  | I2CFIFODATA Register                                                       | 254 |

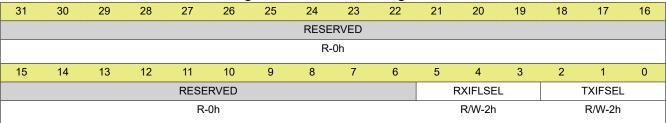

| Figure 7-37.  | I2CFIFOCTL Register                                                        | 255 |

| Figure 7-38.  | I2CFIFOSTATUS Register                                                     | 257 |

| Figure 7-39.  | I2CPP Register                                                             | 258 |

| Figure 7-40.  | I2CPC Register                                                             | 259 |

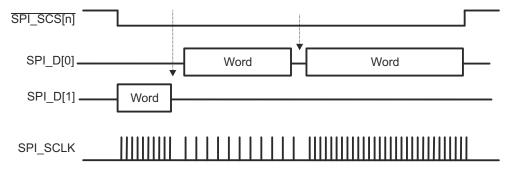

|               | SPI Block Diagram                                                          |     |

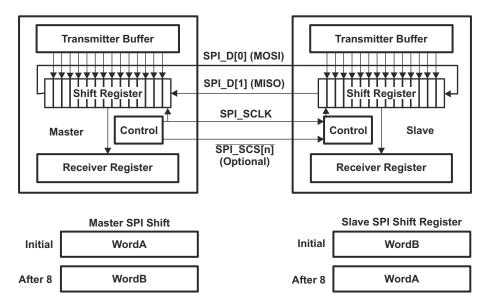

|               | SPI Full-Duplex Transmission (Example)                                     |     |

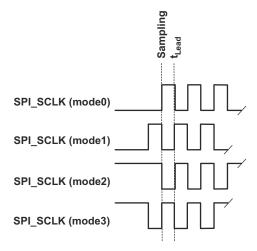

|               | Phase and Polarity Combinations                                            |     |

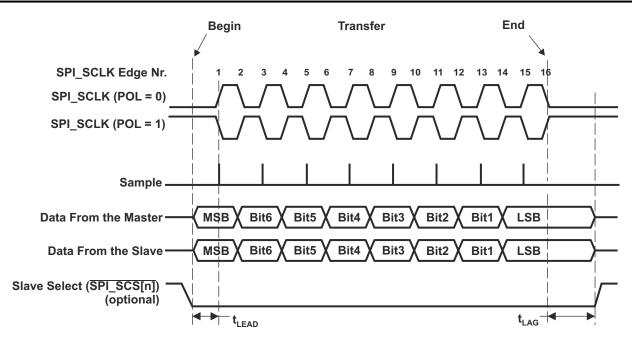

|               | Full-Duplex Single Transfer Format With PHA = 0                            |     |

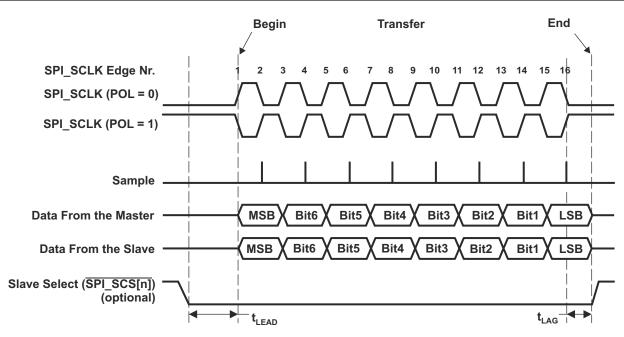

|               | Full-Duplex Single Transfer Format With PHA = 1                            |     |

|               | Contiguous Transfers With SPIEN Kept Active (Two Data Pins Interface Mode) |     |

|               | ransmit/Receive Mode With No FIFO Used                                     |     |

|               | Fransmit/Receive Mode With Only Receive FIFO Enabled                       |     |

|               | ransmit/Receive Mode With Only Transmit FIFO Used                          |     |

|               | Transmit/Receive Mode With Both FIFO Directions Used                       |     |

|               | Buffer Almost Full Level (AFL)                                             |     |

|               | Buffer Almost Empty Level (AEL)                                            |     |

|               | 3-Pin Mode System Overview                                                 |     |

|               | Flow Chart – Module Initialization.                                        |     |

| •             | Flow Chart – Common Transfer Sequence                                      |     |

|               | Flow Chart – Transmit and Receive (Master and Slave)                       |     |

|               | Flow Chart – FIFO Mode Common Sequence (Master)                            |     |

|               | Flow Chart – FIFO Mode Transmit and Receive With Word Count (Master)       |     |

| •             | Flow Chart – FIFO Mode Transmit and Receive without Word Count (Master)    |     |

| -             | SPI_SYSCONFIG Register                                                     |     |

| -             | SPI SYSSTATUS Register                                                     |     |

| •             | = *                                                                        |     |

| •             | SPI_IRQSTATUS Register                                                     |     |

| -             | SPI_IRQENABLE Register                                                     |     |

|               | SPI_MODULCTRL Register                                                     |     |

|               | SPI_CHCONF Register                                                        |     |

| -             | SPI_CHSTAT Register                                                        |     |

| •             | SPI_CHCTRL Register                                                        |     |

| U             | SPI_TX Register                                                            |     |

|               | SPI_RX Register                                                            |     |

| -             | SPI_XFERLEVEL Register                                                     |     |

|               | GPTM Module Block Diagram                                                  |     |

|               | nput Edge-Count Mode Example, Counting Down                                |     |

|               | 6-Bit Input Edge-Time Mode Example                                         |     |

| -             | 6-Bit PWM Mode Example                                                     |     |

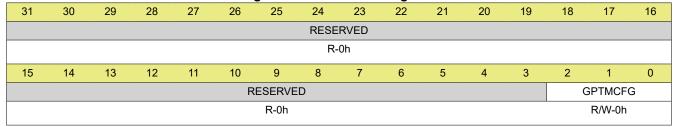

| -             | GPTMCFG Register                                                           |     |

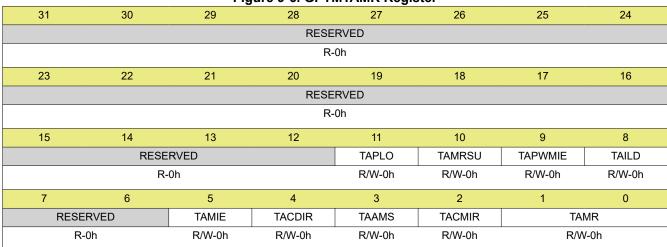

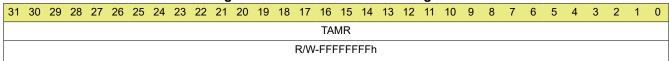

| Figure 9-6. 0 | GPTMTAMR Register                                                          | 315 |

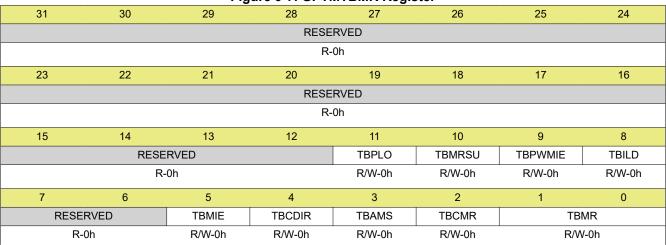

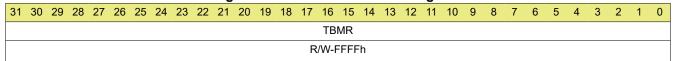

| -             | GPTMTBMR Register                                                          |     |

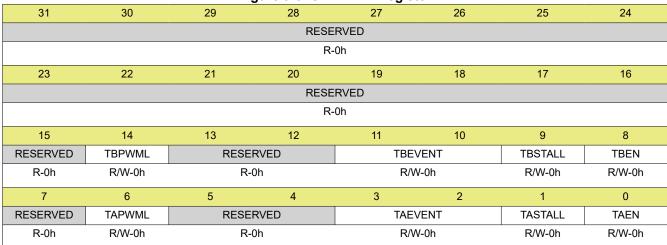

| Figure 9-8. 0 | GPTMCTL Register                                                           | 319 |

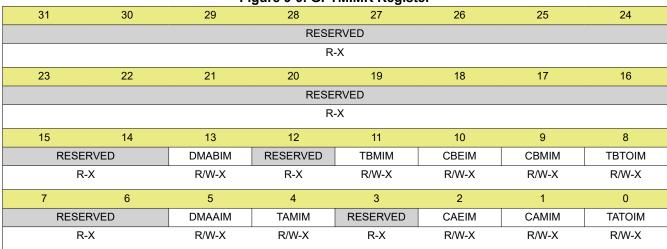

| Figure 9-9. GPTMIMR Register                                                    |     |

|---------------------------------------------------------------------------------|-----|

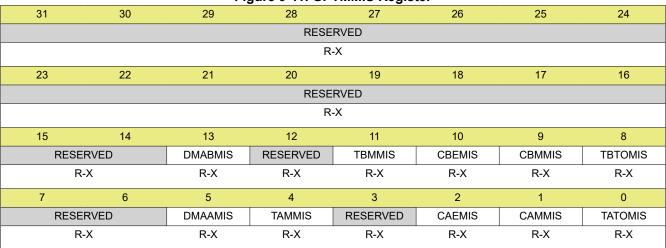

| Figure 9-10. GPTMRIS Register                                                   |     |

| Figure 9-11. GPTMMIS Register                                                   |     |

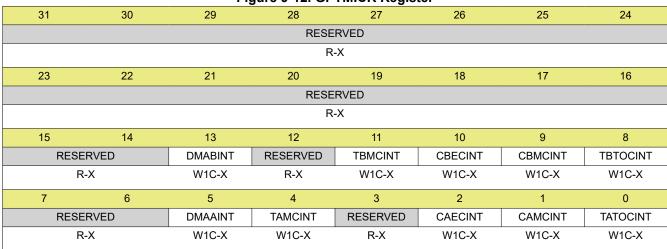

| Figure 9-12. GPTMICR Register                                                   |     |

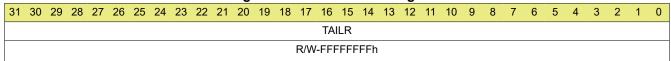

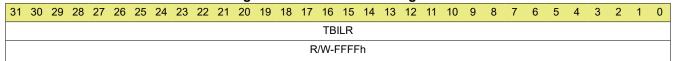

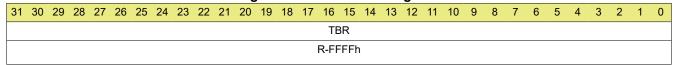

| Figure 9-13. GPTMTAILR Register                                                 |     |

| Figure 9-14. GPTMTBILR Register                                                 |     |

| Figure 9-15. GPTMTAMATCHR Register                                              |     |

| Figure 9-16. GPTMTBMATCHR Register                                              |     |

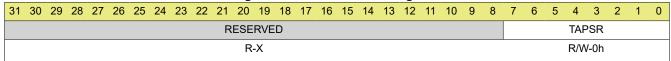

| Figure 9-17. GPTMTAPR Register                                                  |     |

| Figure 9-18. GPTMTBPR Register                                                  |     |

| Figure 9-19. GPTMTAPMR Register                                                 |     |

| Figure 9-20. GPTMTBPMR Register                                                 |     |

| Figure 9-21. GPTMTAR Register                                                   |     |

| Figure 9-22. GPTMTBR Register                                                   |     |

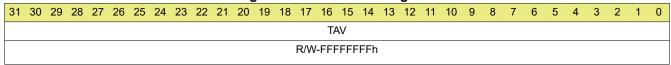

| Figure 9-23. GPTMTAV Register                                                   |     |

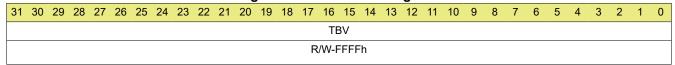

| Figure 9-24. GPTMTBV Register                                                   |     |

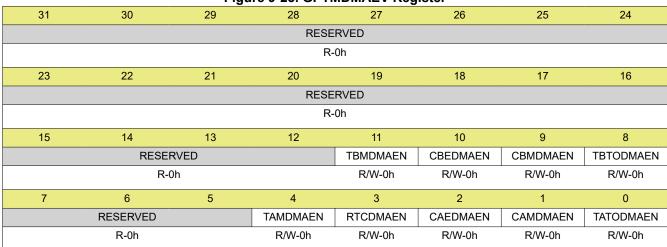

| Figure 9-25. GPTMDMAEV Register                                                 |     |

| Figure 10-1. WDT Module Block Diagram                                           |     |

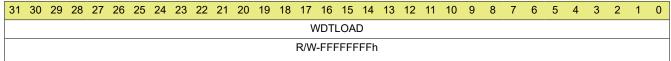

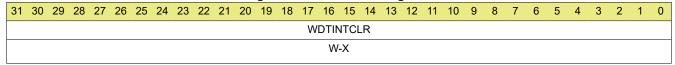

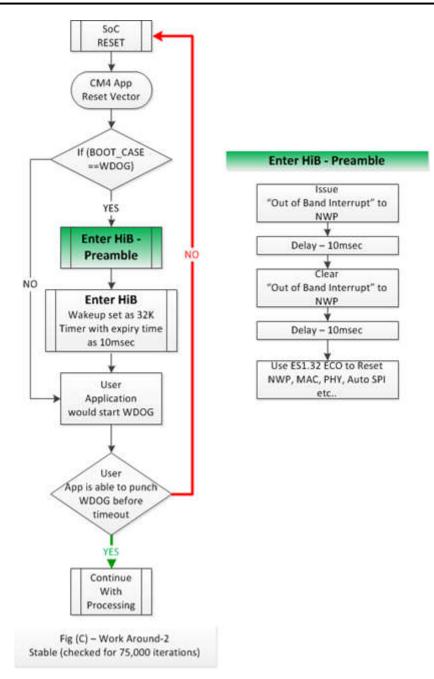

| Figure 10-2. WDTLOAD Register                                                   |     |

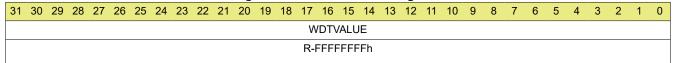

| Figure 10-3. WDTVALUE Register                                                  |     |

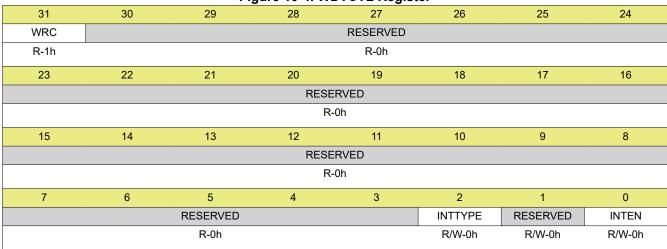

| Figure 10-4. WDTCTL Register                                                    |     |

| Figure 10-5. WDTICR Register                                                    |     |

| Figure 10-6. WDTRIS Register                                                    |     |

| Figure 10-7. WDTTEST Register                                                   |     |

| Figure 10-8. WDTLOCK Register                                                   |     |

| Figure 10-9. Watchdog Flow ChartFigure 10-10. System Watchdog Recovery Sequence |     |

| Figure 11-1. SDHost Controller Interface Block Diagram                          |     |

| Figure 11-2. MMCHS CSRE Register                                                |     |

| Figure 11-3. MMCHS_CON Register                                                 |     |

| Figure 11-4. MMCHS_BLK Register                                                 |     |

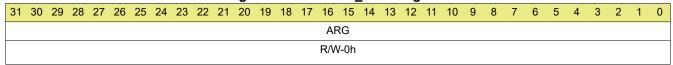

| Figure 11-5. MMCHS_ARG Register                                                 |     |

| Figure 11-6. MMCHS CMD Register                                                 |     |

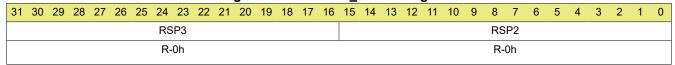

| Figure 11-7. MMCHS_RSP10 Register                                               |     |

| Figure 11-8. MMCHS RSP32 Register                                               |     |

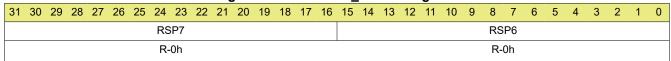

| Figure 11-9. MMCHS_RSP54 Register                                               |     |

| Figure 11-10. MMCHS_RSP76 Register                                              |     |

| Figure 11-11. MMCHS DATA Register                                               |     |

| Figure 11-12. MMCHS_PSTATE Register                                             |     |

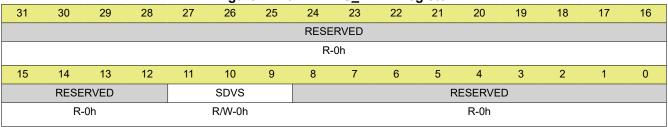

| Figure 11-13. MMCHS HCTL Register                                               |     |

| Figure 11-14. MMCHS_SYSCTL Register                                             |     |

| Figure 11-15. MMCHS_STAT Register                                               |     |

| Figure 11-16. MMCHS IE Register                                                 |     |

| Figure 11-17. MMCHS ISE Register                                                |     |

| Figure 12-1. I2S Protocol                                                       |     |

| Figure 12-2. I2S Module                                                         |     |

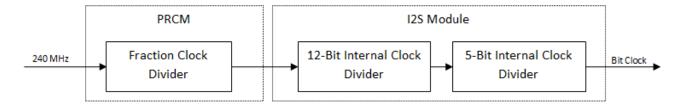

| Figure 12-3. Logical Clock Path                                                 | 402 |

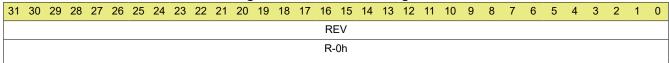

| Figure 12-4. AFIFOREV Register                                                  | 415 |

| Figure 12-5. WFIFOCTL Register                                                  | 416 |

| Figure 12-6. PDIR Register                                                      | 418 |

| Figure 12-7. RFIFOCTL Register                                                  | 420 |

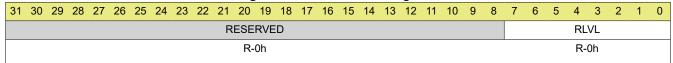

| Figure 12-8. RFIFOSTS Register                                                  | 422 |

| Figure 12-9. GBLCTL Register                                                    |     |

| Figure 12-10. RGBLCTL Register                                                  |     |

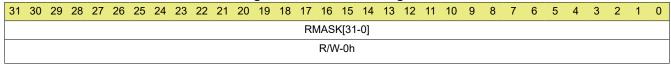

| Figure 12-11. RMASK Register                                                    |     |

| Figure 12-12. RFMT Register                                                     | 429 |

| Figure 12-13. AFSRCTL Register                                                  | 431 |

| Figure 12-14. RTDM Register                                                     | 432 |

| Figure 12-15. RINTCTL Register                                                  |     |

| Figure 12-16. RSTAT Register                                                    |     |

| Figure 12-17. RSLOT Register                                                    | 437 |

| Figure 42.40 DEVECTI Decistor                                    | 420   |

|------------------------------------------------------------------|-------|

| Figure 12-18. REVTCTL Register                                   |       |

| Figure 12-19. XGBLCTL Register                                   |       |

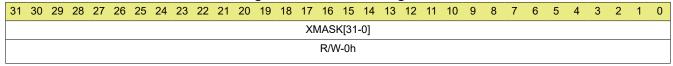

| Figure 12-20. XMASK Register                                     |       |

| Figure 12-21. XFMT Register                                      |       |

| Figure 12-22. AFSXCTL Register                                   |       |

| Figure 12-23. ACLKXCTL Register                                  |       |

| Figure 12-24. AHCLKXCTL Register                                 |       |

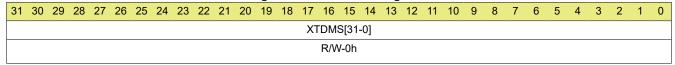

| Figure 12-25. XTDM Register                                      |       |

| Figure 12-26. XINTCTL Register                                   |       |

| Figure 12-27. XSTAT Register                                     |       |

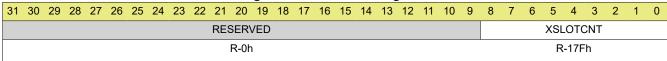

| Figure 12-28. XSLOT Register                                     |       |

| Figure 12-29. XEVTCTL Register                                   |       |

| Figure 12-30. SRCTLn Registers                                   |       |

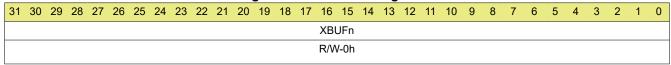

| Figure 12-31. XBUFn Registers                                    | .457  |

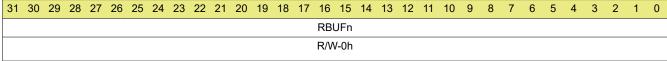

| Figure 12-32. RBUFn Registers                                    |       |

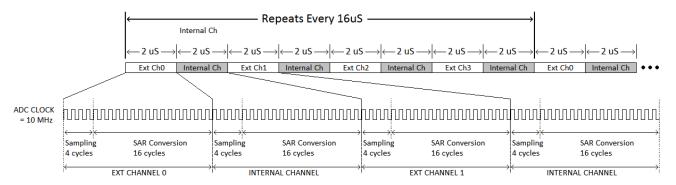

| Figure 13-1. Architecture of the ADC Module in CC32xx            | . 460 |

| Figure 13-2. Operation of the ADC                                | .461  |

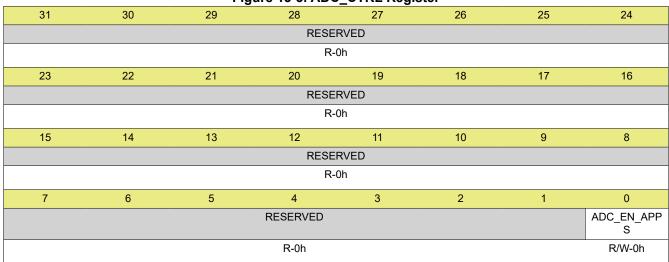

| Figure 13-3. ADC_CTRL Register                                   | .463  |

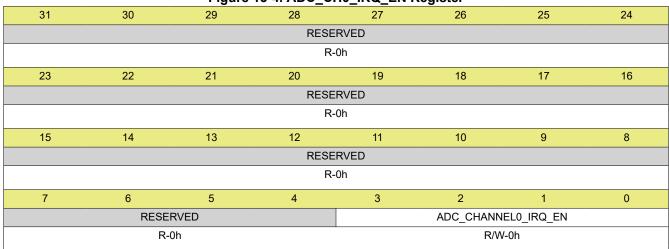

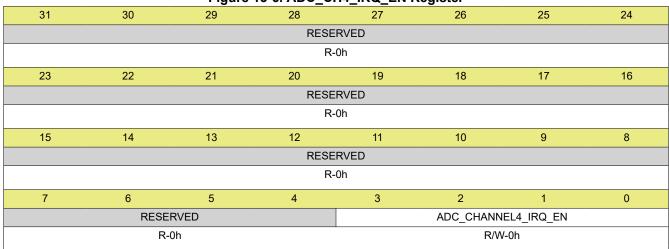

| Figure 13-4. ADC_CH0_IRQ_EN Register                             |       |

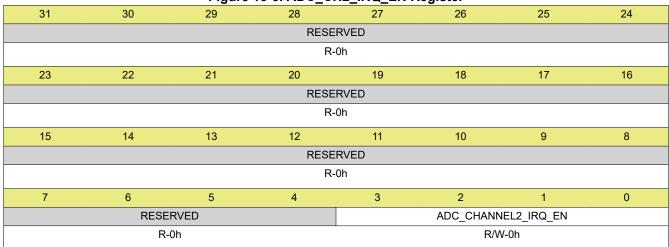

| Figure 13-5. ADC CH2 IRQ EN Register                             |       |

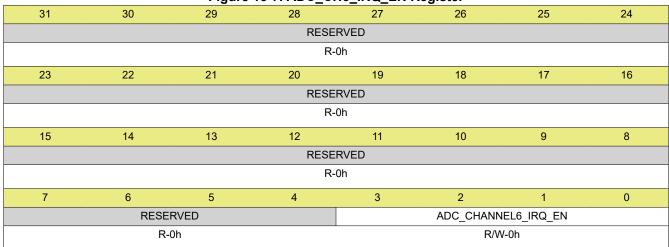

| Figure 13-6. ADC_CH4_IRQ_EN Register                             |       |

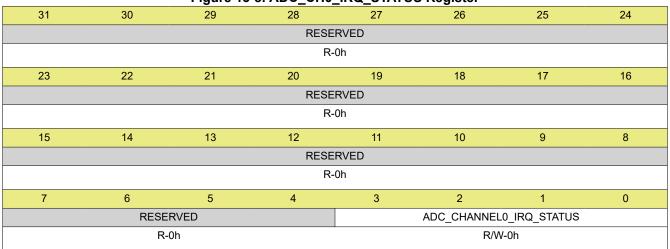

| Figure 13-7. ADC CH6 IRQ EN Register                             |       |

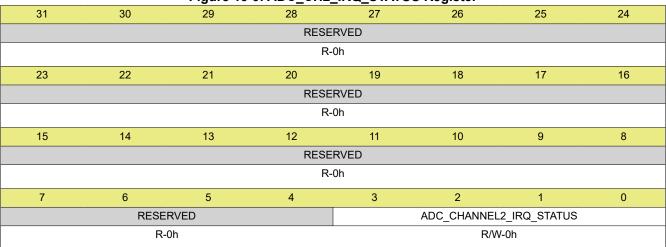

| Figure 13-8. ADC_CH0_IRQ_STATUS Register                         |       |

| Figure 13-9. ADC_CH2_IRQ_STATUS Register                         |       |

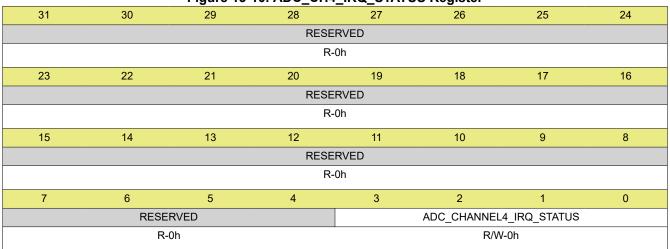

| Figure 13-10. ADC CH4 IRQ STATUS Register                        |       |

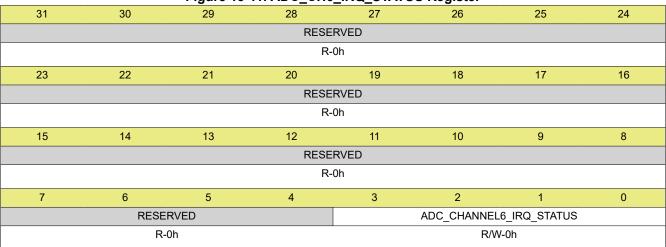

| Figure 13-11. ADC_CH6_IRQ_STATUS Register                        |       |

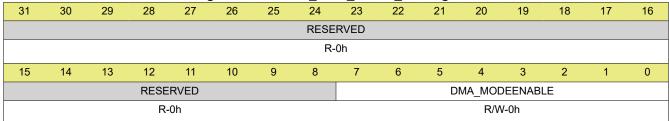

| Figure 13-12. ADC_DMA_MODE_EN Register                           |       |

| Figure 13-13. ADC_TIMER_CONFIGURATION Register                   |       |

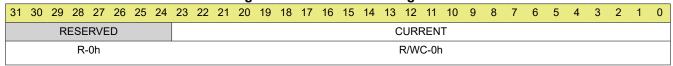

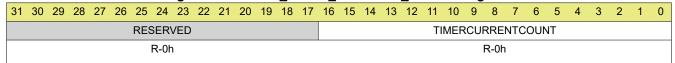

| Figure 13-13. ADC_TIMER_CURRENT_COUNT Register                   |       |

|                                                                  |       |

| Figure 13-15. CHANNEL0FIFODATA Register                          |       |

| Figure 13-16. CHANNEL2FIFODATA Register                          |       |

| Figure 13-17. CHANNEL4FIFODATA Register                          |       |

| Figure 13-18. CHANNEL6FIFODATA Register                          | .4/5  |

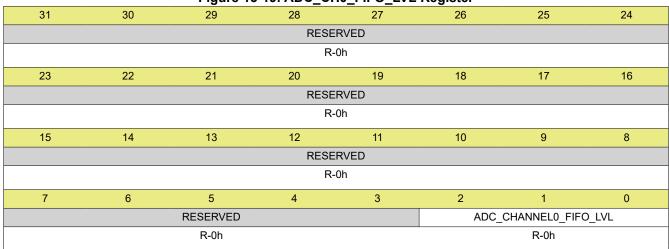

| Figure 13-19. ADC_CH0_FIFO_LVL Register                          |       |

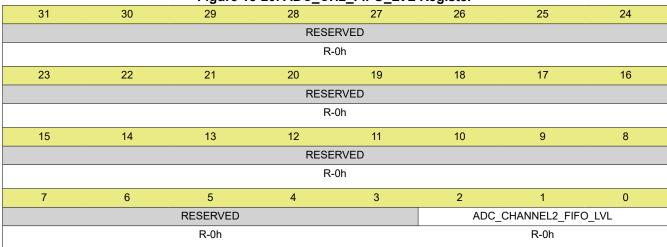

| Figure 13-20. ADC_CH2_FIFO_LVL Register                          |       |

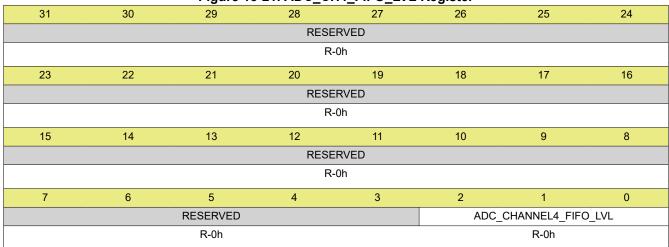

| Figure 13-21. ADC_CH4_FIFO_LVL Register                          |       |

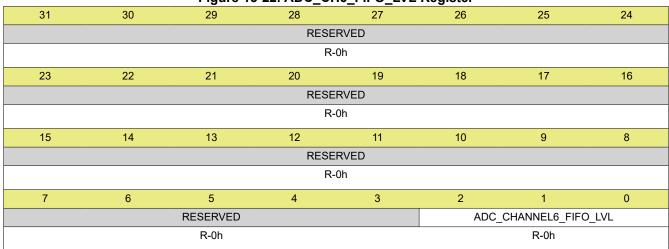

| Figure 13-22. ADC_CH6_FIFO_LVL Register                          |       |

| Figure 13-23. ADC_CH_ENABLE Register                             |       |

| Figure 14-1. Camera Module Interfaces                            |       |

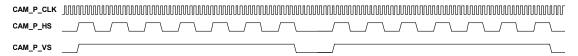

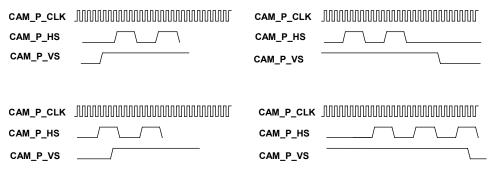

| Figure 14-2. Synchronization Signals and Frame Timing            | .491  |

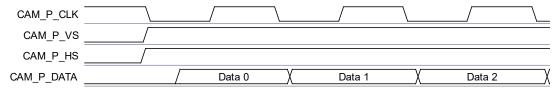

| Figure 14-3. Synchronization Signals and Data Timing             | .491  |

| Figure 14-4. Different Scenarios of CAM_P_HS and CAM_P_VS        | . 492 |

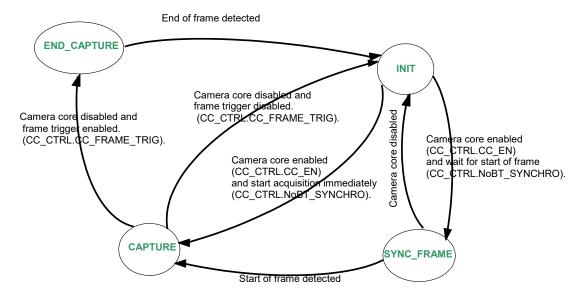

| Figure 14-5. CAM P HS Toggles Between Pixels in Decimation       | . 492 |

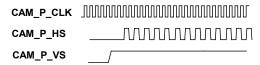

| Figure 14-6. Parallel Camera Interface State Machine             | .492  |

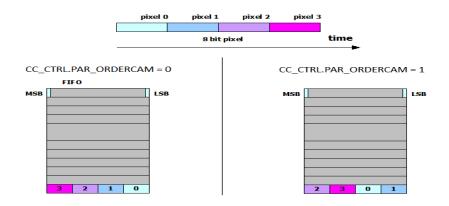

| Figure 14-7. FIFO Image Data Format                              |       |

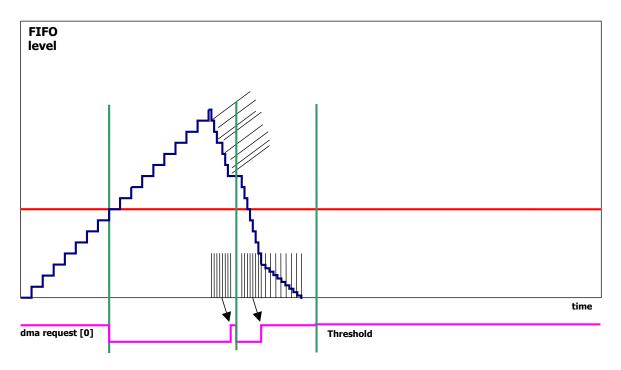

| Figure 14-8. Assertion and Deassertion of the DMA Request Signal |       |

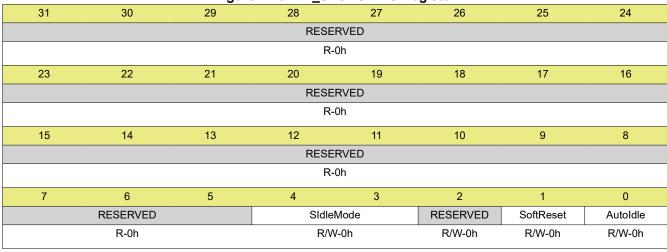

| Figure 14-9. CC_SYSCONFIG Register                               |       |

| Figure 14-10. CC_SYSSTATUS Register                              |       |

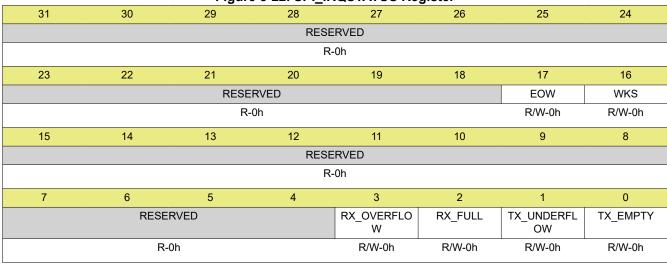

| Figure 14-11. CC_IRQSTATUS Register                              |       |

| Figure 14-12. CC IRQENABLE Register                              |       |

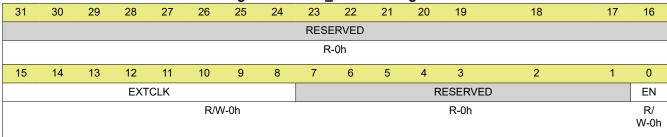

| Figure 14-13. CC_CTRL Register                                   |       |

| Figure 14-14. CC_CTRL_DMA Register                               |       |

| •                                                                |       |

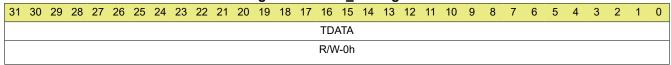

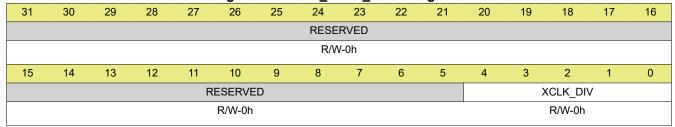

| Figure 14-15. CC_CTRL_XCLK Register                              |       |

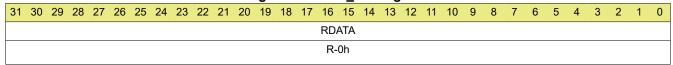

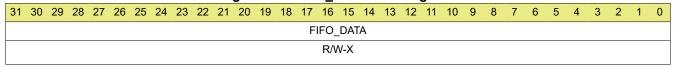

| Figure 14-16. CC_FIFODATA Register                               |       |

| Figure 15-1. Sleep Modes.                                        |       |

| Figure 15-2. Power Management Control Architecture in CC32xx     |       |

| Figure 15-3. CAMCLKCFG Register                                  |       |

| Figure 15-4. CAMCLKEN Register                                   |       |

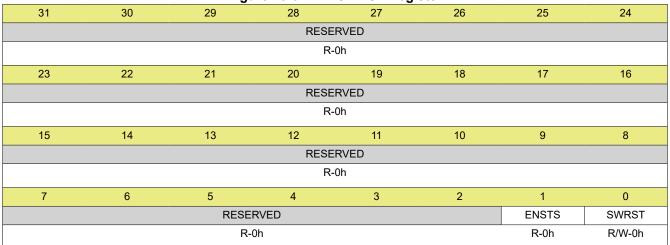

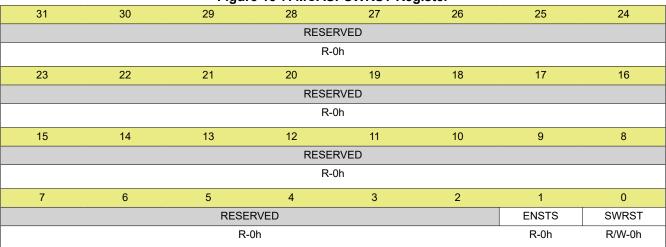

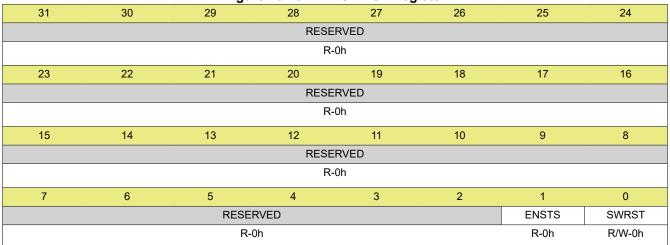

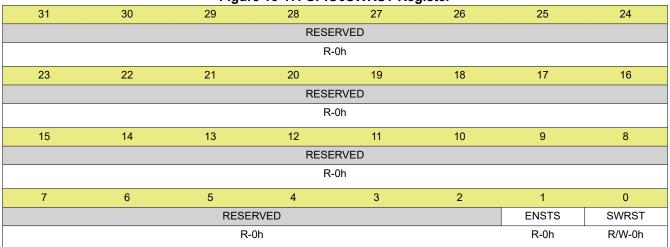

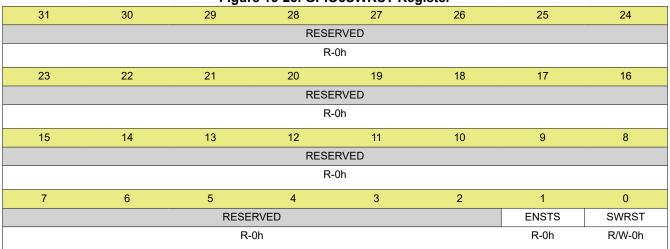

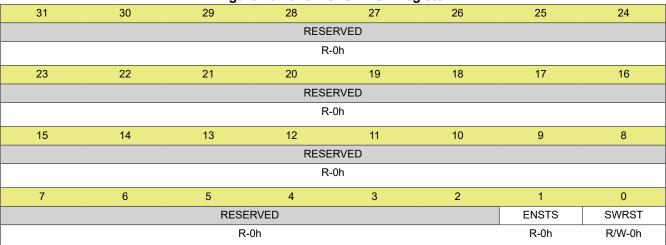

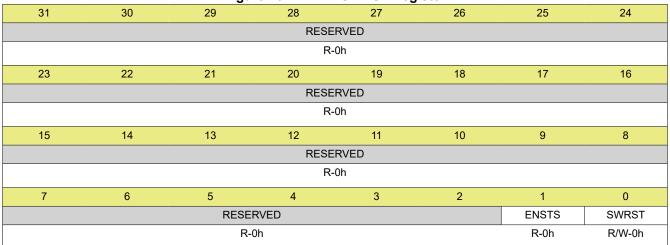

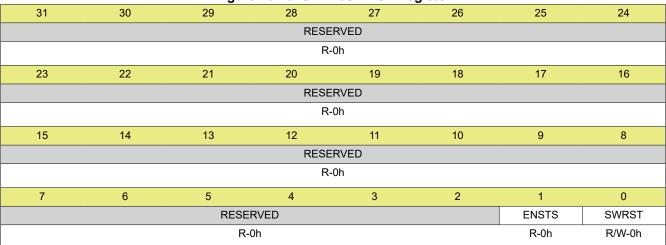

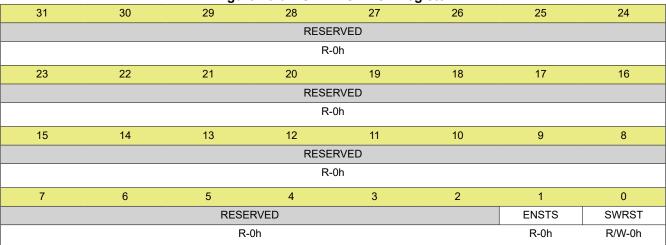

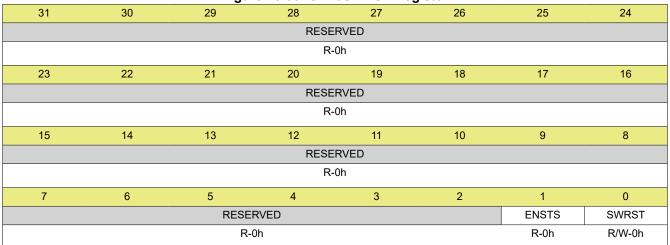

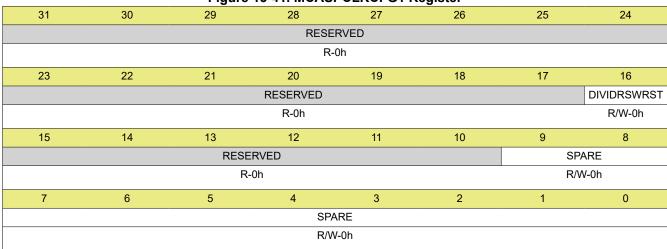

| Figure 15-5. CAMSWRST Register                                   |       |

| Figure 15-6. MCASPCLKEN Register                                 |       |

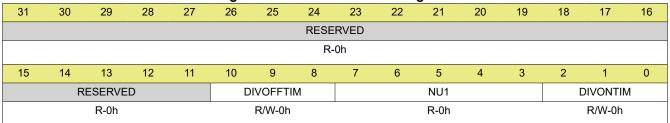

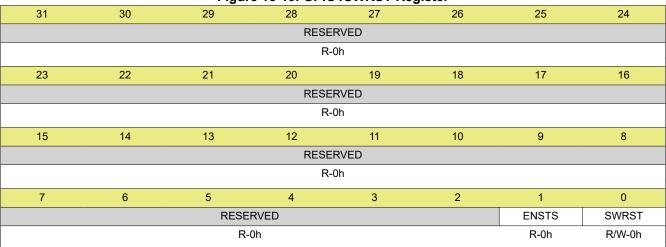

| Figure 15-7. MCASPSWRST Register                                 | . 539 |

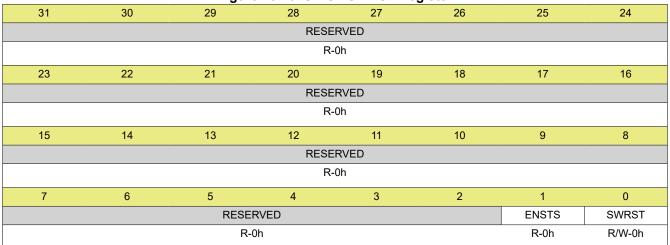

|        | 15-8. SDIOMCLKCFG Register                                         |       |

|--------|--------------------------------------------------------------------|-------|

|        | 15-9. SDIOMCLKEN Register                                          |       |

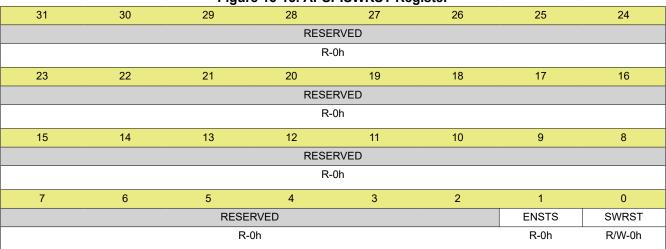

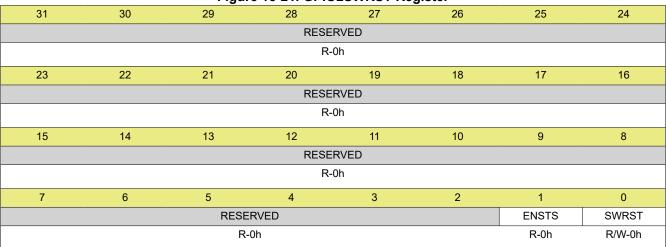

|        | 15-10. SDIOMSWRST Register                                         |       |

|        | 15-11. APSPICLKCFG Register                                        |       |

|        | 15-12. APSPICLKEN Register                                         |       |

| Figure | 15-13. APSPISWRST Register                                         | 545   |

| Figure | 15-14. DMACLKEN Register                                           | .546  |

|        | 15-15. DMASWRST Register                                           |       |

| Figure | 15-16. GPIO0CLKEN Register                                         | 548   |

| Figure | 15-17. GPIO0SWRST Register                                         | 549   |

|        | 15-18. GPIO1CLKEN Register                                         |       |

| Figure | 15-19. GPIO1SWRST Register                                         | . 551 |

| Figure | 15-20. GPIO2CLKEN Register                                         | 552   |

| Figure | 15-21. GPIO2SWRST Register                                         | . 553 |

| Figure | 15-22. GPIO3CLKEN Register                                         | 554   |

| Figure | 15-23. GPIO3SWRST Register                                         | . 555 |

| Figure | 15-24. GPIO4CLKEN Register                                         | 556   |

| Figure | 15-25. GPIO4SWRST Register                                         | 557   |

| Figure | 15-26. WDTCLKEN Register                                           | .558  |

| Figure | 15-27. WDTSWRST Register                                           | .559  |

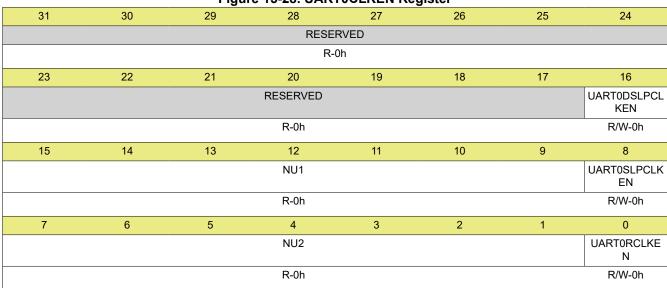

|        | 15-28. UART0CLKEN Register                                         |       |

| Figure | 15-29. UART0SWRST Register                                         | 561   |

| Figure | 15-30. UART1CLKEN Register                                         | 562   |

| Figure | 15-31. UART1SWRST Register                                         | 563   |

| Figure | 15-32. GPT0CLKCFG Register                                         | 564   |

| Figure | 15-33. GPT0SWRST Register                                          | .565  |

| Figure | 15-34. GPT1CLKEN Register                                          | .566  |

| Figure | 15-35. GPT1SWRST Register                                          | .567  |

| Figure | 15-36. GPT2CLKEN Register                                          | .568  |

| Figure | 15-37. GPT2SWRST Register                                          | .569  |

| Figure | 15-38. GPT3CLKEN Register                                          | .570  |

| Figure | 15-39. GPT3SWRST Register                                          | .571  |

| Figure | 15-40. MCASPCLKCFG0 Register                                       | .572  |

| Figure | 15-41. MCASPCLKCFG1 Register                                       | .573  |

| Figure | 15-42. I2CLCKEN Register                                           | 574   |

|        | 15-43. I2CSWRST Register                                           |       |

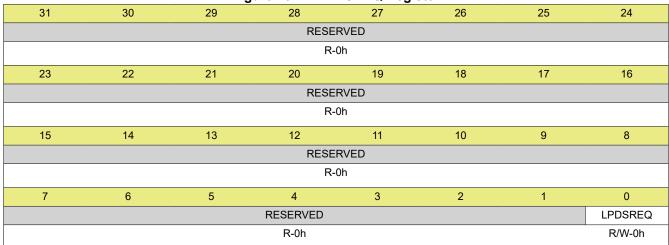

| Figure | 15-44. LPDSREQ Register                                            | .576  |

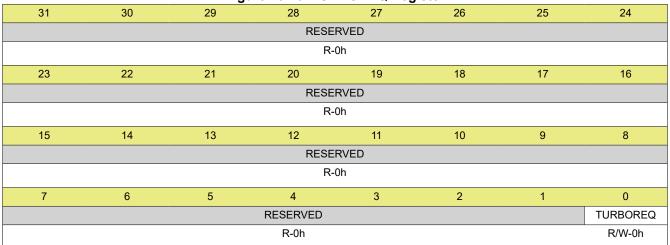

|        | 15-45. TURBOREQ Register                                           |       |

| Figure | 15-46. DSLPWAKECFG Register                                        | .578  |

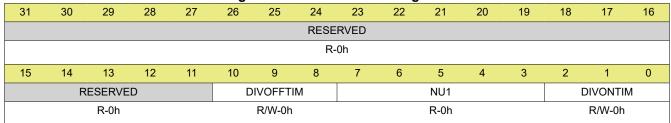

|        | 15-47. DSLPTIMRCFG Register                                        |       |

|        | 15-48. SLPWAKEEN Register                                          |       |

| Figure | 15-49. SLPTMRCFG Register                                          | .581  |

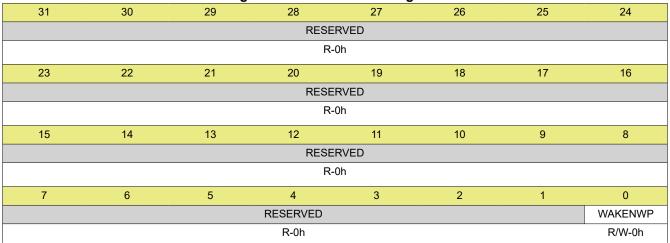

|        | 15-50. WAKENWP Register                                            |       |

|        | 15-51. RCM_IS Register                                             |       |

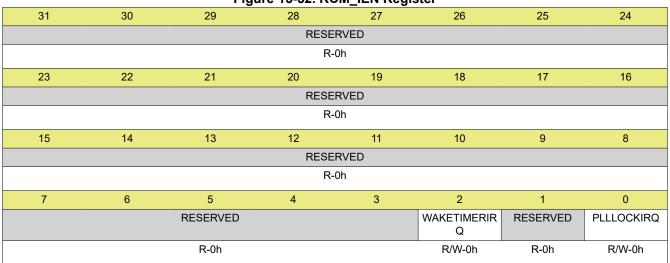

|        | 15-52. RCM_IEN Register                                            |       |

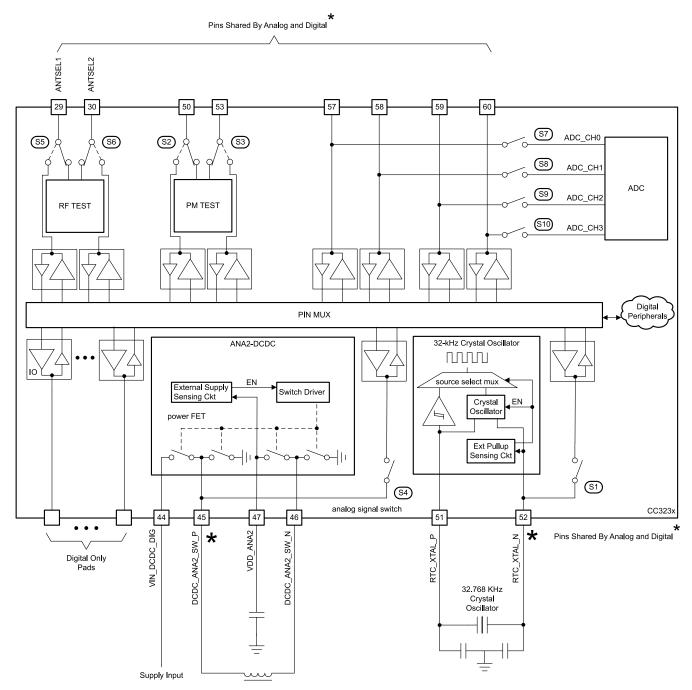

|        | 16-1. Board Configuration to Use Pins 45 and 52                    |       |

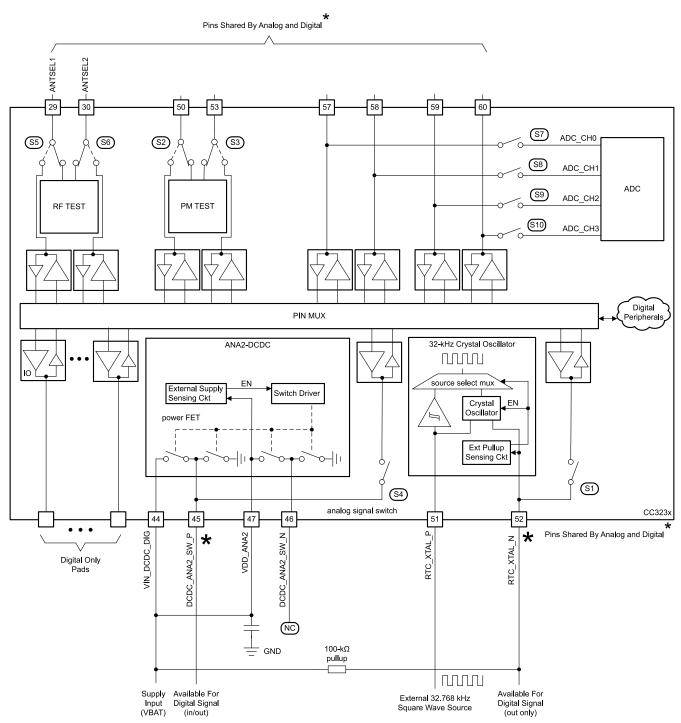

| Figure | 16-2. Board Configuration to Use Pins 45 and 52 as Digital Signals | 590   |

| Figure | 16-3. I/O Pad Data and Control Path Architecture in CC32xx         | .609  |

|        | 16-4. Wake on Pad for Hibernate Mode                               |       |

| Figure | 17-1. AES Block Diagram                                            | .617  |

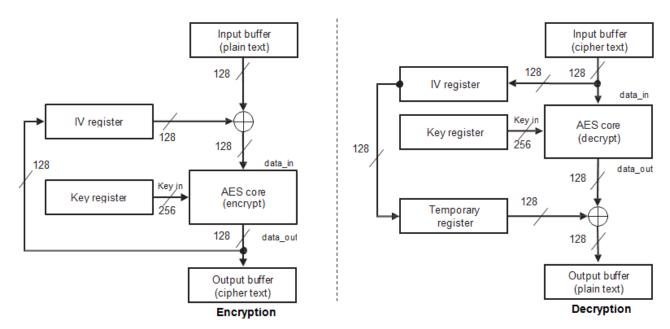

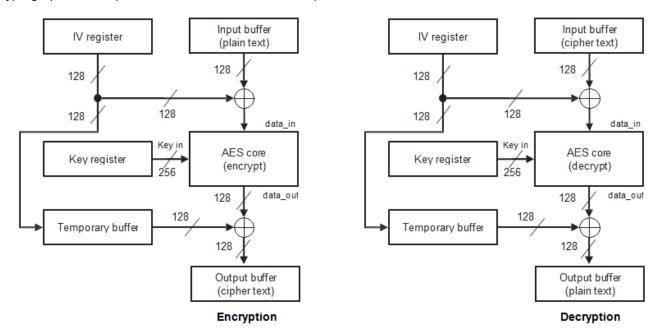

| Figure | 17-2. AES - ECB Feedback Mode                                      | .620  |

|        | 17-3. AES - CBC Feedback Mode                                      |       |

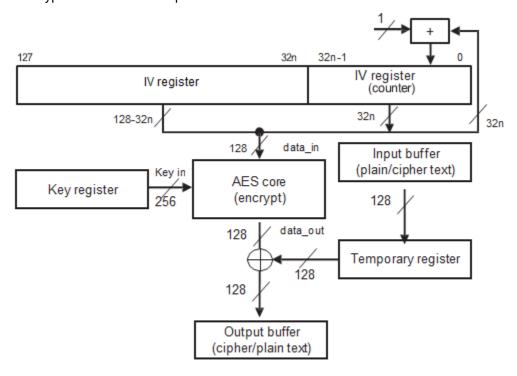

|        | 17-4. AES Encryption With CTR/ICM Mode                             |       |

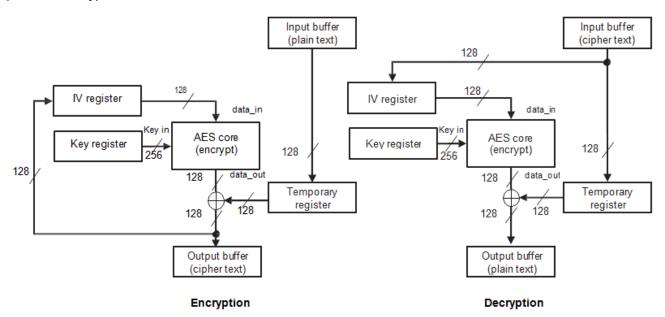

|        | 17-5. AES - CFB Feedback Mode                                      |       |

|        | 17-6. AES - F8 Mode                                                |       |

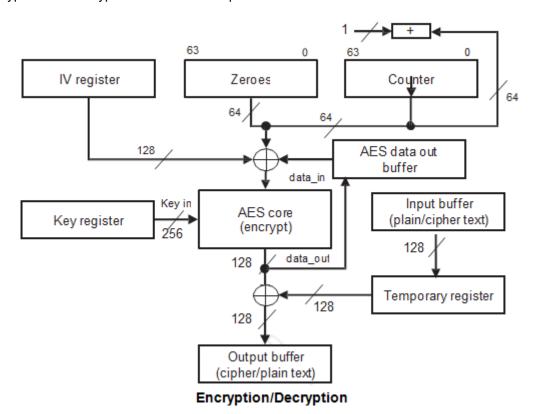

|        | 17-7. AES - XTS Operation                                          |       |

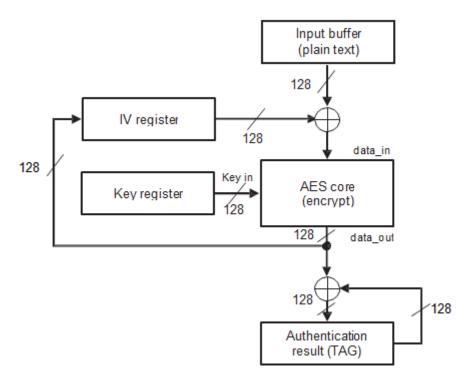

| Figure | 17-8. AES - F9 Operation                                           | 626   |

|        | 17-9. AES - CBC-MAC Authentication Mode                            |       |

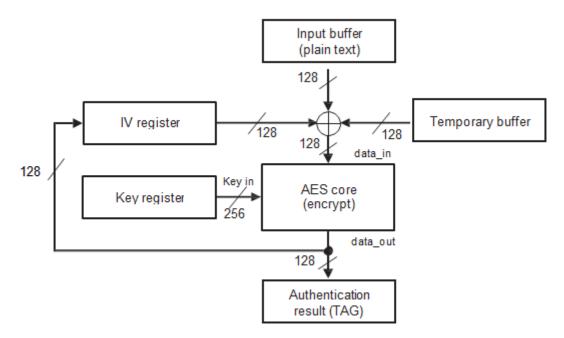

| Figure | 17-10. AES - GCM Operation                                         | .628  |

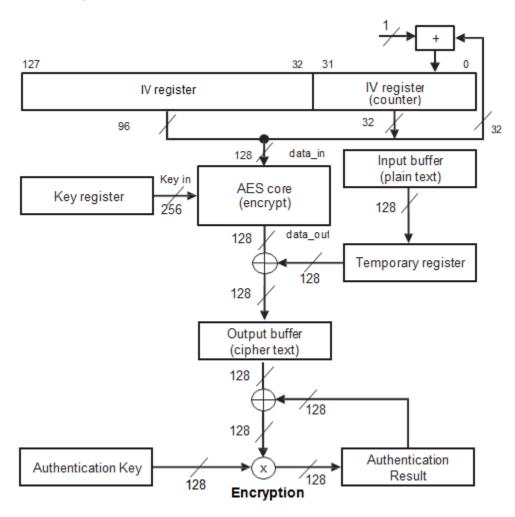

| Figure | 17-11. AES - CCM Operation                                         | 629   |

| Figure | 17-12. AES Polling Mode                                            | 633   |

| Figure 17.12 AES Interrupt Service           | 625 |

|----------------------------------------------|-----|

| Figure 17-13. AES Interrupt Service          |     |

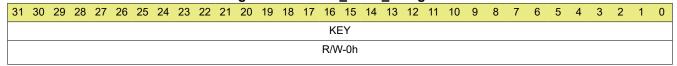

| Figure 17-14. AES_KEY2_6 Register            |     |

| Figure 17-15. AES_KEY2_7 Register            |     |

| Figure 17-16. AES_KEY2_4 Register            |     |

| Figure 17-17. AES_KEY2_5 Register            |     |

| Figure 17-18. AES_KEY2_2 Register            |     |

| Figure 17-19. AES_KEY2_3 Register            |     |

| Figure 17-20. AES_KEY2_0 Register            |     |

| Figure 17-21. AES_KEY2_1 Register            |     |

| Figure 17-22. AES_KEY1_6 Register            |     |

| Figure 17-23. AES_KEY1_7 Register            |     |

| Figure 17-24. AES_KEY1_4 Register            |     |

| Figure 17-25. AES_KEY1_5 Register            |     |

| Figure 17-26. AES_KEY1_2 Register            | 643 |

| Figure 17-27. AES_KEY1_3 Register            | 643 |

| Figure 17-28. AES_KEY1_0 Register            | 644 |

| Figure 17-29. AES_KEY1_1 Register            | 644 |

| Figure 17-30. AES_IV_IN_0 Register           | 645 |

| Figure 17-31. AES_IV_IN_1 Register           | 645 |

| Figure 17-32. AES IV IN 2 Register           | 646 |

| Figure 17-33. AES_IV_IN_3 Register           |     |

| Figure 17-34. AES CTRL Register              |     |

| Figure 17-35. AES_C_LENGTH_0 Register        |     |

| Figure 17-36. AES_C_LENGTH_1 Register        |     |

| Figure 17-37. AES AUTH LENGTH Register       |     |

| Figure 17-38. AES DATA IN 0 Register         |     |

| Figure 17-39. AES_DATA_IN_1 Register         |     |

| Figure 17-40. AES_DATA_IN_2 Register         |     |

| Figure 17-41. AES_DATA_IN_3 Register         |     |

| Figure 17-41. AES_DATA_IN_3 Register         |     |

| Figure 17-43. AES_TAG_OUT_1 Register         |     |

|                                              |     |

| Figure 17-44. AES_TAG_OUT_2 Register         |     |

| Figure 17-45. AES_TAG_OUT_3 Register         |     |

| Figure 17-46. AES_REVISION Register          |     |

| Figure 17-47. AES_SYSCONFIG Register         |     |

| Figure 17-48. AES_IRQSTATUS Register         |     |

| Figure 17-49. AES_IRQENABLE Register         |     |

| Figure 17-50. CRYPTOCLKEN Register           |     |

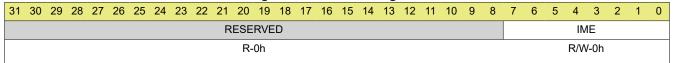

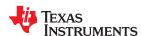

| Figure 17-51. DTHE_AES_IM Register           |     |

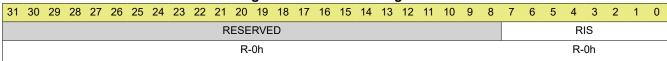

| Figure 17-52. DTHE_AES_RIS Register          |     |

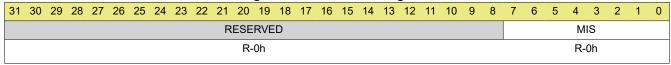

| Figure 17-53. DTHE_AES_MIS Register          |     |

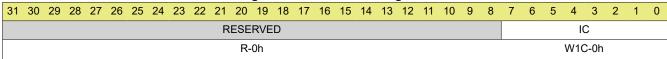

| Figure 17-54. DTHE_AES_IC Register           | 666 |

| Figure 18-1. DES Block Diagram               |     |

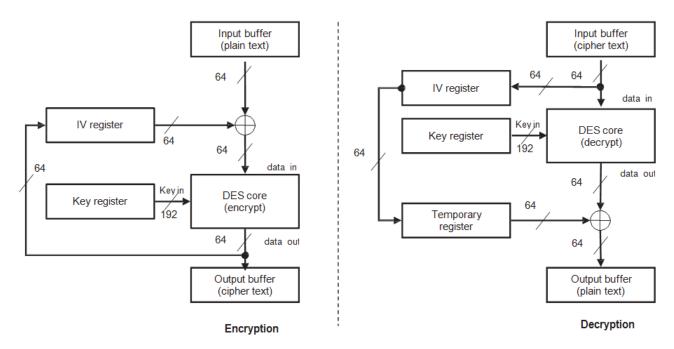

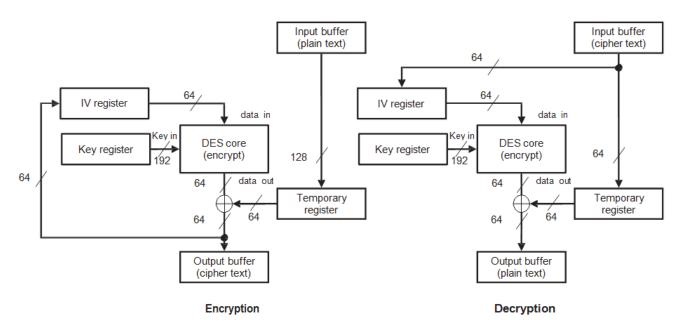

| Figure 18-2. DES – ECB Feedback Mode         | 671 |

| Figure 18-3. DES3DES – CBC Feedback Mode     | 671 |

| Figure 18-4. DES3DES – CFB Feedback Mode     | 672 |

| Figure 18-5. DES Polling Mode                | 674 |

| Figure 18-6. DES Interrupt Service           | 675 |

| Figure 18-7. DES Context Input Event Service |     |

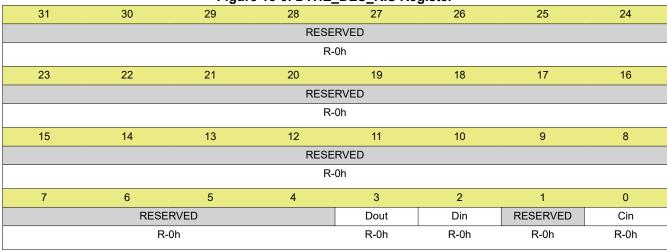

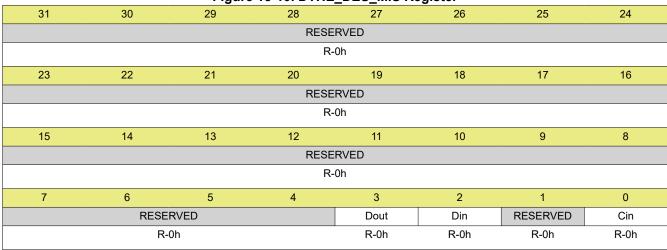

| Figure 18-8. DTHE DES IM Register            |     |

| Figure 18-9. DTHE DES RIS Register           |     |

| Figure 18-10. DTHE_DES_MIS Register          |     |

| Figure 18-11. DTHE_DES_IC Register           |     |

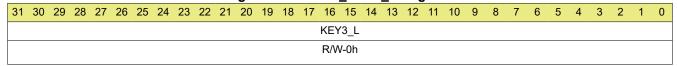

| Figure 18-12. DES KEY3 L Register            |     |

| Figure 18-13. DES KEY3 H Register            |     |

| Figure 18-14. DES_KEY2_L Register            |     |

| Figure 18-15. DES_KEY2_H Register            |     |

|                                              |     |

| Figure 18-16. DES_KEY1_L Register            |     |

| Figure 18-17. DES_KEY1_H Register            |     |

| Figure 18-18. DES_IV_L Register              |     |

| Figure 18-19. DES_IV_H Register              | 689 |

| Figure 18-20. DES_CTRL Register                                                                                   |       |

|-------------------------------------------------------------------------------------------------------------------|-------|

| Figure 18-21. DES_LENGTH Register                                                                                 |       |

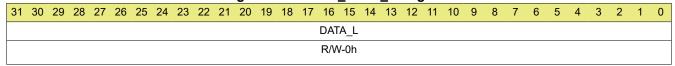

| Figure 18-22. DES_DATA_L Register                                                                                 |       |

| Figure 18-23. DES_DATA_H Register                                                                                 |       |

| Figure 18-24. DES_SYSCONFIG Register                                                                              |       |

| Figure 18-25. DES_IRQSTATUS Register                                                                              |       |

| Figure 18-26. DES_IRQENABLE Register                                                                              |       |

| Figure 19-1. SHA/MD5 Module Block Diagram                                                                         |       |

| Figure 19-2. SHA/MD5 Polling Mode                                                                                 |       |

| Figure 19-3. SHA/MD5 Interrupt Subroutine                                                                         |       |

| Figure 19-4. Overview of Public World, Inner and Outer Digest Registers, and Usage for MD5, SHA-1, and SHA-224/25 |       |

| Figure 19-5. SHAMD5_ODIGEST_A Register                                                                            |       |

| Figure 19-6. SHAMD5_ODIGEST_B Register                                                                            |       |

| Figure 19-7. SHAMD5_ODIGEST_C Register                                                                            |       |

| Figure 19-8. SHAMD5_ODIGEST_D Register                                                                            |       |

| Figure 19-9. SHAMD5_ODIGEST_E Register                                                                            |       |

| Figure 19-10. SHAMD5_ODIGEST_F Register                                                                           |       |

| Figure 19-11. SHAMD5_ODIGEST_G Register                                                                           |       |

| Figure 19-12. SHAMD5_ODIGEST_H Register                                                                           |       |

| Figure 19-13. SHAMD5_IDIGEST_A Register                                                                           |       |

| Figure 19-14. SHAMD5_IDIGEST_B Register                                                                           |       |

| Figure 19-15. SHAMD5_IDIGEST_C Register                                                                           |       |

| Figure 19-16. SHAMD5_IDIGEST_D Register                                                                           |       |

| Figure 19-17. SHAMD5_IDIGEST_E Register                                                                           |       |

| Figure 19-18. SHAMD5_IDIGEST_F Register                                                                           |       |

| Figure 19-19. SHAMD5_IDIGEST_G Register                                                                           |       |

| Figure 19-20. SHAMD5_IDIGEST_H Register                                                                           |       |

| Figure 19-21. SHAMD5_DIGEST_COUNT Register                                                                        |       |

| Figure 19-22. SHAMD5_MODE Register                                                                                |       |

| Figure 19-23. SHAMD5_LENGTH Register                                                                              |       |

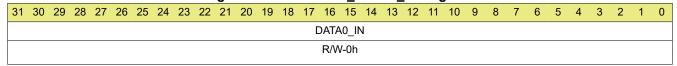

| Figure 19-24. SHAMD5_DATA0_IN Register                                                                            |       |

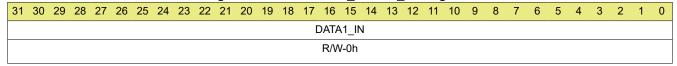

| Figure 19-25. SHAMD5_DATA1_IN Register                                                                            |       |

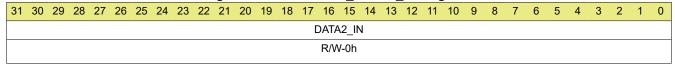

| Figure 19-26. SHAMD5_DATA2_IN Register                                                                            |       |

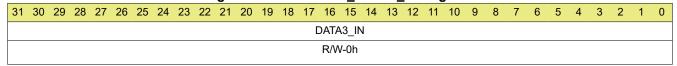

| Figure 19-27. SHAMD5_DATA3_IN Register                                                                            |       |

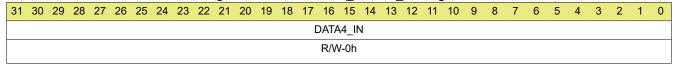

| Figure 19-28. SHAMD5_DATA4_IN Register                                                                            |       |

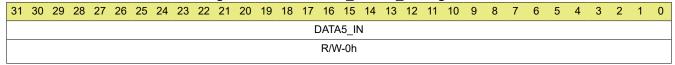

| Figure 19-29. SHAMD5_DATA5_IN Register                                                                            |       |

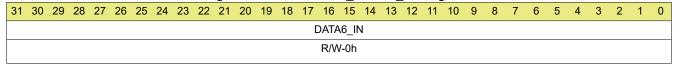

| Figure 19-30. SHAMD5_DATA6_IN Register                                                                            |       |

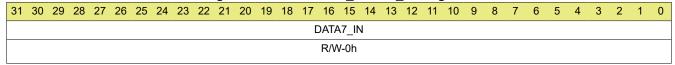

| Figure 19-31. SHAMD5_DATA1_IN Register                                                                            |       |

| Figure 19-32. SHAMD5_DATA8_IN Register                                                                            |       |

| Figure 19-33. SHAMD5_DATA9_IN Register                                                                            |       |

|                                                                                                                   |       |

| Figure 19-35. SHAMD5_DATA11_IN Register                                                                           |       |

| Figure 19-30. SHAMD5_DATA12_IN Register                                                                           |       |

| Figure 19-37. SHAMD5_DATA13_IN Register                                                                           |       |

| Figure 19-36. SHAMD5_DATA14_IN Register                                                                           |       |

| Figure 19-39. SHAMD5_BATATS_IN Register                                                                           |       |

|                                                                                                                   |       |

| Figure 19-41. SHAMD5_IRQSTATUS Register<br>Figure 19-42. SHAMD5_IRQENABLE Register                                |       |

|                                                                                                                   |       |

| Figure 19-43. DTHE_SHA_IM Register<br>Figure 19-44. DTHE SHA RIS Register                                         |       |

|                                                                                                                   |       |

| Figure 19-45. DTHE_SHA_MIS Register<br>Figure 19-46. DTHE_SHA_IC Register                                         |       |

| Figure 19-40. DTRE_SRA_IC Register                                                                                |       |

| · ·                                                                                                               |       |

| Figure 20.3. CRCDIN Register                                                                                      |       |

| Figure 20-3. CRCDIN RegisterFigure 20-4. CRCRSLTPP Register                                                       |       |

| Figure 21-1. FMA Register                                                                                         |       |

| Figure 21-2. FMD Register                                                                                         |       |

| Figure 21-3. FMC Register                                                                                         |       |

| Figure 21-4. FCRIS Register                                                                                       |       |

| 1 19410 E 1 1. 1 O 1 10 1 10 10 10 10 10 10 10 10 10 10 10                                                        | , , , |

| Figure 21-5. FCIM Register                                            |                  |

|-----------------------------------------------------------------------|------------------|

| Figure 21-6. FCMISC Register                                          |                  |

| Figure 21-7. FMC2 Register                                            |                  |

| Figure 21-8. FWBVAL Register                                          |                  |

| Figure 21-9. FWBn Register                                            |                  |

| Figure 21-10. CC323xSF Boot Flow                                      |                  |

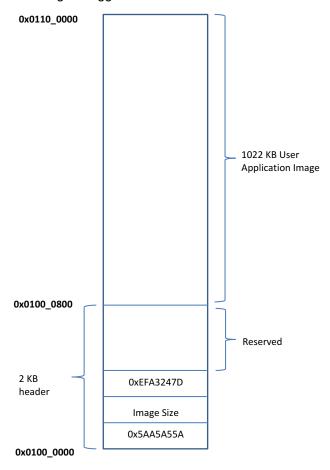

| Figure 21-11. Flash Memory Partition                                  | 786              |

| Figure 21-12. User Application Image Binary Structure on Serial Flash | 787              |

| Figure 21-13. On-Chip Flash Programming and Update                    |                  |

| Figure 21-14. Flash Debug Image Layout                                |                  |

| Figure 24-1. DMA_IMR Register                                         |                  |

| Figure 24-2. DMA_IMS Register                                         |                  |

| Figure 24-3. DMA_IMC Register                                         |                  |

| Figure 24-4. DMA_ICR Register                                         |                  |

| Figure 24-5. DMA_MIS Register                                         |                  |

| Figure 24-6. DMA_RIS Register                                         |                  |

| Figure 24-7. GPTTRIGSEL Register                                      | 805              |

|                                                                       |                  |

| List of Tables                                                        |                  |

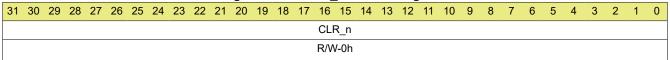

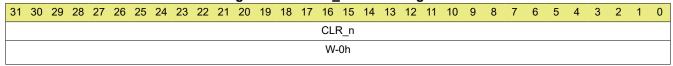

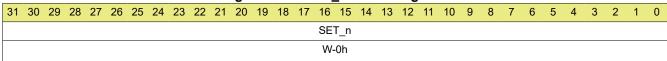

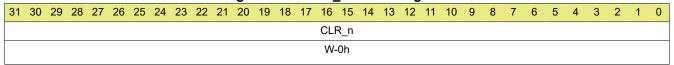

| Table 1-1. Register Bit Accessibility and Initial Condition           |                  |

| Table 2-1. Summary of Processor Mode, Privilege Level, and Stack Use  |                  |

| Table 2-2. Processor Register Map                                     |                  |

| Table 2-3. PSR Register Combinations                                  | 47               |

| Table 2-4. Memory Map                                                 | 49               |

| Table 2-5. SRAM Memory Bit-Banding Regions                            | <mark>50</mark>  |

| Table 2-6. Exception Types                                            | 54               |

| Table 2-7. CC32xx Application Processor Interrupts                    |                  |

| Table 2-8. Faults                                                     | 5 <mark>8</mark> |

| Table 2-9. Fault Status and Fault Address Registers                   | 59               |

| Table 2-10. Cortex®-M4 Instruction Summary                            | 63               |

| Table 3-1. Core Peripheral Register Regions                           | 69               |

| Table 3-2. Peripherals Register Map                                   | 71               |

| Table 3-3. Cortex Registers                                           | 75               |

| Table 3-4. ACTLR Register Field Descriptions                          |                  |

| Table 3-5. STCTRL Register Field Descriptions                         | 7 <mark>8</mark> |

| Table 3-6. STRELOAD Register Field Descriptions.                      | 80               |

| Table 3-7. STCURRENT Register Field Descriptions                      | 81               |

| Table 3-8. EN_0 to EN_6 Register Field Descriptions                   | 8 <mark>2</mark> |

| Table 3-9. DIS_0 to DIS_6 Register Field Descriptions                 | 83               |

| Table 3-10. PEND_0 to PEND_6 Register Field Descriptions              | 84               |

| Table 3-11. UNPEND_0 to UNPEND_6 Register Field Descriptions          |                  |

| Table 3-12. ACTIVE_0 to ACTIVE_6 Register Field Descriptions          |                  |

| Table 3-13. PRI_0 to PRI_49 Register Field Descriptions               |                  |

| Table 3-14. CPUID Register Field Descriptions.                        |                  |

| Table 3-15. INTCTRL Register Field Descriptions                       |                  |

| Table 3-16. VTABLE Register Field Descriptions.                       | 92               |

| Table 3-17. APINT Register Field Descriptions                         |                  |

| Table 3-18. SYSCTRL Register Field Descriptions.                      | 95               |

| Table 3-19. CFGCTRL Register Field Descriptions                       | 9 <mark>6</mark> |

| Table 3-20. SYSPRI1 Register Field Descriptions                       |                  |

| Table 3-21. SYSPRI2 Register Field Descriptions                       |                  |

| Table 3-22. SYSPRI3 Register Field Descriptions                       |                  |

| Table 3-23. SYSHNDCTRL Register Field Descriptions                    |                  |

| Table 3-24. FAULTSTAT Register Field Descriptions.                    |                  |

| Table 3-25. HFAULTSTAT Register Field Descriptions                    |                  |

| Table 3-26. FAULTDDR Register Field Descriptions.                     |                  |

| Table 3-27. SWTRIG Register Field Descriptions                        |                  |

| Table 4-1. DMA Channel Assignment                                     |                  |

| Table 4-2. Channel Control Memory                                     |                  |

| Table 4-3. Individual Control Structure                               | 116              |

| Table 4-4. 8-Bit Data Peripheral Configuration           | 121 |

|----------------------------------------------------------|-----|