# Ecoship Technology and Enviropack Tape and Reel: The Sustainable Solution for Storage and Shipping

Ryan Huang, Franklin Lai, Stanley Chou, Steven Kummerl, June Chang

#### **ABSTRACT**

Today's electronics shipping methods include Tray, Tube, and Tape and Reel. Among these major types, tape and reel is the most widely used method, particularly for high-volume production, due to its high speed, precise placement in automated pick-and-place machines, and ESD protection. As a result, tape and reel has become the preferred method for packaging a wide range of electronics, including ICs, passive components, terminals, modules, bare dies, and heat sinks. However, the traditional tape and reel packing method has some drawbacks, such as underutilized packing density, significant storage space requirements, and frequent changeovers. To support the rapid growth of the semiconductor industry, a more efficient method is needed to pack and ship electronic components to our customer factories.

This technical white paper introduces a groundbreaking, industry-first packing method: multi-row tape and reel. This document discusses how the innovative multi-row design addresses storage and shipping challenges, why it is crucial for the industry, and how to successfully adopt this technology in your factory.

#### **Table of Contents**

| 1 Introduction                                                                                                                                            | 2 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2 Motivation                                                                                                                                              |   |

| 3 Feature                                                                                                                                                 |   |

| 4 Cover Tape Peeling Strength                                                                                                                             |   |

| 5 Electrostatic Charges                                                                                                                                   |   |

| 6 Multi-Row Carrier Tape Design                                                                                                                           |   |

| 7 Device Name Nomenclature                                                                                                                                | 6 |

| 8 What I Need to do on my SMT Equipment?                                                                                                                  |   |

| 9 Conclusion                                                                                                                                              |   |

| 10 Additional Resources                                                                                                                                   |   |

| List of Figures  Figure 1-1. Multiple Row Carrier tape, Ecoship Technology and Enviropack Tape and Reel                                                   | 2 |

| Figure 2-1. Traditional Single Row Method of SOIC 8D Requires Three Boxes to Meet the Same QTY of Multi-Row Figure 6-1. Pin1 Orientation and Sealing Line |   |

| Figure 6-2. SOIC and TSSOP Configuration                                                                                                                  |   |

| Figure 8-1. Non-Shutter (a) and Shutter Options are all Compatible With Multi-Row Tape and Reel (b)                                                       |   |

| List of Tables                                                                                                                                            |   |

| Table 6-1. SOIC and TSSOP Tape and Reel Guideline                                                                                                         | 5 |

| Trademarks                                                                                                                                                |   |

Ecoship<sup>™</sup> and Enviropack<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

Introduction www.ti.com

## 1 Introduction

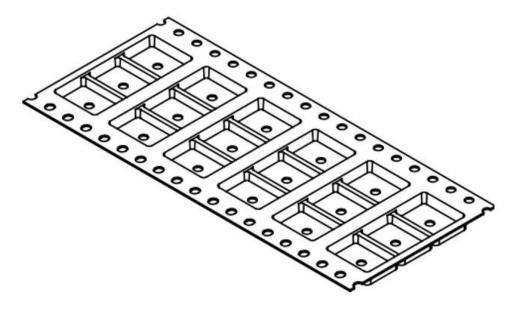

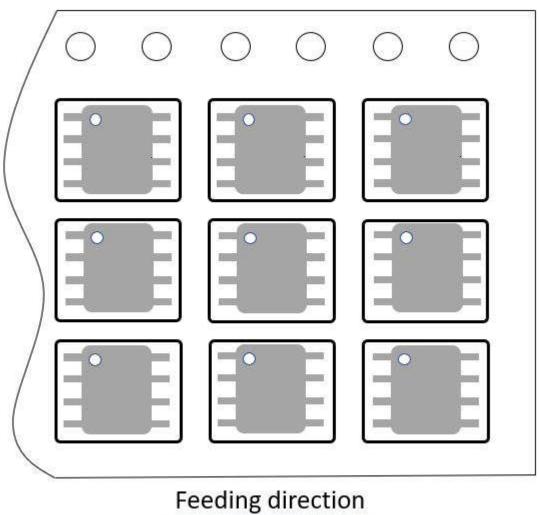

The electronics industry is making a significant investment in surface mount technology (SMT), driven by the potential for cost savings and increased efficiency. However, current carrier tape technology has a limitation - it typically only accommodates one row of components per product, with a standard packing quantity of 500 to 3,000 units in one reel. In a mass production, this means that the reel needs to be replaced up to 10 times a day, resulting in significant productivity losses, increased warehouse space, higher transportation costs, and more industrial waste. To address this challenge, TI's new technology references the design of trays, introducing a matrix-style arrangement to tape and reel that increases packing density by 200%. In this article, TI explores how its Ecoship™ technology and Enviropack™ tape and reel solutions can help SMT assembly houses overcome these challenges. By leveraging this revolutionary packing solution, our customers can mount TI's packages at a lower cost and ultimately alleviate storage and shipping challenges.

Figure 1-1. Multiple Row Carrier tape, Ecoship Technology and Enviropack Tape and Reel

## 2 Motivation

As you continue to navigate the ever-changing landscape of the SMT industry, it is essential that you prioritize cost reduction as a vital component, improve storage strategy, and reduce packing material and costs. This can unlock significant benefits including increased packing and SMT tool utilization through reduced changeover, driving the industry forward and ensuring long-term success.

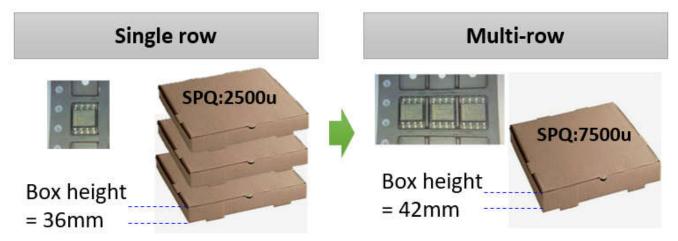

Using the SOIC 8D as an example, the standard packing quantity (SPQ) for traditional single-row tape and reel is 2500 units. The corresponding outer box has a height of 36mm. In contrast, the new multi-row method is able to increases the packing density, allowing the SPQ to be boosted to 7500 units, while the outer box height is only marginally increased to 42mm, as illustrated in Figure 2-1. This results in a significant reduction in box volume of 66% for SOIC 8D. Furthermore, shipping efficiency is greatly improved due to the substantial decrease in total shipping volume.

www.ti.com Feature

Figure 2-1. Traditional Single Row Method of SOIC 8D Requires Three Boxes to Meet the Same QTY of Multi-Row

## 3 Feature

- Multiple rows number available: 3 rows for SOIC 8D and TSSOP 8/14/16PW packages. More rows might be

available in the future.

- Carrier tape width: 24mm for SOIC 8D and TSSOP 8/14/16PW packages.

- Texas Instrument tape and reel specifications are in conformance with the EIA Standard 481 "Taping of Surface-Mount Components for Automatic Placement.

- The reel is made of polystyrene (PS) plastic material and topically coated with antistatic solution.

- The carrier tape is made of standard polycarbonate or polystyrene materials.

- · The cover tape is made of polyester material.

- The cover tape uses pressure sensitive or heat activated adhesive.

## **4 Cover Tape Peeling Strength**

The force required to peel off the cover tape from the carrier tape falls within the range of 0.1 Newton to 1.3 Newton (10 grams to 130 grams) at a peeling speed to 300mm per minute. This complies with the EIA standard

## **5 Electrostatic Charges**

Texas Instrument uses only static dissipative tape-and-reel materials (surface resistivity of  $10^5$  to  $10^{12}\Omega$  to avoid damaging static charges building up during the peeling off of the cover tape prior to pick and place. Texas Instrument ran extensive evaluations on cover tape materials and found that static charge builds up was very low (less than 200 volts) on static dissipative cover tapes. In comparison, commonly used insulative cover tapes had readings consistently in excess of 3000 volts.

## 6 Multi-Row Carrier Tape Design

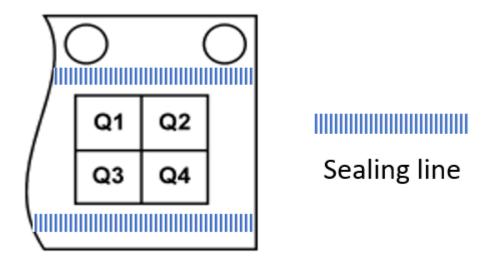

Figure 6-1. Pin1 Orientation and Sealing Line

## SOIC (D) 8

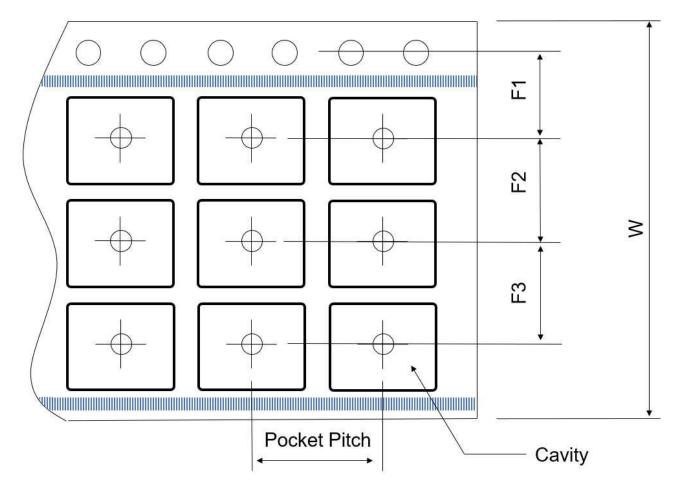

Figure 6-2. SOIC and TSSOP Configuration

Table 6-1. SOIC and TSSOP Tape and Reel Guideline

| Package<br>Group | Pins and<br>Package<br>Designator | Rows | Tape Width<br>W (mm) | Pocket<br>Pitch<br>(mm) | Pin1<br>Quadrant<br>(see Figure<br>6-1) | Units per Reel | Reel Size<br>(Inches) | F1   | F2   | F3   |

|------------------|-----------------------------------|------|----------------------|-------------------------|-----------------------------------------|----------------|-----------------------|------|------|------|

| SOIC             | 8D                                | 3    | 24                   | 8                       | Q1                                      | 7500           | 13                    | 5.25 | 6.25 | 6.25 |

| TSSOP            | 8PW                               | 3    | 24                   | 8                       | Q1                                      | 9000           | 13                    | 5.25 | 6.25 | 6.25 |

| TSSOP            | 14/16PW                           | 3    | 24                   | 8                       | Q1                                      | 9000           | 13                    | 5.05 | 6.45 | 6.45 |

Device Name Nomenclature www.ti.com

## 7 Device Name Nomenclature

TI is introducing a new suffix "-E" to designate our multi-row Ecoship technology and Enviropack tape and reel packing option, distinguishing it from the traditional single-row "-R" suffix. The "E" stands for Ecoship/Enviropack, representing our commitment to eco-friendly and environmentally conscious shipping methods.

- E = Multi-row Tape and Reel (Ecoship technology and Enviropack tape and reel)

- R = Large Tape and Reel

- T = Small Tape and Reel

- J = Jumbo Tape and Reel

- Blank = Tube

## 8 What I Need to do on my SMT Equipment?

The installation of multi-row carrier tape onto an SMT feeder follows the same steps as traditional single-row tape. Here's a step-by-step guide:

- 1. Loading the tape and reel: Load the multi-row tape and reel onto the holder. The reel diameter and width meet standard specifications, making it compatible with mainstream SMT equipment.

- 2. Inserting the tape into the tape guide: Insert the tape into the guide, utilizing the approximately 50cm of dummy tape provided for setup purposes.

- 3. Separating the cover tape from the carrier tape: Similar to traditional single-row tape, thread the cover tape through the slot and secure it into the gear.

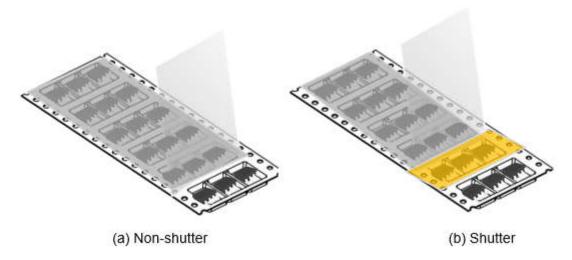

- 4. Index pitch setup: Set the index pitch according to the recommended value per Table 6-1. For example, an 8mm pitch is recommended for SOIC 8D, as illustrated in Figure 8-1. In this setup, the carrier tape is indexed by one column pitch, and the cover tape is peeled off accordingly to expose only one index of units. Most SMT equipment offers Non-shutter and shutter options, both of which are compatible with multi-row tape and reel, providing flexibility in your setup.

- 5. Setting up the pick-up location: Determine the IC center location using the values listed in Table 6-1, which includes vertical pitch (F1, F2, F3) and horizontal pitch (P) information.

Note that the recommended pick-and-place equipment and models for supporting Ecoship technology and Enviropack tape and reel are announced in this TI technical white paper. If you require any immediate support, please contact TI sales team.

Figure 8-1. Non-Shutter (a) and Shutter Options are all Compatible With Multi-Row Tape and Reel (b)

www.ti.com Conclusion

## 9 Conclusion

Through this technology, our customers no longer need to frequently replace material reels during the Surface Mount Technology (SMT) production. This not only saves warehouse space and reduces the generation of industrial waste, but also effectively lowers logistics costs. The aforementioned benefits all contribute to reducing carbon emissions and having a positive environmental impact. For more information, contact local TI sales.

## 10 Additional Resources

• Carrier tape standard: Semiconductor Packing Methodology

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated