# EVM User's Guide: AM261x AM261x LaunchPad User Guide

# Description

The AM261x LaunchPad<sup>™</sup> development kit is a simple and inexpensive hardware evaluation module (EVM) for the Texas Instruments<sup>™</sup> Sitara<sup>™</sup> AM261x series of microcontrollers (MCUs). This EVM provides an easy way to start developing on the AM261x MCUs with on-board emulation for programming and debugging as well as user-controlled buttons and LEDs for a simple user interface.

# **Get Started**

- Order the AM261x LaunchPad Evaluation Board (EVM)

- 2. Order the DP83826 Industrial Ethernet Add-on Board if required for your application

- Download the latest Code Composer Studio<sup>TM</sup> Integrated Development Environment (IDE) and the AM261x MCU PLUS Software Development Kit

# Features

The AM261x LaunchPad has the following features:

- Powered through 5V, 3A USB Type-C input

- PMIC with three buck converters and one LDO

- 2x Ethernet PHY add-on board connectors

- On-board XDS110 debug probe

- 2x independent BoosterPack XL connector sites (80 total pins) for rapid prototyping and use with supported TI BoosterPack hardware

- Three push buttons:

- PORz

- User interrupt

- RESETz

- LEDs for:

- Power status

- User testing

- I2C driven array

- USB2.0 interface

- · CAN connectivity with onboard CAN transceiver

- Dedicated FSI connector

- 2x independent Enhanced Quadrature Encoder Pulse (EQEP) based encoder connectors

- · On-board memory:

- 1x 64Mb, 1.8V NOR OSPI Flash (Macronix)

- 1x 128Mb, 1.8V PSRAM (AP Memory)

- 1 Mb I2C Board ID EEPROM

- 1x memory expansion connector

1

# **1 Evaluation Module Overview**

# **1.1 Introduction**

The LP-AM261 LaunchPad Evaluation Module is a single-board development platform that can be used to evaluate the performance of the AM261x microcontroller. The LaunchPad architecture includes all the necessary power, reset, and clock logic to operate the AM261x device.

The 80-pin AM261x LaunchPad is intended to provide a well-filtered, robust design that is capable of working in most environments. This document provides the hardware details of the AM261x LaunchPad and explains the functions of the on-board peripherals, locations of jumpers and connectors, and configurations of switches and muxes present on the PCB.

### 1.1.1 Preface: Read This First

#### 1.1.1.1 Sitara MCU+ Academy

Texas Instruments offers the *MCU*+ *Academy* as a resource for designing with the MCU+ software and tools on supported devices. The MCU+ Academy features easy-to-use training modules that range from the basics of getting started to advanced development topics.

#### 1.1.1.2 Important Usage Notes

#### Note

The AM261x LaunchPad requires a 5V, 3A power supply to function. A 5V, 3A power supply is not included in the kit and must be ordered separately. The *Belkin USB-C Wall Charger* is known to work with the LaunchPad and supplied type-C cable. For more information on power requirements refer to Section 2.2.

#### Note

The AM261x SoC (U1) on the LaunchPad can reach and exceed temperatures of 55°C during high power consumption use cases as per internal testing. This user guide statement is to alert users to this temperature condition.

Caution Caution Hot surface. Contact may cause burns. Do not touch!

#### Note

External Power Supply or Power Accessory Requirements:

- Nominal output voltage: 5VDC

- Max output current: 3000mA

- Power Delivery

#### Note

TI recommends using an external power supply or accessory which complies with applicable regional safety standards such as (by example) UL, CSA, VDE,CCC,PSE, etc.

# **1.2 Kit Contents**

The Sitara AM261x LaunchPad Development Kit contains the following items:

- LP-AM261 development board

- USB micro-B cable

- USB Type-C cable

The kit does not include:

USB type-C 5V/3A AC/DC supply

• DP83826-EVM-AM2 Ethernet Add-on Board

### **1.3 Device Information**

#### 1.3.1 System Architecture Overview

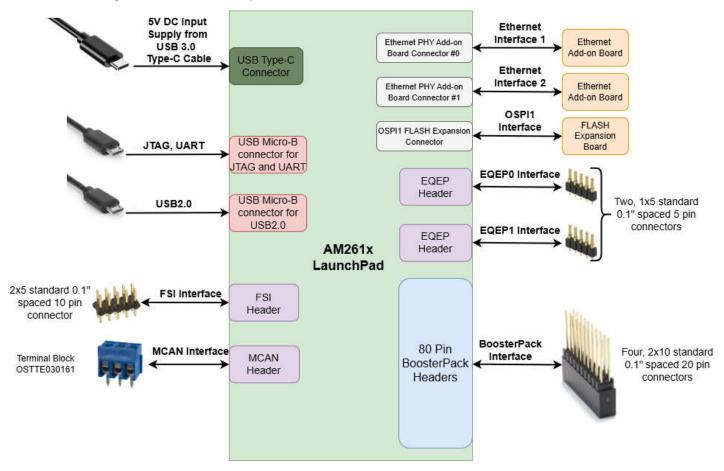

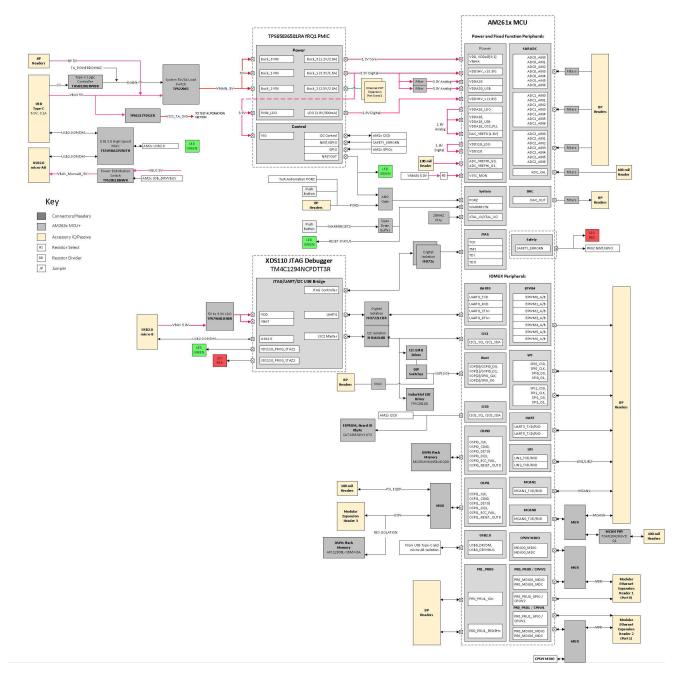

The below image shows the overall top level architecture of the AM261x LaunchPad.

Figure 1-1. System Architecture

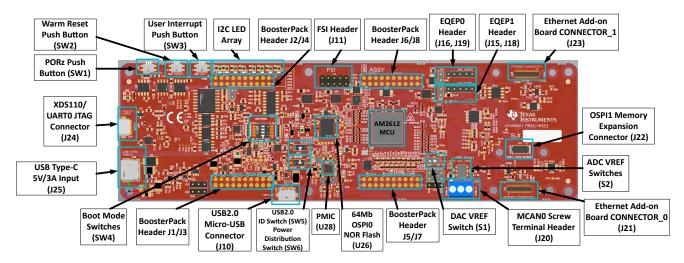

#### 1.3.2 Component Identification

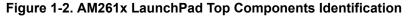

Figure 1-3. AM261x LaunchPad Bottom Components Identification

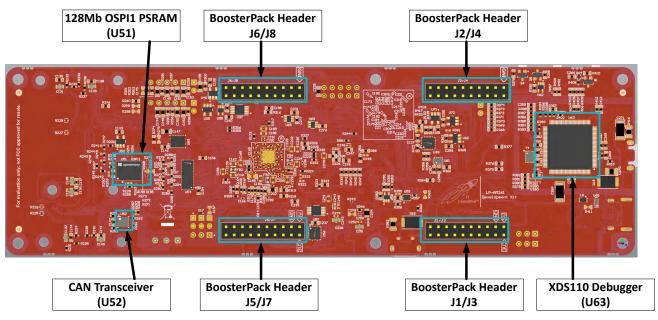

# 1.3.3 Functional Block Diagram

Figure 1-4. AM261x LaunchPad Functional Block Diagram

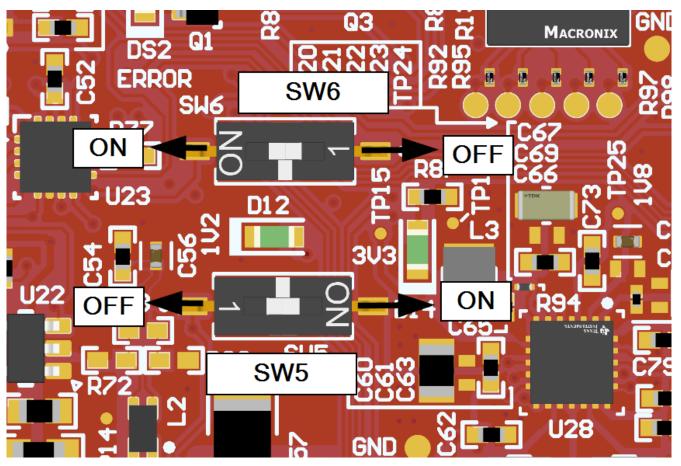

#### 1.3.4 BoosterPacks

The AM261x LaunchPad development kit provides an easy and inexpensive way to develop applications with the AM261x Series microcontroller. BoosterPacks are add-on boards that follow a pin-out standard created by Texas Instruments. The TI and third-party ecosystem of BoosterPacks greatly expands the peripherals and potential applications that you can easily explore with the AM261x LaunchPad. For a detailed look at the pinout of the AM261x LaunchPad BoosterPack headers, refer to Section 2.12.

You can also build your own BoosterPack by following the design guidelines on TI's website. Texas Instruments even helps you promote your BoosterPack to other members of the community. TI offers a variety of avenues for you to reach potential customers with your solutions.

## 1.3.5 Device Information

The AM261x Sitara Arm® Microcontrollers are part of Sitara AM26x real-time MCU families designed to meet the complex real-time processing needs of next generation industrial and automotive embedded products. With scalable Arm® Cortex®-R5F performance and an extensive set of peripherals, AM261x device is designed for a broad range of applications while offering safety features and optimized peripherals for real time control.

Key features and benefits:

- Peripherals supporting system level connectivity such as Gigabit Ethernet, USB, OSPI/QSPI, CAN, UARTs, SPI and GPIOs.

- Granular firewalls managed by Hardware Security Manager (HSM) enable developers to implement stringent security minded system design requirements.

- Up to two R5F cores in cluster with 256KB of shared Tightly Coupled Memory (TCM) per core along with 1.5MB of shared SRAM, greatly reducing the need for external memory.

#### 1.3.5.1 Security

The AM261x LaunchPad features a High Security, Field Securable (HS-FS) device. An HS-FS device has the ability to use a one time programming to convert the device from HS-FS to High Security, Security Enforced (HS-SE) device.

The AM261x device leaves the TI factory in an HS-FS state where customer keys are not programmed and has the following attributes:

- Does not enforce the secure boot process

- M4 JTAG port is closed

- R5 JTAG port is open

- Security Subsystem firewalls are closed

- SoC Firewalls are open

- ROM Boot expects a TI signed binary (encryption is optional)

- TIFS-MCU binary is signed by the TI private key

The One Time Programmable (OTP) keywriter converts the secure device from HS-FS to HS-SE. The OTP keywriter programs customer keys into the device efuses to enforce secure boot and establish a root of trust. The secure boot requires an image to be encrypted (optional) and signed using customer keys, which will be verified by the SoC. A secure device in the HS-SE state has the following attributes:

- M4, R5 JTAG ports are both closed

- Security Subsystems and SoC Firewalls are both closed

- TIFS-MCU and SBL need to be signed with active customer key

# 2 Hardware

## 2.1 Setup

The AM261x LaunchPad setup supports two different configurations. Each configuration enables a different evaluation setup.

Note

When the LaunchPad is used in a high-voltage setup, the user is responsible to confirm that the voltages and isolation requirements are identified and understood prior to energizing the board or simulation. When energized, the LaunchPad or components connected to the LaunchPad cannot be touched.

#### 2.1.1 Standalone Configuration

The standalone configuration is used for most software development use cases that do not require Ethernet.

In this configuration, Code Composer Studio<sup>TM</sup> connects to the LaunchPad by JTAG and enables software development. The on-board XDS110 debug probe enumerates a virtual COM port (VCP) for communication with the AM261x MCU by UART.

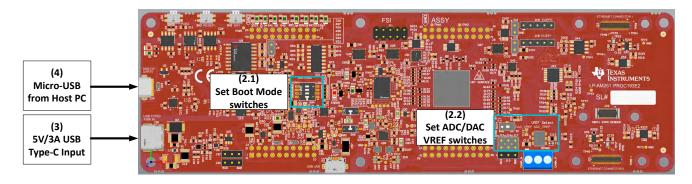

Follow these steps to set up the AM261x LaunchPad in its default configuration:

- 1. Collect the required equipment

- a. AM261x LaunchPad (LP-AM261)

- b. 5V/3A USB Type-C power supply

- c. Micro-USB cable

- 2. Verify that the switch settings are correct on the LaunchPad

- a. Use SW4 to select the desired boot mode (Boot Mode Selection)

- b. Use S1 and S2 to select the desired ADC voltage reference mode (if applicable for the application) (ADC and DAC)

- 3. Connect the 5V/3A USB Type-C power supply to connector J25 of the LaunchPad

- 4. Connect the micro-USB cable to connector J24 of the LaunchPad

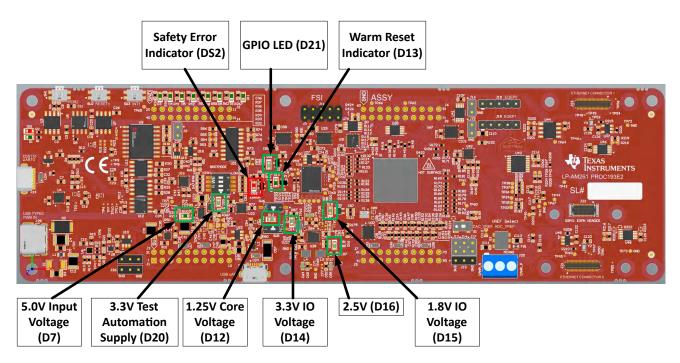

- 5. Verify the power status LEDs (D7, D12, D14, D15, D16) on the LaunchPad are turned on

- 6. The LaunchPad is ready for use. Follow the steps in Software to get started on developing software

Figure 2-1. LP-AM261 Standalone Configuration

#### 2.1.2 Ethernet Application Configuration

This configuration is used for software development use cases that require Ethernet.

In this configuration, Code Composer Studio<sup>TM</sup> connects to the LaunchPad by JTAG and enables software development. The on-board XDS110 debug probe enumerates a virtual COM port (VCP) for communication with the AM261x MCU by UART. Ethernet Add-on Board(s) connect externally via RJ-45 connector cables.

Follow these steps to set up the AM261x LaunchPad in its default configuration:

7

- 1. Collect the required equipment

- a. AM261x LaunchPad (LP-AM261)

- b. 5V/3A USB Type-C power supply

- c. Micro-USB cable

- d. 1-2x DP83826-EVM-AM2 Ethernet Add-on Board(s)

- i. 2x mounting screws per add-on board

- ii. 2x spacers per add-on board

- iii. 2x washers per add-on board

- iv. 2x hex nuts per add-on board

- e. 1-2x RJ-45 cables

- 2. Verify that the switch settings are correct on the LaunchPad

- a. Use SW4 to select the desired boot mode (Boot Mode Selection)

- b. Use S1 and S2 to select the desired ADC voltage reference mode (if applicable for the application) (ADC and DAC)

- 3. Assemble the Ethernet Add-on Board onto the LaunchPad

- a. Refer to Section 2.10.2 for assembly instructions

- 4. Connect the 5V/3A USB Type-C power supply to connector J25 of the LaunchPad

- 5. Connect the micro-USB cable to connector J24 of the LaunchPad

- 6. Verify the power status LEDs (D7, D12, D14, D15, D16) on the LaunchPad are turned on

- 7. The LaunchPad is ready for use. Follow the steps in Software to get started on developing software

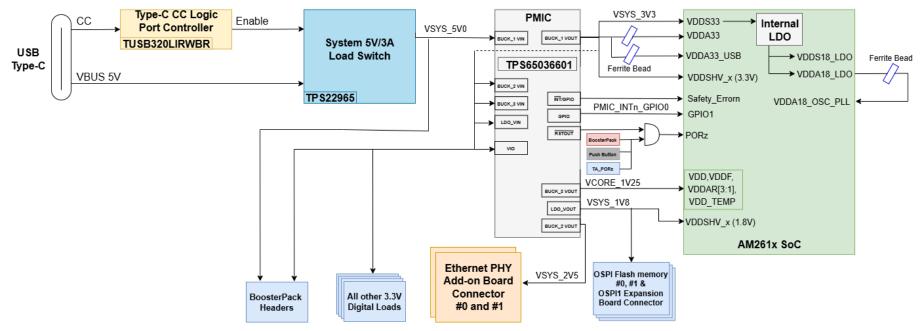

# 2.2 Power Requirements

The AM261x LaunchPad is powered from a 5V, 3A USB type-C input. The following sections describe the power distribution network topology that supply the AM261x LaunchPad, supporting components and the reference voltages.

Power supply solutions that are compatible with the AM261x LaunchPad:

- When using the USB type-C input:

- 5V, 3A power adapter with USB-C receptacle

- 5V, 3A power adapter with captive USB-C cable

- PC USB type-C port that has Power Delivery classification

- Thunderbolt

- Battery behind USB logo

|                                       | USB 2.0<br>High Speeds<br>480 MBit/s | USB 3.0<br>(USB 3.1 Gen 1)<br>Super Speed<br>5 GBit/s | USB 3.1 Gen 2<br>Super Speed Plus<br>10 GBit/s |

|---------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------|

| Does NOT<br>support Power<br>Delivery |                                      | 55~ <b>C</b>                                          | 55-1 <sup>10</sup>                             |

| Does support<br>Power Delivery        |                                      |                                                       |                                                |

| Thunderbolt<br>Does support Po        | wer Delivery                         |                                                       | 10                                             |

### Figure 2-2. USB Type-C Power Delivery Classification

Power supply solutions that are **NOT** compatible with the AM261x LaunchPad:

- When using USB type-C input:

- Any USB adapter cables such as:

- Type-A to type-C

- micro-B to type-C

- DC barrel jack to type-C

- 5V, 1.5A power adapter with USB-C captive cable or receptacle

- PC USB type-C port not capable of 3A

# 2.2.1 Power Input Using USB Type-C Connector

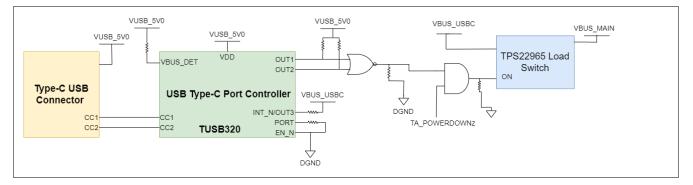

The AM261x LaunchPad is powered through a USB Type-C connection. The USB Type-C source must be capable of providing 3A at 5V and advertises the current sourcing capability through the CC1 and CC2 signals. On the AM261x LaunchPad, the CC1 and CC2 nets from the USB Type-C connector are interfaced to the port controller IC (TUSB320). This device uses the CC pins to determine port attach and detach, cable orientation, role detection, and port control for Type-C current mode. The CC logic detects the Type-C current mode as default, medium, or high.

The Port pin is pulled down to ground with a resistor to configure it as upward facing port (UFP) mode. VBUS detection is implemented to determine a successful attach in UFP mode. The OUT1 and OUT2 pins are connected to a NOR gate. Active low on both the OUT1 and OUT2 pins advertises high current (3A) in the attached state which enables the VUSB\_5V0 power switch to provide the VSYS\_5V0 supply - which powers the PMIC and LDOs.

In UFP mode, the port controller IC constantly presents pull down resistors on both CC pins. The port controller IC also monitors the CC pins for the voltage level corresponding to the Type-C mode current advertisement by the connected DFP. The port controller IC de-bounces the CC pins and waits for VBUS detection before successfully attaching. As a UFP, the port controller device detects and communicates the advertised current level of the DFP to the system through the OUT1 and OUT2 GPIOs.

The AM261x LaunchPad power requirement is 5V at 3A. If the source is not capable of providing the required power, the output at the NOR gate becomes low and disables the VUSB\_5V0 power switch. Therefore, if the power requirement is not met, all power supplies except VCC3V3\_TA remain in the off state. The board gets powered on completely only when the source can provide 5V at 3A.

Figure 2-3. Type-C CC Configuration

| OUT1 | OUT2 | Advertisement                           |

|------|------|-----------------------------------------|

| Н    | н    | Default current in unattached state     |

| Н    | L    | Default current in attached state       |

| L    | н    | Medium current (1.5A) in attached state |

| L    | L    | High current (3.0A) in attached state   |

The AM261x LaunchPad system power solution is PMIC-based. The on-board PMIC supplies the output of its three buck converters and one LDO regulator for each of the power rails. The PMIC generates the supplies required for the AM261x microcontroller and all other EVM peripherals. During the initial stage of the power supply, 5V supplied by the type-C USB connector is used to generate all of the necessary voltages required by the LaunchPad.

| Component | Reference<br>Designator | Function                                                                                                     | Voltage In                                                                                                          | Voltage Out                                                                                                              |

|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| TPS650360 | U28                     | <ul> <li>Core Digital 1.25V</li> <li>System 3.3V</li> <li>System 1.8V</li> <li>Ethernet Port 2.5V</li> </ul> | <ul> <li>Buck_1 VIN - 5.0V</li> <li>Buck_2 VIN - 5.0V</li> <li>LDO VIN - 3.3V</li> <li>Buck_3 VIN - 5.0V</li> </ul> | <ul> <li>Buck_1 VOUT - 3.3V</li> <li>Buck_2 VOUT - 2.5V</li> <li>LDO VOUT - 1.8V</li> <li>Buck_3 VOUT - 1.25V</li> </ul> |

#### Table 2-2. Voltage Rail Generation

#### 2.2.2 Power Tree

Figure 2-4. Power Tree Diagram of AM261x LaunchPad

# 2.2.3 Power Status LEDs

Multiple power-indication LEDs are provided onboard to indicate to users the output status of major supplies. The LEDs indicate power across various domains.

| Name | Default Status | Operation     | Function                                                  |

|------|----------------|---------------|-----------------------------------------------------------|

| D7   | ON             | VSYS_5V0      | Power indicator for supply 5V voltage                     |

| D14  | ON             | VSYS_3V3      | Power indicator for generated 3.3V voltage                |

| D16  | ON             | VSYS_2V5      | Power indicator for generated 2.5V voltage                |

| D12  | ON             | VDD_1V25      | Power indicator for generated<br>1.25V power-good voltage |

| D15  | ON             | VSYS_1V8      | Power indicator for generated 1.8V voltage                |

| D13  | OFF            | WARMRSTN      | Power indication for WARMRSTN                             |

| DS2  | OFF            | SAFETY_ERROR  | Power error indication for<br>SAFETY_ERROR                |

| D1   | OFF            | XDS_PROGSTAZ1 | LED will glow after micro-B connection is made            |

| DS1  | OFF            | XDS_PROGSTAZ2 | LED will glow to indicate communication over JTAG         |

Table 2-3. Power Status LEDs

**Note** DS2 LED that corresponds to SAFETY\_ERROR is always ON.

Figure 2-5. Power Status LEDs

# 2.3 Header Information

The AM261x LaunchPad can be interfaced with external hardware through various on-board headers. These headers provide access to a number of pins on the AM261x device and other signals found on the LP-AM261 board.

### 2.3.1 OSPI Expansion Connector

The LP-AM261 has a 30-pin high density connector for connecting an external OSPI memory to interface with the OSPI1 peripheral on the AM261x MCU. The pinout is detailed in Table 2-4 below:

| EVM Connection   | Pin | Pin | EVM Connection |

|------------------|-----|-----|----------------|

| GND              | 1   | 2   | VSYS_1V8       |

| VSYS_1V8         | 3   | 4   | GND            |

| OSPI1_RESET_OUT0 | 5   | 6   | OSPI1_ECC_FAIL |

| OSPI1_CSn0       | 7   | 8   | OSPI1_CSn1     |

| GND              | 9   | 10  | OSPI1_CLK      |

| GND              | 11  | 12  | OSPI1_DQS      |

| GND              | 13  | 14  | OSPI1_D0       |

| OSPI1_D1         | 15  | 16  | OSPI1_D2       |

| OSPI1_D3         | 17  | 18  | GND            |

| OSPI1_D4         | 19  | 20  | OSPI1_D5       |

| OSPI1_D6         | 21  | 22  | OSPI1_D7       |

| GND              | 23  | 24  | -              |

| -                | 25  | 26  | -              |

| -                | 27  | 28  | -              |

| -                | 29  | 30  | -              |

#### Table 2-4. OSPI Expansion Connector (J22)

For more information, see Section 2.10.1.1.

#### 2.3.2 ADC/DAC External VREF Headers

The AM261x LaunchPad has headers for connecting external voltage references to the ADC and DAC peripherals. The header pinouts are detailed in the tables below:

#### Table 2-5. DAC External VREF Header (J12)

| Pin | EVM Connection |  |  |  |  |

|-----|----------------|--|--|--|--|

| 1   | DAC_EXT_VREF   |  |  |  |  |

| 2   | GND            |  |  |  |  |

#### Table 2-6. ADC External VREF Header (J17)

| Pin | EVM Connection |  |  |  |

|-----|----------------|--|--|--|

| 1   | ADC_EXT_VREF   |  |  |  |

| 2   | GND            |  |  |  |

#### Table 2-7. ADC Calibration Header (J14)

| Pin | EVM Connection |

|-----|----------------|

| 1   | ADC_CAL0       |

Table 2-7. ADC Calibration Header (J14) (continued)

| Pin | EVM Connection |

|-----|----------------|

| 2   | GND            |

For more information, see Section 2.10.11.

#### 2.3.3 Ethernet Add-on Board Connectors

The LP-AM261 has **two** 48-pin high-density shielded connectors (DF40GB-48DP-0.4V(58)) for connecting supported TI Ethernet Add-on Boards, such as the DP83826-EVM-AM2.

The PR0\_PRU0/RGMII2 instance of the AM261x is routed to **Ethernet add-on board Connector 0 (J21)**. The PR0\_PRU1/RGMII1 instance of the AM261x is routed to **Ethernet add-on Board Connector 1 (J23)**. The connector pinout is standard across TI EVMs that support Ethernet add-on boards, and is detailed in Table 2-8 below.

| Pin # | AM261x EVM<br>Connection           | Ethernet Add-on<br>Board Standard | Description                   | Description                      | Ethernet Add-on<br>Board Standard | AM261x EVM<br>Connection          | Pin # |

|-------|------------------------------------|-----------------------------------|-------------------------------|----------------------------------|-----------------------------------|-----------------------------------|-------|

| 1     | GND                                | GND                               | Ground                        | PMIC External<br>Voltage Monitor | EXT_VMON                          | EXT[2:1]_VMON2                    | 2     |

| 3     | RGMII[2:1]_TXC                     | TX_CLK                            | Transmit Clock                | 2.5V supply                      | VDD_2V5                           | VSYS_2V5                          | 4     |

| 5     | GND                                | GND                               | Ground                        | 2.5V supply                      | VDD_2V5                           | VSYS_2V5                          | 6     |

| 7     | RGMII[2:1]_TD0                     | TX_D0                             | Transmit Data 0               | Ground                           | GND                               | GND                               | 8     |

| 9     | RGMII[2:1]_TD1                     | TX_D1                             | Transmit Data 1               | Interrupt To<br>Ethernet PHY     | PWDN/INTn                         | RGMII[2:1]_INTn                   | 10    |

| 11    | RGMII[2:1]_TD2                     | TX_D2                             | Transmit Data 2               | Reset input to<br>Ethernet PHY   | RESETn                            | RGMII[2:1]_RES<br>ETn             | 12    |

| 13    | RGMII[2:1]_TD3                     | TX_D3                             | Transmit Data 3               | Collision Detected               | COL                               | MII[2:1]_COL                      | 14    |

| 15    | GND                                | GND                               | Ground                        | Ground                           | GND                               | GND                               | 16    |

| 17    | GND                                | GND                               | Ground                        | Ground                           | GND                               | GND                               | 18    |

| 19    | RGMII[2:1]_RXC                     | RX_CLK                            | Receive Clock                 | MDIO Clock                       | MDIO_MDC                          | MDIO_CLOCK_E<br>TH[2:1]           | 20    |

| 21    | GND                                | GND                               | Ground                        | MDIO Data                        | MDIO_MDIO                         | MDIO_DATA_ET<br>H[2:1]            | 22    |

| 23    | RGMII[2:1]_RD0                     | RX_D0                             | Receive Data 0                | Ground                           | GND                               | GND                               | 24    |

| 25    | RGMII[2:1]_RD1                     | RX_D1                             | Receive Data 1                | <br>Inhibit                      | INH                               | GND                               | 26    |

| 27    | RGMII[2:1]_RD2                     | RX_D2                             | Receive Data 2                | PRUx Reference<br>Clock          | REF_CLK                           | OSC_CLK_OUT[<br>2:1] / TP47       | 28    |

| 29    | RGMII[2:1]_RD3                     | RX_D3                             | Receive Data 3                | Carrier Sense                    | CRS                               | RMII[2:1]_CRS_D<br>V/MII[2:1]_CRS | 30    |

| 31    | GND                                | GND                               | Ground                        | Ground                           | GND                               | GND                               | 32    |

| 33    | GND                                | GND                               | Ground                        | <br>Ground                       | GND                               | GND                               | 34    |

| 35    | RGMII[2:1]_TX_C<br>TL              | TXEN                              | Transmit Enable               | Board Connection<br>Detect       | BRD_CONN_DE<br>T                  | VSYS_3V3                          | 36    |

| 37    | ETH[2:1]_EEPRO<br>M_A2             | EEPROM_A2                         | EEPROM I2C<br>Address bit [2] | IEEE 1588 SFD                    | 1588_SFD                          | TP51                              | 38    |

| 39    | RMII[2:1]_RX_ER<br>/MII[2:1]_RX_ER | RX_ER                             | Receive Data<br>Error         | I2C Clock                        | I2C_SCL                           | I2C0_SCL                          | 40    |

| 41    | GND                                | GND                               | Ground                        | I2C Data                         | I2C_SDA                           | I2C0_SDA                          | 42    |

| 43    | RGMII[2:1]_RXLI<br>NK              | RX_LINK                           | Receive Indicator             | IO Voltage Supply                | VDDIO                             | VSYS_3V3                          | 44    |

| 45    | RGMII[2:1]_RX_C<br>TL              | RXDV                              | Receive Data<br>Valid         | IO Voltage Supply                | VDDIO                             | VSYS_3V3                          | 46    |

#### Table 2-8. DF40GB Header Pinout (J21 and J23)

#### Table 2-8. DF40GB Header Pinout (J21 and J23) (continued)

| Pin # | AM261x EVM             | Ethernet Add-on |                               | <b>`</b>        | Ethernet Add-on | -          | Pin # |

|-------|------------------------|-----------------|-------------------------------|-----------------|-----------------|------------|-------|

|       | Connection             | Board Standard  |                               |                 | Board Standard  | Connection |       |

| 47    | ETH[2:1]_EEPRO<br>M_A0 | EEPROM_A0       | EEPROM I2C<br>Address bit [0] | Audio Bit Clock | GPIO_2/CLKOUT   | -          | 48    |

For more information, see Section 2.10.2.

#### 2.3.4 FSI Header

The LP-AM261 has a 10-pin Fast Serial Interface (FSI) header for interfacing with the AM261x FSI peripheral. The pinout is shown in Table 2-9 below.

#### Table 2-9. FSI Header (J11) Pinout

| EVM Connection | Pin | Pin | EVM Connection |

|----------------|-----|-----|----------------|

| FSIRX0_CLK     | 1   | 2   | FSITX0_CLK     |

| GND            | 3   | 4   | GND            |

| FSIRX0_D0      | 5   | 6   | FSITX0_D0      |

| FSIRX0_D1      | 7   | 8   | FSITX0_D1      |

| GND            | 9   | 10  | VSYS_3V3       |

For more information on the FSI implementation, see Section 2.10.7.

#### 2.3.5 EQEP Headers

The LP-AM261 terminates the EQEP0 and EQEP1 peripheral signals to a set of breakout headers for use with external encoder hardware.

| Pin   | EVM Connection |  |

|-------|----------------|--|

| J19.1 | EQEP0_A        |  |

| J19.2 | EQEP0_B        |  |

| J19.3 | EQEP0_INDEX    |  |

| J19.4 | VSYS_5V0       |  |

| J19.5 | GND            |  |

| J16.1 | EQEP0_STROBE   |  |

| J16.2 | GND            |  |

|       |                |  |

#### Table 2-11. EQEP1 Headers - J18 and J15

| Pin   | EVM Connection |

|-------|----------------|

| J18.1 | EQEP1_A        |

| J18.2 | EQEP1_B        |

| J18.3 | EQEP1_INDEX    |

| J18.4 | VSYS_5V0       |

| J18.5 | GND            |

| J15.1 | EQEP1_STROBE   |

| J15.2 | GND            |

For more information on EQEP, see Section 2.10.12.

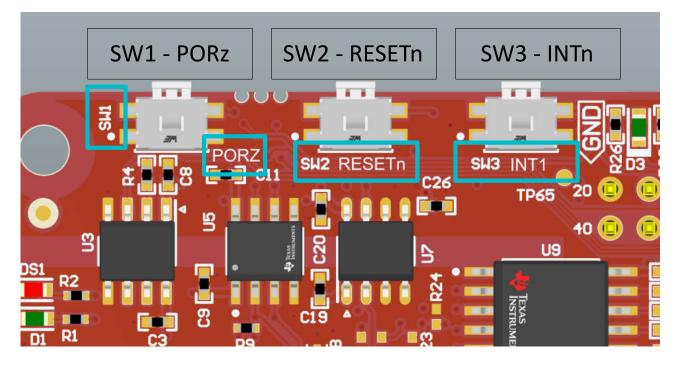

### 2.4 Push Buttons

The LaunchPad supports multiple user push buttons that provide reset inputs and user interrupts to the AM261x SoC.

## Figure 2-6. Push Buttons

#### Table 2-12 lists the push buttons that are placed on the top side of the AM261x LaunchPad.

| Table 2-12. LaunchPad Push Buttons |        |                       |  |

|------------------------------------|--------|-----------------------|--|

| Push Button Signal Function        |        |                       |  |

| SW1                                | PORz   | SoC PORz reset input  |  |

| SW2                                | RESETz | SoC warm reset input  |  |

| SW3                                | INT1   | User Interrupt Signal |  |

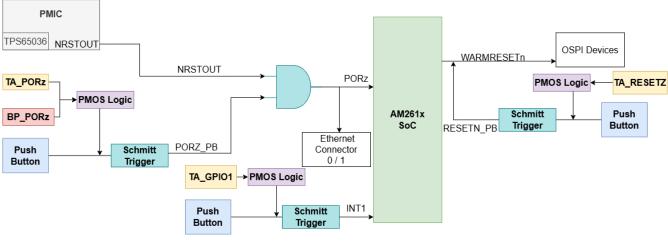

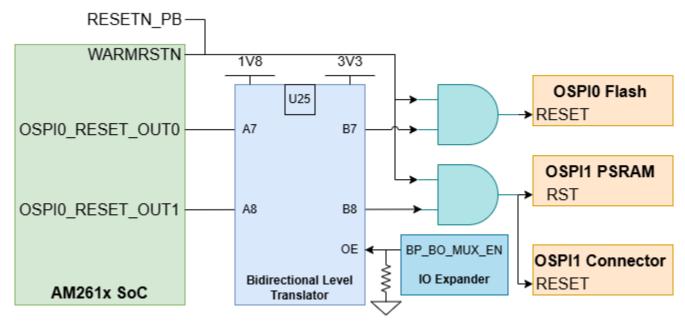

# 2.5 Reset

Figure 2-7 shows the reset architecture of the AM261x LaunchPad

Figure 2-7. Reset Architecture

The AM261x LaunchPad has the following resets:

- PORz (Power On Reset)

- WARMRESETn (Warm Reset)

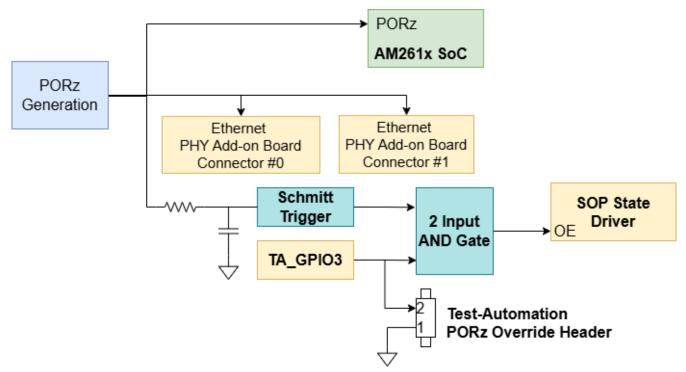

Figure 2-8. PORZ Reset Signal Tree

# PORz

The PORz signal is driven by a 2-input AND gate that generates a power on reset for the MAIN domain when:

- The PMIC's (TPS650360) NRSTOUT is driven low

- The user push button (SW1) is pressed.

- A P-Channel MOSFET gate's signal is logic LOW which causes V<sub>GS</sub> of the PMOS to be less than zero. The PORz signal connects to the PMOS drain which is tied directly to ground. The signals that can create the logic LOW input to the PMOS gate are:

- TA\_PORZ output from the Test Automation header

- BP\_PORZ output from either of the BoosterPack sites.

The PORz signal is tied to:

- AM261x SoC PORz input

- Both Ethernet add-on board connector reset logic

- Boot mode State Driver (U61) output enable input

- There is an RC filter to create a 1ms delay from GND to 3.0V such that the SOP State Driver's output enable input is low longer than the required SOP hold time following a PORz de-assertion.

### WARMRESETn

The WARMRESETn signal creates a warm reset to the MAIN domain when:

• The user push button (SW2) is pressed.

The WARMRESETn signal is tied to:

- AM261x SoC WARMRESETN output

- RESETN\_PB signal that is created from push button + PMOS logic

- OSPI0 and OSPI1 device reset logic

#### Note

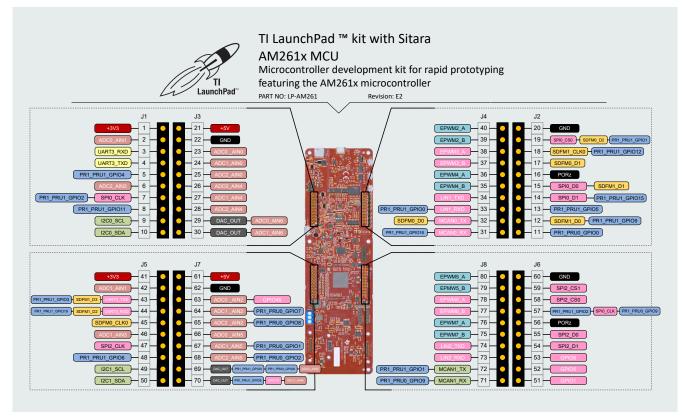

OSPI0\_RESET\_OUT0 is pinmuxed from GPIO61, which has a known issue associated with the AM261x boot ROM. At boot, the ROM code sets GPIO61 to OSPI0\_RESET\_OUT0 and drives the pin low to reset an external flash device. However, due to an error in the OSPI controller configuration, the pin does not drive high once the flash device has been reset, thus holding the flash device in reset and preventing proper boot. The bidirectional level translator (U25) is disabled by default through a pull resistor connected to the Output Enable pin. This prevents the OSPI0\_RESET\_OUT0 (on GPIO61) from pulling the input to the AND gate low before the device boots from the OSPI0 flash. The OSPI0\_RESET\_OUT0 net is pulled high at the AND gate. Once the device boots, OSPI0\_RESET\_OUT0 can be configured in software as an OSPI reset, and the level translator (U25) can be enabled from the I2C-controlled IO expander (U23). For more information on this boot ROM issue, see the AM261x Errata Document.

### INTn

The AM261x LaunchPad also has an external interrupt to the SoC , INT1, that occurs when:

• The user push button (SW3) is pressed

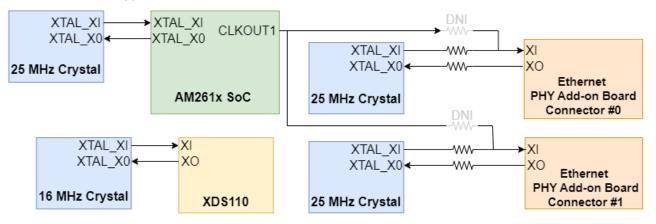

# 2.6 Clock

The AM261x SoC requires a 25MHz clock input for XTAL\_XI. The AM261x LaunchPad uses a 25MHz crystal for the SoC clock source. The LaunchPad also has two 25MHz Crystals onboard for the Ethernet PHY clocking which can be connected to the ethernet port connectors on the board using ethernet add-on boards. The SoC clock signal output CLKOUT1 can be used as a clock source for an Ethernet PHY on an attached Ethernet add-on board. The resistors (R211 & R214) must be removed from the traces connecting the 25MHz Crystals to Ethernet Connector 0 and Ethernet Connector 1. Mount the appropriate resistors (R212 & R213) for CLKOUT1 to be routed to both of the Ethernet add-on board connectors to connect the CLKOUT1 net to the XI pin of the Ethernet PHYs on the add-on boards.

The LaunchPad also has a on board crystal (Y4) of frequency 16MHz which is clock source for the XDS110 for UART-USB JTAG support.

Figure 2-10. AM261x LaunchPad Clock Tree

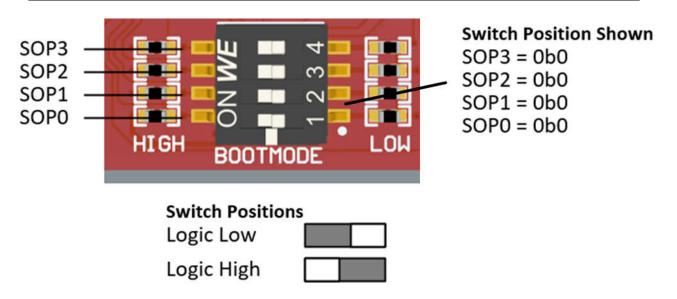

# 2.7 Boot Mode Selection

The boot mode for the AM261x is selected by a DIP (Dual In-Line Package) switch (SW4) or the test automation header. The test automation header uses an I2C expansion buffer to drive the boot mode when PORz is toggled. The supported boot modes are shown in Table 2-13. The DIP Switch configurations for each boot mode are shown in Table 2-14.

**Note** The Boot Mode DIP Switch Positions on the LP-AM261 are the **inverse** of the SOPx settings. For example, if a boot mode setting calls for SOP3=0, then SW4.4=1.

# Figure 2-11. Boot mode DIP Switch Positions - LP AM261x E2 SW1 SOP Switches

| Boot Mode or Peripheral          | Boot Media or Host | ROM Activity / Notes                                                                                                                                                                           |

|----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSPI-OSPI (4S), 50MHz, SDR, 0x6B | Flash Memory       | ROM configures OSPI controller in OSPI 4S<br>mode and downloads image from external<br>flash, supports UART fallback boot mode if<br>any failures                                              |

| UART, XMODEM, 115200bps          | External Host      | ROM configures UART0 with baud rate of<br>115200 bps and downloads image from<br>external PC terminal using x-modem protocol                                                                   |

| OSPI-OSPI (1S), 50MHz, SDR, 0x0B | Flash Memory       | ROM configures OSPI controller in OSPI 1S<br>mode and downloads image from external<br>flash, supports UART fallback boot mode if<br>any failures                                              |

| OSPI (8S), SDR, 33 MHz, 0x8B     | Flash Memory       | ROM configures OSPI controller in 8S mode<br>and downloads image from external flash,<br>supports UART fallback boot mode if any<br>failures                                                   |

| DevBoot                          | N/A                | To support SBL development, R5-will come<br>up with ROM eclipsed, PLLs are initialized,<br>No L2, TCMA and TCMB PBIST are<br>performed, No L2 and TCM memInit.<br>Supported only on FS devices |

#### Table 2-13. Supported Boot Modes

|                             | Table 2-13. Supported Boot Modes (continued) |                                                                                                                                                                                                                                                                |  |  |  |

|-----------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Boot Mode or Peripheral     | Boot Media or Host                           | ROM Activity / Notes                                                                                                                                                                                                                                           |  |  |  |

| xSPI (1S->8D), 20 MHz, SFDP | Flash Memory, External Host                  | ROM configures OSPI controller in xSPI 8D<br>mode, Reads SFDP table for read command<br>and downloads image from external flash,<br>Flashes with SFDP are of JEDEC standard<br>Rev D only supported. In case of any failure it<br>falls back to UART boot mode |  |  |  |

| USB DFU                     | External Host                                | ROM configures USB controller to work in<br>device mode and download the image into<br>L2 memory to process. In case of any failure<br>it falls back to UART boot mode. Supports<br>USB 2.0 device mode at High-Speed (HS,<br>480 Mbps)                        |  |  |  |

#### Table 2-14. Boot Mode Selection

| Boot Mode                        | AM261x SOP[3:0] | SW4.4 (SOP3<br>Inverse) | SW4.3 (SOP2<br>Inverse) | SW4.2 (SOP1<br>Inverse) | SW4.1 (SOP0<br>Inverse) |

|----------------------------------|-----------------|-------------------------|-------------------------|-------------------------|-------------------------|

| OSPI-OSPI (4S), 50MHz, SDR, 0x6B | 0000            | 1                       | 1                       | 1                       | 1                       |

| UART, XMODEM, 115200bps          | 0001            | 1                       | 1                       | 1                       | 0                       |

| OSPI-OSPI (1S), 50MHz, SDR, 0x0B | 0010            | 1                       | 1                       | 0                       | 1                       |

| OSPI (8S), SDR, 33 MHz, 0x8B     | 0011            | 1                       | 1                       | 0                       | 0                       |

| DevBoot                          | 1011            | 0                       | 1                       | 0                       | 0                       |

| xSPI (1S->8D), 20 MHz, SFDP      | 1100            | 0                       | 0                       | 1                       | 1                       |

| USB DFU                          | 1110            | 0                       | 0                       | 0                       | 1                       |

# 2.8 GPIO Mapping

| GPIO Description | GPIO    | Functionality | Net Name             | Active<br>Status |

|------------------|---------|---------------|----------------------|------------------|

| GPIO LED         | GPIO84  | GPIO          | AM261_LED_GPIO84     | LOW              |

| Interrupt To SoC | GPIO124 | Interrupt     | AM261_INT_PB_GPIO124 | LOW              |

## Table 2-15. GPIO Mapping Table

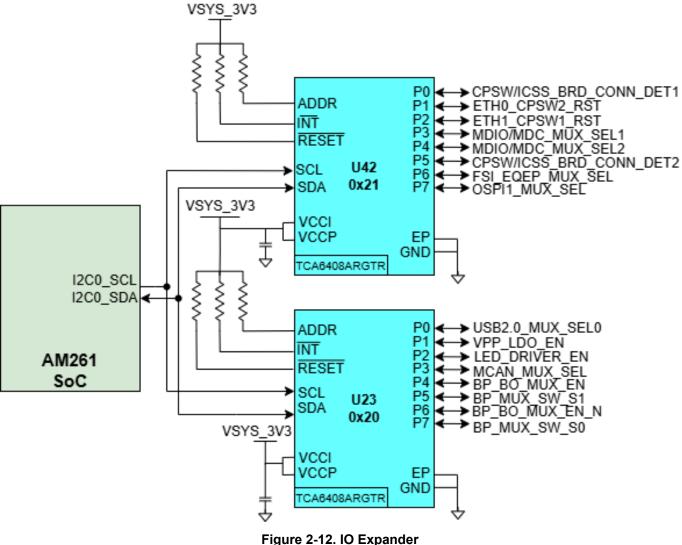

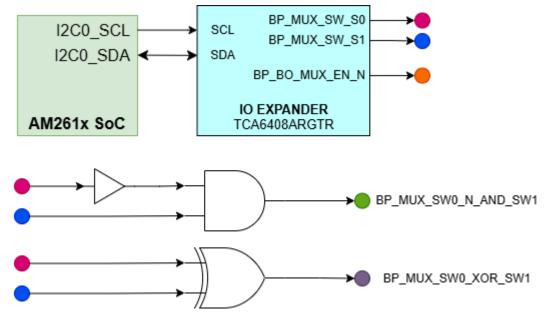

# 2.9 IO Expander

The AM261x LaunchPad has two TCA6408ARGTR IO Expanders that provide general-purpose I/O expansion and bidirectional voltage translation for processors through I2C communication.

The TCA6408A consists of one 8-bit Configuration (input or output selection), Input, Output, and Polarity Inversion (active high) Register. At power on, the I/Os are configured as inputs. The system controller can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding Input or Output Register. The polarity of the Input Port Register can be inverted with the Polarity Inversion Register. All registers can be read by the system controller. The AM261x MCU communicates with the IO Expander through the I2C0 bus. The signals coming out of the IO Expander are shown in Figure 2-12. Refer to the TCA6408ARGTR Data sheet for the programming guide for TCA6408ARGTR.

#### Table 2-16. IO Expander 1 GPIO Mapping (U42)

| IO# | Net Name                | GPIO Description                     | Active Status |

|-----|-------------------------|--------------------------------------|---------------|

| P0  | CPSW/ICSS_BRD_CONN_DET1 | Ethernet Connector 0 board detection | HIGH          |

| P1  | ETH0_CPSW2_RST          | Ethernet Connector 0 reset           | LOW           |

| P2  | ETH1_CPSW1_RST          | Ethernet Connector 1 reset           | LOW           |

| P3  | MDIO/MDC_MUX_SEL1       | MDIO/MDC mux select 1                | PREFERABLE    |

| P4  | MDIO/MDC_MUX_SEL2       | MDIO/MDC mux select 2                | PREFERABLE    |

| P5  | CPSW/ICSS_BRD_CONN_DET2 | Ethernet Connector 1 board detection | HIGH          |

| P6  | FSI_EQEP_MUX_SEL        | FSI/EQEP mux select                  | PREFERABLE    |

| P7  | OSPI1_MUX_SEL           | OSPI1 mux select                     | PREFERABLE    |

# Table 2-17. IO Expander 2 GPIO Mapping (U23)

| IO# | Net Name        | GPIO Description                                                      | Active Status |

|-----|-----------------|-----------------------------------------------------------------------|---------------|

| P0  | USB2.0_MUX_SEL0 | USB mux select                                                        | PREFERABLE    |

| P1  | VPP_LDO_EN      | 1.7V LDO enable                                                       | HIGH          |

| P2  | LED_DRIVER_EN   | LED driver enable                                                     | LOW           |

| P3  | MCAN_MUX_SEL    | MCAN mux select                                                       | PREFERABLE    |

| P4  | BP_BO_MUX_EN    | EPWM bidirectional level translator enable                            | HIGH          |

| P5  | BP_MUX_SW_S1    | Input 1 to XOR gate controlling alternate<br>boosterpack function mux | PREFERABLE    |

| P6  | BP_BO_MUX_EN_N  | Alternate boosterpack function mux output enable                      | LOW           |

| P7  | BP_MUX_SW_S0    | Input 0 to XOR gate controlling alternate<br>boosterpack function mux | PREFERABLE    |

# 2.10 Interfaces

2.10.1 Memory Interfaces 2.10.1.1 OSPI

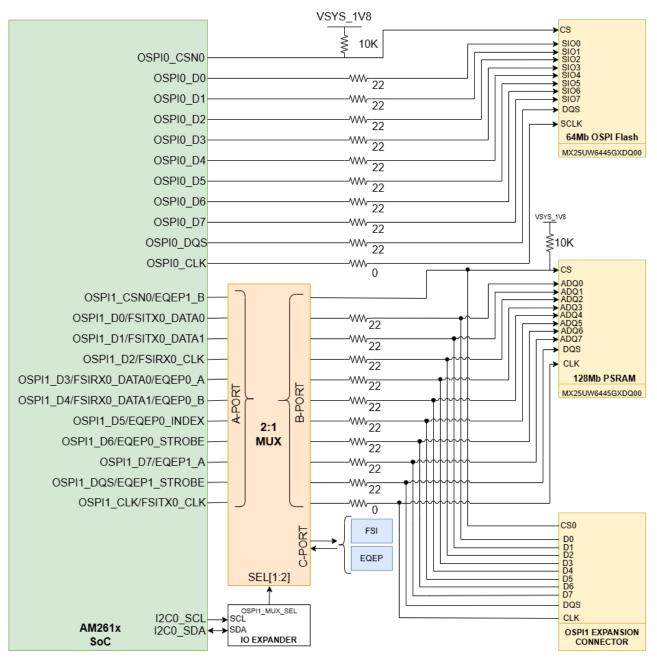

### **OSPI Flash**

The LP-AM261 has a 64Mb, 1.8V OSPI flash memory device (MX25UW6445GXDQ00) connected to the OSPI0 interface of the AM261x MCU. The OSPI flash device is powered by the 1.8V LDO output from the PMIC. The AM261x can boot from binary images flashed to this memory device connected to OSPI0.

**Note** There is a known limitation with the OSPI0 flash reset with a workaround implemented on the LP-AM261. For more details, see Section 6.3.

#### **OSPI PSRAM**

The LP-AM261 has a 128Mb, 1.8V PSRAM memory device (APS12808L-OBMX-BA) connected to the OSPI1 interface of the AM261x MCU. The OSPI PSRAM is powered by the 1.8V LDO output from the PMIC. The AM261x can utilize this interface for external memory.

**Note** AM261x cannot boot from the PSRAM device connected to OSPI1.

#### **OSPI Expansion Connector**

The AM261x OSPI1 signal traces have the option to be routed to a 30-pin high-density connector for connecting compatible OSPI memory add-on boards. Table 2-18 details the resistor modifications that need to be made in order to enable the OSPI1 routing path to the expansion connector.

| LP-AM261 Net      | DNI Resistor | Populate Resistor |

|-------------------|--------------|-------------------|

| EX_OSPI1_CLK      | R242         | R245              |

| EX_OSPI1_D0       | R291         | R286              |

| EX_OSPI1_D1       | R282         | R276              |

| EX_OSPI1_D2       | R294         | R289              |

| EX_OSPI1_D3       | R283         | R277              |

| EX_OSPI1_D4       | R292         | R287              |

| EX_OSPI1_D5       | R284         | R278              |

| EX_OSPI1_D6       | R295         | R290              |

| EX_OSPI1_D7       | R285         | R279              |

| EX_OSPI1_DQS      | R293         | R288              |

| EX_OSPI1_CSn0     | R248         | R243              |

| EX_OSPI1_ECC_FAIL | R249         | R244              |

| EX_OSPI1_RSTn     | R247         | R241              |

#### Table 2-18. OSPI Expansion Connector Resistor Mods

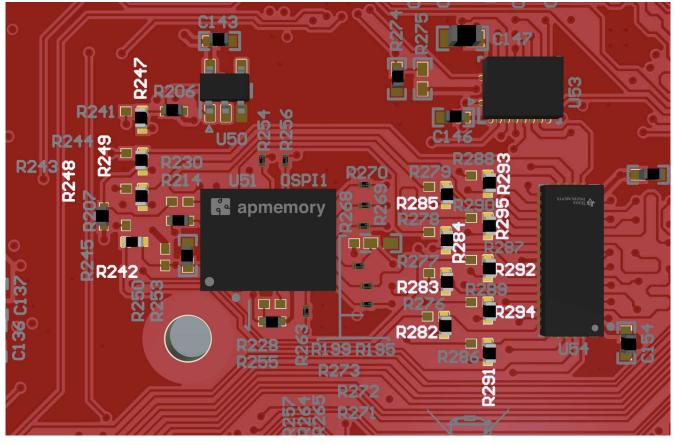

Figure 2-13. OSPI1 Expansion Connector - Depopulate Resistors

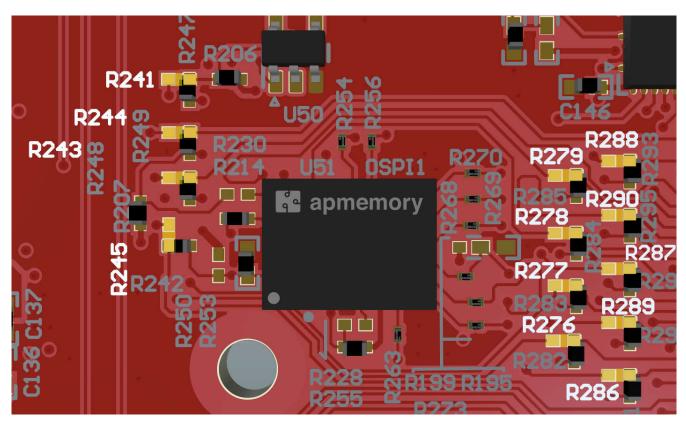

Figure 2-14. OSPI1 Expansion Connector - Populate Resistors

#### The pinout of the OSPI Expansion Connector can be found in Section 2.3.1, OSPI Expansion Connector.

Figure 2-15. LP-AM261 OSPI Interface

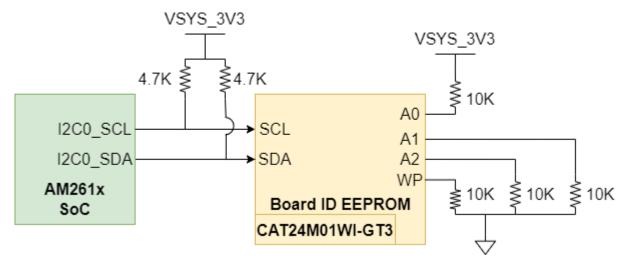

#### 2.10.1.2 Board ID EEPROM

The AM261x LaunchPad has a I2C-based 1Mbit EEPROM (CAT24M01WI-GT3) to store board configuration details. The Board ID EEPROM is connected to the I2C1 interface of the AM261x MCU. The default I2C address of the EEPROM is set to 0x51 by pulling up the address pin A0 to 3.3V, and pulling down the address pins A1 and A2 to ground. The Write Protect pin for the EEPROM is by pulled to ground by default. Therefore, Write Protect is disabled.

Figure 2-16. Board ID EEPROM

#### 2.10.2 Ethernet Interface

The LP-AM261 has two Ethernet Add-on board connectors for enabling Ethernet evaluation and development. The Ethernet peripheral to connector connectivity is detailed in Table 2-19 below:

| Ethernet Signals | CONNECTOR_0  | CONNECTOR_1  |  |  |

|------------------|--------------|--------------|--|--|

| RGMII1           |              | ✓            |  |  |

| RGMII2           | $\checkmark$ |              |  |  |

| CPSW MDIO        | ✓ (via MUX)  | ✓ (via MUX)  |  |  |

| PR0_PRU0         | $\checkmark$ |              |  |  |

| PR0_PRU1         |              | $\checkmark$ |  |  |

| PRU MDIO         | ✓ (via MUX)  | ✓ (via MUX)  |  |  |

#### Table 2-19. Ethernet Peripheral - Connector Connections

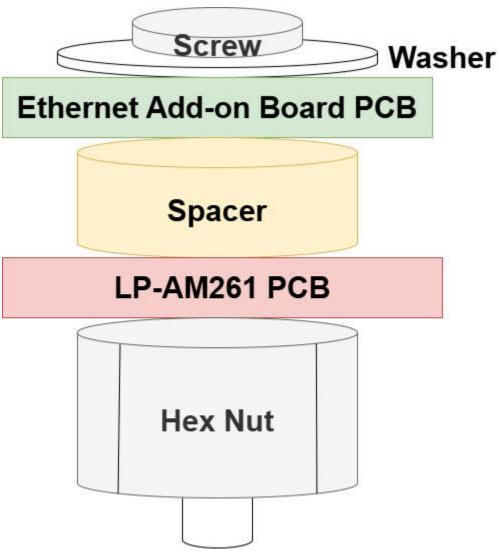

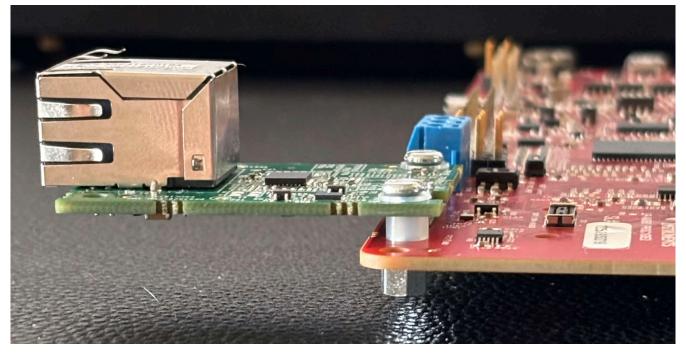

Supported Ethernet add-on boards, such as the DP83826-EVM-AM2 can be connected to the add-on board connectors for evaluating Ethernet on LP-AM261. To connect the Ethernet add-on board to the LP-AM261, attach the receptacle on the bottom side of the add-on board to J21 (CONNECTOR\_0) or J23 (CONNECTOR\_1) on the LP-AM261. Use the screws, washers, spacers, and hex nuts included in the Ethernet add-on board kit to securely mount the two boards together.

Figure 2-17. Ethernet Add-on Board Assembly Hardware

Figure 2-18. LP-AM261 and Ethernet Add-on Board Stack

The connected board assembly is shown in Figure 2-19:

The Ethernet add-on board header pinout is detailed in Section 2.3.3.

#### Figure 2-19. LP-AM261 with DP83826-EVM-AM2 Ethernet Add-on Boards

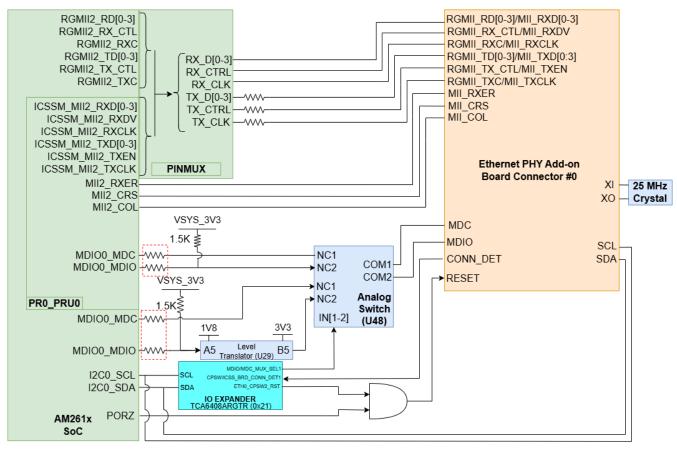

#### 2.10.2.1 Ethernet PHY Add-on Board Connector #0 - CPSW RGMII/ICSSM

The AM261x LaunchPad has a 48-pin Ethernet PHY add-on board connector connected to either RGMII2 (CPSW Ethernet) or the PR0\_PRU0 instance of the AM261x on-die Programmable Real-time Unit and Industrial Communication Sub System (PRU-ICSS). The RGMII2 CPSW signals and PR0\_PRU0 signals are internally pinmuxed on the AM261x MCU. For more information on the internal muxing of signals refer to the device data sheet.

Figure 2-20. Ethernet PHY Add-on Board CONNECTOR\_0

The MDIO signal from the AM261x MCU to the Ethernet connector requires  $1.5k\Omega$  pullup resistors to the 3.3V system supply voltage for proper operation. An analog switch selects between the CPSW MDIO/MDC and the PRU-ICSS MDIO/MDC signals to be routed to the Ethernet add-on board connector. This analog switch is controlled by an IO expander signal.

The reset input for the PHY from Ethernet port connector is controlled by the PORz AM261x SoC output signal.

The I2C address of the Ethernet Add-on board EEPROM is determined by on-board pull resistors that connect to the address pins of the EEPROM on the add-on board when connected to the LP-AM261. These address pins also drive a FET network on the add-on board that determine the Ethernet PHY's address. All Ethernet add-on boards in the TI Ethernet Add-on Board Ecosystem follow the same addressing convention.

| Connector_# | EEPROM_A2<br>(connector pin 37) |    | EEPROM_A1 |    | EEPROM_A0 (connector<br>pin 47) |    | I2C Address | PHY<br>Address                        |

|-------------|---------------------------------|----|-----------|----|---------------------------------|----|-------------|---------------------------------------|

|             | Pull                            | A2 | Pull      | A1 | Pull                            | A0 |             |                                       |

| CONNECTOR_0 | GND                             | 0  | VDDIO     | 1  | GND                             | 0  | 0x52        | Ethernet<br>add-on board<br>dependent |

#### Table 2-20. CONNECTOR 0 I2C / PHY Addressing Scheme

The PHY address is dependent on which Ethernet add-on board is being used, since different PHYs have different address configurations. To determine the PHY address for a specific Ethernet Add-on Board, see the Add-on Board's User Guide and find the *Multi-Connector Addressing* section in the document.

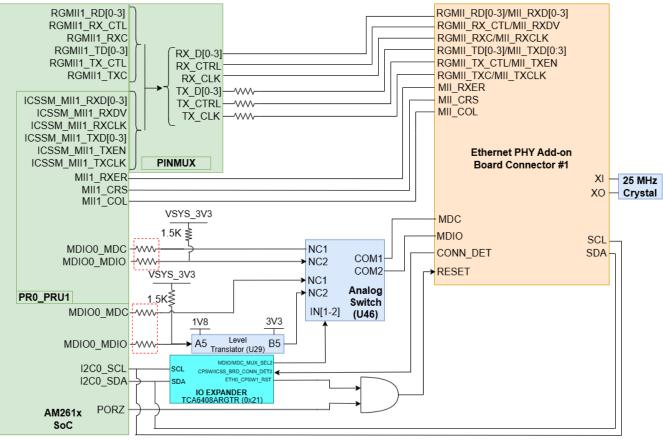

#### 2.10.2.2 Ethernet PHY Add-on Board Connector #1 - CPSW RGMII/ICSSM

The AM261x LaunchPad has a 48-pin Ethernet PHY add-on board connector connected to either RGMI1 (CPSW Ethernet) or the PR0\_PRU1 instance of the AM261x on-die Programmable Real-time Unit and Industrial Communication Sub System (PRU-ICSS). The RGMI11 CPSW signals and PR0\_PRU1 signals are internally pinmuxed on the AM261x MCU. For more information on the internal muxing of signals refer to the device data sheet.

Figure 2-21. Ethernet PHY Add-on Board CONNECTOR\_1

The MDIO signal from the AM261x MCU to the Ethernet connector requires  $1.5k\Omega$  pullup resistors to the 3.3V system supply voltage for proper operation. An analog switch selects between the CPSW MDIO/MDC and the PRU-ICSS MDIO/MDC signals to be routed to the Ethernet add-on board connector. This analog switch is controlled by an IO expander signal.

The reset input for the PHY from Ethernet port connector is controlled by the PORz AM261x SoC output signal.

The I2C address of the Ethernet Add-on board EEPROM is determined by on-board pull resistors that connect to the address pins of the EEPROM on the add-on board when connected to the LP-AM261. These address pins also drive a FET network on the add-on board that determine the Ethernet PHY's address. All Ethernet add-on boards in the TI Ethernet Add-on Board Ecosystem follow the same addressing convention.

#### Table 2-21. CONNECTOR 1 I2C / PHY Addressing Scheme

| Connector_# | EEPROM_A2<br>(connector pin 37) |    | EEPROM_A1 |    | EEPROM_A0 (connector<br>pin 47) |    | I2C Address | PHY<br>Address                        |

|-------------|---------------------------------|----|-----------|----|---------------------------------|----|-------------|---------------------------------------|

|             | Pull                            | A2 | Pull      | A1 | Pull                            | A0 |             |                                       |

| CONNECTOR_1 | GND                             | 0  | VDDIO     | 1  | VDDIO                           | 1  | 0x53        | Ethernet<br>add-on board<br>dependent |

The PHY address is dependent on which Ethernet add-on board is being used, since different PHYs have different address configurations. To determine the PHY address for a specific Ethernet Add-on Board, see the Add-on Board's User Guide and find the *Multi-Connector Addressing* section in the document.

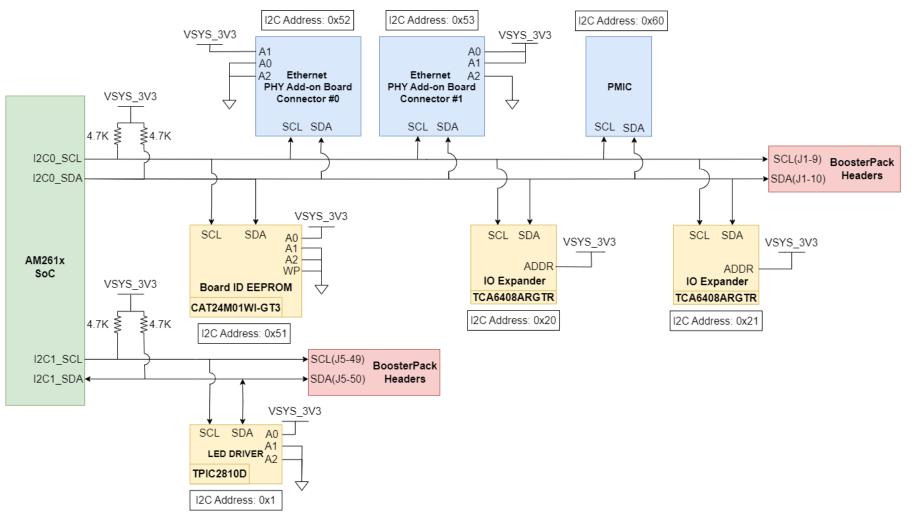

# 2.10.3 I2C

The AM261x LaunchPad uses two AM261x SoC inter-integrated circuit (I2C) instances to operate as a controller for various targets. I2C data and clock lines are pulled up to the 3.3V system voltage supply.

# Figure 2-22. LP-AM261 I2C Interface

#### Table 2-22. I2C Addressing

|      | Target       | I2C Instance | I2C Addres Bit Description                                                                                                                                             | Device Addressing                                         | LaunchPad Config. | I2C Address |

|------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|-------------|

| Boar | rd ID EEPROM | I2C0         | The first 4 bits of the device address are set to 1010, the next two are set by the A2 and A1 pins, the seventh bit, a16, is the most significant internal address bit | 0b10110[A2][A1][a16]<br>A1 and A2 are connected to ground | 0b1010001         | 0x51        |

### Table 2-22. I2C Addressing (continued)

| Target I2C Instance                    |                                     | I2C Addres Bit Description                                                                                                                                                                                                                 | Device Addressing                                                                    | LaunchPad Config. | I2C Address |  |

|----------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------|-------------|--|

| LED Driver                             | I2C1                                | The first four bits of the target address are 0000, the following three are determined by A2, A1, and A0       0b0000[A2][A1][A0]       0l         A2, A1, and A0       A1 are connected to ground A0 is connected to 3.3V supply       0l |                                                                                      | 06000001          | 0x01        |  |

| BoosterPack Headers                    | Pack Headers 12C0, Target dependent |                                                                                                                                                                                                                                            |                                                                                      |                   |             |  |

|                                        | I2C1                                |                                                                                                                                                                                                                                            |                                                                                      |                   |             |  |

| IO Expander #1                         | 12C0                                | The first 6 bits of the target address are set to 010000, the next bit is determined by the addr pin of the IO expander                                                                                                                    | IO_ADDR pin connected to 3.3V supply                                                 | 0b0100001         | 0x21        |  |

| IO Expander #2                         | 12C0                                | The first 6 bits of the target address are set to 010000, the next bit is determined by the addr pin of the IO expander                                                                                                                    | IO_ADDR pin connected to 3.3V supply                                                 | 0b0100000         | 0x20        |  |

| Ethernet PHY add-on Board Connector #0 | 12C0                                | The first four bits of the target address are 1010, the following three are determined by A2, A1, and A0                                                                                                                                   | 0b1010[A2][1][A0]<br>A2 and A0 are connected to ground                               | 0b1010010         | 0x52        |  |

| Ethernet PHY add-on Board Connector #1 | 12C0                                | The first four bits of the target address are 1010, the following three are determined by A2, A1, and A0                                                                                                                                   | 0b1010[A2][1][A0]<br>A2 is connected to ground and A0 is connected<br>to 3.3V supply | 0b1010011         | 0x53        |  |

| PMIC                                   | I2C0                                | 7 bit device address for the PMIC is 1100000                                                                                                                                                                                               | 0b1100000                                                                            | 0b1100000         | 0x60        |  |

Note

Underlined address bits are fixed based on the device addressing and cannot be configured.

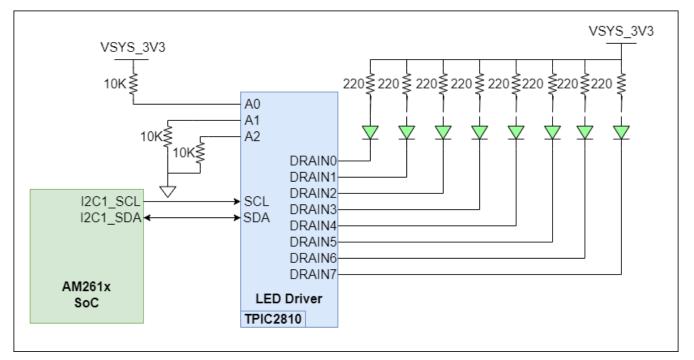

### 2.10.3.1 Industrial Application LEDs

The AM261x LaunchPad has an LED Driver (TPIC2810D) that is used for controlling the Industrial Communication LED array. The driver is connected to eight green LEDs and has an I2C address of 0x01.

Figure 2-23. Industrial Application I2C LED Array

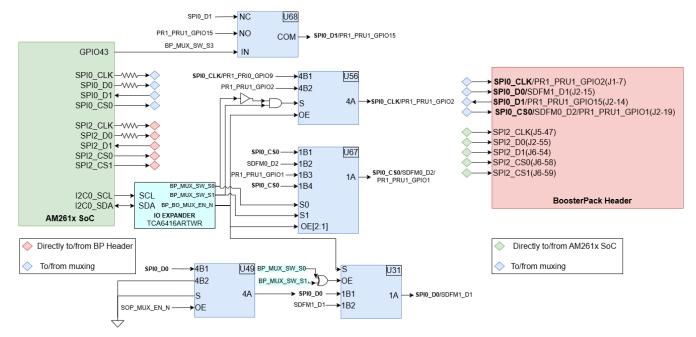

### 2.10.4 SPI

The AM261x LaunchPad maps two SPI instances (SPI0, SPI2) from the AM261x MCU to the BoosterPack headers. Series termination resistors are placed near the SoC for each SPI clock and SPI D0 signal. There are a series of muxes that route the SPI0 signals to the BoosterPack headers depending on the BoosterPack mode selected. The following tables detail the mux select signals for routing SPI0 signals to the BoosterPack headers:

| Table 2-23. U68 Mux Select             |                 |  |

|----------------------------------------|-----------------|--|

| BP_MUX_SW_S3 (GPIO43) Mux Output (COM) |                 |  |

| 0                                      | SPI0_D1         |  |

| 1                                      | PR1_PRU1_GPIO15 |  |

#### Table 2-24. U56 Mux Select

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | Mux Output (4A) |

|--------------|--------------|-----------------|

| 0            | 0            | SPI0_CLK        |

| 0            | 1            | PR1_PRU1_GPIO2  |

| 1            | 0            | SPI0_CLK        |

| 1            | 1            | SPI0_CLK        |

#### Table 2-25. U67 Mux Select

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | Mux Output (4A) |  |

|--------------|--------------|-----------------|--|

| 0            | 0            | SPI0_CS0        |  |

| 0            | 1            | SDFM0_D2        |  |

| 1            | 0            | PR1_PRU1_GPIO1  |  |

| 1            | 1            | SPI0_CS0        |  |

#### Table 2-26. U31 Mux Select

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | Mux Output (1A) |

|--------------|--------------|-----------------|

| 0            | 0            | SPI0_D0         |

| 0            | 1            | SDFM1_D1        |

| 1            | 0            | SDFM1_D1        |

| 1            | 1            | SPI0_D0         |

All SPI2 signals are directly routed to the boosterpack.

Figure 2-24. LP-AM261 SPI Interface

Hardware

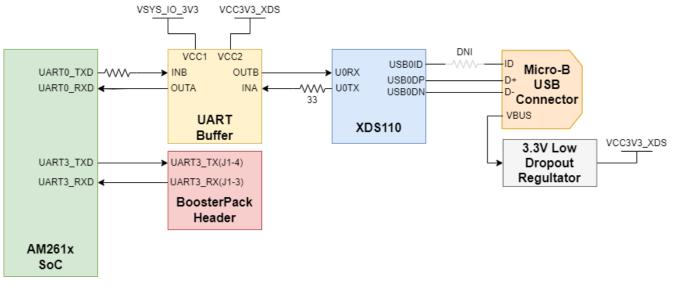

# 2.10.5 UART

The AM261x LaunchPad uses the XDS110 as a USB2.0 to UART bridge for terminal access. UART0 transmit and receive signals of the AM261x SoC are mapped to the XDS110 with a dual channel isolation buffer (ISO7721DR) for translating from the 3.3V IO voltage supply to the 3.3V XDS supply. The XDS110 is connected to a micro-B USB connector for the USB 2.0 signals. ESD protection is provided to the USB 2.0 signals by a transient voltage suppression device (TPD4E02B04DQAR). The micro-B USB connector's VBUS 5V power is mapped to a low dropout regulator (TPS79601DRBR) to generate the 3.3V XDS110 supply. A separate 3.3V supply for the XDS110 allows for the emulator to maintain a connection when power to the LaunchPad is removed.

The UART3 instance is mapped directly to the BoosterPack header J1.

Figure 2-25. LP-AM261 UART Interface

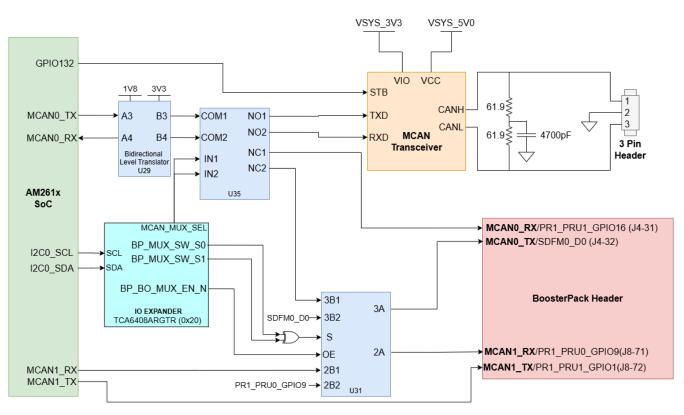

# 2.10.6 MCAN

The AM261x LaunchPad is equipped with a single MCAN Transceiver (TCAN1044VDRBTQ1) that is connected to the MCAN0 interface of the AM261x MCU. The MCAN Transceiver has two power inputs: VIO is the transceiver 3.3V system level shifting supply voltage and VCC is the transceiver 5V supply voltage. The AM261x MCU CAN data transmit data input is mapped to TXD of the transceiver and the CAN receive data output of the transceiver is mapped to the MCAN RX signal of the MCU.

The system has a  $120\Omega$  split termination on the CANH and CANL signals to improve EMI performance. Split termination improves the electromagnetic emissions behavior of the network by eliminating fluctuations in the bus common-mode voltages at the start and end of message transmissions.

The low and high level CAN bus input output lines are terminated to a three pin screw-terminal header.

The standby control signal is an AM261x GPIO signal. The STB control input has a pullup resistor that is used to put the transceiver in low-power standby mode to prevent excessive system power. Below is a table that shows the operating modes of the MCAN transceiver based on the STB control input logic.

| STB  | Device Mode                               | Driver  | Receiver | RXD Pin                                         |

|------|-------------------------------------------|---------|----------|-------------------------------------------------|

| High | Low current standby mode with bus wake-up |         | · ·      | High (recessive) until valid<br>WUP is received |

| Low  | Normal Mode                               | Enabled | Enabled  | Mirrors bus state                               |

### Table 2-27. MCAN Transceiver Operating Modes

MCAN0 and MCAN1 are routed to the BoosterPack Headers through a series of muxes. The following table details the mux select signals for routing MCAN1 signals to the BoosterPack Headers.

| Table 2 | 2-28. l | J35 M | ux Select |

|---------|---------|-------|-----------|

|---------|---------|-------|-----------|

| MCAN_MUX_SEL | Mux Output                         |  |

|--------------|------------------------------------|--|

| 0            | MCAN0_RX/TX to BoosterPack Headers |  |

| 1            | MCAN0_RX/TX to MCAN Transceiver    |  |

#### Table 2-29. U31 Mux Select

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | Mux Output (3A) | Mux Output (2A) |

|--------------|--------------|-----------------|-----------------|

| 0            | 0            | MCAN0_TX        | MCAN1_RX        |

| 0            | 1            | SDFM0_D0        | PR1_PRU0_GPIO9  |

| 1            | 0            | SDFM0_D0        | PR1_PRU0_GPIO9  |

| 1            | 1            | MCAN0_TX        | MCAN1_RX        |

Figure 2-26. LP-AM261 MCAN Interface

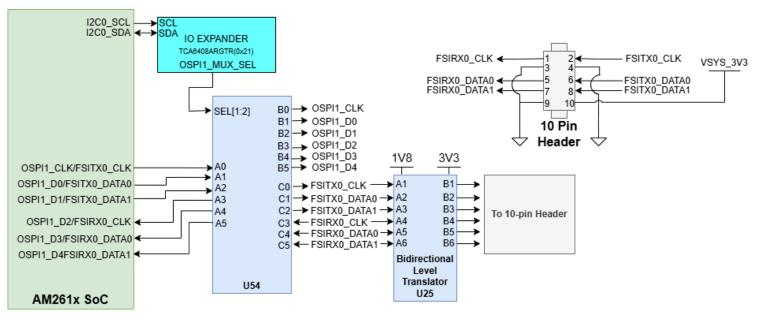

### 2.10.7 FSI

The AM261x LaunchPad supports a Fast Serial Interface peripheral by terminating the AM261x FSI RX and TX signals to a 10-pin header. The interface has two lines of data and a clock line for both the receive and transmit signals. The 10-pin header is connected to the 3.3V System voltage supply. The AM261x internal pinmux can be used to select between FSI signals and other functionality of the associated pins. A 2:1 mux selects between FSI and OSPI1 signals, and routes to the appriopriate hardware on the PCB.

### Figure 2-27. LP-AM261 FSI Interface

#### Table 2-30. U54 Mux Select

| OSPI1_MUX_SEL | Output        |

|---------------|---------------|

| 0             | OSPI1 Signals |

| 1             | FSI Signals   |

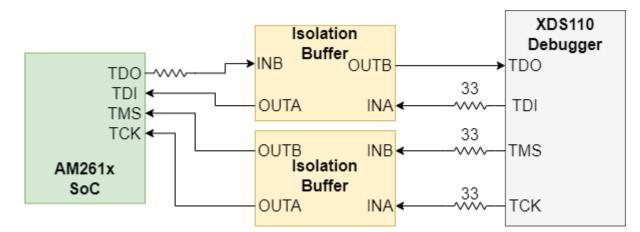

### 2.10.8 JTAG

The AM261x LaunchPad includes an XDS110 class on-board emulator. The LaunchPad includes all circuitry needed for XDS110 emulation. The emulator uses a USB 2.0 Micro-B connector to interface the USB 2.0 signals that are generated from the UART-USB bridge. The VBUS power from the connector is used to power the emulator circuit so that the connection to the emulator is not lost when power to the LaunchPad is removed.

Figure 2-28. JTAG Interface to XDS110

### 2.10.9 Test Automation Pin Mapping

The following table details the Test Automation GPIO mapping.

| Signal Name   | Description                                                                                                                                      | Direction |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| TA_POWERDOWNZ | When logic low, disables the 5V Supply                                                                                                           | Output    |

| TA_PORZ       | When logic low, connects the PORz signal to ground due to PMOS $V_{\rm GS}$ being less than zero creating a power on reset to the MAIN domain    | Output    |

| TA_RESETZ     | When logic low, connects the WARM RESETn signal to ground due to PMOS $V_{\rm GS}$ being less than zero creating a warm reset to the MAIN domain | Output    |

| TA_GPIO1      | When logic low, connects the INTn signal to ground due to PMOS $V_{\rm GS}$ being less than zero creating an interrupt to SoC                    | Output    |

| TA_GPIO3      | When logic low, disables the boot mode buffer output enable                                                                                      | Output    |

| TA_GPIO4      | Reset signal for boot mode IO Expander                                                                                                           | Output    |

| TA_I2C_SCL    | I2C Clock signal used to communicate with bootmode IO expander to change the boot modes.                                                         | Output    |

| TA_I2C_SDA    | I2C Data signal used to communicate with bootmode IO expander to change the boot modes.                                                          | Output    |

### Table 2-31. Test Automation GPIO and I2C Mapping

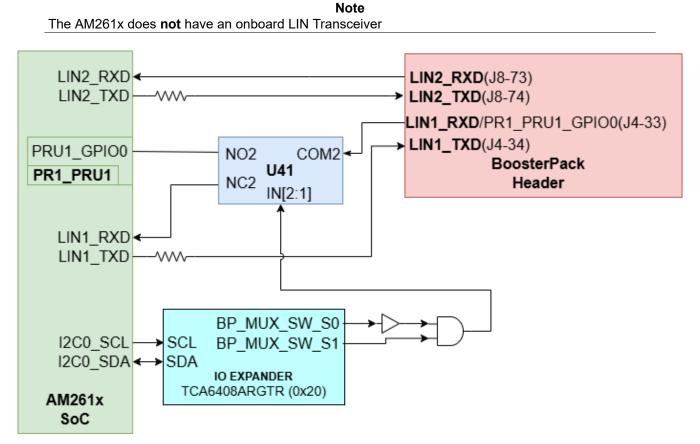

### 2.10.10 LIN

The AM261x LaunchPad supports Local Interconnect Network communication with two LIN instances mapped to the BoosterPack header.

### Figure 2-29. LIN Instances to BoosterPack Header

LIN2\_TXD, LIN2\_RXD and LIN1\_TXD signals are directly routed to BoosterPack connectors. LIN1\_RXD is routed through a mux. The mux selection table is shown below.

Table 2-32. U41 Mux Select

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | Mux Output (COM2) |

|--------------|--------------|-------------------|

| 0            | 0            | LIN1_RXD          |

| 0            | 1            | PR1_PRU1_GPIO0    |

| 1            | 0            | LIN1_RXD          |

| 1            | 1            | LIN1_RXD          |

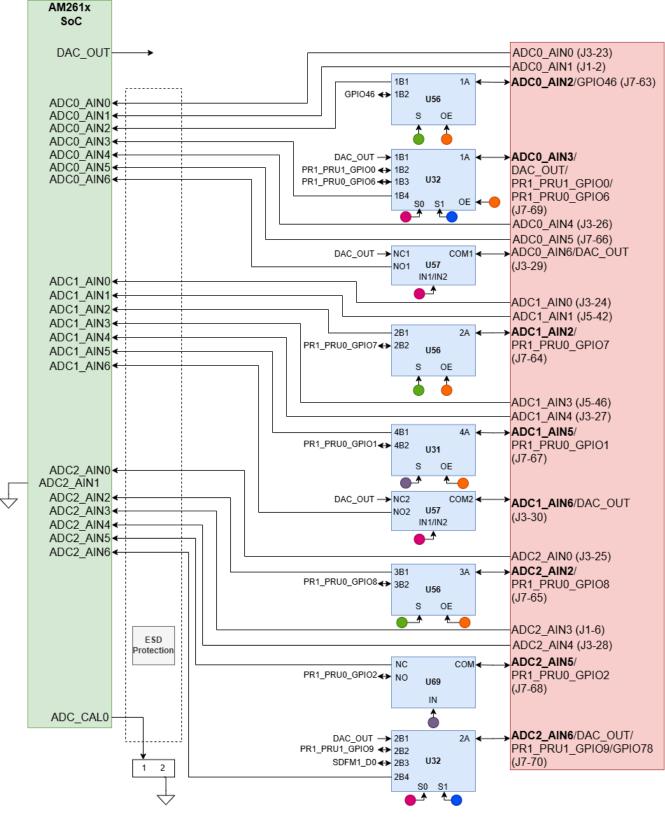

# 2.10.11 ADC and DAC

The AM261x LaunchPad maps 20 ADC inputs to the BoosterPack header. All of the ADC inputs that are used in the LaunchPad are ESD protected.

There are several muxes that determine the path of the ADC input signals depending on the BoosterPack mode selected. shows the mux select signal logic used in the BoosterPack mode muxes.

Figure 2-30. BoosterPack Mode Mux Select Logic

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | BP_MUX_SW0_N_AND_SW1 | BP_MUX_SW0_XOR_SW1 |  |  |  |  |

|--------------|--------------|----------------------|--------------------|--|--|--|--|

| 0            | 0            | 0                    | 0                  |  |  |  |  |

| 0            | 1            | 1                    | 1                  |  |  |  |  |

| 1            | 0            | 0                    | 1                  |  |  |  |  |

| 1            | 1            | 0                    | 0                  |  |  |  |  |

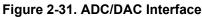

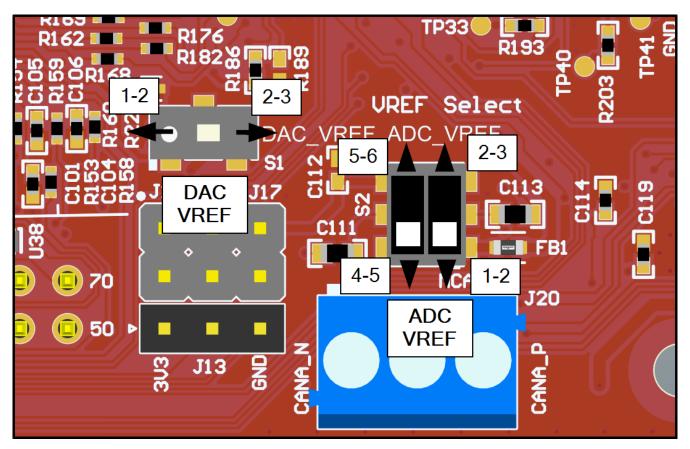

The ADC and DAC require a voltage reference. The AM261x LaunchPad has two switches that allow the user to select the ADC and DAC voltage reference.

Figure 2-32. ADC and DAC VREF Switches

The DAC VREF Switch (S1) is a single pole double throw switch that controls the input of the ADC VREF inputs of the AM261x SoC.

Note

| The DAC VREF switch must be in the <b>Pin 1-2</b> position for SDK examples to function properly. |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Table 2-34. DAC VREF Switch                                                                       |  |  |  |  |  |

| DAC VREF Switch Position Reference Selection                                                      |  |  |  |  |  |

| Pin 1-2 (LEFT) AM261x on-die LDO                                                                  |  |  |  |  |  |

| Pin 2-3 (RIGHT) External DAC VREF Header                                                          |  |  |  |  |  |

The ADC VREF Switch (S2) contains two single pole double throw switches that controls the input of the ADC VREF inputs of the AM261x SoC.

| Note                                                                                                       |

|------------------------------------------------------------------------------------------------------------|

| The ADC VREF switches must be in position <b>1-2</b> and <b>4-5</b> for SDK examples to function properly. |

| Table 2-35. ADC VREF Switch                  |                                                              |  |  |  |

|----------------------------------------------|--------------------------------------------------------------|--|--|--|

| ADC VREF Switch Position Reference Selection |                                                              |  |  |  |

| Pin 1-2 (DOWN)                               | OPEN - Allow for reference to be AM261x on-die LDO reference |  |  |  |

| Pin 2-3 (UP)                                 | External ADC VREF Header                                     |  |  |  |

| Pin 4-5 (DOWN)                               | OPEN - Allow for reference to be AM261x on-die LDO reference |  |  |  |

| Pin 5-6 (UP)                                 | External ADC VREF Header                                     |  |  |  |

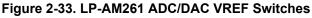

### 2.10.12 EQEP

The AM261x LaunchPad internally muxes the eQEP, FSI and OSPI1 signals. The eQEP0 instance of the AM261x is terminated to two headers (J19, J16). The eQEP1 instance of the AM261x is terminated to two headers (J18, J15).

All eQEP signals have series termination resistors between the AM261x SoC and the Voltage Level Translator (TXB0108RGYR). The voltage level shifter is responsible for translating the 1.8V to 5V.

# 2.10.13 EPWM

The AM261x LaunchPad maps 12 PWM channels (6 PWM\_A/B pairs) to the BoosterPack Header. Each EPWM signal has a series termination resistor. For the mapping of each EPWM signal refer to BoosterPack Header.

| EPW<br>EPW<br>EPW<br>EPW<br>EPW<br>SOC<br>EPW | /M2_A<br>/M2_B<br>/M3_A<br>/M3_B<br>/M4_A |                                                    | EPWM2<br>EPWM3<br>EPWM3<br>EPWM4<br>EPWM4<br>EPWM5<br>EPWM5 | A(J4-40)<br>B(J4-39)<br>A(J4-38)<br>B(J4-37)<br>A(J4-36)<br>B(J4-35)<br>Called A<br>A(J8-80)<br>A(J8-80)<br>A(J8-78)<br>B(J8-77)<br>B(J8-77)<br>Called A<br>Called |  |

|-----------------------------------------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EPW<br>EPW                                    |                                           | 3V3<br>B1 -<br>B2 -<br>B8 -<br>B8 -<br>B8 -<br>U29 | EPWM6_<br>-<br>EPWM7_<br>EPWM7_                             | _B(J8-77)<br>A(J8-76)<br>_B(J8-75)<br>_B(J8-79)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

Figure 2-35. EPWM Signal Mapping to BoosterPack Header

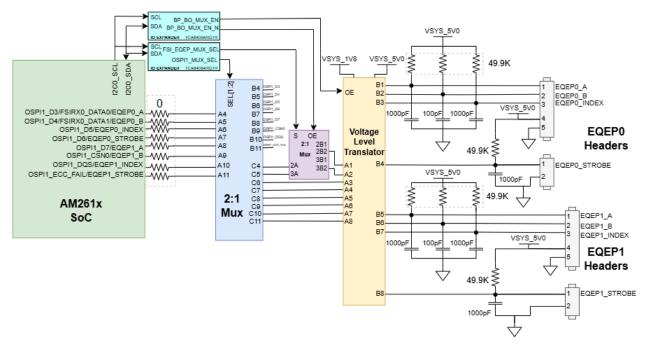

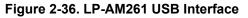

### 2.10.14 USB

The LP-AM261 has one USB2.0 interface connected to the USB0 peripheral on the AM261x MCU.

AM261x supports USB DFU Bootmode. Boot mode selection and details are given in Bootmode