# AM64x SK Evaluation Module (EVM)

# **Description**

The AM64B starter kit (SK) is a low-cost stand-alone test and development platform based on the Sitara™ AM6442 processor that is ideal for accelerating the prototype phase of your next design. The kit includes wired (Ethernet) and wireless (2.4GHz and 5GHz) connectivity, three expansion headers, multiple boot options and flexible debug.

### **Features**

- Software: TI Processor SDK Linux®/ RT Linux kernel, Yocto file system, out-of-box demos including Wi-Fi™

- Processing: AM64x with 2x Arm® Cortex®-A53, 4x Arm Cortex-R5, 2x TI PRU ICSSG

- Networking: Wi-Fi (dual-band), Bluetooth®/ Bluetooth Low Energy 5.1; 2x RJ-45 Ethernet 1000/100Mbps

- Connectivity: 1x Type A USB 3.1 gen1 (SuperSpeed), on-board XDS110 JTAG Emulator and 3x UARTs via micro-USB

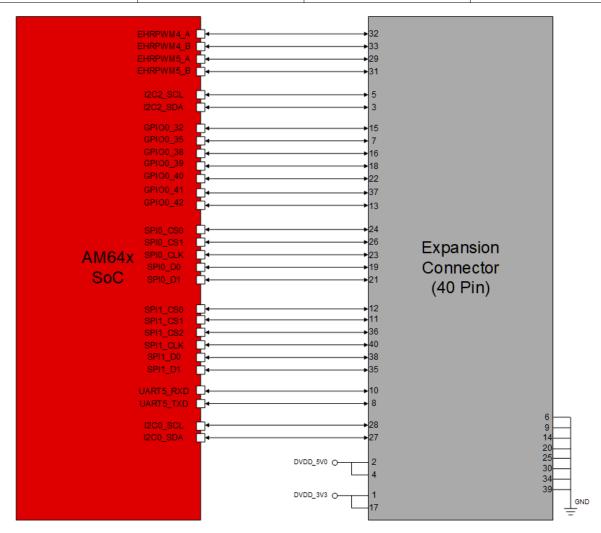

- Expansion and prototyping: 40-pin Raspberry Pi (RPI4) HATs, PRU-ICSSG Real-Time I/O, and TI-MCU headers

- Storage: 2GB LPDDR4

- Bootable interfaces on SK: Removable uSD, USB, 16MB OSPI, Ethernet, universal asynchronous receiver/transmitter (UART)

This design incorporates HDMI® technology.

# 1 Evaluation Module Overview

#### 1.1 Introduction

This evaluation module user's guide describes the hardware architecture of the AM64x SKEVM. The AM64x processor comprises of a Dual-Core 64-bit Arm® Cortex®-A53 microprocessor, 2x Dual core Arm Cortex-R5F MCUs and an Arm Cortex-M4F MCU.

The AM64x starter kit is a stand-alone test and development platform that is an excellent choice for accelerating the prototype phase of the next design. The kit includes: wired and wireless connectivity, three expansion headers, multiple boot options and flexible debug capabilities.

The starter kit is equipped with AM64x processor from TI and an optimized feature-set to allow the user to create commercial and industrial devices using Ethernet-based, USB, and serial wired interfaces plus 2.4-GHz and 5-GHz wireless communications. Two 1-Gbps Ethernet Ports for wired connectivity are on-board, in addition to three expansion headers (PRU, MCU, User) headers to expand the functionality of the board. Using standard serial protocols such as UART, I2C, and SPI, the starter kit can interface with a multitude of other devices, acting as a communications gateway. Receiving 5-V power from a standard USB-C port, the starter kit allows the user to access the R5F cores of the AM64x; making the device an excellent choice as a programmable logic controller (PLC) or motor controller, processing sensor inputs and managing peripherals in real-time while running Linux on the A53 cores, and making the device the central engine in a remote industrial communication network. The embedded emulation logic allows for emulation and debugging using standard development tools such as Code Composer Studio™ from TI.

#### Note

This evaluation board is a pre-production release and has several known issues that must not be copied into a production system. For detailed information, see Section 5.1.

During custom board design, customers tend to reuse the SK design files and make edits to the design file. Alternatively, customers reuse some of the common implementations including the SOC, memory and communication interfaces. Since the SK is expected to have additional functionalities, customers optimize the SK implementation to suit their board design requirements. While optimizing the SK schematics, errors get introduced into the custom design that could cause functional, performance or reliability issues. When optimizing customers have queries regarding the SK implementation resulting in design errors. Many of the optimization and design errors are common across designs. Based on the learnings and data sheet pin connectivity recommendations, comprehensive Design Notes (D-Note:), Review Notes (R-Note:) and Cad Notes (Cad Note:) have been added near each section of the SK schematic that customers could review and follow to minimize errors. Additional files as part of the design downloads have been included to support customer evaluation.

#### 1.2 Kit Contents

#### Major Features of AM64B SKEVM are as follows:

- Includes AM64x SoC, Memory, boot interfaces, on-board JTAG and power supply circuit.

- Provides general purpose expansion interfaces for hardware add on boards.

- · Operates in a stand-alone mode without any of the daughter cards.

- Powered through USB Type-C Connector.

- External Communication through Giga-Bit Ethernet Ports (x2) and USB 3.0 Type-A (x1).

- USB3.0 high speed interface terminated on Type-A USB Host connector.

- Wi-link WL1837 Module with support for both Wi-Fi and Bluetooth.

- Optionally supply the power needed for the daughter cards (limited to 500 mA on 3V3 and 155 mA on 5 V rail).

# AM64x System-on-Chip (SoC):

AM64x combines two instances of Sitara's gigabit TSN-enabled PRU-ICSSG with up to two Arm Cortex-A53

cores, up to four Cortex-R5F MCUs, and a Cortex-M4F MCU. The SoC is soldered to the PCB without

socket.

#### Memory

www.ti.com Evaluation Module Overview

- 2GB DDR4 supporting data rate up to 1600MT/s

- Micro Secure Digital (SD) Card with UHS-1 support

- 512 Mbit OSPI EEPROM

- 512 Kbit Inter-Integrated Circuit (I2C) board ID EEPROM

# **High Speed Interface:**

- Two CPSW Gigabit Ethernet (RGMII) ports interfaced with Texas Instruments Gigabit Ethernet PHYs

- One USB3.0 Host interface terminated on a USB Type-A connector for data transfer

# **Expansion Bus:**

- 3x Expansion connectors using 0.1" spaced 0.025" square post connectors

- 1x Raspberry Pi compatible 40 pin expansion connector allowing seamless integration to HAT boards

- 1x PRU 54 pin connector to PRG0 interface

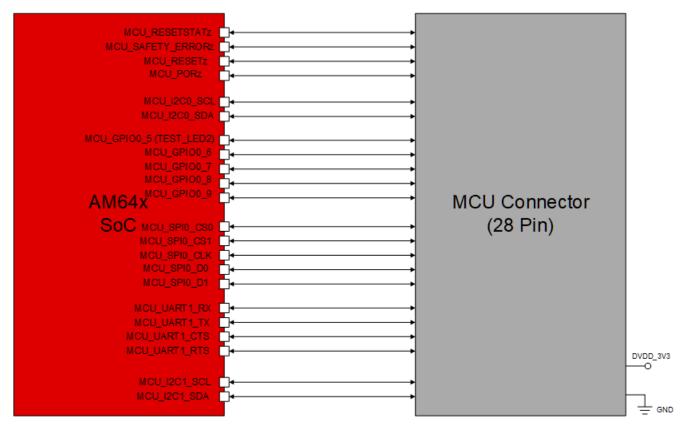

- 1x MCU 28 pin connector

### Debug:

- XDS110 On-Board Emulator

- Supports 20-pin JTAG connection from external emulator

- Automatic selection between on-board and external emulator (higher priority)

- Dual port Universal Asynchronous Receiver/Transmitter (UART) to USB circuit over micro-B USB connector prodivded via CP2105

- 2x 8-Bit DIP Switches for user selection of SoC Boot Modes

- 1x Push button for Interrupt SoC GPIO

- LEDs. One for Main Power, one for PMIC good, 1 for MCU Domain, 1 for MCU Domain GPIO and others connected to the two industrial interfaces

# **Power Supply:**

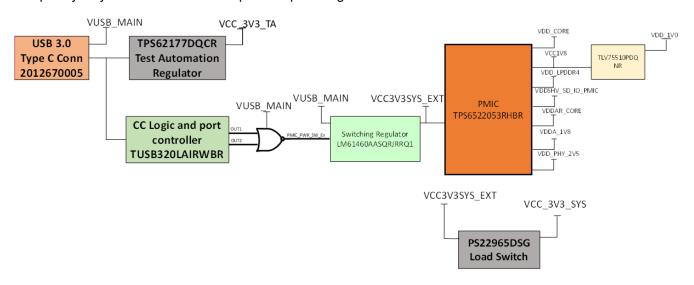

- The SK-AM64B EVM is powered through a USB Type-C Connector.

- 5 V is stepped down to 3V3 by LM61460AASQRJRRQ1 regulator. VCC3V3SYS\_EXT is the input supply to the PMIC.

- TPS6522053RHBR PMIC and other discrete regulators on the starter kit provide all the required power supplies for SoC and other peripherals (LPDDR4, Wi-Fi Module, and OSPI, Clock buffers, Level translators and logic gates).

- Dedicated regulators are also provided for:

- Powering the always-on circuits of the Test Automation Header section.

- E-Fuse programming of the SoC.

- XDS110 Debugger section.

- 3V3 for SoC and peripherals.

- 1V0 for Ethernet Phys.

### Recommended Power Supplies:

- CUI Inc. 5 V 15W AC/DC External Wall Mount Adapter SWC15-S5-NB

- GlobalTek Inc. 5 V 15W AC/DC External Mount Wall Adapter WR9QA3000USBC3MNA-CIMR6B

- Qualtek USB 2.0 Cable C Male to C Male 3.28' Shielded Cable for powering the boards through a laptop Type-C port - 3021091-01M

- · Status Output: LEDs to indicate power status

# Compliance:

- RoHS Compliant

- REACH Compliant

# 1.3 Device Information

# 2 Hardware

# 2.1 EVM Revisions and Assembly Variants

The various AM64 SK EVM PCB design revisions, and assembly variants are listed in Table 2-1. Specific PCB revision is indicated in silkscreen on the PCB. Specific assembly variant is indicated with an additional sticker label. Table 2-2 lists known board issues.

Table 2-1. AM64 SK EVM PCB Design Revisions, and Assembly Variants

| PCB Revision | Revision and Assembly Variant Description                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROC100E1    | First prototype, early release revision of the AM64 SK EVM. Used a blue solder mask.Implements the Sitara™ AM6442 MPU.                                                     |

| PROC100E2    | First production release of the AM64 SK EVM. Uses a white solder mask. Implements the Sitara AM6442 MPU.                                                                   |

| PROC100E3    | Production release of the SK-AM64 EVM. Uses a Red solder mask. Implements the Sitara AM64x MPU with two PMIC power solution.                                               |

| PROC100E4    | Prototype revision of SK-AM64 EVM. Used a Green solder mask. Implements the Sitara AM64x MPU with single PMIC power solution.                                              |

| PROC100A     | Production release of SK-AM64B EVM. Used a Red solder mask. Implements the High-Security Field-Securable (HS-FS) silicon Sitara AM64x MPU with single PMIC power solution. |

Table 2-2. Summary of Known Issues

| Table 2-2. Sulfilliary of Kilowii issues |          |                                                                     |                      |      |  |  |  |

|------------------------------------------|----------|---------------------------------------------------------------------|----------------------|------|--|--|--|

| ID                                       | Severity | Summary                                                             | HW Versions Affected | Fix  |  |  |  |

| 1                                        | HIGH     | AM64x power requirements not met by power solution                  | E1, E2, E3           | E4   |  |  |  |

| 2                                        | HIGH     | AM64x voltage spec not met                                          | E1, E2, E3           | E4   |  |  |  |

| 3                                        | INFO     | Do not use MMC0 for SDIO devices                                    | E1, E2               | E3   |  |  |  |

| 4                                        | MEDIUM   | LPDDR4 data rate limitation under stressful benchmarking conditions | E1, E2               | E3   |  |  |  |

| 5                                        | INFO     | Junk Character on UART<br>Console                                   | E3                   | E3A  |  |  |  |

| 6                                        | MEDIUM   | Test power down signal is floating                                  | E4                   | RevA |  |  |  |

| 7                                        | HIGH     | uSD boot not working                                                | E1, E2, E3, E4       | RevA |  |  |  |

Hardware Www.ti.com

# 2.2 Important Usage Notes

Please read through this section prior to using your AM64x Starter Kit. These notes are intended to make your evaluation as trouble-free as possible. If you have any questions, please create a post on E2E and request clarification.

Verify your intended boot media against the boot modes described the Configuration section later in this document.

The AM64x Starter Kit shall be powered through the USB-C port (no data or display alt-mode support)/

The USB-C power controller on the AM64x Starter Kit is expecting a negotiation sequence with the power-delivery source, and requires a source capable of supplying 5 V at 3 A. A red LED on the bottom of the AM64x Starter Kit illuminates if the power-delivery source cannot meet these requirements.

Older and low-cost mains voltage to 5VDC USB type-A bricks intended for powering or charging consumer electronics do not have the capability to properly complete the negotiation sequence with the USB-C power controller on the AM64x Starter Kit, and prevents the EVM from powering on. Guidelines on recommended supplies are given in the Power-On/Off Procedures section.

**Caution** AM64x Starter Kit shall not be powered through the 5V0 or 3V3 pins on the 40-pin "User Expansion Connector". The AM64x Starter Kit was not designed to be powered through the expansion headers.

**Caution** Expansion headers on the AM64x Starter Kit are not fail-safe. This means expansion boards shall not drive any I/O pins while the AM64x Starter Kit is powered off. Doing so violates AM64x data sheet specifications and can cause damage to the processor or other components on the board, and is not covered by warranty.

The 40-pin "User Expansion Connector" was designed to match the types of signals and hardware interfaces found on the RPI4 40-pin connector, thereby enabling a large percentage of community developed add-on boards at a hardware level. Some deeper alternate pin functions do not match those found on the RPI4 due to the nature of each SoC vendor deciding their own pin function multiplexing.

**Attention:** Concerning HAT compatibility with the 40-pin "User Expansion Connector", always check the hardware resources required by HAT, and the active pin function PRIOR to attaching the HAT to the AM64x Starter Kit. Pin multiplex settings can require a change in the bootloader first.

**Caution: ESD Susceptible**

Electrostatic discharge (ESD) can damage equipment and impair electrical circuitry. ESD can occur when electronic printed circuit cards are improperly handled and can cause complete or intermittent failures.

Starter Kit Evaluation Board contains ESD Sensitive Electronic Devices. Hence due care must be taken while handling these boards. SK EVM must be used under controlled Lab Environment with All ESD Safe Precautions being adapted by the Test Engineers and Developers.

Please refer below for the precautionary measures:

- Make sure that the user is using the equipment in the ESD protected lab environment.

- Persons handling the product must have electronics training and observe good engineering practice standards.

- Wear an ESD-preventive coat, ESD slippers, or wrist strap, making sure that the gear makes good skin contact.

- Handle components by only their handles or edges; do not touch the printed circuit boards or connectors.

- Avoid contact between the printed circuit boards and clothing. The wrist strap only protects components from ESD voltages on the body; ESD voltages on clothing can still cause damage so wear ESD coat.

# 2.3 System Description

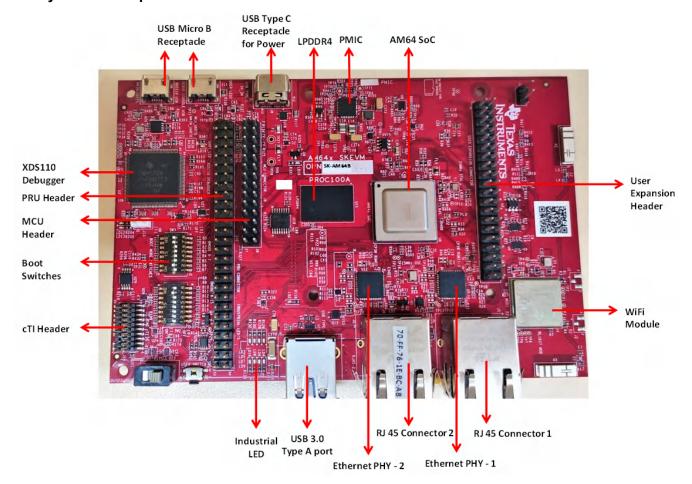

Figure 2-1. Top View of Starter Kit Processor Board

**Note: Two USB Micro-B Receptacles**

J12: XDS110 USB TO MAIN UART1

J11: DEBUG CONSOLE (MCU UART0 and MAIN UART1)

Hardware INSTRUMENTS

www.ti.com

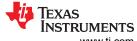

Figure 2-2. Bottom View of Starter Kit Processor Board

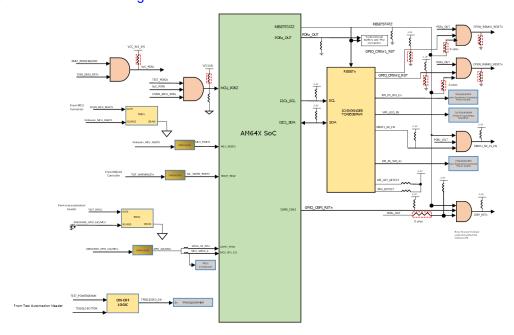

# 2.3.1 Functional Block Diagram

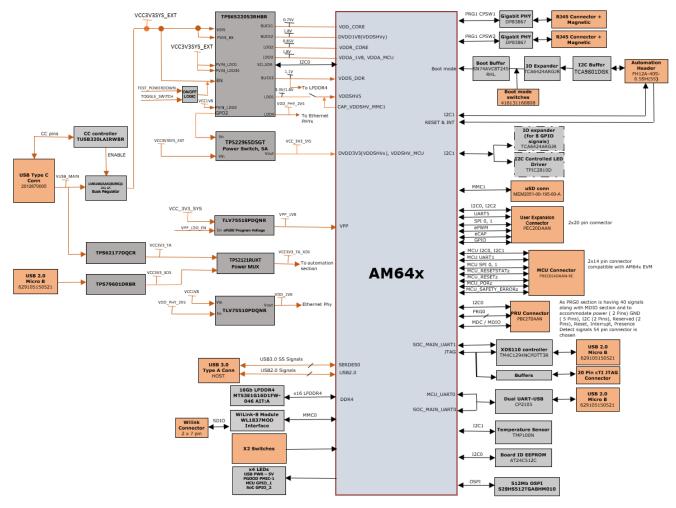

Figure 2-3 shows the functional block diagram of the AM64x SK EVM.

Figure 2-3. Starter Kit Processor Board Functional Block Diagram

Hardware Www.ti.com

#### 2.3.2 Power-On/Off Procedures

Power to the EVM is provided through an external AC/DC converter providing 5 V, 3 A (max) DC voltage to the USB Type-C Port.

### 2.3.2.1 Power-On Procedure

#### Note

The Processor SDK Linux image provides an interactive user demo by default. Once booted, the board acts as a Wireless access point with SSID **AM64xSK-AP** and Password **tiwilink8**. Once connected, the demo can be found by navigating to <a href="http://192.168.43.1:8081">http://192.168.43.1:8081</a>. More details can be found on the Software Quick Start Guide, located on the product page.

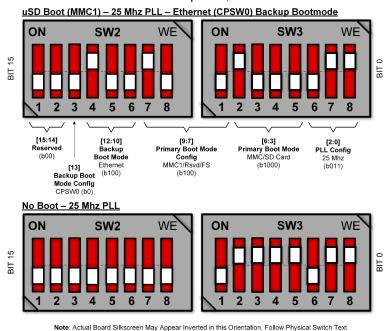

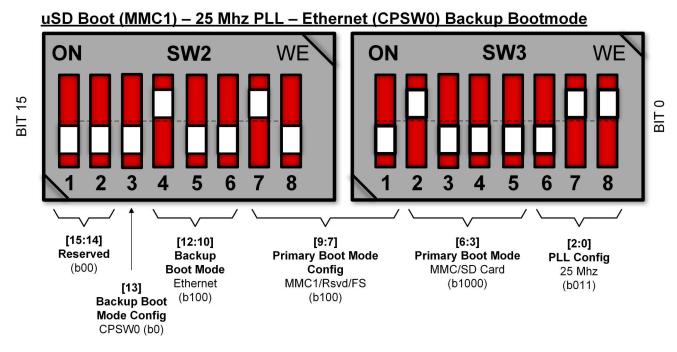

1. Place the SK EVM boot switch selectors (SW2, SW3) into selected boot mode. Example boot-modes for SD card and no-boot are shown below. For additional options, see Section 2.3.3.4.1.

, .,

### Figure 2-4. Common Bootmode Switch Positions

- 2. Connect your boot media (if applicable).

- 3. Attach the 5 V USB Type-C cable to the SK EVM Type-C (J8) Connector.

- 4. Connect the other end of the Type-C cable to the source, either AC Power Adapter, or Type C source device (such as a Laptop computer).

- 5. Use ON/OFF sliding switch SW5 to Power on the board.

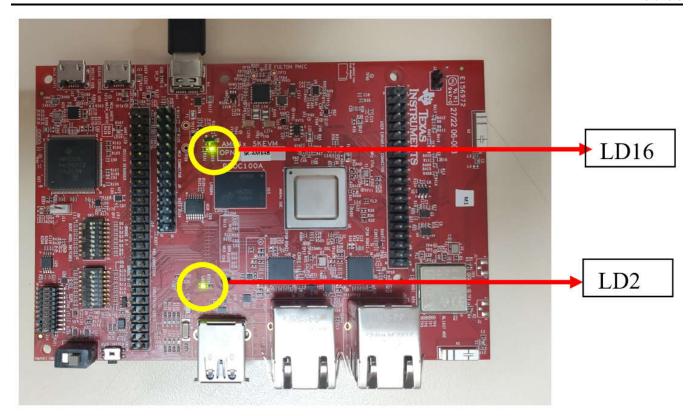

- 6. Visually inspect the LEDs against the reference photos below. The following LEDs are illuminated: LD2 and LD16 on top side of the board.

Figure 2-5. Top LED

7. XDS110 JTAG and UART debug console output are routed to micro-USB ports J12 and J11, respectively.

#### Note

Linux console output is routed to the second enumerated ttyUSB port.

#### 2.3.2.2 Power-Off Procedure

- 1. Use ON/OFF sliding switch SW5 to Power off the Board.

- 2. Disconnect AC power from AC/DC converter.

- 3. Remove the USB Type-C cable from the EVM.

# 2.3.3 Peripheral and Major Component Description

The following sections provide an overview of the different interfaces and circuits on the AM64x SK EVM.

Hardware Very Instruments

www.ti.com

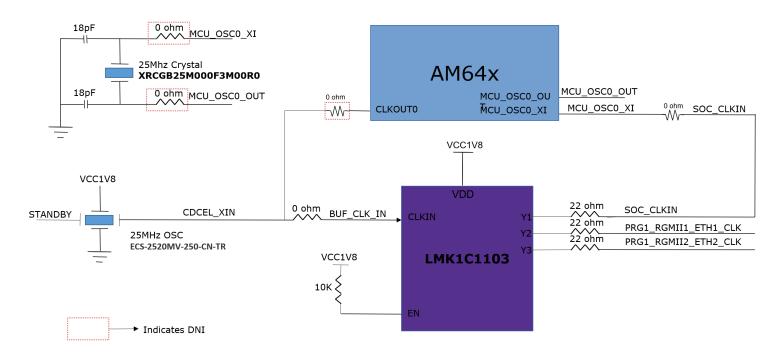

#### 2.3.3.1 Clocking

#### 2.3.3.1.1 Ethernet PHY Clock

The clock buffer of part number **LMK1C1103PWR** is used to drive the 25 MHz clock to the Ethernet PHYs. LMK1C1103PWR is a 1:3 LVCMOS clock buffer, which takes a 25 MHz crystal/LVCMOS reference input and provides four 25 MHz LVCMOS clock outputs. The source for the clock buffer is either the CLKOUT0 pin from the SoC or a 25 MHz oscillator (**ECS-2520MV-250-CN-TR**). The selection can be made using a set of resistors. By default, the oscillator is used as input to the clock buffer in SK-AM64B EVM. Output Y2 and Y3 of the clock buffer LMK1C1103PWR are used as a reference clock input for two Gigabit Ethernet PHYs in SKEVM.

Figure 2-6. AM64x SK EVM Clock Tree

Note

Resistors that are marked with a red color box are DNI.

#### 2.3.3.1.2 AM64x SoC Clock

Output Y0 from the clock buffer LMK1C1103PWR is used as a reference clock for the SoC on SKEVM. An optional 25 MHz crystal (XRCGB25M000F3M00R0) is also provided for driving the SoC. Selection of clock for the SoC is done using resistors. By default an output from the SoC\_CLKIN clock buffer is provided to the SoC. For clock source selection, see Table 2-3.

Table 2-3. SoC Clock Source

| Clock Source to SoC | Part Number        | Mount   | Unmount |

|---------------------|--------------------|---------|---------|

| Clock Buffer        | LMK1C1103PWR       | R116    | R40,R41 |

| 25 MHz Crystal      | XRCGB25M000F3M00R0 | R40,R41 | R116    |

#### 2.3.3.2 Reset

The AM64x SoC has the following resets:

- RESETSTATz is the warm reset status output for Main domain.

- PORz OUT is the power ON reset status output from Main and MCU domain.

- MCU PORz is the power ON/ Cold Reset input for MCU and Main domain.

- MCU\_RESETz is the warm reset input for MCU domain.

MCU\_RESETSTATz is the Warm Reset status output for MCU domain.

SoC\_PORz signal is provided by ANDing the PGOOD signal of PMIC and JTAG emulator reset. MCU\_PORz is provided by ANDing the CONN\_MCU\_PORz from MCU Connector, TEST\_PORZn from Test Automation Connector and SoC\_PORz.

MCU Domain warm reset (MCU\_RESETz) and MCU Domain cold reset (MCU\_PORz) of the SoC is achieved by CONN MCU RESETz and CONN MCU PORz respectively from the Safety Connector.

Upon Power on Reset, all peripheral devices connected to the main domain get reset by RESETSTATz along with a GPIO control as shown in Figure 2-7.

Figure 2-7. Overall Reset Architecture of the AM64x SK Event

#### 2.3.3.3 Power

#### 2.3.3.3.1 Power Input

The AM64x SK EVM receives 5 V input from a USB Type-C connector. The following sections describe the power distribution network topology that supply the SK EVM board, supporting components and reference voltages.

SK-AM64B EVM board includes a power solution based on PMIC and few discrete regulators. The initial stage of the power supply is 5 V from a Type-C USB connector with part No 2012670005 from Molex, which supports 3 A current rating and necessary protection circuits for over current and voltage surge. The 5 V input (VUSB\_MAIN) from the USB Connector is used to generate 3.3V (VCC3V3SYS\_EXT) with the help of switching regulator (part No. LM61460AASQRJRRQ1), which is the input supply to the PMIC section. PMIC generates necessary voltages required for the SKEVM.

An ON/OFF Toggle switch (with part number AS11AP) is provided to initiate the power on and power down sequence of the Board. This switch connects TPS6522053\_EN enable signal to ground when switch is in OFF position and enables PMIC TPS6522053RHBR when the switch is in ON position, thereby initiating the Power – Up Sequence. A low on enable pin of the TPS6522053RHBR PMIC by sliding the switch to OFF position initiates the Power-down Sequence.

Additionally, TEST\_POWERDOWN from the test automation header is also connected to the enable pin of TPS6522053RHBR PMIC to control on/off of the EVM via the test automation board. The test automation connector requires 3.3V supply, which is provided from power mux (part No: TPS2121RUXT). The inputs to the power mux are 3V3 from two different sources. First, 3V3 supply is generated from 5 V (XDS\_USB\_VBUS) using an LDO (Part No: TPS79601DRBR). This is generated as long as Micro B cable is connected to J12. Second,

Hardware www.ti.com

3V3 input is generated from 5 V (VUSB\_MAIN) using a switching Buck regulator (part No: TPS62177DQCR). This is an Always ON Regulator and is supplying the necessary power as long as the USB Type C Cable is plugged in. When Both Type C cable and Micro B cable at J12 are connected, the mux priority is set to the first input supply (VCC3V3\_XDS). If USB is not connected to the J12, then the mux output is from VCC3V3\_TA, which is an always ON power supply.

#### 2.3.3.3.2 USB Type-C Interface for Power Input

The AM64x SKEVM is powered through a USB type-C Connector. The USB Type-C source is capable of providing 3 A at 5 V and advertises the current sourcing capability through CC1 and CC2 signals. On SK EVM. CC1 and CC2 from the USB Type-C connector are interfaced to the TUSB320LAIRWBR port controller IC. This device uses the CC pins to determine port attach and detach, cable orientation, role detection, and port control for Type-C current mode. This IC allows for pin swapping when the Type-C cable is flipped and inserted. The CC logic block monitors the CC1 and CC2 pins for pull-up or pull-down resistances to determine when a USB port has been attached, the orientation of the cable, and the role detected. The CC logic detects the Type-C current mode as default, medium, or high depending on the role detected. Pin PORT is pulled down to ground through a resistor to configure as UFP (Upward Facing Port) mode. VBUS detection is implemented to determine a successful attach in UFP mode. Pin ADDR is left open to configure as GPIO mode. OUT1 and OUT2 pin is connected to a NOR gate. Active low on both OUT1 and OUT2 pin advertises high current (3 A) in the attached state which enables the VUSB\_MAIN power switch to provide the VUSB\_PMIC supply which powers one PMIC. In UFP mode, the TUSB320 device constantly presents pull-down resistors (Rd) on both CC pins. The TUSB320 device monitors the CC pins for the voltage level corresponding to the Type-C mode current advertisement by the connected DFP. The TUSB320 device de-bounces the CC pins and waits for VBUS detection before successfully attaching. As a UFP, the TUSB320 device detects and communicates the advertised current level of the DFP to the system through the OUT1 and OUT2 GPIOs. SKEVM power requirement is 5 V @ 3 A. If the source is not capable of providing 5 V at 3 A, output at the NOR gate becomes low which disables VUSB Main power switch. Hence all power supplies except VCC3V3\_TA remain in the off state. The board gets powered ON completely only when the source is capable of providing 5 V at 3 A.

Figure 2-8. USB Type-C Interface for Power Input

Table 2-4. Current Sourcing Capability and State of USB Type C Cable

| OUT1 | OUT2 | Advertisement                           |

|------|------|-----------------------------------------|

| Н    | Н    | Default current in unattached state     |

| Н    | L    | Default current in attached state       |

| L    | Н    | Medium current (1.5A) in attached state |

| L    | L    | High current (3.0A) in attached state   |

### 2.3.3.3.3 Power Fault Indication

Red led LD15 is used to indicate power fault condition (for example, current less than 3A) by using USB type C configuration channel logic and port controller IC.

**Table 2-5. Power Fault Indication LED**

| LED  | ON Status                     | OFF Status                             |  |

|------|-------------------------------|----------------------------------------|--|

| LD15 | Source provides less than 15W | Source provides the required 15W power |  |

# 2.3.3.3.4 Power Supply

The SK-AM64B EVM board utilizes one PMIC and three discrete regulators to supply the necessary voltage and power to SOC, various memories, Wi-link module and other peripherals on the board. Probe points for power supplies provided on the SKEVM Board are mentioned in Table 2-6.

**Table 2-6. Power Test Points**

| SI. No | Power Supply          | Probe Point | Ground     | Probe Point  | Expected Voltage |

|--------|-----------------------|-------------|------------|--------------|------------------|

| 31. NO | Power Supply          |             |            | Probe Politi | (V)              |

|        |                       | Points on   | •          |              |                  |

| 1      | VUSB_MAIN             | TP28        | DGND       | J3.2         | 5                |

| 2      | XDS_USB_VBUS          | TP75        | DGND       | J3.2         | 5                |

| 3      | VCC_3V3_SYS           | TP80        | DGND       | J3.2         | 3.3              |

| 4      | VDDAR_CORE            | TP85        | DGND       | J3.2         | 0.85             |

| 5      | VPP_1V8               | TP89        | DGND       | J3.2         | 0                |

| 6      | VDD_CORE              | TP81        | DGND       | J3.2         | 0.75             |

| 7      | VDD_LPDDR4            | TP83        | DGND       | J3.2         | 1.1              |

| 8      | VDD_1V0               | TP88        | DGND       | J3.2         | 1                |

| 9      | VCC1V8                | TP82.       | DGND       | J3.2         | 1.8              |

| 10     | VDD_PHY_2V5           | TP87        | DGND       | J3.2         | 2.5              |

| 11     | VDDSHV_SD_IO_PM<br>IC | TP84        | DGND       | J3.2         | 3.3              |

| 12     | VDD_MMC1              | C47.1       | DGND       | J3.2         | 3.3              |

| 13     | VBUS_USB_CP2105       | TP76        | DGND       | J3.2         | 5                |

| 14     | VCC3V3_XDS            | TP74        | DGND       | J3.2         | 3.3              |

| 15     | VDDSHV_SD_IO          | TP15        | DGND       | J3.2         | 3.3              |

|        |                       | Points on B | ottom Side | 1            |                  |

| 16     | VCC3V3SYS_EXT         | TP78        | DGND       | J3.2         | 3.3              |

| 17     | VDDA_1V8              | TP86        | DGND       | J3.2         | 1.8              |

| 18     | VCC3V3_TA             | C340.1      | DGND       | J3.2         | 3.3              |

| 19     | VCC3V3_TA_XDS         | C421.1      | DGND       | J3.2         | 3.3              |

Hardware www.ti.com

Table 2-7 gives details about power-good LEDs provided on SKEVM board to give users positive confirmation of the status of each supply. Figure 2-7 highlights the power-good LEDs in SK EVM board.

| Tah | le 2- | 7 P | owe | r I | FDs |

|-----|-------|-----|-----|-----|-----|

|     |       |     |     |     |     |

| SI.No | Power Supply      | LED Part Reference |

|-------|-------------------|--------------------|

| 1     | VCC3V3SYS_EXT     | LD2                |

| 2     | VCC_3V3_SYS       | LD16               |

| 3     | VDDAR_CORE        | LD16               |

| 4     | VDDA_1V8          | LD16               |

| 5     | VDD_LPDDR4        | LD16               |

| 6     | VDD_CORE          | LD16               |

| 7     | VCC1V8            | LD16               |

| 8     | VDDSHV_SD_IO_PMIC | LD16               |

| 9     | VDD_PHY_2V5       | LD16               |

| 10    | VDDA_1V8          | LD16               |

| 11    | VDD_CP2105        | LD18               |

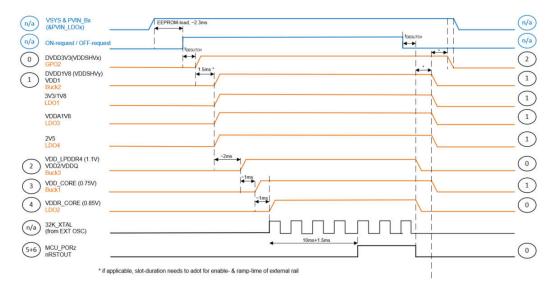

# 2.3.3.3.5 Power Sequencing

Figure 2-9 shows the Power Up and Power Down Sequence of all the Power supplies present on the SK EVM Board.

Figure 2-9. Power-Up and Power-Down Sequencing

#### 2.3.3.3.6 Power Supply

The SoC Core voltage (VDD\_CORE) of the AM64x SoC is set to 0.75V. SoC Array Core Voltage (VDDR\_CORE) and other array core voltages (VDDA\_0P85\_SERDES0\_C, VDDA\_0P85\_SERDES0, VDDA\_0P85\_USB0, VDD\_DLL\_MMC0 and VDD\_MMC0) are configured to 0.85V and are supplied through a common rail.

The SoC has different IO groups. Each IO group is powered by specific power supplies as given in Table 2-8.

Table 2-8. SoC Power Supply

| SI.No | Power Supply             | SoC Supply Rails        | IO Power Group | Power |

|-------|--------------------------|-------------------------|----------------|-------|

| 1     | VDDAR_CORE               | VDDA_0P85_SERDES0       | SERDES0        | 0.85  |

|       |                          | VDDA_0P85_SERDES0_<br>C |                | 0.85  |

|       |                          | VDDA_0P85_USB0          | USB0           | 0.85  |

|       |                          | VDD_MMC0                | MMC0           | 0.85  |

|       |                          | VDDR_CORE               | CORE           | 0.85  |

| 2     | SoC_DVDD3V3              | VDDSHV_MCU              | MCU            | 3.3   |

|       |                          | VDDA_3P3_USB0           | USB0           | 3.3   |

|       |                          | VDDSHV0                 | General        | 3.3   |

|       |                          | VDDSHV1                 | PRG0           | 3.3   |

|       |                          | VDDSHV2                 | PRG1           | 3.3   |

|       |                          | VDDSHV3                 | GPMC           | 3.3   |

|       |                          | VMON_3P3_MCU            |                | 3.3   |

|       |                          | VMON_3P3_SOC            |                | 3.3   |

| 3     | VDDA_1V8_MCU             | VDDA_MCU                | MCU            | 1.8   |

| 4     | VDDA_1V8_SERDES          | VDDA_1P8_SERDES0        | SERDES0        | 1.8   |

| 5     | VDDA_1V8_USB0            | VDDA_1P8_USB0           | USB0           | 1.8   |

| 6     | VDDA_1V8                 | VDDS_OSC                | OSC0           | 1.8   |

|       |                          | VDDA_TEMP_0/1           |                | 1.8   |

|       |                          | VDDA_PLL_0/1/2          |                | 1.8   |

| 7     | VDDS_DDR                 | VDDS_DDR                | DDR0           | 1.1   |

|       |                          | VDDS_DDR_C              |                | 1.1   |

| 8     | SOC_DVDD1V8              | VDDSHV4                 | FLASH          | 1.8   |

|       |                          | VDDS_MMC0               | MMC0           | 1.8   |

|       |                          | VMON_1P8_MCU            |                | 1.8   |

|       |                          | VMON_1P8_SOC            |                | 1.8   |

| 9     | VDDSHV_SD_IO             | VDDSHV5                 | MMC1           | 3.3   |

| 10    | VDDS_MMC0/<br>ADC0_VREFP | VDDS_MMC0               | MMC0           | 0     |

Hardware Www.ti.com

#### 2.3.3.4 Configuration

#### 2.3.3.4.1 Boot Modes

The boot mode for the SK EVM board is defined by two banks of switches, SW2 and SW3, or by the I2C buffer connected to the test automation connector. This allows for AM64x boot mode control by either the user (DIP Switch Control) or the test automation header. At the minimum, all the boot mode pins require a footprint for a pull-up or pull-down resistor. Any boot mode pin that must be toggled to support a needed boot mode must have a weak pull-down resistor and a switch (416131160808 from Wurth) capable of connecting a stronger pull-up resistor. The switch disconnects the pull-up resistor in the OFF position. For boot mode pins that are not controlled by switches, pull-up and pull-down resistor pads are included. Various boot modes for AM64x must be controlled by the user with the help of 8-Bit DIP switches. The following boot modes are supported by SK EVM:

- OSPI

- MMC1 SD-Card

- CSPW Ethernet

- USB devices

The boot mode pins of the SoC have associated alternate functions during normal operation. Hence, isolation is provided using the Buffer IC to cater for alternate pin functionality. The output of the buffer is connected to the bootmode pins ON the AM64x and the output is enabled when the bootmode is needed during a reset cycle. The input to the buffer is connected to the DIP switch circuit and to the output of an I2C buffer set by the test automation circuit. If the test automation circuit is going to control the bootmode, then all the switches are manually set to the OFF position. The bootmode buffer are powered by an always ON power supply to make sure that the bootmode remains present even if the SoC power is cycled..

Figure 2-10 and Table 2-9 provide guidance to select the boot mode before the device is powered up.

Note: Actual Board Silkscreen May Appear Inverted in this Orientation. Follow Physical Switch Text

Figure 2-10. Bootmode Switch Positions Example

Table 2-9. BOOT-MODE Pin Mapping

| Bit 15       | Bit 14       | Bit 13                                      | Bit 12 | Bit 11  | Bit 10 | Bit 9              | Bit 8             | Bit 7 | Bit 6   | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1      | Bit 0 |

|--------------|--------------|---------------------------------------------|--------|---------|--------|--------------------|-------------------|-------|---------|---------|-------|-------|--------|------------|-------|

| Reserv<br>ed | Reserv<br>ed | Backup<br>Boot<br>Mode<br>Config<br>uration | Backup | Boot Mo | de     | Primary<br>Configu | Boot Mo<br>ration | de    | Primary | Boot Mo | de    |       | PLL Co | nfiguratio | on    |

• BOOT-MODE [0:2] – Denote system clock frequency for PLL configuration. By default, this bits are set for 25 MHz.

Table 2-10 gives details ON PLL reference clock selection.

Table 2-10. PLL Reference Clock Selection BOOTMODE [2:0]

| 14510 2 10:1 22 Kolololio Glock Golockich Boo 1 1110 22 [2:0] |       |       |                                               |  |  |  |

|---------------------------------------------------------------|-------|-------|-----------------------------------------------|--|--|--|

| SW3.6                                                         | SW3.7 | SW3.8 | PLL REF CLK (MHz)                             |  |  |  |

| OFF                                                           | OFF   | OFF   | 19.2                                          |  |  |  |

| OFF                                                           | OFF   | ON    | 20                                            |  |  |  |

| OFF                                                           | ON    | OFF   | 24                                            |  |  |  |

| OFF                                                           | ON    | ON    | 25                                            |  |  |  |

| ON                                                            | OFF   | OFF   | 26                                            |  |  |  |

| ON                                                            | OFF   | ON    | 27                                            |  |  |  |

| ON                                                            | ON    | OFF   | Reserved                                      |  |  |  |

| ON                                                            | ON    | ON    | No PLL Configuration Done (slow speed backup) |  |  |  |

• BOOT-MODE [3:6] – This provides primary boot mode configuration to select the requested boot mode after POR, that is, the peripheral/memory to boot from. Table 2-11 provides primary boot device selection details.

Table 2-11. Boot Device Selection BOOT-MODE [6:3]

| Table 2-11. Door Device Selection DOO1-MODE [0.5] |       |       |       |                                 |  |  |  |

|---------------------------------------------------|-------|-------|-------|---------------------------------|--|--|--|

| SW3.2                                             | SW3.3 | SW3.4 | SW3.5 | Primary Boot Device<br>Selected |  |  |  |

| OFF                                               | OFF   | OFF   | OFF   | Reserved                        |  |  |  |

| OFF                                               | OFF   | OFF   | ON    | OSPI                            |  |  |  |

| OFF                                               | OFF   | ON    | OFF   | QSPI                            |  |  |  |

| OFF                                               | OFF   | ON    | ON    | SPI                             |  |  |  |

| OFF                                               | ON    | OFF   | OFF   | Ethernet RGMII                  |  |  |  |

| OFF                                               | ON    | OFF   | ON    | Ethernet RMII                   |  |  |  |

| OFF                                               | ON    | ON    | OFF   | I2C                             |  |  |  |

| OFF                                               | ON    | ON    | ON    | UART                            |  |  |  |

| ON                                                | OFF   | OFF   | OFF   | MMC/SD card                     |  |  |  |

| ON                                                | OFF   | OFF   | ON    | emmc                            |  |  |  |

| ON                                                | OFF   | ON    | OFF   | USB                             |  |  |  |

| ON                                                | OFF   | ON    | ON    | Reserved                        |  |  |  |

| ON                                                | ON    | OFF   | OFF   | GPMC NOR                        |  |  |  |

| ON                                                | ON    | OFF   | ON    | PCle                            |  |  |  |

| ON                                                | ON    | ON    | OFF   | xSPI                            |  |  |  |

| ON                                                | ON    | ON    | ON    | No boot/Dev Boot                |  |  |  |

<sup>•</sup> BOOT-MODE [10:12] – Select the backup boot mode, that is, the peripheral/memory to boot from, if primary boot device failed.

Table 2-12 provides backup boot mode selection details.

Hardware www.ti.com

Table 2-12. Backup Boot Mode Selection BOOT-MODE [12:10]

|       |       | -     | <b>-</b>                    |

|-------|-------|-------|-----------------------------|

| SW2.4 | SW2.5 | SW2.6 | Backup Boot Device Selected |

| OFF   | OFF   | OFF   | None (No backup mode)       |

| OFF   | OFF   | ON    | USB                         |

| OFF   | ON    | OFF   | Reserved                    |

| OFF   | ON    | ON    | UART                        |

| ON    | OFF   | OFF   | Ethernet                    |

| ON    | OFF   | ON    | MMC/SD                      |

| ON    | ON    | OFF   | SPI                         |

| ON    | ON    | ON    | I2C                         |

• BOOT-MODE [9:7] – These pins provide optional settings and are used in conjunction with the primary boot device selected.

Table 2-13 gives primary boot media configuration details.

Table 2-13. Primary Boot Media Configuration BOOT-MODE [9:7]

| SW2.7     | SW2.8    | SW3.1     | Boot Device      |  |

|-----------|----------|-----------|------------------|--|

|           | Reserved |           | Reserved         |  |

| Speed     | Iclk     | Csel      | OSPI             |  |

| Reserved  | Iclk     | Csel      | QSPI             |  |

| Reserved  | Mode     | Csel      | SPI              |  |

| Clkout    | Delay    | Link stat | Ethernet RGMII   |  |

| Clkout    | Clk src  | Reserved  | Ethernet RMII    |  |

| Bus Reset | Reserved | Addr      | I2C              |  |

| Re        | Reserved |           | UART             |  |

| Port      | Reserved | Fs/raw    | MMC/ SD card     |  |

| Re        | Reserved |           | eMMC             |  |

| Reserved  | Mode     | Lane swap | USB              |  |

|           | Reserved | 1         | Reserved         |  |

|           | Reserved |           |                  |  |

| Re        | Reserved |           | PCle             |  |

| Speed     | Pin Cmd  | Csel      | xSPI             |  |

| Re        | Reserved |           | No boot/Dev Boot |  |

- BOOT-MODE [13] These pins provide optional settings and are used in conjunction with the backup boot device devices. Switch SW2.6 when ON sets 1 and sets 0 if OFF, see the device-specific TRM.

- BOOT-MODE [14:15] Reserved.

Table 2-14 provides backup boot media configuration options.

Table 2-14. Backup Boot Media Configuration BOOT-MODE [13]

| Table 2 14: Backap Boot Media Configuration Boot Mobb [10] |             |  |  |  |

|------------------------------------------------------------|-------------|--|--|--|

| SW2.3                                                      | Boot Device |  |  |  |

| Reserved                                                   | None        |  |  |  |

| Mode                                                       | USB         |  |  |  |

| Reserved                                                   | Reserved    |  |  |  |

| Reserved                                                   | UART        |  |  |  |

| IF                                                         | Ethernet    |  |  |  |

| Port                                                       | MMC/SD      |  |  |  |

| Reserved                                                   | SPI         |  |  |  |

| Reserved                                                   | I2C         |  |  |  |

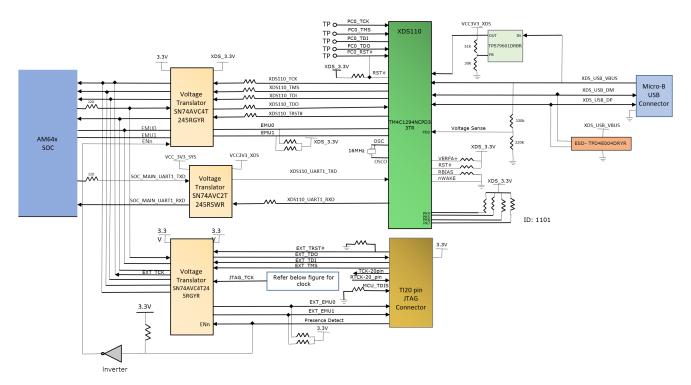

#### 2.3.3.5 JTAG

Optionally, a JTAG Interface on SKEVM is also provided through a 20 Pin Standard JTAG cTI Header (J14). This allows the user to connect an external JTAG Emulator. Voltage translation buffers are used to isolate the JTAG signals from the cTI header from the rest of the EVM. The output from the voltage translators from the XDS110 Section and cTI Header Section is muxed and connected to the SoC JTAG Interface. If a connection to the cTI 20 Pin JTAG connector is sensed using a present detect circuit, then the mux are set to route the 20pin signals to the AM64x in place of the on-board emulation circuit.

The pin-outs of cTI 20 pin JTAG connector J14 are given in Table 2-15. An ESD protection (part number TPD4E004) is provided on the USB signals to steer ESD current pulses to VCC or GND. TPD4E004 protects against ESD pulses up to ±15-kV Human-Body Model (HBM) as specified in IEC 61000-4-2 and provides ±8-kV contact discharge and ±12- kV air-gap discharge. For cTI 20 pin connector pin-out details, see Table 2-15.

|         | 144.00 = 101.011 = 0.111.0000. (0.1.) 1.111.0000 |         |               |  |  |  |  |

|---------|--------------------------------------------------|---------|---------------|--|--|--|--|

| Pin No. | Signal                                           | Pin No. | Signal        |  |  |  |  |

| 1       | JTAG_TMS                                         | 11      | JTAG_cTI_TCK  |  |  |  |  |

| 2       | JTAG_TRST#                                       | 12      | DGND          |  |  |  |  |

| 3       | JTAG_TDI                                         | 13      | JTAG_EMU0     |  |  |  |  |

| 4       | JTAG_TDIS                                        | 14      | JTAG_EMU1     |  |  |  |  |

| 5       | VCC_3V3_SYS                                      | 15      | JTAG_EMU_RSTN |  |  |  |  |

| 6       | NC                                               | 16      | DGND          |  |  |  |  |

| 7       | JTAG_TDO                                         | 17      | NC            |  |  |  |  |

| 8       | SEL_XDS110_INV                                   | 18      | NC            |  |  |  |  |

| 9       | JTAG_cTI_RTCK                                    | 19      | NC            |  |  |  |  |

| 10      | DGND                                             | 20      | DGND          |  |  |  |  |

Figure 2-11. JTAG Interface

The SKEVM board includes XDS110-class on board emulation and a test automation header to support TI internal testing of software builds. The connection for the emulator uses an USB2.0 micro-B connector (J12) and the circuit acts as a powered USB slave device. The VBUS power from the connector is used to power the

Hardware www.ti.com

emulation circuit such that connection to the emulator is not lost when the power to the EVM is removed. Voltage translation buffers are used to isolate the XDS110 circuit from the rest of the EVM. Additionally, XDS110 also offers UART to USB signal translation on the same USB port. UART1 of the SoC MAIN Domain without flow control is connected to the XDS110 UART port via an isolator.

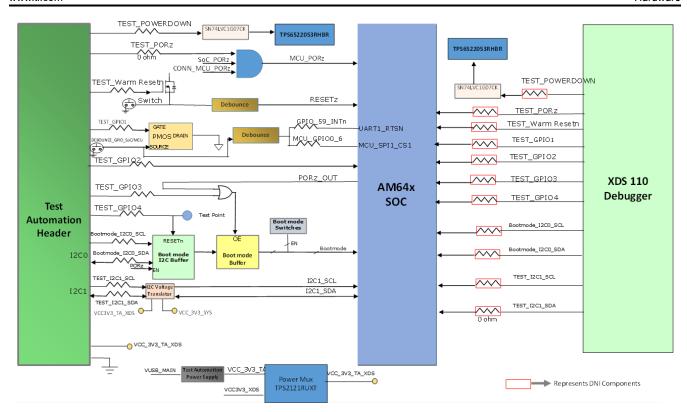

#### 2.3.3.6 Test Automation

The SKEVM has a 40 pin test automation header (J16) to allow an external controller to manipulate some basic operations like Power Down, POR, Warm Reset, Boot Mode control, etc. The test automation header includes four GPIOs and two I2C interfaces (I2C1, Boot mode I2C0).

The test automation circuit has voltage translation circuits so that the controller is isolated from the IO voltages used by the AM64x. Boot mode for the AM64x must be controlled by either the user using DIP Switches or the test automation header through the I2C IO Expander.

Boot Mode Buffers are used to isolate the Boot Mode controls driven through DIP Switches or I2C IO Expanders. Power to Test Automation Circuit is provided from a Power Mux (TPS2121RUXT) which is having the input supplies VCC3V3\_TA supply generated from a dedicated regulator and VCC3V3\_XDS generated from an LDO (it is the supply for XDS110 Debugger section). The basic controls of test automation header J16 are as follows. Table 2-16 gives details about test automation header signals.

Optionally, the Test Automation header functionality can be implemented by the XDS110 controller. Hence resistor options (R420, R421, R422, R423, R424, R425, R426, R427, R436, R437, R438 and R439) are provided for Power Down, POR, Warm Reset, Boot Mode controls and GPIO signals. By default these resistors are made as DNI so that an external controller controls the basic operations through the Automation header. Once the firmware for the XDS110 is developed, then mount the above mentioned resistors and DNI the following resistors R380, R381, R382, R383, R384, R385, R386, R432, R433, R434 and R435 to control the basic operations through the XDS110 microcontroller.

Proper Isolation to be provided on Boot Mode signals to allow normal operation. SoC\_I2C [1] connected to test automation header to communicate with external controller.

One of the I2C interfaces from Test automation header is connected to the Boot mode buffer to control the boot mode of AM64x and another I2C interface is connected to the I2C1 port of AM64x.

Table 2-16 lists the reset signals routed from test automation header. The boot mode for the AM64x can be controlled by either the user or the test automation header. The boot mode is controlled by the user using two separate 8-positions DIP switches on the board. The switches connect a pull-up resistor to the output of a buffer when the switch is set to ON position. When the switch is off, a weaker pull-down resistor holds the signal low. The output of the buffer is connected to the boot mode pins on the AM64x and the output is enabled when the boot mode is needed during a reset cycle and the input of buffer is connected to output of an I2C buffer set by the test automation circuit.

| Table 2-16. List of Signals Routed to Test Automation Header J16 |             |          |  |

|------------------------------------------------------------------|-------------|----------|--|

|                                                                  | Signal Type | Function |  |

| Signal        | Signal Type | Function                                     |  |

|---------------|-------------|----------------------------------------------|--|

| POWER_DOWN    | GPIO        | Instructs the EVM to power down all circuits |  |

| PORZn         | GPIO        | Creates a PORz to the AM64X                  |  |

| WARM_RESETn   | GPIO        | Creates a RESETz to the AM64X                |  |

| GPIO1         | GPIO        | GPIO for communication with AM64X            |  |

| GPIO2         | GPIO        | GPIO for communication with AM64X            |  |

| GPIO3         | GPIO        | Used to Enable the BOOTMODE Buffer           |  |

| GPIO4         | GPIO        | Used to Reset the Boot mode IO Expander      |  |

| Bootmode I2C0 | I2C         | Communicates with boot mode I2C buffer       |  |

| I2C1          | 12C         | Communicates with AM64x                      |  |

If the test automation circuit is going to control the boot mode, then all the switches have to be manually be set to the off position. The pins used for boot mode also have other functions, which is isolated by disabling the boot mode buffer during normal operation. Figure 2-12 shows the test automation signal connection with AM64x.

Figure 2-12. Test Automation Header

Test Automation Header signals are optionally connected to the XDS110 microcontroller via zero ohm resistors. By default those resistors are made as DNI.

Table 2-17. Automation Header Signals Connected to XDS110

| TM4C1294 Pin Name | Signal Name     |

|-------------------|-----------------|

| PM0               | TEST_POWERDOWN  |

| PM1               | TEST_PORZn      |

| PM2               | TEST_WARMRESETn |

| PM3               | TEST_GPI01      |

| PM4               | TEST_GPIO2      |

| PM5               | TEST_GPIO3      |

| PM6               | TEST_GPIO4      |

| PM7               | TEST_POWERDOWN  |

| PG0               | TEST_PORZn      |

| PG1               | TEST_WARMRESETn |

Hardware www.ti.com

Table 2-18 lists test automation header's pin-out and IO direction.

# Table 2-18. Test Automation Header (J16) Pin-Outs

| Pin No. | IO Direction (wrt SoC) |               |

|---------|------------------------|---------------|

| 1       | Signal Name VCC3V3_TA  | Power (out)   |

| 2       | VCC3V3_TA              | Power (out)   |

| 3       | VCC3V3_TA              | Power (out)   |

| 4       | NC NC                  | NA            |

| 5       | NC                     | NA            |

| 6       | NC                     | NA            |

| 7       | DGND                   | Ground        |

| 8       | NC                     | NA            |

| 9       | NC                     | NA            |

| 10      | NC                     | NA            |

| 11      | NC                     | NA            |

| 12      | NC                     | NA            |

| 13      | NC                     | NA            |

| 14      | NC                     | NA            |

| 15      | NC                     | NA            |

| 16      | DGND                   | Ground        |

| 17      | NC                     | NA            |

| 18      | NC                     | NA            |

| 19      | NC                     | NA            |

| 20      | NC                     | NA            |

| 21      | NC                     | NA            |

| 22      | NC                     | NA            |

| 23      | NC                     | NA            |

| 24      | NC                     | NA            |

| 25      | DGND                   | Ground        |

| 26      | TEST_POWERDOWN         | Input         |

| 27      | TEST_PORZn             | Input         |

| 28      | TEST_WARMRESETn        | Input         |

| 29      | NC                     | NA            |

| 30      | TEST_GPIO1             | Bidirectional |

| 31      | TEST_GPIO2             | Bidirectional |

| 32      | TEST_GPIO3             | Input         |

| 33      | TEST_GPIO4             | Input         |

| 34      | DGND                   | Ground        |

| 35      | NC                     | NA            |

| 36      | SOC_I2C1_TA_SCL        | Bidirectional |

| 37      | BOOTMODE_I2C_SCL       | Bidirectional |

| 38      | SOC_I2C1_TA_SDA        | Bidirectional |

| 39      | BOOTMODE_I2C_SDA       | Bidirectional |

| 40      | DGND                   | Ground        |

| 41      | DGND                   | Ground        |

| 42      | DGND                   | Ground        |

|         |                        |               |

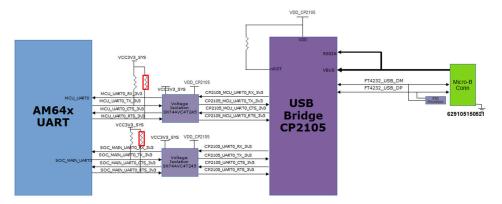

#### 2.3.3.7 UART Interface

The two UART ports MAIN\_UART0 and MCU\_UART0 provided by AM64x are connected to two channel USB to UART Bridge (CP2105) and terminated to a USB Micro B Connector J11. Two ports of the CP2105, connected to MAIN\_UART0 and MCU\_UART0 with the RXD, TXD, RTS and CTS signals.

The USB interface circuit is used in bus powered configuration and a voltage translator (SN74AVC4T245) is used to isolate AM64x IOs. The CP2105 includes an on-chip 5 to 3.45 V voltage regulator. This allows the CP2105 to be configured as a USB bus-powered device. The voltage regulator output appears on the VDD pin and can be used to drive the IO supply as well as one of the supply rails of voltage Translator. Internally the same VDD is used to operate the core section of CP2105. CP2105 also includes an integrated clock and hence no external crystal is required. MAIN\_UART0 and MCU\_UART0 from SOC are at 3.3V IO level. The devices uses the internal POR Circuit. For normal Operation, the nRST pin needs to be pulled up to 3V3 Supply via 10K Resistor. Since the Device operates in Bus Powered Configuration, VBUS from the USB Connector needs to be connected to "REGIN" pin of CP2105 to serve as the input for the internal regulator.

A ESD protection is provided on USB signals to steer ESD current pulses to VCC or GND. TPD4E004 protects against ESD pulses up to ±15-kV Human-Body Model (HBM) as specified in IEC 61000-4-2 and provides ±8-kV contact discharge and ±12- kV air-gap Discharge. Figure 2-13 shows the dual UART to USB bridge connection with AM64x.

Figure 2-13. UART Interface

Hardware Www.ti.com

#### 2.3.3.8 Memory Interfaces

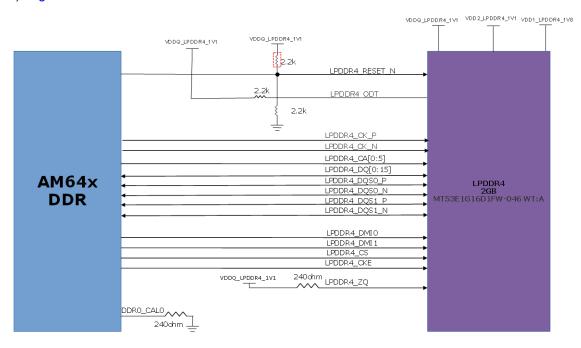

#### 2.3.3.8.1 LPDDR4 Interface

The SK EVM has 2GB, 16bit wide LPDDR4 memory with operating data rate of 4226Mbps per pin. Micron's MT53E1G16D1FW-046 WT: A is used. The LPDDR memory is mounted on-board (single chip) and requires 1.1V and thus reduces power demand. The LPDDR4 device requires I/O power and core 2 power of 1.1V, DRAM activating power supply (core 1) of 1.8V.

LPDDR4 reset is active low signal, which is controlled by SOC and the signal is pulled up to set the default active state and a footprint for pull-down is also provided. A 240  $\Omega$  resistor is connected from ZQ pin to 1.1V supply for LPDDR4 device and SoC DDR0\_CAL pin is grounded.

The ODT (On Die Termination) is applied to DQ, DQS and DM\_n signals. The device is capable of providing three different ODT modes: Nominal, Dynamic and Park with termination values: RTT (Park), RTT (NOM), and RTT (WR). Figure 2-14 shows the DDR interface between LPDDR4 and AM64x.

Figure 2-14. LPDDR4 Interface

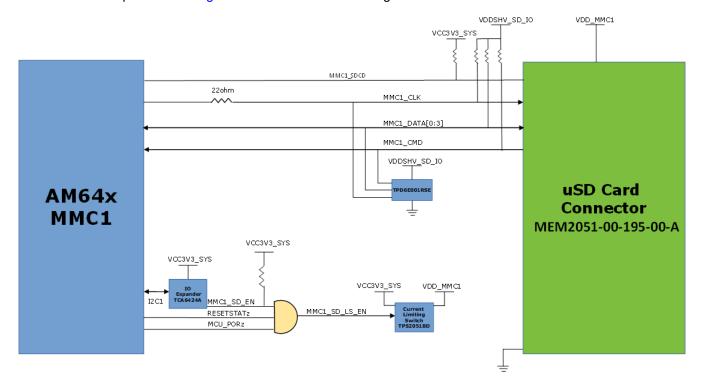

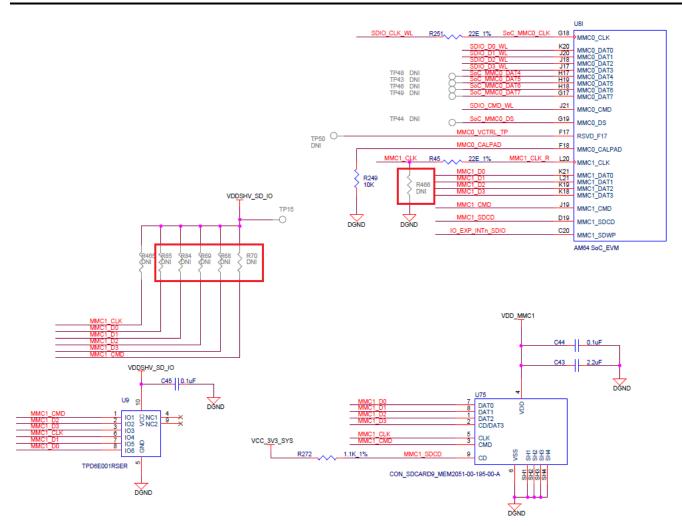

### 2.3.3.8.2 MMC Interface

The AM64x processor provides two MMC interfaces. Out of which, one is connected to Wilink Module and other is used for micro SD card interface.

## 2.3.3.8.2.1 Micro SD Interface

The SKEVM board provides a micro SD card interface connected to MMC1 port of AM64x SOC. The micro-SD card interface supports 16 GB density with UHS1 operation including IO operations at both 1.8V and 3.3V. The circuit included in AM64x SoC to support the IO voltage switching is connected to IO voltage of SD signals to allow the processor to negotiate IO voltage. For high-speed cards, ROM Code of SOC attempts to find the fastest speed that the card and controller can support and can have a transition to 1.8V. The internal SDIO LDO output from the SOC available at CAP\_VDDSHV\_SDLDO pin is connected to IO voltage of SD signals and VDDSHV MMC1 power pins of SOC, which is the power supply for MMC1 interface.

An ESD protection device (TPD6E001RSE) is provided for data, clock and command signals. TPD6E001RSE is a line termination device with integrated TVS diodes providing system-level IEC 61000-4-2 ESD protection,  $\pm$  8-kV contact discharge and  $\pm$  15kV air-gap discharge.

The SD card is set to operate in SD mode. The CD (card detect) pin of SD card connector is pulled low and connected to CD pin of SOC. Figure 2-15 shows the block diagram of micro-SD card interface.

Figure 2-15. Micro SD Interface

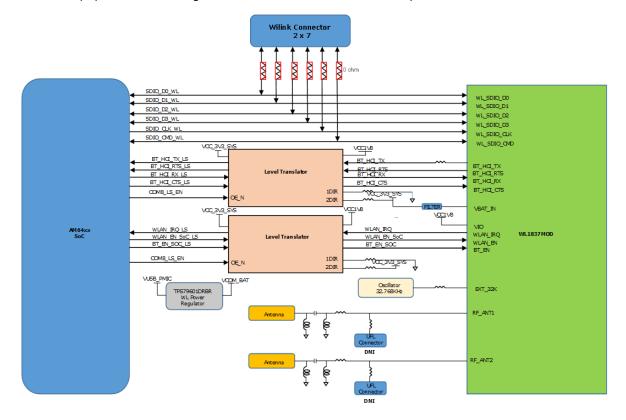

#### 2.3.3.8.2.2 WiLink Interface

The SKEVM board has WiLink Module (WL1837MODGIMOCT) from TI connected to MMC0 port of the AM64x SoC. The WL1837MOD is a Wi-Fi, dual-band, 2.4- and 5-GHz module solution with two antennas (W3006) supporting Industrial temperature grade. The Module is connected to 4-bit IO of the MMC0 interface supporting IEEE standard 802.11a/b/g/n data rates with 20 or 40-MHz SISO or 20-MHz MIMO. The Module offers high throughput and extended range along with Wi-Fi and Bluetooth coexistence in a power-optimized design.

The device supports the following Bluetooth features:

- Bluetooth 4.2 secure connection as well as CSA2

- Concurrent operation and built-in coexisting and prioritization handling of Bluetooth and Bluetooth low energy wireless technology, audio processing, and WLAN

- Dedicated audio processor supporting on-chip SBC encoding + A2DP

- Assisted A2DP (A3DP): SBC encoding implemented internally

- Assisted WB-speech (AWBS): modified SBC codec implemented internally. Figure 2-16 shows the block diagram of Wilink module interfaced with AM64x.

SKEVM does not support A2DP BT Audio profile or HF profile.

The Module requires two power supplies, 3.3V for VBAT\_IN and 1.8V for VIO\_IN. WL1837MOD WiLink module is supplied from PMIC and also provided through a dedicated regulator (This is optional and DNI by default).

The MMC0 interface of SOC is powered by VDDSHV\_MMC0 power supply, which is connected to 1.8V IO supply. Bluetooth UART signals, enable of BT and WLAN and WLAN\_IRQ signals are connected to GPIO's of AM64x using level translator (SN74AVC4T245RSVR). Input clock is provided by using 32.768 KHz oscillator.

Test points are provided on MMC0\_DAT [4:7] pins of SOC and WL\_GPIO, BT\_UART\_DEBUG, WL\_UART\_DEBUG pins on WL1837 Module.

Hardware www.ti.com

14 pin Wi-link connector is also provided. An external Wi-Fi module (Bluetooth module is not supported) can be communicated with SoC through the 14 pin Wi-Link connector. By default, 14 pin Wi-link connector and 0E resistors are not populated on the signals which are connected to the 14 pin Wi-link connector

Figure 2-16. WiLink Module Interface

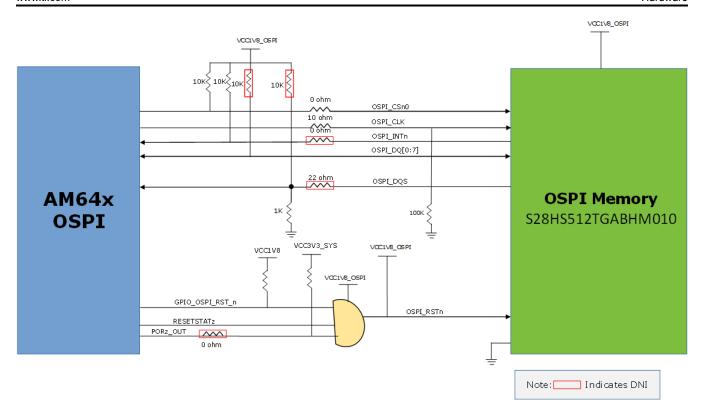

#### 2.3.3.8.2.3 OSPI Interface

The SK EVM board has 512 Mbit OSPI memory device of part number S28HS512TGABHM010 from Cypress is connected to OSPI0 interface of AM64x SOC. The OSPI supports memory speed up to 166 MHz. The OSPI flash is powered by 1.8V IO supply. The 1.8V supply is provided to both VCC and VCCQ pins of the flash memory.

The reset for the flash is connected to a circuit that ANDs the RESETSTATz, PORz\_OUT and OSPI0\_CSN2 (GPI0\_OSPI\_RSTn) from SoC. This applies reset for warm and cold reset. A pull-up is provided on GPI0\_OSPI\_RSTn coming from SOC pin to set the default active state.

Two signals are routed to OSPI0 DQS:

- 1. OSPI0\_DQS from the memory device

- 2. OSPI0\_LBCLK from SoC

To route DQS from memory device: DNI R33 & R39.

To route OSPI0 LBCLK from SoC: Mount R33 & R39.

OSPI & QSPI implementation: 0 ohm resistors are provided for DATA [7:0], DQS, INT# and CLK signals. Footprints to mount external pull up resistors are provided on DATA [7:0] to prevent bus floating.

Figure 2-17 shows the OSPI interface block diagram for AM64x SK EVM.

Figure 2-17. OSPI Interface

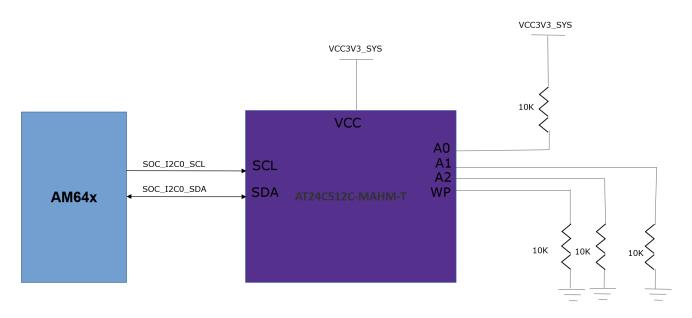

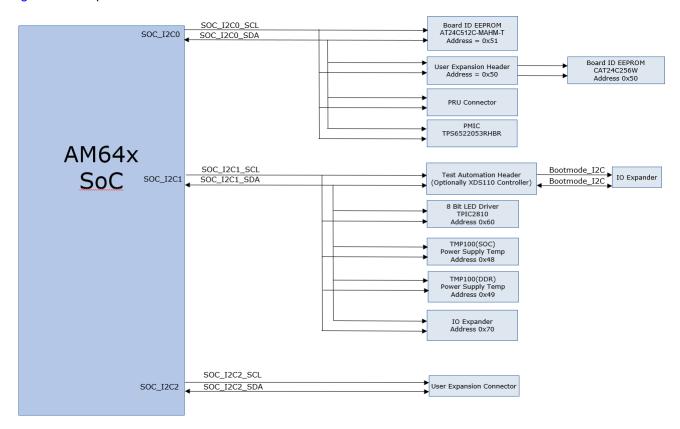

#### 2.3.3.8.2.4 Board ID EEPROM Interface

The AM64x processor is identified by the version and serial number, which are stored in the onboard EEPROM. The Board ID memory shall be configured to respond to address 0x51. AT24C512C-MAHM-T from Microchip is used, this is interfaced to I2C0 port of the SOC. I2C address of the EEPROM can be modified by driving the A0, A1, A2 pins to LOW. The write-protect input, when connected to GND, allows normal write operations. When the WP pin is connected directly to VCC, all write operations to the protected memory are inhibited. If the pin is left floating, then the WP pin is internally pulled down to GND. Here, WP is connected through GND through 10k resistor.

Figure 2-18. Board ID EEPROM

Hardware www.ti.com

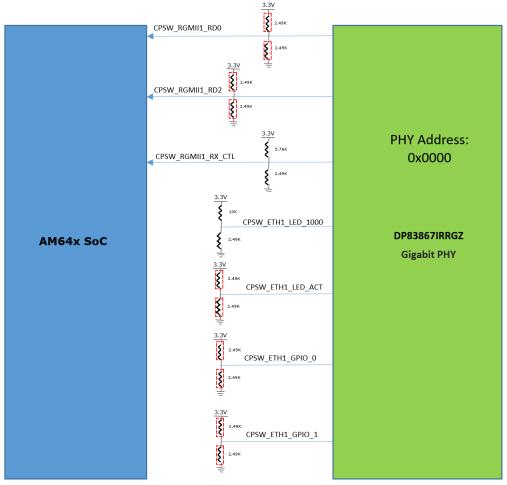

#### 2.3.3.9 Ethernet Interface

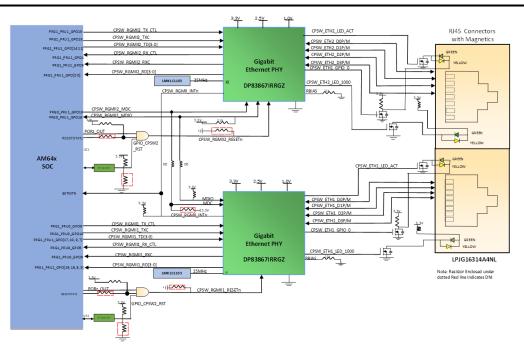

SKEVM offers two Ethernet Ports of 1Gigabit Speed for external Communication. Two channels of RGMII Gigabit Ethernet CPSW Ports from AM64xx SoC are connected to two separate Gigabit Ethernet PHY Transceivers DP83867, which is finally terminated on two RJ45 connectors with integrated magnetics.

The 48pin version of the PHY DP83867 is configured to advertise 1-Gb operation with the internal delay set to accommodate the internal delay inside the AM64x. The RGMII1 signals shared with PRG1 are used for the RX path to allow the PRG0 to be connected to the PRU header on the board. CPSW\_RGMII1 and CPSW\_RGMII2 Ports of PRG1 share a common MDIO Bus to communicate with the external PHY Transceiver.

Two port RJ45 Connector (LPJG16314A4NL) used on the board for Ethernet 10/100/1G Connectivity. RJ45 Connectors have integrated magnetics and LEDs for indicating 1000BASE-T link as well as receive or transmit activity.

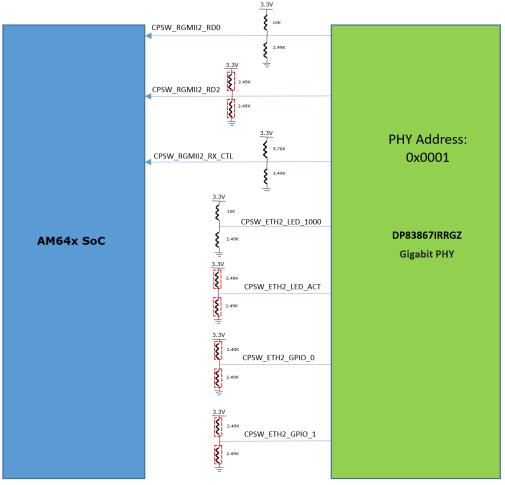

#### 2.3.3.9.1 DP83867 PHY Default Configuration

The DP83867 PHY uses four level configurations based on resistor strapping which generate four distinct voltages ranges. The resistors are connected to the RX data and control pins which are normally driven by the PHY and are inputs to the AM64x. The voltage range for each mode is shown below.

Mode 1 - 0 V to 0.3234V

Mode 2 - 0.462V to 0.6303V

Mode 3 - 0.7425V to 0.9372V

Mode 4 - 2.2902V to 2.904V

DP83867 device includes internal pull-down resistor. The value of the external pull resistors is selected to provide voltage at the pins of the AM64x as close to ground or 3.3V as possible. The strapping is shown in Figure 2-19. The strap values are given in Table 2-19

**Target Voltage** Ideal Rlo Ideal Rhi Mode Vmin(V) Vtyp(V) Vmax(V) (k Ω) (k Ω) n 0.098 \* VDDIO **OPEN OPEN** 2 10 0.140 \* VDDIO 0.165 \* VDDIO 0.191 \* VDDIO 2.49 0.225 \* VDDIO 0.255 \* VDDIO 0.284 \* VDDIO 3 5.76 2.49 4 0.694 \* VDDIO 0.763 \* VDDIO 0.886 \* VDDIO 2.49 **OPEN**

**Table 2-19. Strap Value Configuration**

Address strapping is provided for CPSW PHY-1 to set address -00000 (0h) and CPSW PHY-2 to set address 00001(01h). By default, as strapping pins has internal pull-down resistors. Footprint for both pull up and pull down is provided on all the strapping pins except LED\_0. LED\_0 is for Mirror Enable, which is set to mode 1 by default, Mode 4 is not applicable and Mode2, Mode3 option is not desired. Default strap setting of CPSW RGM I 1Ethernet PHY and CPSW RGMII1 Ethernet PHY are given in Table 2-20 and Table 2-21.

Note: Resistor Enclosed under dotted Red line indicates DNI

Figure 2-19. CPSW Ethernet PHY-1 Strap Settings

Hardware INSTRUMENTS

www.ti.com

Note: Resistor Enclosed under dotted Red line indicates DNI

Figure 2-20. CPSW Ethernet PHY-2 Strap Settings

Table 2-20. Default Strap Setting of CPSW RGMII-1 Ethernet PHY

| Strap Setting    | Pin Name      | Strap Function | Mode for<br>PRG1_PRU1,<br>PRG1_PRU0 | Value of Strap<br>Function for PRG1 | Description        |

|------------------|---------------|----------------|-------------------------------------|-------------------------------------|--------------------|

| PHY Address      | RX_D2         | PHY_AD3        | 1                                   | 0                                   | PHY Address: 0000  |

|                  |               | PHY_AD2        | 1                                   | 0                                   |                    |

|                  | RX_D0         | PHY_AD1        | 1                                   | 0                                   |                    |

|                  |               | PHY_AD0        | 1                                   | 0                                   |                    |

| Auto Negotiation | RX_DV/RX_CTRL | Auto- neg      | 3                                   | 0                                   | Auto neg Disable=0 |

Table 2-20. Default Strap Setting of CPSW RGMII-1 Ethernet PHY (continued)

| Mode for             |          |                           |                         |                                     |                                       |

|----------------------|----------|---------------------------|-------------------------|-------------------------------------|---------------------------------------|

| Strap Setting        | Pin Name | Strap Function            | PRG1_PRU1,<br>PRG1_PRU0 | Value of Strap<br>Function for PRG1 | Description                           |

| Modes of Operation   | LED2     | RGMII Clock Skew TX[1]    | 5                       | 0                                   | RGMII TX Clock<br>Skew is set to 0 ns |

|                      |          | RGMII Clock Skew TX[0]    | 5                       | 0                                   |                                       |

| LED_1  LED_0  GPIO_1 | LED_1    | RGMII Clock Skew<br>TX[2] | 5                       | 1                                   |                                       |

|                      |          | ANEG_SEL                  | 1                       | 0                                   | advertise ability of 10/100/1000      |

|                      | LED_0    | Mirror Enable             | 1                       | 0                                   | Mirror Enable<br>Disabled             |

|                      | GPIO_1   | RGMII Clock Skew<br>RX[2] | 1                       | 0                                   | RGMII RX Clock<br>Skew is set to 2 ns |

|                      |          | RGMII Clock Skew TX[1]    | 1                       | 0                                   |                                       |

|                      | GPIO_0   | RGMII Clock Skew<br>RX[0] | 1                       | 0                                   |                                       |

Table 2-21. Default strap setting of CPSW RGMII-2 Ethernet PHY

| Strap Setting      | Pin Name      | Strap Function            | Mode for<br>PRG1_PRU1,<br>PRG1_PRU0 | Value of Strap<br>Function for PRG0<br>and PRG1 | Description                           |

|--------------------|---------------|---------------------------|-------------------------------------|-------------------------------------------------|---------------------------------------|

| PHY Address        | RX_D2         | PHY_AD3                   | 1                                   | 0                                               | PHY Address: 0001                     |

|                    |               | PHY_AD2                   | 1                                   | 0                                               |                                       |

|                    | RX_D0         | PHY_AD1                   | 2                                   | 0                                               |                                       |

|                    |               | PHY_AD0                   | 2                                   | 1                                               |                                       |

| Auto Negotiation   | RX_DV/RX_CTRL | Auto- neg                 | 3                                   | 0                                               | Auto neg Disable=0                    |

| Modes of Operation | LED2          | RGMII Clock Skew TX[1]    | 5                                   | 0                                               | RGMII TX Clock<br>Skew is set to 0 ns |

|                    |               | RGMII Clock Skew TX[0]    | 5                                   | 0                                               |                                       |

|                    | LED_1         | RGMII Clock Skew<br>TX[2] | 5                                   | 1                                               |                                       |

|                    |               | ANEG_SEL                  | 1                                   | 0                                               | advertise ability of 10/100/1000      |

|                    | LED_0         | Mirror Enable             | 1                                   | 0                                               | Mirror Enable<br>Disabled             |

|                    | GPIO_1        | RGMII Clock Skew<br>RX[2] | 1                                   | 0                                               | RGMII RX Clock<br>Skew is set to 2 ns |

|                    |               | RGMII Clock Skew TX[1]    | 1                                   | 0                                               |                                       |

|                    | GPIO_0        | RGMII Clock Skew<br>RX[0] | 1                                   | 0                                               |                                       |

Hardware www.ti.com

### 2.3.3.9.2 DP83867 - Power, Clock, Reset, Interrupt and LEDs

The PHY devices include Integrated MDI Termination Resistors. So external termination is not provided.

Power: The RGMII signals from PRG0 and PRG1 domain is at 3.3V IO level. The Gigabit PHY device DP83867 requires I/O power of 3.3V and analog supply of 2.5V and 1.0V

Clock: A 25 MHz LVCMOS clock is given to the PHYs through clock buffer LMK1C1103 (individual outputs).

Reset: The reset for PHYs is from a circuit that ANDs the PORz\_OUT and GPIO from IO expander and an optional RESETSTATz from SoC. By default RESETSTATz is not used for resetting the PHY. The IO expander is controlled through I2C1 port of AM64x SOC. Footprints for both a pull-up and a pull-down resistor are provided to the GPIO to set the default value. Each of the Ethernet PHY's have separate Reset Signals driven by GPIO's. A hardware reset is accomplished by applying a low pulse, with a duration of at least 1 micro-second to the RESET\_N pin.

Interrupt: The interrupt from two CPSW RGMII PHYs from PRG1 domain are tied together and is connected to EXTINTN pin of AM64x SOC.

Four configurable LED pins and two GPIO of Ethernet PHY are used to indicate link status. Several functions can be multiplexed onto the LEDs for different modes of operation. The LED operation mode can be selected using the LEDCR1 register address 0x0018 on the DP83867 device. The default configurations are as follows.

LED0: By default, this pin indicates that link is established. Additional functionality is configurable via LEDCR1 [3:0] register bits in the DP83867 device. LDE0 is not used in the CPSW PHY (DP83867), this is also a strap pin which is used to set mirror enable. Since these features are not required the strapping for the LED0 is not provided.

LED\_1: By default, this pin indicates that 1000BASE-T link is established. This setting can be changed to Auto negotiate to 10/100Mbps using the strap resistors. Additional functionality is configurable via LEDCR1 [7:4] register bits in the DP83867 device. LED\_1 is a also an strap pin, which is having internal pull-down resistor to set RGMII TX Clock Skew in the DP83867 device. Since this pin is set to active on both the devices, this results in dim LED lighting when LED is driven directly. So a MOSFET is used to drive LED.

LED\_2: By default, this pin indicates receive or transmit activity. Additional functionality is configurable via LEDCR1 [11:18] register bits in the DP83867 device. LED\_2 is also a strap pin, which is having internal pull-down resistor to set RGMII TX Clock Skew in the DP83867 device. The default condition is to auto negotiate and advertise link as 10/100/1000Mbps, this can be changed using the strap resistors provided. The pull up resistor used for strap setting results in dim LED lighting when LED is driven directly. So a MOSFET is used to drive LED.

GPIO0: In the DP83867 PHY, the GPIO can be configured to function as LED3 through GPIO Mux Control Register 1 (GPIO\_MUX\_CTRL1) and the LED configuration can be set by programming LEDCR1 register and this pin is used to indicate operating as a 100-Mbps connection. A MOSFET is used to drive LED as shown in the below figure.

GPIO1: In the DP83867 PHY, the GPIO can be configured to function as LED3 through GPIO Mux Control Register 1 (GPIO\_MUX\_CTRL1) and the LED configuration can be set by programming LEDCR1 register this is also a strap pin which is used to set fast link drop (FDP), currently this is disabled.

LED Indication in Ethernet RJ45 Connector: LED Control is achieved through an external MOSFET.

RJ45 Connector LED Indication - CPSW (DP83867): LED1 is connected to RJ45 LED (Green) to indicate 1000 MHz link and LED2 is connected to RJ45 LED (Yellow) to indicate transmit/receive activity. LED Control is achieved through an external MOSFET.

Figure 2-21. Ethernet Interface

# Note

Resistors which are highlighted by red color box are DNI components

Hardware Very INSTRUMENTS

www.ti.com

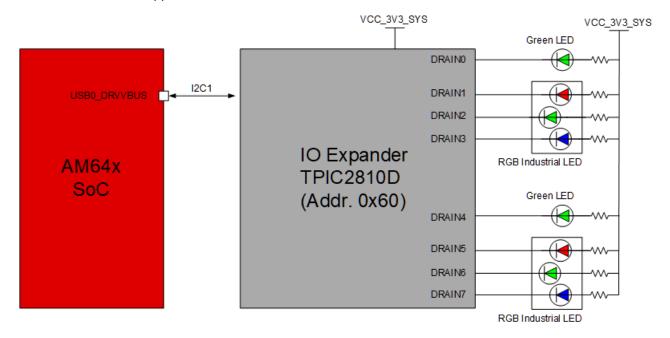

#### 2.3.3.9.3 Industrial Application LEDs

There are 8 LED's which are connected to an I2C Based LED Driver (TPIC2810D) which is controlled by the SoC via the I2C1 port. These 8 LED's can be toggled based on the user application. Primarily these eight LEDs are meant for Industrial application.

Figure 2-22. Ethernet Interface - LEDs

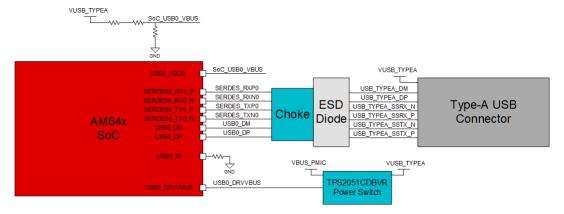

#### 2.3.3.10 USB 3.0 Interface

On AM64x SKEVM, USB 3.0 HOST Interface is offered through USB Type-A Connector (692121030100) which supports data rate up-to 5Gbps. Super-speed differential signals from Type-A connector are connected to the SERDES-0 block of SoC via choke and ESD protection device. USB2.0 Lines of the Type-A Connector are directly interfaced to the USB0 port of AM64x SOC. USB0\_DRVVBUS from SoC enables the 5V power switch to provide VUSB\_TYPEA supply which is used for USB Type-A Connector.

An ESD protection device meeting the USB 3.0 speed and capacitance specification shall be included on all USB3.0 Lines (TX\_P, RX\_P, TX\_N, and RX\_N) to dissipate ESD strikes. A common mode choke on USB Data lines shall be provided to take care of EMI/EMC. An ESD protection device of part number TPD4S012 is included to dissipate ESD strikes on USB2.0 DP/DM Signals.

Figure 2-23. USB 3.0 Host Interface

www.ti.com Hardware

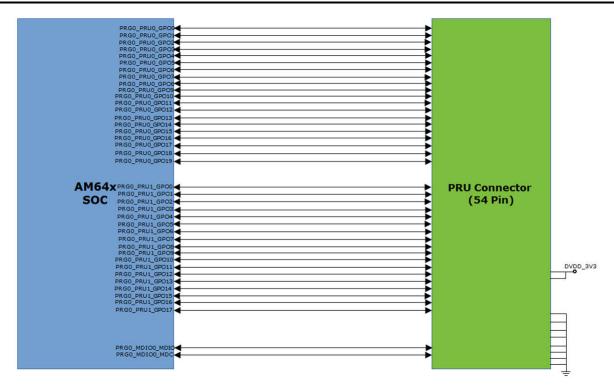

#### 2.3.3.11 PRU Connector

PRU Header offers Low speed connection to PRG0 Interface. PRU\_ICSSG signals from PRG0 Port (PRG0\_PRU0 and PRG0\_PRU1) are terminated on the PRU Expansion Connector. PRU0 signals are connected to a 27x2 standard 0.1" spaced 54 pin connector. Connector shall contain MDIO Control Signals (2 Pins), PRG0\_PRU0\_GPO [0: 19], PRG0\_PRU1\_GPO [0: 17], +3.3V PWR (2 Pins) and Ground reference (5 Pins), DETECT, RESET, INT going to the daughter card and SoC I2C0 lines (2 Pins). 3.3V are current limited to 500 mA. This is achieved by using load switch TPS22902YFPR. Enable for the load switch is controlled by SoC.

Signals routed from the PRU Connector are listed in Table 2-22.

Table 2-22. Selection of PRG0 Signals on PRU Connector

| Pin | Net Name        | Pin | Net Name       |

|-----|-----------------|-----|----------------|

| 1   | VCC3V3_PRU      | 2   | DGND           |

| 3   | PRU_DETECT      | 4   | PRU_RESETz     |

| 5   | PRU_INTn        | 6   | SoC_I2C0_SCL   |

| 7   | PRG0_PRU0GPO16  | 8   | SoC_I2C0_SDA   |

| 9   | PRG0_MDIO0_MDC  | 10  | NC             |

| 11  | PRG0_MDIO0_MDIO | 12  | NC             |

| 13  | PRG0_PRU0GPO0   | 14  | PRG0_PRU0GPO1  |

| 15  | PRG0_PRU0GPO2   | 16  | PRG0_PRU0GPO3  |

| 17  | PRG0_PRU0GPO4   | 18  | PRG0_PRU0GPO5  |

| 19  | PRG0_PRU0GPO6   | 20  | PRG0_PRU0GPO7  |

| 21  | PRG0_PRU0GPO8   | 22  | PRG0_PRU0GPO9  |

| 23  | PRG0_PRU0GPO10  | 24  | PRG0_PRU0GPO11 |

| 25  | PRG0_PRU0GPO12  | 26  | PRG0_PRU0GPO13 |

| 27  | PRG0_PRU0GPO14  | 28  | PRG0_PRU0GPO15 |

| 29  | DGND            | 30  | PRG0_PRU0GPO17 |

| 31  | PRG0_PRU0GPO18  | 32  | PRG0_PRU0GPO19 |

| 33  | DGND            | 34  | DGND           |