# TMS320VC5501/5502 DSP Direct Memory Access (DMA) Controller Reference Guide

Literature Number: SPRU613G March 2005

## **Preface**

# **Read This First**

#### **About This Manual**

This manual describes the features and operation of the direct memory access (DMA) controller that is available on the TMS320VC5501 and TMS320VC5502 digital signal processors (DSPs) in the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP generation. This DMA controller allows movement of data among internal memory, external memory, and peripherals to occur without intervention from the CPU and in the background of CPU operation.

#### **Notational Conventions**

This document uses the following conventions:

In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers often are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

#### Related Documentation From Texas Instruments

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

**TMS320C55x Technical Overview** (literature number SPRU393). This overview is an introduction to the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000™ DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- TMS320C55x DSP CPU Reference Guide (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- **TMS320C55x DSP Peripherals Reference Guide** (literature number SPRU317) describes the peripherals, interfaces, and related hardware that are available on TMS320C55x DSPs.

- TMS320C55x DSP Algebraic Instruction Set Reference Guide (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- TMS320C55x DSP Mnemonic Instruction Set Reference Guide (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x<sup>™</sup> C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- TMS320C55x Assembly Language Tools User's Guide (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- TMS320C55x DSP Programmer's Guide (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

#### **Trademarks**

TMS320, TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

# **Contents**

| 1  | Introduction to the DMA Controller  1.1 Key Features of the DMA Controller  1.2 Block Diagram of the DMA Controller  1.3 DMA Requests Versus CPU Requests for Internal Memory | 10<br>10       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2  | Channels and Port Accesses                                                                                                                                                    | 12             |

| 3  | Channel Auto-initialization Capability  3.1 Auto-initialization with Unchanging Context  3.2 Auto-initialization with Changing Context                                        | 17             |

| 4  | Service Chain                                                                                                                                                                 |                |

| 5  | Units of Data: Byte, Element, Frame, and Block                                                                                                                                | 22             |

| 6  | Start Addresses in a Channel  6.1 Start Address in Memory  6.2 Start Address in I/O Space                                                                                     | 23             |

| 7  | Updating Addresses in a Channel                                                                                                                                               | 25             |

| 8  | Data Burst Capability                                                                                                                                                         | 26             |

| 9  | Data Packing                                                                                                                                                                  | 27             |

| 10 | Write Posting: Buffering Writes to Internal Memory                                                                                                                            | 29             |

| 11 | Synchronizing Channel Activity to an Event                                                                                                                                    | 31             |

| 12 | Monitoring Channel Activity  12.1 Channel Interrupt  12.2 Time-Out Error Condition  12.3 Address Error Condition  12.4 Bus Error Interrupt                                    | 33<br>34<br>34 |

| 13 | Latency in DMA Transfers                                                                                                                                                      | 36             |

| 14 | Powe   | r, Emulation, and Reset Considerations                                                  | 37 |

|----|--------|-----------------------------------------------------------------------------------------|----|

|    | 14.1   | Reducing Power Consumed by the DMA Controller (Idle Configurations)                     |    |

|    | 14.2   | Emulation Modes of the DMA Controller                                                   | 37 |

|    | 14.3   | DMA Controller after DSP Reset                                                          | 37 |

| 15 | DMA (  | Controller Registers                                                                    | 38 |

|    | 15.1   | Global Control Register (DMAGCR)                                                        | 39 |

|    | 15.2   | Global Time-Out Control Register (DMAGTCR)                                              | 40 |

|    | 15.3   | Channel Control Register (DMACCR)                                                       | 42 |

|    | 15.4   | Interrupt Control Register (DMACICR) and Status Register (DMACSR)                       | 49 |

|    | 15.5   | Source and Destination Parameters Register (DMACSDP)                                    | 55 |

|    | 15.6   | Source Start Address Registers (DMACSSAL and DMACSSAU)                                  | 60 |

|    | 15.7   | Destination Start Address Registers (DMACDSAL and DMACDSAU)                             | 61 |

|    | 15.8   | Element Number Register (DMACEN) and Frame Number Register (DMACFN)                     | 62 |

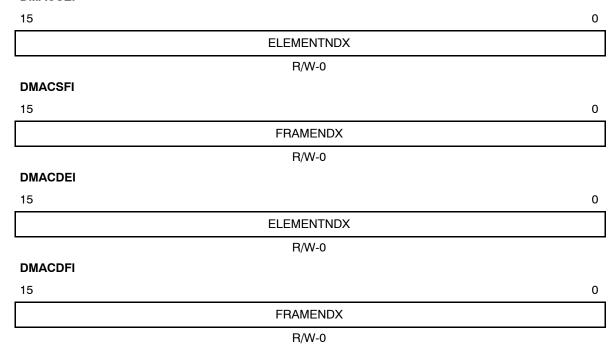

|    | 15.9   | Element Index Registers (DMACSEI, DMACDEI) and Frame Index Registers (DMACSFI, DMACDFI) | 64 |

|    | 15.10  | Source Address Counter (DMACSAC) and Destination Address Counter (DMACDAC)              | 67 |

| Re | vision | History                                                                                 | 69 |

# **Figures**

| 1  | Conceptual Block Diagram of the DMA Controller Connections                                 | 11   |

|----|--------------------------------------------------------------------------------------------|------|

| 2  | The Two Parts of a DMA Transfer                                                            |      |

| 3  | Registers for Controlling a Channel's Context                                              |      |

| 4  | Channel Control Register (DMACCR)                                                          |      |

| 5  | Auto-initialization Sequence with Unchanging Context (REPEAT = 1)                          |      |

| 6  | Auto-initialization Sequence with Changing Context (REPEAT = 0)                            |      |

| 7  | One Possible Configuration for the Service Chains                                          |      |

| 8  | Service Chain Applied to Three DMA Ports                                                   |      |

| 9  | High-Level Memory Map for TMS320C55x DSPs                                                  |      |

| 10 | High-Level I/O Map for TMS320C55x DSPs                                                     |      |

| 11 | Triggering a Channel Interrupt Request                                                     | . 33 |

| 12 | Global Control Register (DMAGCR)                                                           |      |

| 13 | Global Time-Out Control Register (DMAGTCR)                                                 | . 40 |

| 14 | Channel Control Register (DMACCR)                                                          | . 42 |

| 15 | Interrupt Control Register (DMACICR) and Status Register (DMACSR)                          | . 50 |

| 16 | Source and Destination Parameters Register (DMACSDP)                                       | . 56 |

| 17 | Source Start Address Registers (DMACSSAL and DMACSSAU)                                     | . 60 |

| 18 | Destination Start Address Registers (DMACDSAL and DMACDSAU)                                | . 62 |

| 19 | Element Number Register (DMACEN) and Frame Number Register (DMACFN)                        | . 63 |

| 20 | Element Index Registers (DMACSEI, DMACDEI) and Frame Index Registers (DMACSFI, DMACDFI)    |      |

| 21 | Channel Source Address Counter (DMACSAC) and Channel Destination Address Counter (DMACDAC) | . 67 |

# **Tables**

| 1  | Event and Non-Event Driven Ports                                              |

|----|-------------------------------------------------------------------------------|

| 2  | Channel Control Register (DMACCR) Field Descriptions                          |

| 3  | Activity Shown in Figure 8                                                    |

| 4  | Registers Used to Define the Start Addresses for a DMA Transfer               |

| 5  | Data Packing Performed by the DMA Controller                                  |

| 6  | 32-bit Data Packing Conditions                                                |

| 7  | 16-bit Data Packing Conditions                                                |

| 8  | Event and Non-Event Driven Ports                                              |

| 9  | DMA Controller Operational Events and Their Associated Bits and Interrupts 32 |

| 10 | Registers of the DMA Controller                                               |

| 11 | DMAGCR Bit Field Descriptions                                                 |

| 12 | DMAGTCR Bit Field Descriptions 4                                              |

| 13 | DMACCR Bit Field Descriptions                                                 |

| 14 | Synchronization Event Mapping for the TMS320VC5501/5502 DSPs 48               |

| 15 | DMACICR Bit Field Descriptions                                                |

| 16 | DMACSR Bit Field Descriptions                                                 |

| 17 | DMACSDP Bit Field Descriptions                                                |

| 18 | DMACSSAL Bit Field Description6                                               |

| 19 | DMACSSAU Bit Field Description6                                               |

| 20 | DMACDSAL Bit Field Description                                                |

| 21 | DMACDSAU Bit Field Description                                                |

| 22 | DMACEN Bit Field Description                                                  |

| 23 | DMACFN Bit Field Description                                                  |

| 24 | DMACSEI Bit Field Description                                                 |

| 25 | DMACSFI Bit Field Description                                                 |

| 26 | DMACDEI Bit Field Description6                                                |

| 27 | DMACDFI Bit Field Description6                                                |

| 28 | DMACSAC Bit Field Description                                                 |

| 29 | DMACDAC Bit Field Description6                                                |

| 30 | Document Revision History                                                     |

# **DMA Controller**

This document describes the direct memory access (DMA) controller of the TMS320VC5501/TMS320VC5502 digital signal processors (DSPs). This DMA controller allows movement of data among internal memory, external memory, and peripherals to occur without intervention from the CPU and in the background of CPU operation.

1.2

## 1 Introduction to the DMA Controller

Acting in the background of CPU operation, the DMA controller can transfer data among internal memory, external memory, and on-chip peripherals.

# 1.1 Key Features of the DMA Controller

|              | The  | e DMA controller has the following important features:                                                                                                                                                                                                                                       |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |      | Operation that is independent of the CPU.                                                                                                                                                                                                                                                    |

|              |      | Four standard ports: Two for internal dual-access RAM (DARAM), one for external memory, and one for peripherals.                                                                                                                                                                             |

|              |      | Six channels, which allow the DMA controller to keep track of the context of six independent block transfers among the standard ports.                                                                                                                                                       |

|              |      | Bits for assigning each channel a low priority or a high priority. For details, see <i>Service Chain</i> on page 19.                                                                                                                                                                         |

|              |      | Event synchronization. DMA transfers in each channel can be made dependent on the occurrence of selected events. For details, see <i>Synchronizing Channel Activity</i> on page 30.                                                                                                          |

|              |      | An interrupt for each channel. Each channel can send an interrupt to the CPU on completion of certain operational events. See <i>Monitoring Channel Activity</i> on page 32.                                                                                                                 |

|              |      | Software-selectable options for updating addresses for the sources and destinations of data transfers.                                                                                                                                                                                       |

|              |      | A dedicated idle domain. You can put the DMA controller into a low-power state by turning off this domain. Each multichannel buffered serial port (McBSP) on the C55x DSP has the ability to temporarily take the DMA domain out of this idle state when the McBSP needs the DMA controller. |

|              |      | read about the registers used to program the DMA controller, see section on page 38.                                                                                                                                                                                                         |

| Block Diagra | ım c | of the DMA Controller                                                                                                                                                                                                                                                                        |

|              | _    | ure 1 is a conceptual diagram of connections between the DMA controller<br>d other parts of the DSP. The DMA controller has four ports:                                                                                                                                                      |

|              |      | Two ports for internal dual-access RAM (DARAM). For ease of reference, these ports are called internal memory port 0 and internal memory port 1 throughout this document.                                                                                                                    |

|              |      | One port for external memory. The external memory interface (EMIF) connects the port to the external memory.                                                                                                                                                                                 |

|              |      | One port for peripherals. A peripheral bus controller connects the port to the peripherals.                                                                                                                                                                                                  |

|              |      |                                                                                                                                                                                                                                                                                              |

Data transfers among the ports occur in the six DMA channels. (The DMA channels are described on page 12.) It is possible for multiple channels to request access to the same port at the same time. To arbitrate simultaneous requests, the DMA controller has one programmable service chain that is used by each of the ports. For details on the service chain, see page 19.

TMS320VC5501/5502 DSP

Port

DARAM

Port

DMA controller

Peripheral

bus

controller

Channels

0-5

Port

EMIF

External memory

Figure 1. Conceptual Block Diagram of the DMA Controller Connections

#### 1.3 DMA Requests Versus CPU Requests for Internal Memory

If the CPU and the DMA controller simultaneously request access to the same DARAM block in internal memory, CPU requests always have priority over DMA requests. The DMA requests to a DARAM block will be serviced when there are no more CPU requests. Refer to the device-specific data manual for specific information on the start and end addresses for each DARAM block.

#### 2 Channels and Port Accesses

The DMA controller has six paths, called **channels**, to transfer data among the four ports (two for DARAM, one for external memory, and one for peripherals). Each channel reads data from one port (from the source) and writes data to that same port or another port (to the destination).

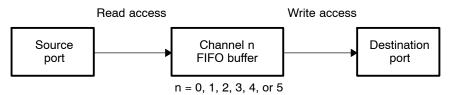

Each channel has a first in, first out (FIFO) buffer that allows the data transfer to occur in two stages (see Figure 2):

Port read access Transfer of data from the source port to the channel

FIFO buffer.

Port write access Transfer of data from the channel FIFO buffer to the

destination port.

The FIFO buffer in each channel is eight 32-bit words deep.

Figure 2. The Two Parts of a DMA Transfer

The different ports in the DMA can be categorized as event driven and non-event driven (see Table 1). This difference between ports is significant when synchronization is used to transfer data, as described in section 11, page 30.

Table 1. Event and Non-Event Driven Ports

| Port            | Category         |

|-----------------|------------------|

| DARAM           | Non-event driven |

| External memory | Non-event driven |

| Peripheral      | Event driven     |

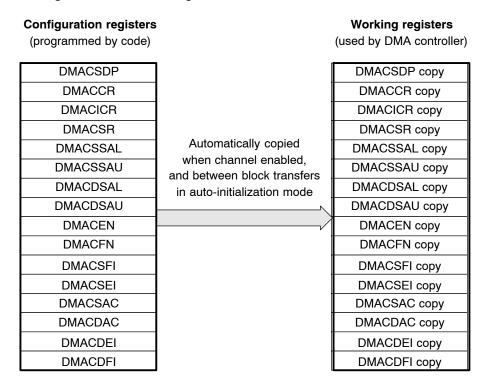

The set of conditions under which transfers occur in a channel is called the **channel context**. Each of the six channels contains a register structure for programming and updating the channel context (see Figure 3). Your code modifies the configuration registers. When it is time for data transferring, the contents of the configuration registers are copied to the working registers, and the DMA controller uses the working register values to control channel activity. The copy from the configuration registers to the working registers occurs whenever your code enables the channel (EN = 1 in DMACCR). In addition, if the auto-initialization mode is on (AUTOINIT = 1 in DMACCR), the copy occurs between block transfers. For more information about the DMA controller registers, see page 38.

Some configuration registers can be programmed for the next block transfer while the DMA is still running the current context from the working registers. The next transfer will use the new configuration without stopping the DMA. The configuration registers that should not be configured in this manner are DMAGCR, DMAGTCR, DMACSDP, DMACCR, DMACICR and DMACSR. Modification of these registers while the DMA channel is running may cause unpredictable operation of the channel.

Figure 3. Registers for Controlling a Channel's Context

# 3 Channel Auto-initialization Capability

After a block transfer is completed (all of the elements and frames in a block have been moved), the DMA controller automatically disables the channel. If it is necessary for the channel to be used again, the CPU can reprogram the new channel context and re-enable the DMA channel, or the DMA controller can automatically initialize the new context and re-enable the channel.

When auto-initialization is used, after each block transfer is completed, the DMA controller automatically recopies the channel context from the configuration registers to the working registers and re-enables the channel allowing the channel to run again. Auto-initialization is enabled by setting the AUTOINIT bit in the channel controller register (DMACCR).

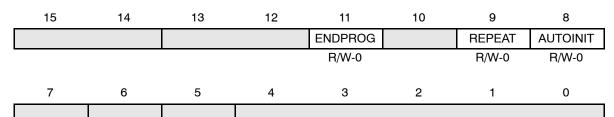

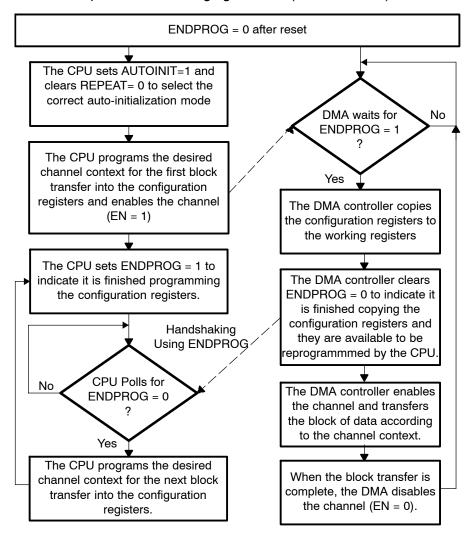

Two additional bits in DMACCR, REPEAT and ENDPROG, are used during the auto-initialization operation. REPEAT controls whether the DMA controller waits for an indication from the CPU that the configuration registers are ready to be copied. ENDPROG is a handshaking bit used to communicate between the CPU and the DMA controller regarding the state of the register copy process. Figure 4 shows DMACCR and Table 2 describes AUTOINIT, REPEAT, and ENDPROG. For a complete description of DMACCR, see section 15.3.

There are two methods for using auto-initialization. The same channel context can be repeated on each block transfer, or a new context can be provided for each transfer. These two cases are explained in the following sections.

Figure 4. Channel Control Register (DMACCR)

**Legend:** R = Read; W = Write; -n = Value after DSP reset

Table 2. Channel Control Register (DMACCR) Field Descriptions

| Bit | Field   | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11  | ENDPROG |       | End-of-programming bit. Each DMA channel has two sets of registers: configuration registers and working registers. When block transfers occur repeatedly because of auto-initialization (AUTOINIT = 1), you can change the context for the next DMA transfer by writing to the configuration registers during the current block transfer. At the end of the current transfer, the contents of the configuration registers are copied into the working registers, and the DMA controller begins the next transfer using the new context. For proper auto-initialization, the CPU must finish programming the configuration registers before the DMA controller copies their contents. |  |

|     |         |       | The DMA controller automatically clears the ENDPROG bit after copying the configuration registers to the working registers. The CPU can then program the DMA channel context for the next iteration of the transfer by programming the configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     |         |       | To make sure auto-initialization waits for the CPU, follow this procedure:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     |         |       | 1) Make auto-initialization wait for ENDPROG = 1 by clearing the REPEAT bit (REPEAT = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     |         |       | <ol> <li>Poll for ENDPROG = 0, which indicates that the DMA controller has<br/>finished copying the previous context. The configuration registers can<br/>now be programmed for the next iteration.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     |         |       | 3) Program the configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|     |         |       | <ol> <li>Set ENDPROG (ENDPROG = 1) to indicate the end of register<br/>programming.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     |         | 0     | Configuration registers ready for programming / Programming in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     |         | 1     | End of programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 9   | REPEAT  |       | Repeat condition bit. If auto-initialization is selected for a channel (AUTOINIT = 1), REPEAT specifies one of two special repeat conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|     |         | 0     | Repeat only if ENDPROG = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     |         |       | Once the current DMA transfer is complete, auto-initialization will wait for the end-of-programming bit (ENDPROG) bit to be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     |         | 1     | Repeat regardless of ENDPROG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|     |         |       | Once the current DMA transfer is complete, auto-initialization occurs regardless of whether ENDPROG is 0 or 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

Table 2. Channel Control Register (DMACCR) Field Descriptions (Continued)

| Bit | Field    | Value | Description                                                                                                                                                                                                   |  |

|-----|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8   | AUTOINIT |       | Auto-initialization bit. The DMA controller supports auto-initialization, which is the automatic reinitialization of the channel between DMA block transfers. Use AUTOINIT to enable or disable this feature. |  |

|     |          | 0     | Auto-initialization is disabled.                                                                                                                                                                              |  |

|     |          |       | Activity in the channel stops at the end of the current block transfer. To stop a transfer immediately, clear the channel enable bit (EN).                                                                    |  |

|     |          | 1     | Auto-initialization is enabled.                                                                                                                                                                               |  |

|     |          |       | Once the current block transfer is complete, the DMA controller reinitializes the channel and starts a new block transfer. To stop activity in the channel you have two options:                              |  |

|     |          |       | ☐ To stop activity immediately, clear the channel enable bit (EN = 0).                                                                                                                                        |  |

|     |          |       | ☐ To stop activity after the current block transfer, clear AUTOINIT (AUTOINIT= 0).                                                                                                                            |  |

# 3.1 Auto-initialization with Unchanging Context

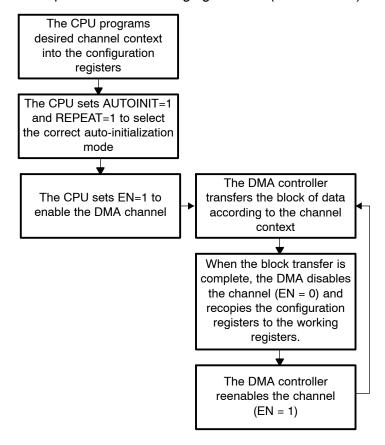

If the desired context for the channel needs to be repeated but does not need to be changed, then the DMA controller is configured with AUTOINIT = 1 and REPEAT = 1. When REPEAT = 1, the DMA controller ignores the state of the ENDPROG handshaking bit. After the CPU has initially configured the DMA channel, no other CPU intervention is required to keep the channel running. A detailed sequence of events in this mode is shown in Figure 5.

Figure 5. Auto-initialization Sequence with Unchanging Context (REPEAT = 1)

# 3.2 Auto-initialization with Changing Context

If the desired context for the channel needs to be repeated and is not the same on each block transfer, then the DMA controller must be configured with AUTOINIT = 1 and REPEAT = 0. When REPEAT = 0, the DMA controller waits for the CPU to write ENDPROG = 1 before it copies the configuration registers. This provides handshaking for the DMA to prevent it from copying the registers while they are still being configured by the CPU. A detailed sequence of events in this mode is shown in Figure 6.

Figure 6. Auto-initialization Sequence with Changing Context (REPEAT = 0)

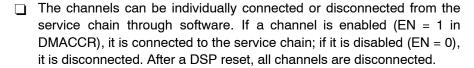

#### 4 Service Chain

Each of the ports of the DMA controller can arbitrate simultaneous access requests sent by the six DMA channels. Each of the ports has an independently functioning service chain—a software—and hardware-controlled scheme for servicing access requests. Although the four service chains function independently, they share a common configuration. For example, if you disable channel 2, it is disabled in all four ports, and if you make channel 4 high-priority, it is high-priority in all four of the ports. One possible configuration for the service chains is shown in Figure 7. Important characteristics of the service chain are listed after the figure.

Section 4.1 contains an example that shows a service chain configuration applied to three ports.

High Priority High Priority High Priority Channel Channel Channel 0 2 5 Channel Channel Channel 3 Low Priority Low Priority Low Priority

Figure 7. One Possible Configuration for the Service Chains

- The channels have a programmable priority level. Each channel has a PRIO bit in DMACCR for selecting a high priority or a low priority. The DMA controller only services the low-priority items when all the high-priority items are done or stalled. After a DSP reset, all channels are low priority.

- In the figure, channels 0, 2, and 5 are high-priority (in each of these channels, PRIO = 1). DMA channels 1, 3, and 4 are low priority (in each of these channels, PRIO = 0).

- ☐ The channels have fixed positions in the service chain. Regardless of the programmed priorities, the port checks the channels in a repeating circular sequence: 0, 1, 2, 3, 4, 5, 0, 1, 2, 3, 4, 5, and so on. At each position in the service chain, the port checks whether the channel is ready and able to be serviced. If so, it is serviced; otherwise, the port skips to the next position. After a DSP reset, the port restarts its circular sequence, beginning with channel 0.

In the figure, only channel 1 is disconnected. As a port checks the channels in its repeating circular sequence, it will keep skipping channel 1 until the channel is reconnected.

☐ If a channel is tied to a synchronization event, the channel does not generate a DMA request (and, therefore, cannot be serviced) until the synchronization event occurs.

#### 4.1 Service Chain Example

Figure 8 shows a DMA service chain applied to a DARAM port, the external memory port, and the peripheral port. The service chain has the following programmed characteristics.

- ☐ Channels 0, 2, and 5 are high-priority (PRIO = 1 in DMACCR). Channels 1, 3, and 4 are low-priority (PRIO = 0).

- ☐ Channels 1, 2, and 4 are enabled (EN = 1 in DMACCR). Channels 0, 3, and 5 are disabled (EN = 0).

Table 3 summarizes the activity at the ports in the figure.

Table 3. Activity Shown in Figure 8

| Port            | This Port Arbitrates                                                        |

|-----------------|-----------------------------------------------------------------------------|

| DARAM           | Write access requests from channel 2<br>Read access requests from channel 4 |

| External memory | Write access requests from channel 1 Write access requests from channel 4   |

| Peripheral      | Read access requests from channel 1 Read access requests from channel 2     |

Finally, notice that for each port in the figure, there is a channel that is connected to the service chain but does not use the port. For example, the peripheral port is not used by channel 4. If channel 4 were redefined to include the peripheral port as source or destination, the port would handle channel 4 according to its position and priority in the service chain.

Figure 8. Service Chain Applied to Three DMA Ports

Configuration for High-priority: 0, 2, 5 Disabled: 0, 3, 5 the service chains Low-priority: 1, 3, 4 Enabled: 1, 2, 4

# 5 Units of Data: Byte, Element, Frame, and Block

This documentation on the DMA controller refers to data in four levels of granularity:

Byte An 8-bit value. A byte is the smallest unit of data transferred in

a DMA channel.

Element One or more bytes to be transferred as a unit. Depending on the

programmed data type, an element is an 8-bit, 16-bit, or a 32-bit value. An element transfer cannot be interrupted; all of its bytes are transferred to a port before another channel can take control

of the port.

**Frame** One or more elements to be transferred as a unit. A frame trans-

fer can be interrupted between element transfers.

**Block** One or more frames to be transferred as a unit. Each channel

can transfer one block of data (once or multiple times). A block transfer can be interrupted between frame transfers and ele-

ment transfers.

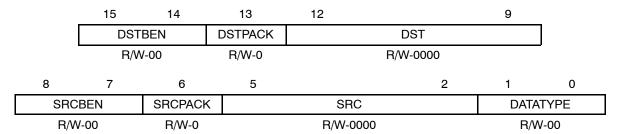

For each of the six DMA channels, you can define the number of frames in a block (with DMACFN), the number of elements in a frame (with DMACEN), and the number of bytes in an element (with the DATATYPE bits in DMACSDP). For descriptions of DMACFN, DMACEN, DMACSDP, and other registers of the DMA controller, see section 15 on page 38.

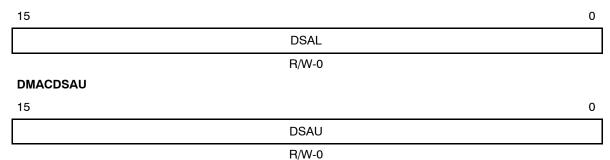

## 6 Start Addresses in a Channel

During a data transfer in a DMA channel, the first address at which data is read is called the source start address. The first address to which the data is written is called the destination start address. These are byte addresses. From the standpoint of the DMA controller, every 8 bits in memory or I/O space has its own address. Each channel contains the following registers for specifying the start addresses:

Table 4. Registers Used to Define the Start Addresses for a DMA Transfer

| Register | Load With                              |

|----------|----------------------------------------|

| DMACSSAL | Source start address (lower part)      |

| DMACSSAU | Source start address (upper part)      |

| DMACDSAL | Destination start address (lower part) |

| DMACDSAU | Destination start address (upper part) |

The following sections explain how to load the start address registers for memory accesses and I/O accesses. The DMA controller can access all of the internal and external memory and all of I/O space (which contains registers for the DSP peripherals).

#### 6.1 Start Address in Memory

Figure 9 is a high-level memory map for TMS320C55x DSPs. The diagram shows both the word addresses (23-bit addresses) used by the CPU and byte addresses (24-bit addresses) used by the DMA controller. To load the source/destination start address registers:

- Identify the correct start address. Check for any alignment constraint for the data type; see the description for the DATATYPE bits in section 15.5 (page 55). If you have a word address, shift it left by 1 bit to form a byte address with 24 bits. For example, word address 02 4000h should be converted to byte address 04 8000h.

- 2) Load the 16 least significant bits (LSBs) of the byte address into DMACSSAL (for source) or DMACDSAL (for destination).

- 3) Load the 8 most significant bits (MSBs) of the byte address into the 8 LSBs of DMACSSAU (for source) or DMACDSAU (for destination).

#### Note:

Word addresses 00 0000h-00 005Fh (which correspond to byte addresses 00 0000h-00 00BFh) are reserved for the memory-mapped registers (MMRs) of the DSP CPU.

Figure 9. High-Level Memory Map for TMS320C55x DSPs

|                    | Word Addresses<br>(Hexadecimal Ranges) | Memory | Byte Addresses<br>(Hexadecimal Ranges) |

|--------------------|----------------------------------------|--------|----------------------------------------|

| ſ                  | MMRs 00 0000-00 005F                   |        | 00 0000-00 00BF                        |

| Main data page 0 { | 00 0060-00 FFFF                        |        | 00 00C0-01 FFFF                        |

| Main data page 1   | 01 0000-01 FFFF                        |        | 02 0000-03 FFFF                        |

| Main data page 2   | 02 0000-02 FFFF                        |        | 04 0000-05 FFFF                        |

|                    |                                        |        | ·                                      |

|                    | ·                                      |        | i i                                    |

|                    |                                        |        |                                        |

|                    | ·<br>·                                 |        |                                        |

| Main data page 127 | 7F 0000-7F FFFF                        |        | FE 0000-FF FFFF                        |

#### 6.2 Start Address in I/O Space

Figure 10 is an I/O space map for TMS320C55x DSPs. The diagram shows both the word addresses (16-bit addresses) used by the CPU and byte addresses (17-bit addresses) used by the DMA controller. To load the source/destination start address registers:

- Identify the correct start address. Check for any alignment constraint for the data type; see the description for the DATATYPE bits in section 15.5 (page 55). If you have a word address, shift it left by 1 bit to form a byte address with 17 bits. For example, word address 8000h should be converted to byte address 1 0000h.

- 2) Load the 16 least significant bits (LSBs) of the byte address into DMACSSAL (for source) or DMACDSAL (for destination).

- Load the most significant bit (MSB) of the byte address into the LSB of DMACSSAU (for source) or DMACDSAU (for destination).

Figure 10. High-Level I/O Map for TMS320C55x DSPs

| Word Addresses (Hexadecimal Range) | I/O Space | Byte Addresses<br>pace (Hexadecimal Range) |  |  |

|------------------------------------|-----------|--------------------------------------------|--|--|

| 0000-FFFF                          |           | 0 0000-1 FFFF                              |  |  |

## 7 Updating Addresses in a Channel

During data transfers in a DMA channel, the DMA controller begins its read and write accesses at the start addresses you specify (as described in section 6). In many cases, after a data transfer has begun, these addresses must be updated so that data is read and written at consecutive or indexed locations. You can configure address updates at two levels:

- ☐ Block-level address updates. In the auto-initialization mode (AUTOINIT = 1 in DMACCR), block transfers can occur one after another until you turn off auto-initialization or disable the channel. If you want different start addresses for the block transfers, you can update the start addresses between the block transfers.

- □ Element-level address updates. You can have the DMA controller update the source address and/or the destination address after each element transfer. You can make sure the source address points to the start of the next element, and you can make sure the element will be precisely positioned at the destination. Choose an addressing mode for the source with the SRCAMODE bits in DMACCR. Choose an addressing mode for the destination with the DSTAMODE bits in DMACCR.

## 8 Data Burst Capability

Data bursts can be used to improve DMA throughput if one or both of the ports associated with the DMA channel support burst capability. When burst is enabled, the DMA controller executes a burst of four elements each time a channel is serviced instead of moving a single element. The DARAM ports support burst capability. The EMIF port supports bursts only if the requested address range is configured as a synchronous (burst) memory type. If the requested address is configured as asynchronous memory, the DMA will perform four single accesses to move the burst of data. The peripheral port does not support burst capability. The DMA will perform four single peripheral-port accesses to move the burst data.

If burst is used, the start addresses for the source and destination should be aligned on a burst boundary. Burst boundaries correspond to byte addresses with 0h as the least significant 4 bits.

To use burst, the following conditions should be met:

| The start address for the port on which burst is enabled should be on a burst boundary.                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| The element index should be 1.                                                                                                                           |

| The frame index should cause each burst access to align on a burst boundary.                                                                             |

| (Element number x Element size) should align on a burst boundary. This means at the end of each frame the address should be aligned on a burst boundary. |

If both the source and destination have burst enabled, but the source address does not start on a burst boundary, the source burst will be automatically disabled internally. The source will load the channel FIFO and, when enough data is available, a destination burst will be executed. If the destination does not start on a burst boundary, the destination accesses will be performed as single accesses.

If the frame size is not a multiple of 4 elements, the remaining 1 to 3 elements at the end of the frame will be transferred as single (nonburst) accesses.

# 9 Data Packing

The DMA controller can perform data packing to double or quadruple the amount of data passed to the destination or source in a single transfer. For example, if an 8-bit data type is selected and the destination port has a 32-bit data bus, four 8-bit pieces of data can be packed into 32 bits before being sent to the destination. The resultant packed data depends on the bus size for the destination or source port as shown in Table 5.

Table 5. Data Packing Performed by the DMA Controller

| Port       | Data Type | Data Packing                               |

|------------|-----------|--------------------------------------------|

| DARAM      | 8-bit     | Four 8-bit data values packed into 32 bits |

|            | 16-bit    | Two 16-bit data values packed into 32 bits |

| EMIF       | 8-bit     | Four 8-bit data values packed into 32 bits |

|            | 16-bit    | Two 16-bit data values packed into 32 bits |

| Peripheral | 8-bit     | Two 8-bit data values packed into 16 bits  |

The addressing mode used for the destination and source ports also affects whether or not the DMA controller tries to pack data. The conditions that have to be met for both 32-bit and 16-bit data packing are listed in Table 6 and Table 7, respectively.

Table 6. 32-bit Data Packing Conditions†

| Data Type | Byte Address<br>Lower Bits | Addressing Mode     | Element Index | Access |

|-----------|----------------------------|---------------------|---------------|--------|

| 8-bit     | 00b                        | Post Increment      | -             | Packed |

|           |                            | Single/Double Index | 1             | Packed |

|           |                            |                     | Other         | Single |

|           |                            | Constant            | -             | Single |

|           | 11b                        | Single/Double Index | -1            | Packed |

|           |                            | Other               | -             | Single |

|           | Other                      | -                   | -             | Single |

| 16-bit    | 00b                        | Post Increment      | -             | Packed |

|           |                            | Single/Double Index | 1             | Packed |

|           |                            |                     | Other         | Single |

|           |                            | Constant            | -             | Single |

|           | 10b                        | Single/Double Index | -3            | Packed |

|           |                            | Other               | -             | Single |

|           | Other                      | -                   | -             | Single |

<sup>&</sup>lt;sup>†</sup> Remaining bytes to be transferred is greater than or equal to 4 bytes.

Table 7. 16-bit Data Packing Conditions†

| Data Type | Byte Address<br>Lower Bits | Addressing Mode     | Element Index | Access |

|-----------|----------------------------|---------------------|---------------|--------|

| 8-bit     | 00b or 10b                 | Post Increment      | -             | Packed |

|           |                            | Single/Double Index | 1             | Packed |

|           |                            |                     | Other         | Single |

|           |                            | Constant            | -             | Single |

|           | 11b or 01b                 | Single/Double Index | -1            | Packed |

|           |                            | Other               | -             | Single |

<sup>&</sup>lt;sup>†</sup> Remaining bytes to be transferred is greater than or equal to 2 bytes.

When using element synchronization, no data packing is performed when reading from the source port if that source port is event driven (see section 2, page 12). If the source port is non-event driven, data packing will be performed if packing is enabled at the source (SRCPACK = 1), regardless of whether or not element synchronization is used. However, only one element will be transferred to the destination on every event.

# 10 Write Posting: Buffering Writes to Internal Memory

The DMA controller can take advantage of the write-posting capability of the internal memory interface. When the write posting bit is set (WP = 1 in DMACCR), the DMA controller can initiate a write and then can receive acknowledgement from the internal memory interface before the data is actually written to memory. The DMA controller is free to begin the next operation while the internal memory interface assumes control of the posted data.

When write posting is disabled (WP = 0), the DMA controller waits for the internal memory interface to finish the memory access before continuing with the next operation. It might be useful during debugging to disable write posting.

#### 11 Synchronizing Channel Activity to an Event

Activity in a channel can be synchronized to an event in a DSP peripheral or to an event signaled by the driving of an external interrupt pin. Using the SYNC bits of DMACCR, you can specify which synchronization event (if any) triggers activity.

Each channel also has an FS bit in DMACCR that allows you to choose among two synchronization modes:

- □ Element synchronization mode (FS = 0) requires one event per element transfer. When the selected synchronization event occurs, an element is transferred from the channel FIFO buffer to the destination port. When all the bytes of the current element are transferred, the channel makes no more requests to the destination port until the next occurrence of the synchronization event. The channel will request data from the source port as described below.

- Frame synchronization mode (FS = 1) requires one event to trigger an entire frame of elements. When the event occurs, an entire frame of elements is transferred from the channel FIFO buffer to the destination port. When all the elements in the frame are transferred, the channel makes no more requests to the destination port until the next occurrence of the event. The channel will request data from the source port as described below.

If a synchronization event is specified and the source port is event driven (see Table 8), the channel will not place an access request to the source port until the event occurs. When the event occurs, the channel will take data from the source port, place it in its FIFO buffer, and place an access request to the destination port. Requests received by the source or destination ports are handled according to the predefined position and the programmed priority of the channel in the DMA service chain (see section 4, page 19).

Table 8. Event and Non-Event Driven Ports

| Port            | Category         |

|-----------------|------------------|

| DARAM           | Non-event driven |

| External memory | Non-event driven |

| Peripheral      | Event driven     |

On the other hand, if the source port being used is non-event driven, the channel will place an access request to the source port immediately after it is enabled (EN = 1 in DMACCR) without waiting for the event. For the remainder of the block, the channel will continue to make source read requests to keep the FIFO buffer filled. The read requests from the source will stop only when the FIFO is full or when all of the source data for the current block has been moved into the FIFO. The channel will not access more than one block at a time. After the event occurs, the channel will transfer data from FIFO buffer to the destination port. The amount of data that is transferred to the destination port at each event depends on the use of frame or element synchronization. The channel will request more data from the source port as soon as there is space in the channel FIFO and as long as the entire block has not been completely copied to the channel FIFO. Read or write requests to the different ports are handled according to the predefined position and the programmed priority of the channel in the DMA service chain (see page 6).

If you choose not to synchronize the channel (SYNC = 00000b), the channel sends an access request to the source port as soon as the channel is enabled (EN = 1 in DMACCR). Setting EN = 1 initiates the transfer of the entire block defined for the channel.

#### 11.1 Checking the Synchronization Status

Each channel has a synchronization flag (SYNC) in its status register, DMACSR. When the synchronization event occurs, the DMA controller sets the flag (SYNC = 1). The flag is cleared (SYNC = 0) as follows:

- ☐ If the source port is event driven, the SYNC bit is cleared when the source port initiates the request placed by the DMA channel.

- If the source port is non-event driven, the SYNC bit is cleared when the destination port initiates the request placed by the DMA channel.

#### 11.2 Dropped Synchronization Event

If a synchronization event occurs before the DMA controller is done servicing the previous one (before the DMA controller clears the SYNC bit in DMACSR), a synchronization event has been dropped. The DMA controller responds to an event drop in the following manner:

- After the current element transfer, activity in the channel stops.

- ☐ If the corresponding interrupt enable bit is set (DROPIE = 1 in DMACICR), the DMA controller also sets the event drop status bit (DROP = 1 in DMACSR) and sends an interrupt request to the CPU. For more details, see *Monitoring Channel Activity* on page 32.

Before initiating the next DMA transfer, the CPU must clear the error condition by making EN = 0 in DMACCR.

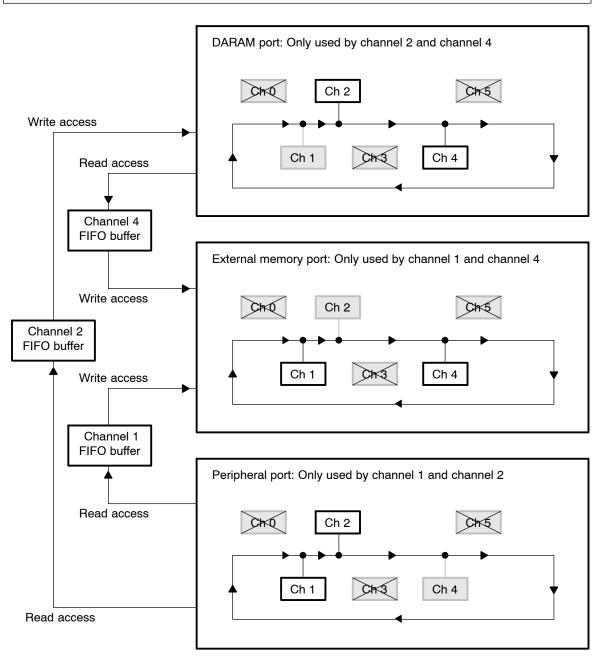

# 12 Monitoring Channel Activity

The DMA controller can send an interrupt to the CPU in response to the operational events listed in the following table. Each channel has interrupt enable (IE) bits in the interrupt control register (DMACICR) and some corresponding status bits in the status register (DMACSR). (DMACICR and DMACSR are described in section 15.4 on page 49.) If one of the operational events in the table occurs, the DMA controller checks the corresponding IE bit and acts accordingly:

- If the IE bit is 1 (the interrupt is enabled), the DMA controller sets the corresponding status bit and sends the associated interrupt request to the CPU. DMACSR is automatically cleared if your program reads the register.

- If the IE bit is 0, the DMA controller sets the corresponding status bit but does not send an interrupt to the CPU.

DMACSR also has a SYNC bit that is used if you choose a synchronization event for the channel. SYNC indicates when the selected synchronization event has occurred (SYNC = 1) and when it has been serviced (SYNC = 0). For more details about synchronization events, see *Synchronizing Channel Activity* on page 30.

Table 9. DMA Controller Operational Events and Their Associated Bits and Interrupts

| Operational Event                                             | Interrupt Enable Bit | Status Bit | Associated Interrupt |

|---------------------------------------------------------------|----------------------|------------|----------------------|

| Address error has occurred                                    | AERRIE               | AERR       | Channel interrupt    |

| Block transfer is complete                                    | BLOCKIE              | BLOCK      | Channel interrupt    |

| Last frame transfer has started                               | LASTIE               | LAST       | Channel interrupt    |

| Frame transfer is complete                                    | FRAMEIE              | FRAME      | Channel interrupt    |

| First half of current frame has been transferred <sup>†</sup> | HALFIE               | HALF       | Channel interrupt    |

| Synchronization event has been dropped                        | DROPIE               | DROP       | Channel interrupt    |

| Time-out error has occurred                                   | TIMEOUTIE            | TIMEOUT    | Channel interrupt    |

<sup>&</sup>lt;sup>†</sup> For a frame with an odd number of elements, the half-frame event occurs as soon as the number of elements transferred is greater than the number that remain to be transferred. For example, for a frame of five elements, the half-frame event occurs when the DMA controller has transferred three of the elements.

#### 12.1 Channel Interrupt

Each of the six channels has its own interrupt. As shown Figure 11, the channel interrupt is the logical OR of all the enabled operational events. You can choose any combination of these events by setting or clearing the appropriate interrupt enable (IE) bits in the interrupt control register (DMACICR) for the channel. You can determine which event(s) caused the interrupt by reading the bits in the status register (DMACSR) for the channel. A read of DMACSR clears all of the status bits. DMACSR should be read each time an interrupt occurs to clear the pending status bits.

Figure 11. Triggering a Channel Interrupt Request

As an example of using the interrupt enable bits, suppose you are monitoring activity in channel 1, and suppose that in DMACICR:

AERRIE = 0 BLOCKIE = 0 LASTIE = 0 FRAMEIE = 1 HALFIE = 0 DROPIE = 1 TIMEOUTIE = 0

When the current frame transfer is done or if a synchronization event is dropped (see section 11.2 on page 31), the channel 1 interrupt request is sent to the CPU. No other event can generate the channel 1 interrupt. To determine whether one or both of the events triggered the interrupt, you can read the DROP and FRAME bits in DMACSR.

The channel 1 interrupt sets its corresponding flag bit in an interrupt flag register of the CPU. The CPU can respond to the interrupt or ignore the interrupt.

For more details about DMACICR and DMACSR, see section 15.4 on page 49.

#### 12.2 Time-Out Error Condition

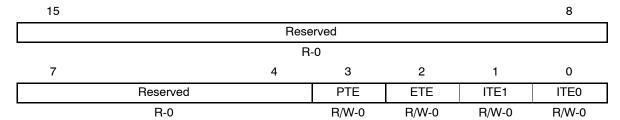

The DMA controller has a time-out counter for each of the four DMA ports (internal memory port 0, internal memory port 1, the external memory port, and the peripheral port). The clock that controls the DMA controller runs on the fast peripherals clock (SYSCLK1) that has been programmed inside the TMS320VC5501/5502 DSPs. Once a DMA transfer is requested at one of the ports, the corresponding time-out counter is incremented every SYSCLK1 cycle. If the transfer has not been completed within 512 SYSCLK1 cycles, a time-out error signal is generated. The time-out counter for all four DMA ports is disabled by default, but can be enabled for each individual port through the DMAGTCR.

In response to a time-out error signal, activity in the affected DMA channel stops. If the corresponding interrupt enable bit is set (TIMEOUTIE = 1 in DMACICR), the DMA controller also sets the time-out status bit (TIMEOUT = 1 in DMACSR) and sends a channel interrupt request to the CPU. The CPU can respond to the interrupt request or ignore the interrupt request.

Before the next DMA transfer is initiated, the CPU must clear the time-out error condition by making EN = 0 in DMACCR.

#### 12.3 Address Error Condition

If the DMA controller accesses a reserved address in the I/O space of the DSP, an address error signal is generated in the DMA controller. In response, activity in the effected DMA channel stops. If the corresponding interrupt enable bit is set (AERRIE = 1 in DMACICR), the DMA controller also sets the address error status bit (AERR = 1 in DMACSR) and sends a channel interrupt request to the CPU. The CPU can respond to the interrupt request or ignore the interrupt request.

Before the next DMA transfer is initiated, the CPU must clear the address error condition by making EN = 0 in DMACCR.

#### 12.4 Bus Error Interrupt

The following actions by the CPU will cause the DMA controller to send a bus error interrupt (BERRINT) request to the CPU. The CPU can respond to the interrupt request or ignore the interrupt request.

- ☐ The CPU attempts to access a reserved address in the DMA register map.

- The CPU attempts to write an illegal/reserved value to a register or to a field inside a register. Here are two important examples:

- The CPU attempts to load an address register with an unaligned address (an address that is not properly aligned according to the chosen data type).

- The CPU attempts to load an index register with an index that would create an unaligned address.

# 13 Latency in DMA Transfers

Each element transfer in a channel is composed of a read access (a transfer from the source location to the channel buffer) and a write access (a transfer from the channel buffer to the destination location). The time to complete this activity depends on factors such as:

The selected frequency of the fast peripherals clock (SYSCLK1) signal.

| _ | This signal, as propagated to the DMA controller, determines the timing for all DMA transfers.                                                                                                                                                                                             |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Wait states or other extra cycles added by or resulting from an interface.                                                                                                                                                                                                                 |

|   | Activity on other channels. Since channels are serviced in a sequential order, the number of pending DMA service requests in the other channels affects how often a given channel can be serviced. For more details on how the channels are serviced, see <i>Service Chain</i> on page 19. |

|   | The timing of synchronization events (if the channel is synchronized). The DMA controller cannot service a synchronized channel until the synchronization event has occurred. For more details on synchronization, see <i>Synchronizing Channel Activity</i> on page 30.                   |

The minimum (best-case) latency is determined by the ports used. On the DARAM ports, one access can be performed every cycle if the DMA is not competing with the CPU for access to the same memory block. The best-case transfer rate for channels using the DARAM ports would be one cycle to read at the source and one cycle to write at the destination. The minimum latency for the EMIF port is determined by the EMIF settings, including the memory type used, programmable timings, and any delays caused by the memory itself (such as control of the ARDY pin). The latency for the peripheral port is dependent on the peripherals being accessed and the configuration of the fast and slow peripheral clocks supplied to those peripherals. As explained in section 1.3, page 11, the CPU will always have higher priority than the DMA controller for accesses to the same DARAM block in internal memory.

### 14 Power, Emulation, and Reset Considerations

The following sections describe how to put the DMA controller into a low-power state, how to program the response of the DMA controller to debugger breakpoints, and what values the DMA controller registers have after a DSP reset.

### 14.1 Reducing Power Consumed by the DMA Controller (Idle Configurations)

The DSP is divided into idle domains that can be programmed to be idle or active. The state of all domains is called the idle configuration. Any idle configuration that disables the clock generator domain and/or the DMA domain stops the DMA clock and, therefore, stops activity in the DMA controller. The type of channel synchronization (if any) determines how quickly the DMA controller stops:

| No synchronization (SYNC = 00000b in DMACCR). The DMA controller |

|------------------------------------------------------------------|

| stops after the entire block transfer is completed.              |

|                                                                  |

- ☐ Frame synchronization (SYNC is nonzero and FS = 1 in DMACCR). The DMA controller stops after the current frame transfer is completed.

- ☐ Element synchronization (SYNC is nonzero and FS = 0 in DMACCR). The DMA controller stops after the current element transfer is completed.

When the DMA domain is idle, there is one case when it can be temporarily reactivated without a change in the idle configuration. If one of the multichannel buffered serial ports (McBSPs) needs the DMA controller for a data transfer, the DMA controller will leave its idle state to perform the data transfer and then enter its idle state again.

### 14.2 Emulation Modes of the DMA Controller

The FREE bit of DMAGCR controls the behavior of the DMA controller when an emulation breakpoint is encountered. If FREE = 0 (the reset value), a breakpoint suspends DMA transfers. If FREE = 1, DMA transfers are not interrupted by a breakpoint.

### 14.3 DMA Controller after DSP Reset

A DSP reset resets the DMA controller and the DMA configuration registers. The register definitions that follow indicate the effects of a DSP reset on the register contents.

### 15 DMA Controller Registers

Table 10 lists the types of registers in the direct memory access (DMA) controller. There are two registers that affect all channels: the global control register (DMAGCR) and the global time-out control register (DMAGTCR). In addition, for each of the DMA channels, there are 16 channel configuration registers. For the I/O address of each register, see the data manual for your TMS320C55x DSP.

If the CPU attempts to access a reserved address in the DMA register map, the DMA controller will send a bus error interrupt (BERRINT) request to the CPU. The CPU can respond to the interrupt request or ignore the interrupt request.

Table 10. Registers of the DMA Controller

| Register | Description                                                            | For Details, See |

|----------|------------------------------------------------------------------------|------------------|

| DMAGCR   | Global control register (only one)                                     | Page 39          |

| DMAGTCR  | Global time-out control register (only one)                            | Page 40          |

| DMACCR   | Channel control register (one for each channel)                        | Page 42          |

| DMACICR  | Interrupt control register (one for each channel)                      | Page 49          |

| DMACSR   | Status register (one for each channel)                                 | Page 49          |

| DMACSDP  | Source and destination parameters register (one for each channel)      | Page 55          |

| DMACSSAL | Source start address (lower part) register (one for each channel)      | Page 60          |

| DMACSSAU | Source start address (upper part) register (one for each channel)      | Page 60          |

| DMACDSAL | Destination start address (lower part) register (one for each channel) | Page 61          |

| DMACDSAU | Destination start address (upper part) register (one for each channel) | Page 61          |

| DMACEN   | Element number register (one for each channel)                         | Page 62          |

| DMACFN   | Frame number register (one for each channel)                           | Page 62          |

Table 10. Registers of the DMA Controller (Continued)

| Register | Description                                                 | For Details, See |

|----------|-------------------------------------------------------------|------------------|

| DMACSEI  | Source element index register (one for each channel)        | Page 64          |

| DMACSFI  | Source frame index register (one for each channel)          | Page 64          |

| DMACDEI  | Destination element index register (one for each channel)   | Page 64          |

| DMACDFI  | Destination frame index register (one for each channel)     | Page 64          |

| DMACSAC  | Source address counter register (one for each channel)      | Page 67          |

| DMACDAC  | Destination address counter register (one for each channel) | Page 67          |

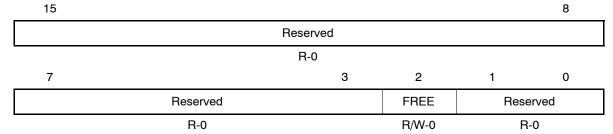

## 15.1 Global Control Register (DMAGCR)

The global control register (see Figure 12) is a 16-bit I/O-mapped register used to set the emulation mode of the DMA controller.

Figure 12. Global Control Register (DMAGCR)

**Legend:** R = Read; W = Write; -n = Value after reset

Table 11. DMAGCR Bit Fleld Descriptions

| Bit  | Field    | Value | Description                                                                                                       |

|------|----------|-------|-------------------------------------------------------------------------------------------------------------------|

| 15-3 | Reserved |       | Writing to these bits has no effect. Reading these bits returns 0s.                                               |

| 2    | FREE     |       | Emulation mode bit. FREE controls the behavior of the DMA controller when an emulation breakpoint is encountered: |

|      |          | 0     | A breakpoint suspends DMA transfers.                                                                              |

|      |          | 1     | DMA transfers continue uninterrupted when a breakpoint occurs.                                                    |