# Throughput Performance Guide for KeyStone II Devices

Multicore Processors

#### **ABSTRACT**

This application report analyzes various performance measurements of the KeyStone II family of processors. It provides a throughput analysis of the various support peripherals to different end-points and memory access.

|        | Contents                                                      |     |

|--------|---------------------------------------------------------------|-----|

| 1      | Introduction                                                  |     |

| 2      | KeyStone II Device Overview                                   |     |

| 3      | Memory Access Throughput Performance                          |     |

| 4      | DDR3 Throughput                                               |     |

| 5      | EDMA Throughput                                               |     |

| 6      | PCIe                                                          |     |

| 7<br>8 | SRIO Throughput                                               |     |

| 9      | 10 Gigabit Ethernet Throughput                                |     |

| 10     | References                                                    |     |

| . •    |                                                               |     |

|        | List of Figures                                               |     |

| 1      | Throughput Comparison Between KeyStone-II TCs                 | . 9 |

| 2      | EDMA Transfer Between CorePac0 L2 and CorePac1 L2             | 12  |

| 3      | EDMA Transfer Between CorePac0 L2 and MSMC SRAM               | 14  |

| 4      | EDMA Throughput Between MSMC SRAM and MSMC SRAM               | 15  |

| 5      | EDMA Transfer Between MSMC SRAM and DDR3A or DDR3B            | 16  |

| 6      | EDMA Throughput Between DDR3A and DDR3A                       | 18  |

| 7      | EDMA Throughput Between Different CorePac L2s to DDR3A        | 19  |

| 8      | Impact of Transfer Size on Throughput                         | 20  |

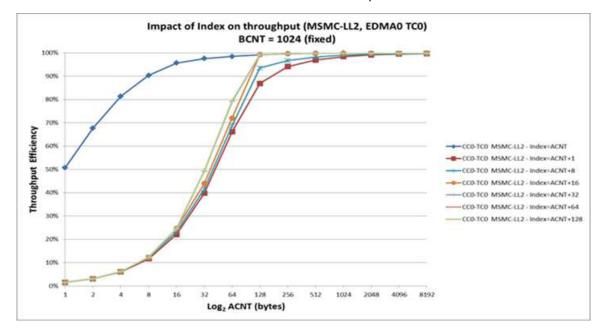

| 9      | Impact of Index on Throughput                                 | 21  |

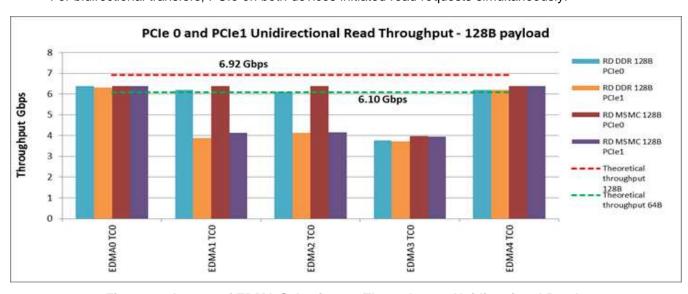

| 10     | Impact of EDMA Selection on Throughput – Unidirectional Reads | 24  |

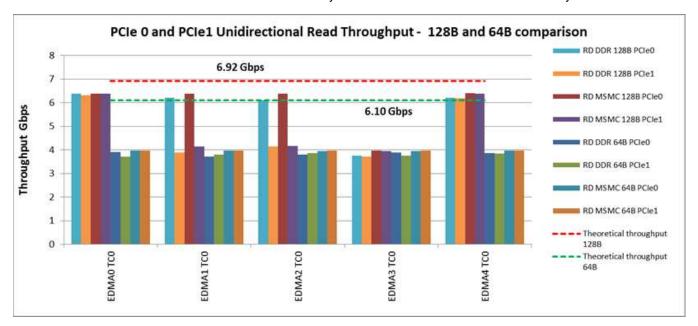

| 11     | Comparing 128B and 64B Payload Size – Unidirectional Reads    | 25  |

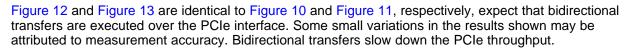

| 12     | Impact of EDMA Selection on Throughput – Bidirectional Reads  | 26  |

| 13     | Comparing 128B and 64B Payload Size – Bidirectional Reads     | 26  |

| 14     | Impact of EDMA Selection on Write Throughput                  | 27  |

| 15     | Comparing 128B and 64B Payload Size                           | 28  |

| 16     | DirectIO NWRITE Throughput With 3 Gbps PHY With Overhead      | 31  |

| 17     | DirectIO NWRITE Throughput With 5 Gbps PHY With Overhead      | 31  |

| 18     | DirectIO NREAD Throughput With 3 Gbps PHY With Overhead       | 32  |

| 19     | DirectIO NREAD Throughput With 5Gbps PHY With Overhead        | 32  |

| 20     | Type 11 Throughput With 3 Gbps PHY With Overhead              | 34  |

| 21     | Type 11 Throughput With 5 Gbps PHY With Overhead              | 35  |

| 22     | Maximum Achievable and Measured Write Throughput              | 37  |

All trademarks are the property of their respective owners.

Introduction www.ti.com Measured Throughput 40 List of Tables

#### 1 Introduction

The purpose of this document is to provide throughput performance data for Keystone II Architecture devices. This document provides theoretical and measured throughput performance for Keystone II memories and peripherals. Note that not all peripherals are supported by all devices. For a particular device, see the table or the device-specific data manual to determine which peripherals are supported.

In addition to throughput performance data, this document also provides an overview of the TeraNet switch fabric implemented on Keystone II devices. Lastly, this document provides a basis for estimating memory access performance and presents theoretical and measured performance data achieved under various operating conditions. Some factors affecting memory access performance also are detailed.

www.ti.com Introduction

#### 1.1 Acronyms Used In This Document

| Acronym | Definition                                |

|---------|-------------------------------------------|

| DSP     | Digital Signal Processor                  |

| DDR     | Dual Data Rate                            |

| EMIF    | External Memory Interface Controller      |

| EDMA3   | Enhanced Direct Memory Access v3.0        |

| LSU     | Load Store Unit                           |

| MSMC    | Multicore Shared Memory Controller        |

| PCle    | Peripheral Component Interconnect Express |

| SDMA    | Slave Direct Memory Access                |

| SDRAM   | Synchronous Dynamic Random Access Memory  |

| SRIO    | Serial Rapid Input Output                 |

| TPDMA   | Third Party DMA Engine                    |

| TPCC    | TPDMA Channel Controller                  |

| TPTC    | TPDMA Transfer Controller                 |

| XMC     | Extended Memory Controller                |

#### 2 **KeyStone II Device Overview**

This section focuses on the TeraNet switch fabric that provides the interconnect between C66x CorePac, ARM CorePac, peripherals, and memories. The high-level details provided in this section are required to understand the throughput performance of the C66x DSP, because the bus widths and the operating frequencies of each part of the TeraNet directly impact the throughput performance of the connected peripherals or memories.

#### 2.1 C66x CorePac Overview

This section provides the fundamental details of the C66x CorePac. Additional details about the C66x CorePac can be found in the C66x CorePac User's Guide (SPRUGW0). The C66x CorePac consists of several components including:

- C66x DSP core

- L1 and L2 memories

- External memory controller

- Extended memory controller (XMC)

- Interrupt controller

- Power and sleep controller

- Embedded trace buffer

- Data trace formatter

- RSA accelerator (core 1 and 2 only)

Each CorePac has the ability to sustain up to 128 bits of load/store operations per cycle to L1D memory and is capable of handling up to 16 GB/second. When accessing data in the L2 memory or external memory, the access rate depends on the memory access pattern and the cache. The cache size varies depending on the platform.

Within each CorePac, there is an internal DMA (IDMA) engine that can move data at the frequency rate of DSP/2 with a data width of 256 bits. The IDMA operates in the background of the DSP core activity (i.e., data can be brought into buffer A while the DSP core is accessing buffer B). The IDMA can transfer data only between the L1 and L2 memories and peripheral configuration ports; it cannot access external memory.

#### 2.2 ARM CorePac Overview

This section provides the fundamental details of the ARM CorePac. Additional details about the ARM CorePac can be found in the *ARM CorePac User's Guide* (SPRUGW0). The ARM CorePac consists of several components including:

- Cortex -A15 processor revision R2P4

- L1 and L2 cache memories

- NEON Media Coprocessor

- Interrupt Controller

- AXI protocol external interface

- Non-invasive Debug Support

- Clock Generation (dedicated ARM PLL)

Each ARM CorePac is capable of supporting 16 word line access using a 128-bit interface to L1 and L2 instruction and data cache. The KeyStone II ARM CorePac supports a shared L2 cache across the cluster and the cache size varies depending on the number of ARM cores (4MB quad, 1MB dual and 512KB). The NEON coprocessor implements the advanced SIMDv2 media processing architecture and the VFPv4 Floating Point architecture. The external interface uses the AXI protocol configured to 128-bit data width.

Within each CorePac, there is an internal DMA (IDMA) engine that can move data at the frequency rate of DSP/2 with a data width of 256 bits. The IDMA operates in the background of the DSP core activity (i.e., data can be brought into buffer A while the DSP core is accessing buffer B). The IDMA can transfer data only between the L1 and L2 memories and peripheral configuration ports; it cannot access external memory.

#### 2.3 TeraNet Overview

The TeraNet switch fabric provides interconnection between the C66x CorePac (and their local memories), MSMC memory, ARM CorePac, external memory, the enhanced DMA v3 (EDMA3) controllers, Multicore Navigator, on-chip coprocessors, and high-speed IO. The TeraNet switch fabric allows each of these to operate at maximum efficiency with no blocking or stalling. It allows for concurrent transfers between non-conflicting master/slave pairs and can support a very high total data rate across any endpoint. If transfers line up such that the source or destination memory is the same, then collisions occur and certain transactions will be blocked.

The TeraNet consists of data switch fabric and configuration switch fabric:

- **Data Switch Fabric:** The data switch fabric mainly moves data across the system and is further subdivided into two smaller switch fabrics. One connects high speed masters to slaves via 256-bit data buses running at the DSP/3 frequency. The second data switch fabric connects high-speed masters to slaves via 128-bit data buses running at a DSP/3 frequency.

- Configuration Switch Fabric: This switch fabric is mainly used to access peripheral registers. It connects the C66x CorePac and masters on the data switch fabric to slaves via 32-bit configuration buses running at either DSP/3 or DSP/6 frequency.

KeyStone II devices contain up to five EDMA Channel Controllers: TPCC0, TPCC1, TPCC2, TPCC3, and, TPCC4. Each TPCC can be programmed to move data concurrently in the background without the expense of any DSP cycles. These TPCCs can move data between on-chip L1 and L2 memory, MSMC SRAM, external memory, and the peripherals on the device that support EDMA-based transfer.

The TeraNet also provides connection to the Multicore Navigator which uses a Queue Manager Subsystem (QMSS) and a Packet DMA (PKTDMA) to control and implement high-speed data packet movement within the device. Frequent tasks are commonly off-loaded from the host processor to peripheral hardware to increase system performance.

The TeraNet also provides a 64-bit DDR3A and 64-bit DDR3B interface to support access to external memories that can be used for either data or program memory.

### 2.4 Memory Access System Overview

This section discusses the KeyStone II memory system. Memory access is critical for applications running on the device. Some memories are internal to the CorePacs, while other system memories are external to the CorePacs. The memory system also provides a 64-bit DDR3A and 64-bit DDR3B interface for accessing off-chip memory.

Internal to each DSP CorePac are the following memories:

- DSP L1D SRAM that can be used as either data memory or data cache or both.

- DSP L1P SRAM that can be used as either program memory or cache or both.

- DSP Local L2 SRAM that can be used as either unified SRAM or unified cache or both.

Internal to each ARM CorePac are the following memories:

- ARM L1D for data cache.

- ARM L1P for program memory cache.

- Shared and coherent ARM L2 cache for both data and program memory.

DSP L1D SRAM, DSP L1P SRAM, DSP L2 SRAM, MSMC SRAM, and DDR3 memories are accessible by all the cores and multiple DMA masters on the device.

External to the CorePacs, the KeyStone II devices have multicore shared memory (MSMC) SRAM, which is shared between the cores. The MSMC memory can be configured in two ways:

- SL2 mode: Shared L2 SRAM mode: L1P/L1D memory will cache MSMC, whereas L2 will not cache requests to MSMC SRAM. Only available for C66x DSP and not for ARM A15.

- SL3 mode: Level 3 SRAM mode: Both L1P/L1D and L2 memories will cache the MSMC SRAM if it is remapped to an external address using the address extension unit. For more information, see the KeyStone Architecture Multicore Shared Memory Controller (MSMC) User's Guide (SPRUGW7)

A 64-bit EMIF interface is provided for accessing off-chip DDR3A and DDR3B SDRAM, which can be used as data or program memory. Although this interface supports a 64-bit data bus, it can also be configured to operate using a 32-bit or 16-bit data bus.

#### 3 Memory Access Throughput Performance

This section discusses the memory access throughput performance of KeyStone II devices. The bandwidth of a memory copy is determined by the lowest of these three factors:

- Bus bandwidth

- Source throughput

- Destination throughput

Table 1 summarizes the maximum theoretical bandwidth of the C66x core, IDMA, and the EDMA when the Main PLL is operating at 1.2 GHz.

Table 1. Theoretical Bandwidth of Core, IDMA and EDMA

| Master                                                           | Maximum Bandwidth MB/s                                                | Comments                                      |

|------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|

| C66x Core                                                        | 19200                                                                 | (128bits)/(8bit/byte)*(1200M)=19200MB/s       |

| ARM A15 Core                                                     | 19200                                                                 | (256bits)/(8bit/byte)*(1200M/2)=19200MB/s     |

| EDMA0(Single TC)                                                 | e TC) 19200 (256bits)/(8bit/byte)*(1200M/2)=19200MB/s (1)             |                                               |

| EDMA1(Single TC)                                                 | <b>EDMA1(Single TC)</b> 6400 (128bits)/(8bit/byte)*(1200M/3)=6400MB/s |                                               |

| EDMA2(Single TC)                                                 | 6400                                                                  | (128bits)/(8bit/byte)*(1200M/3)=6400MB/s      |

| EDMA3(Single TC)                                                 | 6400                                                                  | (128bits)/(8bit/byte)*(1200M/3)=6400MB/s      |

| EDMA4(Single TC) 19200 (256bits)/(8bit/byte)*(1200M/2)=12800MB/s |                                                                       | (256bits)/(8bit/byte)*(1200M/2)=12800MB/s (2) |

<sup>(1) 66</sup>AK2E and AM5K2E devices have EDMA\_0 at CPU/3 on the TeraNet CPU/3 node.

<sup>(2)</sup> For AM5K2E and 66AK2E devices, EDMA0 is at CPU/3 speed resulting in a theoretical bandwidth of (256 bits)/(8 bit/byte)\*(1200M/3)=12800MB/s.

Table 2 summarizes the maximum theoretical throughput of different memories when the C66x Main PLL is operating at 1.2 GHz. The DDR3 performance assumes that a 64-bit bus width is used and that the external memory is operating at 1600 Mtps.

**Table 2. Theoretical Bandwidth of Different Memories**

| Master    | Maximum Bandwidth MB/s | Comments                                   |  |  |  |

|-----------|------------------------|--------------------------------------------|--|--|--|

| DSP L1D   | 38400                  | (256bits)/(8bit/byte)*(1200M)=38400MB/s    |  |  |  |

| DSP L1P   | 38400                  | (256bits)/(8bit/byte)*(1200M)=38400MB/s    |  |  |  |

| DSP L2    | 16000                  | (256 bits)/(8bit/byte)*(1200M/2)=16000MB/s |  |  |  |

| MSMC RAM  | 38400                  | (256bits)/(8bit/byte)*(1200M)=38400MB/s    |  |  |  |

| DDR3A RAM | 12800                  | (64 bits)/(8bit/byte)*(800M)*2=12800MB/s   |  |  |  |

| DDR3B RAM | 12800                  | (64 bits)/(8bit/byte)*(800M)*2=12800MB/s   |  |  |  |

When the C66x core tries to read from or write to different memory endpoints, it consumes some DSP cycles to access the memory region depending on various factors such as prefetching, caching, victim buffer hits, and so on. Section 3.1 and Section 3.2 estimate the number of DSP stalls for accessing different memory endpoints.

Note that MSMC SRAM has up to 8 memory banks of 256 bits. As mentioned previously, MSMC can be configured in either shared L2 (SL2) mode or shared L3 (SL3) mode. Also, the latencies to ARM CorePac L2 memory and DDR3 memory varies based on the number of ARM cores in the SoC.

### 3.1 Memory Read Performance

The C66x core has an improved pipeline between L1D/L1P and L2 memory controller and this significantly reduces the stall cycles for L1D/L1P cache misses.

Table 3 shows the comparison of KeyStone I to KeyStone II DSP stalls for accessing different memories when the DSP core tries to read from memory.

Table 3. C66x DSP Memory Read Performance

|                  | Key         | Stone I                | KeyStone II  DSP Stalls in cycles |            |  |  |

|------------------|-------------|------------------------|-----------------------------------|------------|--|--|

|                  | DSP Stal    | ls in cycles           |                                   |            |  |  |

| Source           | Single Read | Single Read Burst Read |                                   | Burst Read |  |  |

| L1D Hit          | 0           | 0                      | 0                                 | 0          |  |  |

| L2 SRAM          | 7           | 3.5                    | 7                                 | 3.5        |  |  |

| L2 Cache Hit     | 9           | 5                      | 9                                 | 5          |  |  |

| MSMC RAM (SL2)   | 20          | 7                      | 22                                | 7          |  |  |

| MSMC RAM (SL3)   | 23          | 10                     | 25 8                              |            |  |  |

| DDR 3A RAM (SL3) | 100         | 31                     | 103                               | 30         |  |  |

| DDR 3B RAM (SL3) | N/A         | N/A                    | 152                               | 43         |  |  |

The test case details are as follows:

- KeyStone I testing is done on a 1.2 GHz DSP with MSMC at 600MHz and DDR frequency at 1600 MT/s.

- KeyStone II testing is done on a 1.2GHz DSP with MSMC at 1.2GHz and DDR3 frequency at 1600 MT/s.

- Single read scenarios represent endpoint access latency.

- Burst read scenarios

- 1 read miss per cycle

- L2 cache is enabled, cold cache

- Stride = 128 bits

- Prefetch is enabled (SL2/SL3)

- No victims assumed for read latency measurements.

- DDR3 accesses to open pages.

Table 4 shows the KeyStone II ARM stalls for accessing different memories when the ARM core tries to read from memory.

**Table 4. ARM A15 Memory Read Performance**

|                  | KeyStone II |               |  |  |  |  |

|------------------|-------------|---------------|--|--|--|--|

|                  | A15 load t  | o use latency |  |  |  |  |

| Source           | Single Read | Burst Read    |  |  |  |  |

| L1 Cache Hit     | 4           | 0.8           |  |  |  |  |

| L2 Cache Hit     | 20          | 4.4           |  |  |  |  |

| MSMC RAM (SL3)   | 54          | 12            |  |  |  |  |

| DDR 3A RAM (SL3) | 140         | 18            |  |  |  |  |

| DDR 3B RAM (SL3) | 197         | 23            |  |  |  |  |

The test case details are as follows:

- KeyStone II testing is done on a 1.4GHz ARM with MSMC at 1.2GHz and DDR3 frequency at 1600 MT/s

- Single read scenarios represent endpoint access latency.

- Read latency numbers quoted with ARM default cache performance settings.

- DDR3 accesses to open pages.

### 3.2 Memory Write Performance

The C66x CorePac has improved write merging and optimized burst sizes that reduce the stalls to external memory.

The L1D memory controller merges writes, not only to L2 SRAM, but to any address that is allowed to be cached (MAR.PC==1).

For details about memory write performance, see the *TMS320C66x DSP Cache User's Guide* (SPRUGY8).

#### 4 DDR3 Throughput

#### Applies to:

All KeyStone II Devices

The DDR3 module in the C66x DSP is accessible across all cores and other system masters. The DDR3 controller interfaces with most standard DDR3 SDRAM devices. There are two clock domains in the controller. The Command FIFO, Read FIFO and Write FIFO are all on the DSP/2 clock domain for DDR3A and are all on DSP/3 clock domain for DDR3B. The state machine and interface to the DDR PHY are all driven by the DDR3 memory clock. The DDR3 controller is interfaced to the MSMC controller and any access made via any of the EDMAs are handled by MSMC that serves as the common management path.

DDR3 throughput can be measured using a bidirectional EDMA transfer setup with DDR3 and other memory endpoints. The theoretical DDR3 throughput is (64bits)/(8bit/byte)×(800M)×2=12800MB/s, it is impacted by factors such as read-write turnaround and page switch overheads'. For DDR3 related throughput, see the Section 5.2.

EDMA Throughput www.ti.com

### 5 EDMA Throughput

The enhanced direct memory access (EDMA3) controller's primary purpose is to service data transfers between two memory-mapped slave endpoints on the device. An EDMA3 controller consists of the channel controller (EDMA3CC) which serves as the user interface allowing software to program the data transfer and for each channel controller, a number of transfer controllers (TCs) that are responsible for actual data movement. A single transfer controller may not always be able to utilize the desired slave memory bandwidth. For example: With Main PLL running at 1.2GHz a, 128-bit wide TC running at CPU/3 is limited to 128/8 \* 1200/3 = 6400 MB/s. 80% of DDR3 bandwidth with 64-bit DDR running at 1600MT/s is 0.8 \* (64/8)\*1600 = 10240 MB/s. Thus, more than one TC will need to be employed to hit 80% bandwidth.

The EDMA3 throughput section is divided into three subsections:

Section 5.1 provides the baseline reference for EDMA TC throughput. These tests use individual TCs with large, single-dimensional transfers (128KB).

Section 5.2 describes the multi-TC complex throughput tests. The intent is to employ multiple EDMA3 TCs to maximize the end-to-end bandwidth for a given set of slave memory endpoints. These tests utilize large, single-dimensional transfers (32KB) designed to optimize pipelined bus utilization and minimize overhead associated with setting up transfers.

Section 5.3 describes the impact of various parameters like data burst size (DBS), FIFO size and transfer index on the EDMATC throughput. A single transfer controller is used to clearly demonstrate this impact.

All EDMA3 throughput tests were run on a 66AK2H EVM with the Main PLL running at 1.2GHz and 64-bit DDR3 configured at 1600 MT/s.

Note that TC0 through TC13 in this document correlate to the Data Manual nomenclature in the following way:

| TC0 = EDMA0 TC0 | TC7 = EDMA2 TC1  |

|-----------------|------------------|

| TC1 = EDMA0 TC1 | TC8 = EDMA2 TC2  |

| TC2 = EDMA1 TC0 | TC9 = EDMA2 TC3  |

| TC3 = EDMA1 TC1 | TC10 = EDMA3 TC0 |

| TC4 = EDMA1 TC2 | TC11 = EDMA3 TC1 |

| TC5 = EDMA1 TC3 | TC12 = EDMA4 TC0 |

| TC6 = EDMA2 TC0 | TC13 = EDMA4 TC1 |

#### 5.1 Baseline EDMA TC Performance

This section compares the maximum throughput achievable for TCs on various channel controllers found on Keystone II devices. EDMA was programmed in AB-Sync mode with ACNT=1024, BCNT=128, CCNT=1.

NOTE: Some small variations in the results shown may be attributed to measurement accuracy.

www.ti.com EDMA Throughput

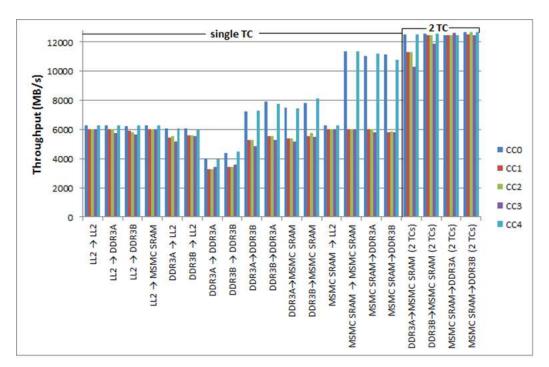

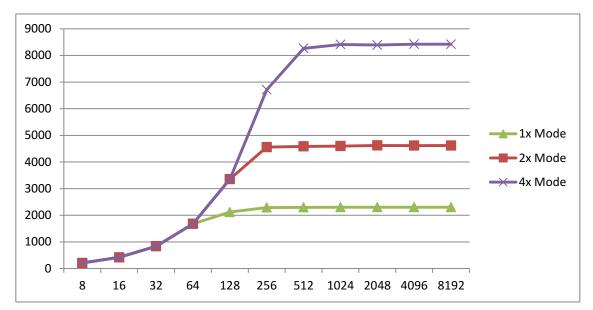

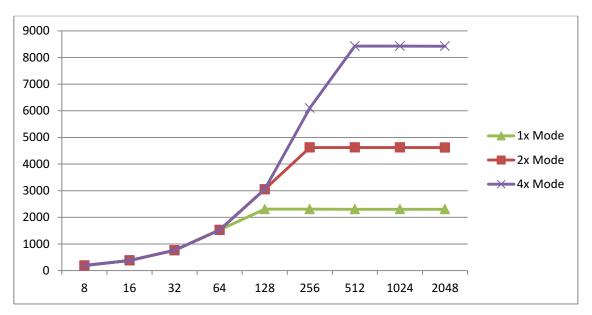

Figure 1. Throughput Comparison Between KeyStone-II TCs

For data transfer between MSMC SRAM and DDR3A/B, TCs on EDMACC0 and EDMACC4 should be used since they achieve much better throughput than other TCs. Due to the high latency of reading from DDR3 memory, a single EDMA TC is unable to issue enough read commands to keep the DDR3 EMIF command pipeline fully utilized which reduces the effective throughput when reading from DDR3A or DDR3B. EDMA is able to keep the command pipeline better utilized during writes thus resulting in higher performance compared to reads. As shown in Figure 1, two EDMA TCs are required to get closer to full DDR3 bandwidth (12800 MB/s for 64-bit, DDR3-1600) on reads or writes. Note that all DDR3 results were measured with a single rank DRAM configuration. In the case of dual rank, the DDR3 controller introduces 6 DDR3 clock cycles (corresponding to T\_CSTA = 5 in the SDRAM Timing 4 Register) between accesses to different ranks. This reduces DDR3 bus efficiency by approximately 20% compared to single rank.

CC0 and CC4 TCs have a wider bus width (256-bit) compared to other TCs (128-bit) and are inherently higher performing than CC1, CC2, and CC3. CC1, CC2 and CC3 TCs have comparable performance to one another.

### 5.2 EDMA3 Complex Throughput

Various complex throughput tests were performed for measuring the EDMA throughput under different conditions. The following tests calculate the EDMA throughput without any background traffic in the CorePac.

The test process includes the following steps:

- 1. Get the transfer time for a payload of 32KB/channel (includes overhead).

- 2. Get the transfer time for 0 bytes this is called a dummy transfer and closely approximates the overhead.

- 3. Subtract 2 from 1 to get the transfer time with overhead removed t3.

- 4. Throughput = [(32KB \* number of channels)/t3] \* 1.2 GHz

The basis of these tests is to set up and trigger bidirectional (read and write) data transfers in parallel for different combinations of TCs of the EDMA. The channel controller is programmed such that each TC performs one read and one write transfer between the TC endpoints bidirectionally on two different logical channels. Once TCs are triggered, wait (poll) for the completion of all transfers and capture the throughput values.

EDMA Throughput www.ti.com

The EDMA configuration uses A-synchronized transfers across all tests and TC combinations with ACNT = 32KB and BCNT = CCNT = 1 per logical channel.

Note that each of the TCs have bidirectional transfers —from endpoint A to endpoint B and the other from endpoint B to endpoint A on two different logical channels. For example, for the TC0 and TC1 testcase, there are a total of four transfers on four different logical channels.

The TeraNet allows for concurrent transfers between non-conflicting master/slave pairs and can support a very high total data rate across any endpoint. If transfers line up such that the source or destination memory is the same, then collisions occur and certain transactions will be blocked.

The throughput is limited by the lowest of the bus bandwidth, source throughput, and destination throughput. Each scenario is accompanied by a figure that highlights the primary bandwidth limiting factor for that scenario. Bidirectional arrows in the figures represent the bidirectional transfers mentioned above.

Note that the EDMA TC combinations used in the results are chosen such that they use independent paths between the TeraNets in order to create concurrent, non-conflicting transfers between source and destination slave memories. If TCs that map to the same inter-TeraNet bridge are used, the bridge will likely be the bandwidth limiting factor. The TC-to-bridge mapping between TeraNets 3A and 3C is shown in Table 5.

Note that TC0 through TC13 in this document correlate to the Data Manual nomenclature in the following way:

EDMA Throughput www.ti.com

## Table 5. TC-to-Bridge Mapping Between TeraNets 3A and 3C (1)

| EDMA Masters           | Br_2<br>(to<br>TeraNet<br>3A) | Br_3<br>(to<br>TeraNet<br>3A) | Br_5<br>(to<br>TeraNe<br>t 3C) | Br_6<br>(to<br>TeraNet<br>3C) | Br_7<br>(to<br>TeraNet<br>3C) | Br_8<br>(to<br>TeraNet<br>3C) | Br_9<br>(to<br>TeraNe<br>t 3C) | Br_10<br>(to<br>TeraNet<br>3C) | Br_<br>SMS0<br>(to<br>MSMC<br>SRAM) | Br_<br>SMS1<br>(to<br>MSMC<br>SRAM) | Br_<br>SMS2<br>(to<br>MSMC<br>SRAM) | Br_<br>SES0<br>(to<br>DDR3) | Br_<br>SES1<br>(to<br>DDR3) | Br_<br>SES2<br>(to<br>DDR3) |

|------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------------|--------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| EDMA TCs on TeraNet 3C |                               |                               |                                |                               |                               |                               |                                |                                |                                     |                                     |                                     |                             |                             |                             |

| EDMA_0_TC0_R           | Х                             | -                             | -                              | -                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_0_TC0_W           | Х                             | -                             | -                              | -                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_0_TC1_R           | -                             | Х                             | -                              | -                             | -                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_0_TC1_W           | -                             | Х                             | -                              | -                             | -                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_4_TC0_R           | Х                             | -                             | -                              | -                             | -                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_4_TC0_W           | Х                             | -                             | -                              | -                             | -                             | -                             | -                              | -                              | 1                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_4_TC1_R           | -                             | Х                             | -                              | -                             | -                             | -                             | -                              | -                              | 1                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_4_TC1_W           | -                             | Х                             | -                              | -                             | -                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

|                        |                               |                               |                                |                               | EDMA                          | TCs on Te                     | raNet 3A                       |                                |                                     |                                     |                                     |                             |                             |                             |

| EDMA_1_TC0_R           | -                             | -                             | X                              | -                             | -                             | -                             | -                              | -                              | Χ                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_1_TC0_W           | -                             | -                             | Х                              | -                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_1_TC1_R           | -                             | -                             | -                              | Х                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_1_TC1_W           | -                             | -                             | -                              | Х                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_1_TC2_R           | -                             | -                             | -                              | -                             | Х                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_1_TC2_W           | -                             | -                             | -                              | -                             | Х                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_1_TC3_R           | -                             | -                             | -                              | -                             | -                             | Х                             | -                              | -                              | 1                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_1_TC3_W           | -                             | -                             | -                              | -                             | -                             | Х                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_2_TC0_R           | -                             | -                             | -                              | -                             | -                             | -                             | Х                              | -                              | -                                   | -                                   | Х                                   | -                           | -                           | Χ                           |

| EDMA_2_TC0_W           | -                             | -                             | -                              | -                             | -                             | -                             | Х                              | -                              | -                                   | -                                   | Х                                   | -                           | -                           | Х                           |

| EDMA_2_TC1_R           | -                             | -                             | -                              | -                             | -                             | -                             | -                              | Х                              | -                                   | -                                   | Х                                   | -                           | -                           | Х                           |

| EDMA_2_TC1_W           | -                             | -                             | -                              | -                             | -                             | -                             | -                              | Х                              | -                                   | -                                   | Х                                   | -                           | -                           | Х                           |

| EDMA_2_TC2_R           | -                             | -                             | Х                              | -                             | -                             | -                             | -                              | -                              | Χ                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_2_TC2_W           | -                             | -                             | Х                              | -                             | -                             | -                             | -                              | -                              | Χ                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_2_TC3_R           | -                             | -                             | -                              | Х                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_2_TC3_W           | -                             | -                             | -                              | Х                             | -                             | -                             | -                              | -                              | Х                                   | -                                   | -                                   | Х                           | -                           | -                           |

| EDMA_3_TC0_R           | -                             | -                             | -                              | -                             | Х                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_3_TC0_W           | -                             | -                             | -                              | -                             | Х                             | -                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_3_TC1_R           | -                             | -                             | -                              | -                             | -                             | Х                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

| EDMA_3_TC1_W           | -                             | -                             | -                              | -                             | -                             | Х                             | -                              | -                              | -                                   | Х                                   | -                                   | -                           | Х                           | -                           |

Legend: X = There is no connection between this TC and the bridge.

– = There is no connection between this TC and the bridge.

EDMA Throughput www.ti.com

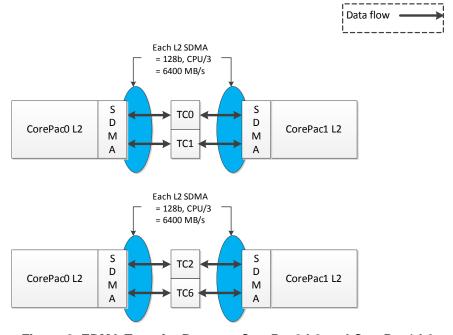

#### 5.2.1 Scenario 1: EDMA Transfer Between CorePac0 L2 and CorePac1 L2

In this scenario, the endpoints used are CorePac0 L2 SRAM and CorePac1 L2 SRAM memory. There is contention among TCs as the same endpoint is used by both TCs for each of the bidirectional transfers. The TCs have to use the same SDMA/IDMA port of the same CorePac and the second transaction will have to wait until the first is complete.

So only one TC transfer is done at a time and the theoretical throughput is equivalent to (128 bits)/(8 bit/byte)x(1200M/3)=6400 MB/s.

The test case descriptions are as follows:

- Every TC sets up bidirectional data transfer between the same CorePac0 L2 and CorePac1 L2.

- TC0 and TC1 test case: Trigger TC0 and TC1 in parallel. After the completion of the TC0 and TC1 transfers in both directions, the steady state throughput is calculated.

- TC2 and TC6 test case: Trigger TC2 first and after a delta lag TC6 is triggered. After the completion of TC2 and TC6 transfers in both directions, the steady state throughput is calculated.

Table 6 shows the measured aggregate throughput of the TCs for this scenario.

Table 6. EDMA Throughput Between CorePac0 L2 and CorePac1 L2 Endpoints

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 |

|--------------------------------------------------------|-------------|-------------|

| Wait for completion of                                 | Both        | Both        |

| Theoretical Max throughput between TC endpoints (MBPS) | 6400        | 6400        |

| Aggregate throughput of TCs fired (MBPS)               | 6201        | 5935        |

| Total transfer efficiency                              | 97%         | 93%         |

Figure 2. EDMA Transfer Between CorePac0 L2 and CorePac1 L2

#### 5.2.2 Scenario 2: EDMA Transfer Between Different CorePac L2 and MSMC SRAM

In this scenario, each TC uses a different CorePac source address and there is no contention between TCs at the inter-TeraNet bridges. There may be some contention at the MSMC but it's bandwidth exceeds the sum total of TC bandwidths and thus contention there may be minimal For example TC0 reads from CorePac0 L2, whereas TC1 reads from CorePac1 L2. So the total throughput for any two TCs would be  $2 \times [(128 \text{ bits})/(8 \text{ bit/byte}) \times (1200 \text{M/s})] = 12800 \text{ MB/s}$  and for any four TCs this would be  $4 \times [(128 \text{ bits})/(8 \text{ bit/byte})]$  $bit/byte) \times (1200M/3)] = 25600 MB/s.$

www.ti.com EDMA Throughput

The testcase setup details are as follows:

TC0 and TC1: TC0 has bidirectional data transferred between CorePac0 L2 and MSMC. TC1 has bidirectional data transferred between CorePac1 L2 and MSMC.

- TC2 and TC6: TC2 has bidirectional data transferred between CorePac0 L2 and MSMC. TC6 has bidirectional data transferred between CorePac1 L2 and MSMC.

- TC2, TC6, TC10, and TC12: Each TC uses a different CorePac to transfer bidirectional data between MSMC and CorePac For example, TC2 uses CorePac0, TC6 uses CorePac1, TC10 uses CorePac2, and TC12 uses CorePac3.

Table 7 shows the measured aggregate throughput of the TCs for this scenario.

Table 7. EDMA Transfer Between Different CorePac L2 and MSMC SRAM

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC2, TC6, TC10, and<br>TC12 |

|--------------------------------------------------------|-------------|-------------|-----------------------------|

| Wait for completion of                                 | Both        | Both        | All                         |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800       | 25600                       |

| Aggregate throughput of TCs fired (MBPS)               | 11843       | 11843       | 24272                       |

| Total transfer efficiency                              | 93%         | 93%         | 95%                         |

EDMA Throughput www.ti.com

Figure 3 shows the measured aggregate throughput of the TCs for this scenario.

Figure 3. EDMA Transfer Between CorePac0 L2 and MSMC SRAM

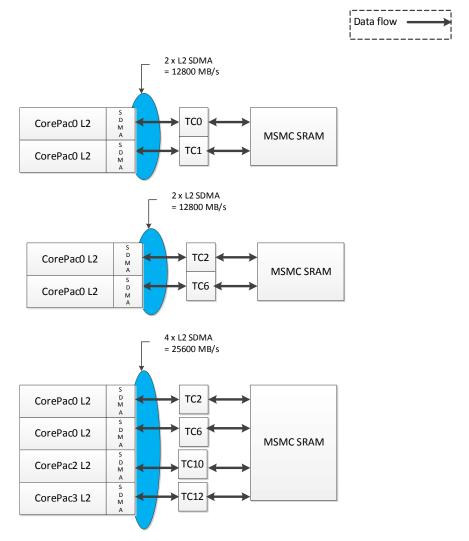

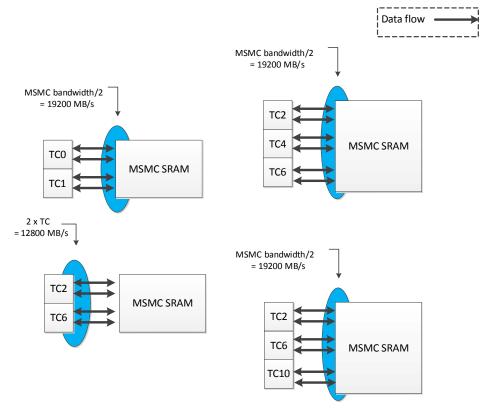

#### 5.2.3 Scenario 3: EDMA Transfer From MSMC SRAM to MSMC SRAM

In this scenario there is contention between TCs because the source/destination are the same for different TCs, so there is only one transfer happening at a time. Even though the theoretical throughput for MSMC is  $(256 \text{ bits})/(8 \text{ bit/byte}) \times (1200 \text{M}) = 38400 \text{MB/s}$ , it cannot do both reads and writes at the same time. It has to wait for the previous read from MSMC to complete and then do the write operation to the MSMC. Therefore, the throughput will be effectively halved and is 38400/2 = 19200 MB/s.

Note that for TC2 and TC6 use case, both TCs use two independent paths on TeraNet 3A which is a CPU/3 128 bit interface. The theoretical throughput is  $(128bits)/(8bit/byte) \times 2 \times (1200M)/3 = 12800$  MB/s.

www.ti.com EDMA Throughput

shows the measured aggregate throughput of the TCs for this scenario.

Table 8 shows the measured aggregate throughput of the TCs for this scenario.

Table 8. EDMA Throughput Between MSMC SRAM and MSMC SRAM

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC2, TC4, and TC6 | TC2, TC6, and TC10 |

|--------------------------------------------------------|-------------|-------------|-------------------|--------------------|

| Wait for completion of                                 | Both        | Both        | All               | All                |

| Theoretical Max throughput between TC endpoints (MBPS) | 19200       | 12800       | 19200             | 19200              |

| Aggregate throughput of TCs fired (MBPS)               | 17329       | 11839       | 17331             | 16186              |

| Total Transfer Efficiency                              | 90%         | 92%         | 90%               | 84%                |

Figure 4. EDMA Throughput Between MSMC SRAM and MSMC SRAM

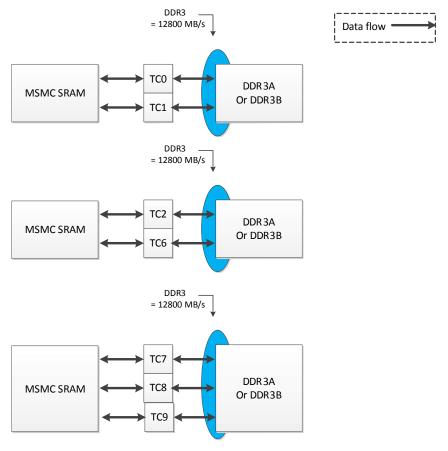

#### 5.2.4 Scenario 4: EDMA Transfer From MSMC SRAM to DDR3

There is no contention between TCs at the inter-TeraNet bridges, but there may be some contention at the DDR3 memory with multiple TCs accessing the same memory endpoint. The throughput is limited by the maximum DDR3 bandwidth, which is (64 bits)/(8 bit/byte)×(800M)×2=12800MB/s.

The testcase setup details are as follows:

- TC0 and TC1: TC0 and TC1 have bidirectional data transferred between MSMC and DDR3A/DDR3B.

- TC2 and TC6: TC2 and TC6 have bidirectional data transferred between MSMC and DDR3A/DDR3B.

- TC7, TC8 and TC9: TC7, TC8 and TC9 have bidirectional data transferred MSMC RAM and DDR3A/3B.

Table 9 and Table 10 show the measured aggregate throughput of the TCs with DDR3A and DDR3B, respectively, for this scenario. Ignore Table 10 if your device does not support DDR3B.

EDMA Throughput www.ti.com

## Table 9. EDMA Throughput Between MSMC SRAM and DDR3A

| Transaction on TCs                                     | TC0 and TC1 | TC2 andTC6 | TC7, TC8 and TC9 |

|--------------------------------------------------------|-------------|------------|------------------|

| Wait for completion of                                 | Both        | Both       | ALL              |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800      | 12800            |

| Aggregate throughput of TCs fired (MBPS)               | 10638       | 9925       | 12137            |

| Total Transfer Efficiency                              | 83%         | 78%        | 95%              |

Table 10. EDMA Throughput Between MSMC SRAM and DDR3B

| Transaction on TCs                                     | TC0 and TC1 | TC2 andTC6 | TC7, TC8 and TC9 |

|--------------------------------------------------------|-------------|------------|------------------|

| Wait for completion of                                 | Both        | Both       | ALL              |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800      | 12800            |

| Aggregate throughput of TCs fired (MBPS)               | 10730       | 10291      | 12192            |

| Total Transfer Efficiency                              | 84%         | 80%        | 95%              |

Figure 5. EDMA Transfer Between MSMC SRAM and DDR3A or DDR3B

www.ti.com EDMA Throughput

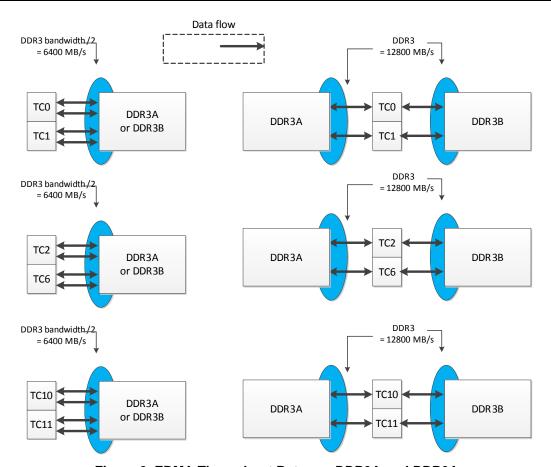

#### 5.2.5 Scenario 5: EDMA Transfer From DDR3 to DDR3

For bidirectional transfers between the same DDR3 endpoint: There is contention between TCs, but because the DDR3 controller cannot do a read from DDR3 and a write to DDR3 in parallel, the EDMA needs to wait until the previous operation is completed. The theoretical max DDR3 throughput of 12800MB/s will be halved and will be equal to 6400 MB/.

For bidirectional transfers between different DDR3 endpoints (DDR3A and DDR3B): Since the TCs can issue a read and write to different DDR3 endpoints in parallel, the theoretical max is not halved and still equals 12800 MB/s.

In both cases, the measured throughput is even lower due to the effects of read-write turnaround and page switch overheads.

The testcase setup details are as follows:

- Every TC sets up bidirectional data transfer between DDR3A and DDR3A SDRAM.

- Every TC sets up bidirectional data transfer between DDR3B and DDR3B SRAM.

- Every TC sets up bidirectional data transfer between DDR3A and DDR3B SDRAM.

Table 11 and Table 12 show the measured aggregate throughput of the TCs for this scenario. Ignore Table 12 and Table 13 if your device does not support DDR3B.

Table 11. EDMA Throughput Between DDR3A and DDR3A

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC10 and TC11 |

|--------------------------------------------------------|-------------|-------------|---------------|

| Wait for completion of                                 | Both        | Both        | Both          |

| Theoretical Max throughput between TC endpoints (MBPS) | 6400        | 6400        | 6400          |

| Aggregate throughput of TCs fired (MBPS)               | 4341        | 4108        | 3954          |

| Total Transfer Efficiency                              | 84%         | 80%         | 95%           |

Table 12. EDMA Throughput Between DDR3B and DDR3B

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC10 and TC11 |

|--------------------------------------------------------|-------------|-------------|---------------|

| Wait for completion of                                 | Both        | Both        | Both          |

| Theoretical Max throughput between TC endpoints (MBPS) | 6400        | 6400        | 6400          |

| Aggregate throughput of TCs fired (MBPS)               | 4078        | 3629        | 3330          |

| Total Transfer Efficiency                              | 64%         | 57%         | 52%           |

Table 13. EDMA Throughput Between DDR3A and DDR3B

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC10 and TC11 |

|--------------------------------------------------------|-------------|-------------|---------------|

| Wait for completion of                                 | Both        | Both        | Both          |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800       | 12800         |

| Aggregate throughput of TCs fired (MBPS)               | 10334       | 9806        | 9240          |

| Total Transfer Efficiency                              | 81%         | 77%         | 72%           |

EDMA Throughput www.ti.com

Figure 6. EDMA Throughput Between DDR3A and DDR3A

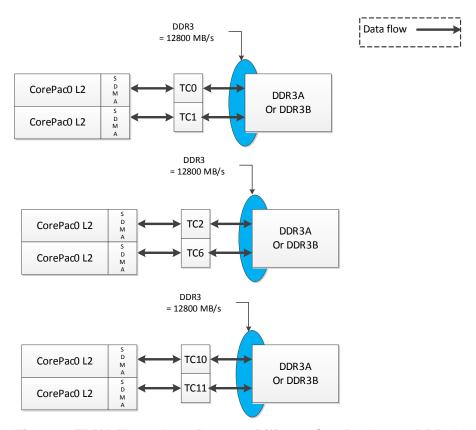

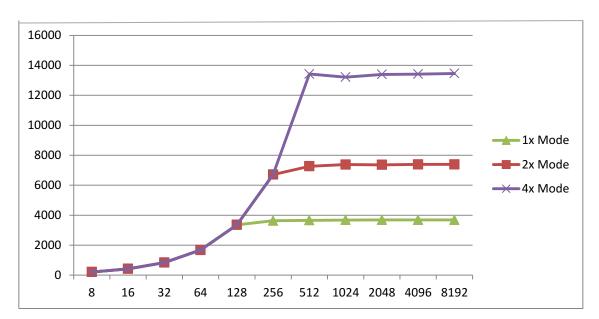

#### 5.2.6 Scenario 6: EDMA Transfer From Different CorePac L2 to DDR3

In this scenario, each TC uses a different CorePac source address and there is no contention between TCs at the inter-TeraNet bridges. However, there is contention among multiple TCs at the DDR3 memory. The throughput is bounded by the DDR3A/DDR3B maximum throughput, which is 12800MB/s.

The testcase setup details are as follows:

- TC0 and TC1: TC0 has bidirectional data transferred between CorePac0 L2 and DDR3A/3B. TC1 has bidirectional data transferred between CorePac1 L2 and DDR3A/3B.

- TC2 and TC6: TC2 has bidirectional data transferred between CorePac0 L2 and DDR3A/3B. TC6 has bidirectional data transferred between CorePac1 L2 and DDR3A/3B.

- TC10 and TC11: TC10 has bidirectional data transferred between CorePac0 L2 and DDR3A/3B. TC11

has bidirectional data transferred between CorePac1 L2 and DDR3A/3B.

Table 14 and Table 15 show the measured aggregate throughput of the TCs for this scenario. Ignore Table 15 if your device does not support DDR3B.

Table 14. EDMA Throughput Between Different CorePac L2s to DDR3A

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC10 and TC11 |

|--------------------------------------------------------|-------------|-------------|---------------|

| Wait for completion of                                 | Both        | Both        | Both          |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800       | 12800         |

| Aggregate throughput of TCs fired (MBPS)               | 10528       | 10135       | 9849          |

| Total Transfer Efficiency                              | 82%         | 79%         | 77%           |

www.ti.com EDMA Throughput

#### Table 15. EDMA Throughput Between Different CorePac L2s to DDR3B

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC10 and TC11 |

|--------------------------------------------------------|-------------|-------------|---------------|

| Wait for completion of                                 | Both        | Both        | Both          |

| Theoretical Max throughput between TC endpoints (MBPS) | 12800       | 12800       | 12800         |

| Aggregate throughput of TCs fired (MBPS)               | 10518       | 10520       | 10311         |

| Total Transfer Efficiency                              | 82%         | 82%         | 81%           |

Figure 7. EDMA Throughput Between Different CorePac L2s to DDR3A

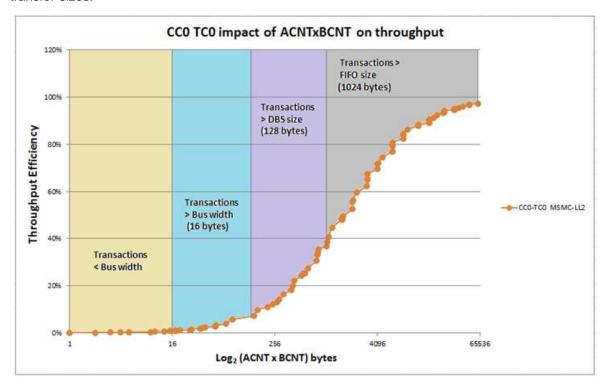

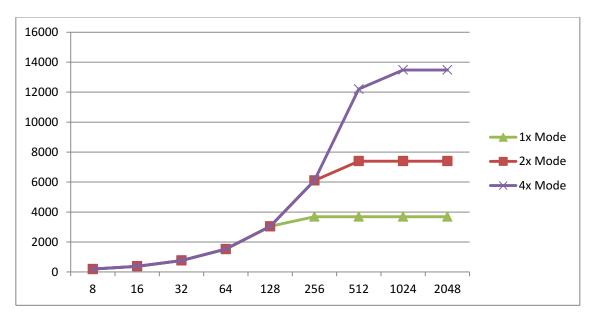

#### 5.3 Impact of Various Parameters on EDMA3 Throughput

This section discusses the impact of various parameters on EDMA3 throughput. EDMA3 is used for data movement in various applications. Some applications might implement single-dimensional (contiguous) bulk transfers. Others might execute multi-dimensional, non-linear transfers such as matrix transposition. The transfer geometry can greatly impact the efficiency of EDMA transfers. So can the choice of EDMA CC/TCs and source/destination memory endpoints. Many of these transfers perform memory paging between internal memory and external memory like DDR3 in order to make it available to the CPU before a real time processing deadline expires. Thus, it is important to understand how the various parameters impact EDMA transfer efficiency.

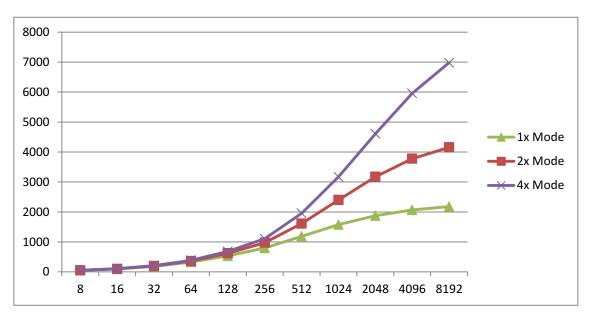

#### 5.3.1 Impact of Total Transfer Size

To make full utilization of the available EDMA bandwidth, it is important to fully utilize the bus width and burst sizes. In order to optimize the EDMA bandwidth, the ACNT x BCNT bytes (for linear) and ACNT bytes (for non-linear):

- Must be larger than the TC bus width. The bus width is 32 bytes for EDMACC0 and EDMACC4 TCs and 16 bytes for other TCs.

- Must be larger than the default burst size (DBS) of the EDMA TC. DBS is 64 bytes for EDMACC3 TCs and 128 bytes for all others.

EDMA Throughput www.ti.com

Must be larger than the TC FIFO size. This is 1024 bytes for all TCs.

Figure 8 shows the impact on throughout for a linear transfer, as it crosses the various stages outlined above. EDMACC0 TC0 performing a data transfer from MSMC SRAM to CorePac0 L2 is chosen to demonstrate. A log scale is chosen for the X-axis to effectively visualize throughput over a large range of transfer sizes.

Figure 8. Impact of Transfer Size on Throughput

www.ti.com EDMA Throughput

### 5.3.2 Impact of Index

Index significantly impacts EDMA throughput. In Figure 9, EDMACC0 TC0 performing data transfers from MSMC SRAM to CorePac0 L2 is used to demonstrate the impact.

Figure 9. Impact of Index on Throughput

A linear transfer (Index=ACNT) performs best because EDMA optimizes the transfer by fully utilizing TC bandwidth. The starting address for MSMC SRAM programmed in the EDMA PaRAM is 64-byte aligned. Incrementing the index in (ACNT + power-of-2) also increases the percentage of SRAM sub-banks that are fully utilized by the EDMA burst, thus increasing the bandwidth efficiency (a sub-bank in MSMC SRAM lies at every 32-byte boundary and is 32-bytes wide). The sub-bank utilization is the worst for an odd index, making it the worst performing condition. For ACNT = 16 bytes or less, the sub-bank utilization is approximately the same for all conditions, making the plots converge. The pipelined bus architecture utilizes the bus infrastructure more efficiently as ACNT increases. This minimizes the significance of sub-bank inefficiency and increases the overall throughput efficiency until all plots eventually converge. For details on SRAM bank architecture, see the *Multicore Shared Memory Controller (MSMC) User's Guide* (SPRUHJ6).

### 5.3.3 Impact of Address Alignment

Address alignment may slightly impact the performance. The default burst size of EDMA3 is 64bytes or 128 bytes. The EDMA transfer controller always generates read or write commands that are less than or equal to DBS size. If the source or destination addresses are not aligned on a DBS-sized boundary, EDMA will generate an extra burst to handle the unaligned head and tail data. This overhead may be ignored for large transfers (typically larger than TC FIFO size).

#### 5.4 General Recommendations

Observations from previous sections lead to some general guidelines. In order to maximize EDMA bandwidth efficiency:

- DO:

- Use linear transfers

- Use power-of-2 sized block sizes

- Use block sizes larger than TC FIFO size

- Use block sizes larger than TC DBS size

- Use block sizes larger than TC bus width size

PCIe www.ti.com

- Use block sizes larger than TC bus width size

- Use EDMACC0 and EDMACC4 TCs for transfers involving MSMC SRAM, DDR3A or DDR3B.

- AVOID:

- Using non-linear transfers

- Using odd-sized source or destination indices

- Using block sizes smaller than TC bus width/DBS/FIFO size

#### 6 PCle

This section discusses the throughput performance of the Keystone II PCIe peripheral. The Keystone II PCIe peripheral is connected to the TeraNet through a 128-bit bus. The peripheral operates at a frequency of DSP/3; however, the I/O clock frequency for this module is derived from the PCIe SerDes PLL. The PCIe peripheral supports the PCIe v2 standard, which has a maximum theoretical throughput of 5 gigabits per second per link. Keystone II devices support two PCIe links, each capable of transferring data five gigabits per second. Together, these two PCIe links have a maximum theoretical throughput of s per second.

It is important to note that the per second data rate includes the overhead due to the physical layer, the data link layer (DLL), and the transaction layer packet (TLP). Due to overhead, the raw data that is able to be transferred is less s per second. The remainder of this section discusses:

- Main Factors Affecting PCIe Throughput Performance

- How to Achieve Maximum Throughput with the PCIe Peripheral

- Measured Throughput Performance

#### 6.1 Main Factors Affecting PCIe Throughput Performance

This section discusses the main factors that affect the performance of the PCIe peripheral. To achieve the maximum throughput possible using the Keystone II PCIe peripheral, the following factors must be kept in mind:

- Overhead Considerations

- Packet Size Considerations

- Packet Size Considerations

#### 6.1.1 Overhead Considerations

The overhead discussed in this section is related to the PCIe protocol itself, and is not due to the Keystone II PCIe implementation. For each PCIe data transfer TLP packets have 20-28 bytes of overhead due to encapsulation. There is also overhead for flow control and acknowledge DLLP packets, which adds 8 bytes of overhead per packet. All data sent over the bus, is encoded using the 8b/10b encoding scheme, which adds an extra 20% overhead. The exact number of bytes of overhead that are required per packet is dependent on the size of the data payload, and the frequency of the DLLP packets.

#### 6.1.2 Packet Size Considerations

For each packet transferred over the PCIe protocol, the overhead associated with transferring the data should be taken into account. For more information on PCIe overhead, see Section 6.1.1. Since the overhead is added on a per packet basis, the amount of overhead can be reduced by making the data payload as large as possible for all packets transferred.

For outbound transfers, the Keystone II PCIe peripheral is able to transfer packets of up to 128 bytes, excluding overhead. Therefore, transferring packets with 128 bytes of data payload will achieve the best throughput. For inbound data transfers, the PCIe peripheral is capable of handling payload sizes larger than 128 bytes, which can further reduce overhead and increase throughput performance. Impact of packet size on performance is discussed in the Measured Throughput section.

**PCIe** www.ti.com

NOTE: For outbound transfers: The packet size is different from the data transfer size. For outbound transfer, the maximum payload size of a packet is 128 bytes. However, data transfers over 128 bytes are supported by the PCIe peripheral. Data transfers over 128 bytes are broken into multiple packets.

NOTE: For inbound transfers: PCle can take advantage of 256 byte inbound size as long as the external device also has 256 bytes (or more) of outbound payload size. This is not possible if the external device is a KeyStone device, because the maximum outbound payload size is only 128 bytes. That limits the maximum inbound packet size to 128B.

#### 6.1.3 **EDMA Considerations**

When using EDMA to transmit data to the Keystone II PCIe, or when using EDMA to receive data from the Keystone II PCIe, the transfer controller (TC) that is used should be taken into consideration. Not all transfer controllers use the same data burst size (DBS), and the size of the data burst can have an impact on the performance of the PCIe peripheral. Since the PCIe peripheral supports data payload sizes of up to 128 bytes, if available, a EDMA TC that also supports 128-byte data burst sizes should be chosen. By matching the PCIe data payload size to the EDMA TC data burst size, the PCIe peripheral can send or receive the maximum possible payload size, thereby reducing overhead as much as possible.

When using a 128-byte data payload, the overhead will be introduced every 128 bytes of payload. If using an EDMA TC with a data burst size below 128 bytes, then more overhead will be introduced. For example, if an EDMA TC with a 64-byte data burst size is chosen, then the PCIe will use 64-byte payloads, and packet overhead will be introduced for every 64 bytes of payload data. When transferring 128 bytes, using two 64-byte data payloads will introduce twice as much overhead as a one 128-byte data payload. For more information on PCIe overhead, see Section 6.1.1. Impact of EDMA TC selection on performance is discussed in Section 6.3.

#### 6.2 How to Achieve Maximum Throughput With the PCle Peripheral

To maximize the throughput of the Keystone II PCIe peripheral, the peripheral should be programmed while keeping in mind the "Main Factors Affecting PCIe Throughput Performance". To achieve maximum performance for the Keystone II PCIe peripheral, the two main considerations should be to reduce packet overhead (maximize data payload) and to reduce the amount of time related to EDMA transactions.

To reduce overhead, the data payload should be as large as possible. The larger the data payload size, the less packet overhead is introduced, and the more the performance is increased. For outbound transactions, the maximum data payload size is 128 bytes, so payloads as close to 128 bytes as possible are desired. Furthermore, to ensure that the EDMA transfer controller provides 128-byte data payloads to the PCIe peripheral, an EDMA transfer controller that supports 128-byte data burst size should be used.

For inbound transactions, the PCle v2 specification permits data payloads up to 4096 bytes; however, in Keystone II devices, the maximum PCIe data payload size is limited to 256 bytes for inbound transactions (compared to 128 bytes for outbound). For details, see the KeyStone Architecture Peripheral Component Interconnect Express (PCIe) User's Guide (SPRUGS6). As explained in the Note above, inbound packet size is limited to 128 bytes if the external device is a KeyStone device. The closer to maximum payload size, the better the throughput performance. Another way to reduce overhead is to reduce packet headers as much as possible. One example may be to remove optional headers, such as the TLP ECRC, if this field is not required by the application. ECRC generation can be disabled by clearing ECRC\_GEN\_EN bit field in PCIE\_ACCR register.

Lastly, overhead can be reduced by reducing DLLP packets. If not required by the application, DLLP flow control packets can be disabled by programming the FC\_DISABLE field in the LANE\_SKEW register. IF DLLP acknowledge packets are not required by the application, then the transmission of these packets can be disabled by programming the ACK\_DISABLE field in the LANE\_SKEW register. If acknowledge packets are required by the application, the frequency of the acknowledge packets can be configured to the lowest rate required by the application by programming the ACK FREQ register.

PCIe www.ti.com

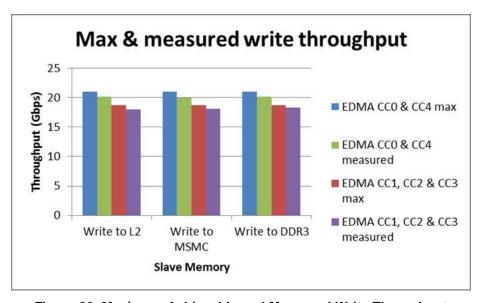

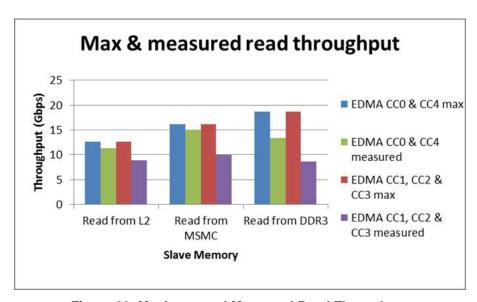

#### 6.3 Measured Throughput Performance

The measurements mentioned in this section were collected on a 66AK2E05 device, which has two PCIe controllers (PCIe0 and PCIe1). PCIe0 data applies to all Keystone-II devices. PCIe1 data applies to 66AK2Ex and AM5K2Ex devices only.

Performance data for the PCIe peripheral is captured in and . For all performance tests, both links of the Keystone II PCIe module were connected directly with another Keystone II PCIe module. One module was configured as the RC and the other device was configured as the EP. For the performance tests, all transactions were outbound transfers initiated by the RC. Some results include bidirectional transfers (on both Keystone-II devices). The tests were measured with MSMC SRAM and DDR3A memory endpoints, and with 2048, 4096, 8192, 16384 and 32768-byte data payload transfer sizes. The published throughput numbers are the result of trending the measured throughput over the various payload transfer sizes.

The performance tests were conducted using TCs from all EDMAs spanning 64-byte and 128-byte data burst sizes. All packets with data payload used PHY, DLLP, and TLP headers. Each TLP packet contained 20-byte overhead of header and footer. Thus, the theoretical data throughput for 2 lanes configured at 5Gbps after removing the overhead and 8b/10b encoding is (packet size in bytes)/(packet size in bytes + 20) x (8/10) x  $(2 \times 5Gbps) = 6.10$  Gbps for 64-byte packets and 6.92 Gbps for 128-byte packets. This is plotted on the graphs. An 8-byte DLLP packet was sent after each packet containing a data payload. Performance data with all overhead excluded is shown in Section 6.3.1 and Section 6.3.2.

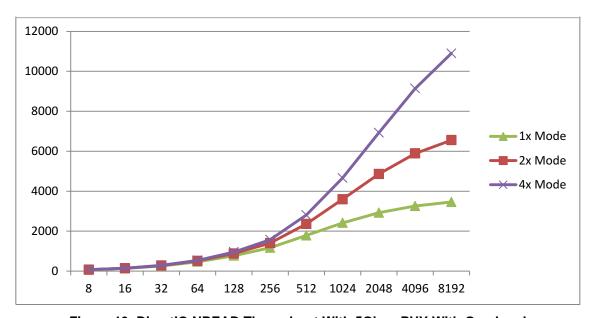

### 6.3.1 PCIe Read Throughput

The throughput shown in this section is the data payload only, and does not include any overhead due to PHY, DLLP, or TLP headers, and does not include overhead due to 8b/10b encoding.

For this test, read transactions were executed between two Keystone II PCIe devices. Device1 was configured as the RC and Device2 was configured as the EP.

For unidirectional reads, the read transactions were all outbound reads, where Device1 read data from Device2. For these transactions, the read request was initiated by Device1. When Device2 received the read request, it used the PCle master to transfer the read data from memory to the PCle module. When Device1 received the read data from Device2, the PCle slave in Device1 provided the data to EDMA to transfer the data from the PCle module to memory. PCle0 of Device1 is connected to PCle0 on Device 2 (same for PCle1).

For bidirectional transfers, PCIe on both devices initiated read requests simultaneously.

Figure 10. Impact of EDMA Selection on Throughput – Unidirectional Reads

www.ti.com PCIe

Figure 10 shows the impact of EDMA TC selection on the read throughput when remote device returns data with 128 byte payload size. Overall, EDMA0 and EDMA4 perform best for both PCle0 and PCle1. EDMA1 and EDMA2 perform similar to EDMA0 & EDMA4 for PCle0 but do not perform well with PCle1. This is because EDMA1/EDMA2 and PCle1 slave lie on different TeraNets which causes 128 byte packets to fragment into 64 byte packets while performing the inter-TeraNet transaction to PCle1 slave. This increases overhead and reduces performance. PCle0 is not impacted since PCle0 slave lies on the same TeraNet as EDMA1 and EDMA2; fragmentation is thus avoided. EDMA3 performance is lower for both PCle0 and PCle1 because it has a smaller DBS size (64 bytes) compared to other EDMAs (128 bytes) resulting in extra overhead.

Some small variations in the results shown may be attributed to measurement accuracy.

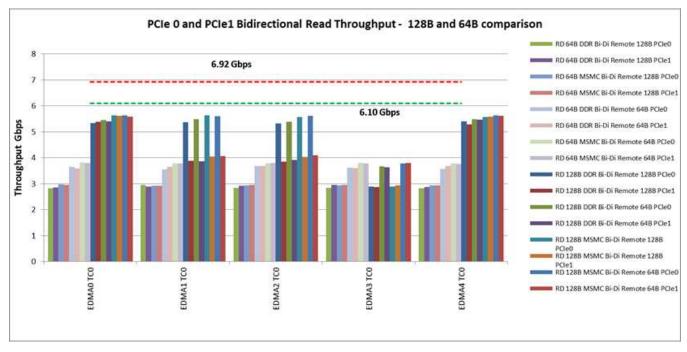

Figure 11 shows the plots in Figure 10 combined with data when the remote device returns data with 64 byte packet size. A 64 byte payload size does not allow EDMAs with 128 byte DBS (EDMA0/1/2/4) to take advantage of the full burst size, resulting in lower throughput compared to 128 byte payload size. EDMA3 results are unaffected since it already has a 64-byte DBS.

Some small variations in the results shown may be attributed to measurement accuracy

Figure 11. Comparing 128B and 64B Payload Size - Unidirectional Reads

PCIe www.ti.com

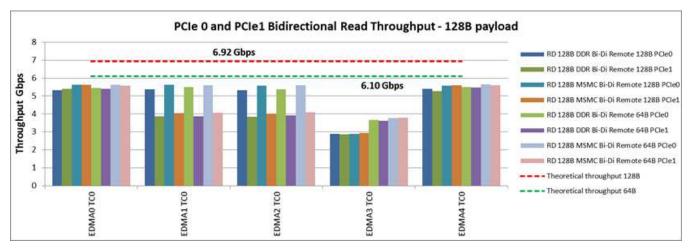

Figure 12. Impact of EDMA Selection on Throughput - Bidirectional Reads

Figure 13. Comparing 128B and 64B Payload Size - Bidirectional Reads

The following broad recommendations can be made to optimize read throughput on PCIe:

- Use 128 byte payload size

- For both PCle0 and PCle1, use EDMA0 or EDMA4 where possible

- Avoid 64 byte payload size

- Avoid EDMA1 and EDMA2 for PCIe1

- Avoid EDMA3 for both PCIe and PCIe1

www.ti.com PCIe

#### 6.3.2 PCle Write Throughput

The throughput shown in this section is the data payload only, and does not include any overhead due to PHY, DLLP, or TLP headers, and does not include overhead due to 8b/10b encoding. For this test, write transactions were executed between two Keystone II PCIe devices. Device1 is configured as the RC and Device2 is configured as the EP.

For unidirectional writes, the write transactions were all outbound writes, where Device1 writes data to Device2. For these transactions, the write request was initiated by Device1. Device1 used EDMA to transfer data from memory to the PCIe slave, which was transferred over the PCIe interface to Device2. When Device2 received the write data, the PCIe master was used to transfer the data to memory. For bidirectional transfers, PCIe on both devices initiated write requests simultaneously.

"Diff ports" is a special case where PCle0 on Device1 is connected to PCle1 on Device2 and PCle1 on Device1 is connected to PCle0 on Device2. For all other cases, PCle0 of Device1 is connected to PCle0 on Device 2 (same for PCle1).

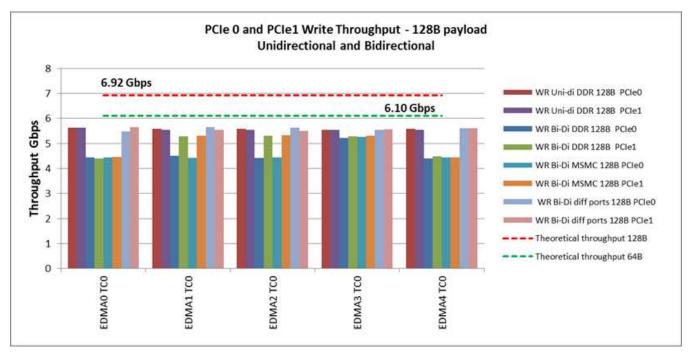

Figure 14. Impact of EDMA Selection on Write Throughput

Figure 14 shows the unidirectional and bidirectional write throughput for PCIe0 and PCIe1 for various EDMA selections. All EDMAs perform equally well for unidirectional write throughput on both PCIe0 and PCIe1. Bidirectional transfers slow down the PCIe0 throughput when EDMA0/1/2/4 are used. However, EDMA3 can be used without slowing down PCIe0 bidirectional write throughput. PCIe1 bidirectional throughput degrades when using EDMA0 or EDMA4, but performs well for EDMA1, EDMA2 and EDMA3. Bidirectional throughput when PCIe are connected to different ports (PCIe0 to PCIe1 and vice-versa) performs well regardless of EDMA selection.

Some small variations in the results shown may be attributed to measurement accuracy.

SRIO Throughput www.ti.com

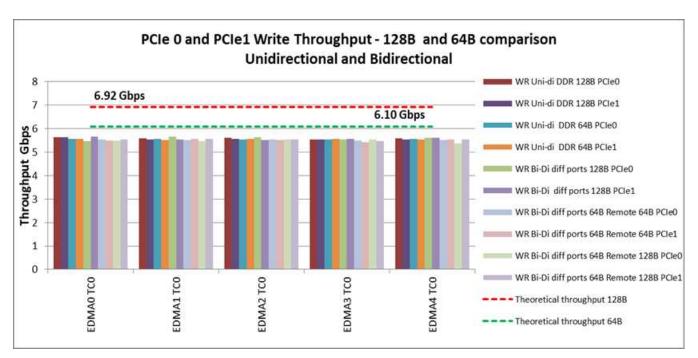

Figure 15. Comparing 128B and 64B Payload Size

As seen in Figure 15, the write throughput does not change with the payload size due to an internal feature of the PCIe subsystem. This feature also results in write throughput being lower than the read throughput for 128 byte payload size.

The following broad recommendations can be made to optimize write throughput on PCIe:

- For unidirectional or bidirectional throughput (both PCle0 and PCle1), use EDMA3 where possible. For PCle1, EDMA1 and EDMA2 can also be used.

- For bidirectional throughput (both PCle0 and PCle1) avoid EDMA0 and EDMA4. For PCle0, also avoid EDMA1 and EDMA2.

#### **7** SRIO Throughput

Serial RapidIO (SRIO) is a high-bandwidth system level interconnect. It is a packet switched interconnect intended for high speed chip-to-chip and board-to-board communication. SRIO supports DirectIO transfers and Message Passing transfers.

The RapidIO specification defines four different bandwidths for each differential pair of I/O signals: 1.25, 2.5, 3.125, and 5 Gbps. Due to 8-bit/10-bit encoding overhead, the effective data bandwidths per differential pair is 1, 2, 2.5, and 4 Gbps, respectively. A 1x port is defined as one TX and one RX differential pair. A 4x port is a combination of four of these pairs.

### 7.1 DirectIO (LSU) Operation

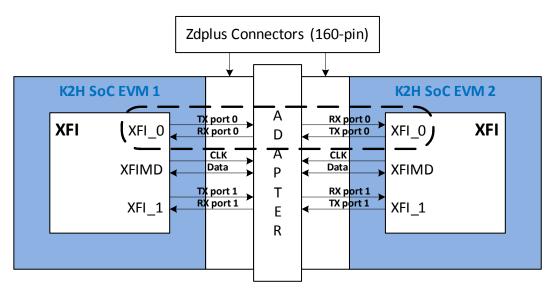

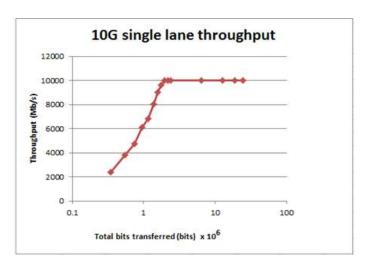

The DirectIO (Load/Store) module serves as the source of all outgoing directIO packets. In this operation, the RapidIO packet contains the specific address where the data should be stored or read in the destination device. There are 8 LSUs in total.