# AN-1032: An Introduction to FPD-Link

#### Ankur Verma

#### **ABSTRACT**

The FPD-Link chipset architecture in conjunction with the LVDS technology provides the high bandwidth interface necessary for leading edge display technology. The conversion from parallel TTL to serial LVDS allows for a narrow interface between graphics controller and panel. A narrower interface means lower cable cost and simplifies the physical connection through a notebook hinge. The high speed of the LVDS technology supports the high data transfer rates required. EMI problems typically associated with such high-speed transmissions are addressed by the low signal swing and differential nature of LVDS. LVDS, with its high speed capabilities, will allow future products in the FPD-Link chipset to support the industry's ever increasing need for bandwidth. Texas Instrument's FPD-Link provides the solution for the latest in display technology.

#### Contents

| 1  | The FPD-Link Chipset                                            | 2 |

|----|-----------------------------------------------------------------|---|

| 2  | LVDS: The Technology of Choice                                  | 3 |

| 3  | Designing With FPD-Link                                         | 3 |

| 4  | TTL to LVDS Translation                                         | 4 |

| 5  | Power Sequencing                                                | 5 |

| 6  | Data Strobes                                                    | Ę |

| 7  | Clock Jitter Considerations                                     | 5 |

| 8  | EMI Benefits                                                    | 6 |

| 9  | AEQ                                                             | 6 |

| 10 | CMLOUT                                                          | 6 |

| 11 | BIST                                                            |   |

| 12 | Frame Sync                                                      |   |

| 13 | Pattern Generation                                              |   |

| 14 | Aliasing                                                        | 6 |

| 15 | Conclusion                                                      | 7 |

|    | List of Figures                                                 |   |

|    | _                                                               |   |

| 1  | Typical FPD-Link Application (24-Bit Color)                     |   |

| 2  | FPD-Link Chipset for 18-Bit Color                               | 2 |

| 3  | FPD-Link Termination                                            | 3 |

| 4  | Decoupling Configuration                                        | 3 |

| 5  | Seven Bits of LVDS in One Clock Cycle                           | 2 |

| 6  | 28 Parallel TTL Data Inputs Mapped to LVDS Outputs (DS90CR581)  |   |

| 7  | 21 Parallel TTL Data Inputs Mapped to LVDS Outputs (DS90CR561)  |   |

| ,  | 21 Faraller FTE Data Iliputs Mapped to EVDS Outputs (DSSOCKSOT) | - |

#### **Trademarks**

TRI-STATE is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

The FPD-Link Chipset www.ti.com

## 1 The FPD-Link Chipset

The FPD-Link (Flat Panel Display Link) chipset is a family of interface devices specifically configured to support data transmission from graphics controllers to LCD panels. The technology employed, LVDS (Low Voltage Differential Signaling), is ideal for high-speed, low-power data transfer. This enables the implementation of high end displays such as SVGA (800 × 600) and XGA (1024 × 768).

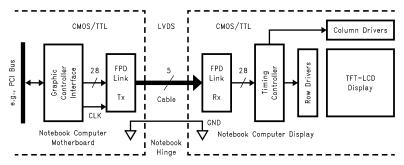

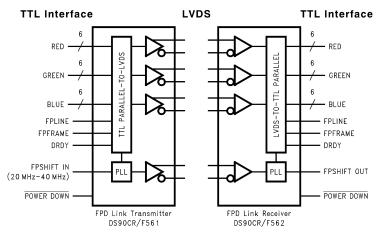

The predominant issues limiting performance in these high-end displays are speed, power, and EMI considerations. The user is also concerned with the physical interface to the display; the fewer wires the better. The FPD-Link chipset addresses these issues with LVDS technology and muxing TTL signals to higher speed LVDS signals which allows a substantially narrower interface between host and display. In a typical application (see Figure 1), TTL-level RGB and control data from the graphic controller arrives at the inputs of the FPD-Link transmitter. The parallel TTL data is muxed and converted to LVDS. The outputs of the FPD-Link transmitter drive the LVDS data on the cable which connects the motherboard to the display. The LVDS data traverses the cable to the FPD-Link receiver at the display. The received data is then demuxed, converted back to TTL levels, and sent to the inputs of the timing controller. This muxing of parallel TTL signals allows the data to travel at faster speeds across a narrow interface, addressing the needs associated with high-bandwidth communication.

The FPD-Link chipset consists of transmitters (TTL to LVDS) and receivers (LVDS to TTL) designed to support 18-bit and 24-bit color displays. Devices are available with falling edge, rising edge or programmable data strobe for a convenient interface to a variety of graphics and LCD panel controllers. The FPD-Link product family includes 5-V and 3.3-V chipsets that support a frequency range of 20 MHz to 65 MHz. See Figure 2.

Figure 1. Typical FPD-Link Application (24-Bit Color)

Figure 2. FPD-Link Chipset for 18-Bit Color

2

# 2 LVDS: The Technology of Choice

LVDS is a differential signaling technology designed to support applications requiring high speed-data transfer, common-mode noise rejection, and low power consumption. The low signal swing (345 mV) and differential nature of the signals reduces noise impact (that is, crosstalk) and allows high operating frequencies. The constant current source is designed for low power consumption: a single LVDS driver has a static  $I_{CC}$  of 4 mA and dynamic  $I_{CC}$  of 22 mA. These attributes contribute to the low EMI of LVDS.

#### 3 Designing With FPD-Link

The FPD-Link chipset provides the support needed for high-speed display interfaces such as SVGA (800  $\times$  600) and XGA (1024  $\times$  768). Take care when designing with these devices to fully realize the benefits of the technology.

**Board Layout:** To obtain the maximum benefit from the noise and EMI reductions of LVDS, pay attention to the layout of differential lines. Lines of a differential pair should always be adjacent to eliminate noise interference from other signals and take full advantage of the noise canceling of the differential signals. The board designer must also maintain equal length on the signal traces for a given pair. As with any high-speed design, the impedance discontinuities should be limited (reduce number of vias, no 90° angles on traces). Any discontinuities which do occur on one signal line should be mirrored in the other line of the differential pair. These considerations limit reflections and crosstalk which would adversely effect high frequency performance and EMI.

**24-Bit to 18-Bit Interface:** It may be necessary to interface a 24-bit transmitter to an 18-bit receiver (or vice-versa). In this case, the least significant color bits of the 24-bit transmitter are mapped to the fourth LVDS channel. Three LVDS data channels are connected to the 18-bit receiver; the remaining fourth LVDS data channel is left open.

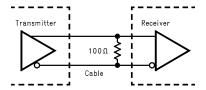

**Termination:** Use of current mode drivers requires a terminating resistor across the receiver inputs. The FPD-Link chipset uses a single  $100-\Omega$  resistor between the positive and negative lines of each receiver differential pair (see Figure 3). No additional pullup or pulldown resistors are necessary as with some other differential technologies (PECL). Surface mount resistors are recommended to avoid the additional inductance that accompanies leaded resistors. These resistors should be placed as close as possible to the receiver input pins to reduce stubs and effectively terminate the differential lines.

Figure 3. FPD-Link Termination

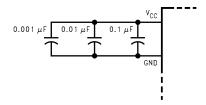

**Decoupling Capacitors:** Bypassing capacitors are needed to reduce the impact of switching noise which could limit performance. Decoupling capacitors (surface mount) between each  $V_{CC}$  and ground pin are recommended. Refer to Figure 4 for an example of connections and capacitor values.

Figure 4. Decoupling Configuration

TTL to LVDS Translation www.ti.com

Cables: A cable interface between the transmitter and receiver needs to support the differential LVDS pairs (2 wires/pair). The 8-bit chipsets require 10 signal wires; the 6-bit chipsets require 8 signal wires. This is a significant reduction in cable width as compared to the straight TTL interface which needs 28 or 21 signal wires. Shielded cables will reduce noise emissions that contribute to EMI. In addition, ground lines between each differential pair will provide further noise shielding. The grounding provides a barrier to noise coupling between adjacent pairs, thus reducing additive effects of the electrical fields. In addition to the noise shielding, the low impedance ground connection between the transmitter and receiver provides a common mode return path. A minimum of two ground conductors is recommended to provide this low impedance path.

An ideal cable or connector interface would have a constant  $100-\Omega$  differential impedance throughout the path. TI recommends that cable skew remain below 250 ps (at 65 MHz) to help maintain a sufficient data sampling window. Edge rate attenuation should also be limited to avoid signal degradation at high frequencies. Both skew and edge rate attenuation are a function of cable length. As the distance between host and display increases, a higher quality cable is needed to preserve signal integrity.

Though the interconnect between host and LCD is typically short, the FPD-Link transmitters can drive cables over 5 meters long. This makes the FPD-Link useful for remote display applications.

#### 4 TTL to LVDS Translation

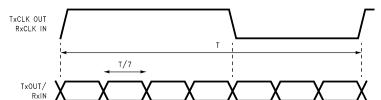

The FPD-Link transmitter translates 21 or 28 bit wide TTL data into LVDS data 3 or 4 bits wide and 7 bits deep. An additional pair of LVDS signals is used to transmit the clock. All 21/28 parallel TTL bits are transferred with a single data strobe. A single strobe also transmits all bits at the LVDS port. The clock to data relationship at the LVDS interface is shown in Figure 5. The clock at the LVDS ports is transmitted at the TTL clock input frequency (that is, 65 MHz); the data is transmitted at 3.5 times the clock frequency (227 MHz).

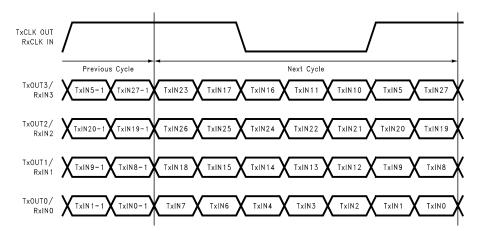

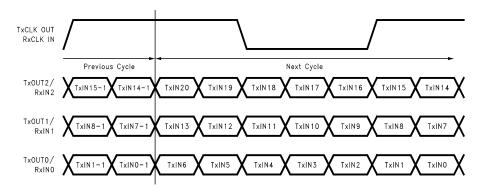

The TTL data bits are mapped into the 3 or 4 LVDS signal lines. Figure 6 and Figure 7 show the relationship of parallel TTL data bits to the LVDS link.

Figure 5. Seven Bits of LVDS in One Clock Cycle

Figure 6. 28 Parallel TTL Data Inputs Mapped to LVDS Outputs (DS90CR581)

www.ti.com Power Sequencing

Figure 7. 21 Parallel TTL Data Inputs Mapped to LVDS Outputs (DS90CR561)

# 5 Power Sequencing

Outputs of the FPD-Link transmitter remain in TRI-STATE® until the power supply reaches 3 V. The receiver outputs are low when power down is asserted. Clock and data outputs will begin to toggle 10 ms after  $V_{CC}$  has reached 3 V and the Powerdown pin is above 2 V.

When powering down the device, the  $\overline{\text{Powerdown}}$  pin may be asserted. This will TRI-STATE the transmitter outputs to prevent excess current flow (55  $\mu\text{A}$  maximum). This input is typically driven by power supply control logic.

The FPD-Link chipset is designed to protect itself from accidental loss of power to either the transmitter or receiver. If power to the transmit board is lost, the receiver clocks (input and output) stop. The data outputs (RxOUT) retain the states they were in when the clocks stopped. When the receiver board loses power, the receiver inputs are shorted to  $V_{\rm CC}$  through a diode. Current is limited (5 mA per input) by the fixed current mode drivers, thus avoiding the potential for latchup when powering the device. (Note: latchup immunity is > 300 mA) In addition, an external circuit can be used such that when the receiver board powers down, the transmit  $\overline{Powerdown}$  pin is pulled low to TRI-STATE the transmitter outputs so short-circuit current does not flow.

#### 6 Data Strobes

The FPD-Link transmitters are available with a falling edge or selectable data strobe. A rising or falling edge strobe device should be selected based on the characteristics of the VGA controller being used. The receiver is available with a falling edge strobe to match flat panel timing controller requirements. The strobe edge only effects the TTL inputs of the transmitter or outputs of the receiver. The LVDS interface is not impacted, therefore, rising and falling edge transmitters and receivers are fully interoperable.

#### 7 Clock Jitter Considerations

The FPD-Link devices employ a PLL to generate and recover the clock transmitted across the LVDS interface. These high-speed signals require an accurate, low noise clock signal. The width of the LVDS data bits is one seventh the clock period. For example, a 40 MHz clock has a period of 25 ns; the width of a data bit is 3.6 ns. Differential signal skew, interconnect skew, data and clock jitter all reduce the available window for sampling data. It is recommended to keep each component as small as possible to support the maximum operating frequency. The initial clock source should provide a clean signal to the Tx clock input. Individual bypassing of each  $V_{\rm CC}$  to ground will minimize the noise passed on to the PLL, thus creating a low jitter LVDS clock. These measures provide more margin for channel-to-channel skew and interconnect skew as a part of the overall jitter/skew budget.

EMI Benefits www.ti.com

#### 8 EMI Benefits

One of the benefits to using the FPD-Link chips with their LVDS signaling is the relatively low EMI. LVDS has demonstrated lower spectral content (EMI) than competing technologies such as RS-422, PECL, and CMOS (often used in display interface applications). Testing was performed using DCM (direct contact method) with a 32-MHz continuous wave. Low EMI translates to less noise on a cable in a box-to-box transmission environment. The cable shielding requirements are less, thus the cost of interconnect is reduced.

#### 9 AEQ

On the latest FPD-Link deserializers, the receiver inputs provide an adaptive equalization filter to compensate for signal degradation from the interconnect components. To determine the maximum cable reach, consider the factors that affect signal integrity such as jitter, skew, ISI, crosstalk, and so forth. The equalization status and configuration are programmable through AEQ registers. If these register values are continuously read and the values jump sporadically, then the AEQ is not properly compensating for factors that affect signal integrity. If the deserializer loses Lock, the adaptive equalizer will reset and perform the Lock algorithm again to reacquire the serial data stream being sent by the serializer.

#### 10 CMLOUT

The latest FPD-Link deserializers include an internal Channel Monitor Loop-through output on the CMLOUTP/N pins. A buffered loop-through output driver is provided on the CMLOUTP/N to observe jitter after equalization for each of the two RX receive channels. The CMLOUT monitors the post EQ stage thus providing the recovered input of the deserializer signal. The measured serial data width on the CMLOUT loop-through is the total jitter including the internal driver, AEQ, back channel echo, and so forth. Each channel also has its own CMLOUT monitor and can be used for debug purposes. This CMLOUT is useful in identifying gross signal conditioning issues. Typically, these pins are routed to test points and not connected. For monitoring CMLOUT, be sure to terminate with 100- $\Omega$  differential load.

### 11 BIST

An optional At-Speed Built-In Self Test (BIST) feature supports testing of the high-speed serial link and the back channel without external data connections. This is useful in the prototype stage, equipment production, in-system test, and system diagnostics.

#### 12 Frame Sync

Most multiple image-sensor systems need the image data to arrive to the image signal processor (ISP) at the same time. The use of a frame synchronization signal (FrameSync) ensures that data for every frame is sent to every deserializer simultaneously. Then, the synchronized data can be forwarded to the ISP. The frame sync signal can be sent across the backchannel from an internally generated signal from the deserializer or an externally generated signal gathered by the deserializer GPIOs.

#### 13 Pattern Generation

Pattern Generation refers to using an internal block of the FPD-Link chipsets to generate test data. The generation of this data is used to check links in the system without directly using the data gathered by the image sensor. This is a very useful feature in debugging the system.

#### 14 Aliasing

Alias ID refers to the alternate 7-bit address assigned to either Serializer, Deserializer, or remote slave. Device Alias helps to differentiate between the devices having same Device ID or physical I2C address. TI recommends that the I2C master should always use the device alias to communicate with a remote I2C slave.

www.ti.com Conclusion

#### 15 Conclusion

The FPD-Link chipset architecture in conjunction with the LVDS technology provides the high bandwidth interface necessary for leading edge display technology. The conversion from parallel TTL to serial LVDS allows for a narrow interface between graphics controller and panel. A narrower interface means lower cable cost and simplifies the physical connection through a notebook hinge. The high speed of the LVDS technology supports the high data transfer rates required. EMI problems typically associated with such high-speed transmissions are addressed by the low signal swing and differential nature of LVDS. LVDS, with its high speed capabilities, will allow future products in the FPD-Link chipset to support the industry's ever increasing need for bandwidth. TI's FPD-Link provides the solution for the latest in display technology.

Revision History www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from B Revision (April 2013) to C Revision |                    | Page |   |

|----------------------------------------------------|--------------------|------|---|

| •                                                  | Added new sections |      | 6 |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated