# How to Map RGB Signals to LVDS/OpenLDI(OLDI) Displays

The purpose of this application note is to provide the data mapping to ensure interoperability between the LVDS (OpenLDI/OLDI) display interface and 18-bit or 24-bit LVDS SerDes (Serializer/Deserializer, or transmitter/receiver). These devices are also known as Channel-Link and FPD-Link devices.

#### Contents

| 1 | Introduction                                                                 | 1 |

|---|------------------------------------------------------------------------------|---|

| 2 | How to Read the Tables                                                       | 2 |

| 3 | Single Pixel per Clock Input Application                                     | 2 |

| 4 | Dual Pixel per Clock Input Application                                       | 4 |

| 5 | Single Pixel per Clock Input to Dual Pixel per Clock Output Application      | 6 |

| 6 | TFT Control Data Signal and CLK                                              |   |

| 7 | Conclusion                                                                   | 7 |

|   | List of Figures                                                              |   |

| 1 | JEIDA/Format 1 Mapping for 24-bit, Single Pixel per Clock Input Applications | 3 |

| 2 | VESA/Format 2 Mapping for 24-bit, Single Pixel per Clock Input Applications  | 3 |

| 3 | JEIDA/Format 1 Mapping for 24-bit Transmitters in 18-bit Applications        | 3 |

| 4 | JEIDA/Format 1 Mapping for Dual Pixel per Clock Input Application            | 5 |

| 5 | VESA/Format 2 Mapping for Dual Pixel per Clock Input Application             | 5 |

|   | List of Tables                                                               |   |

| 1 | Single Pixel per Clock Input Application                                     | 2 |

| 2 | Dual Pixel per Clock Input Application                                       | 4 |

| 3 | Single Pixel per Clock Input to Dual Pixel per Clock Output Application      | 6 |

| 4 | TFT Control Data Signal and CLK                                              | 7 |

### **Trademarks**

All trademarks are the property of their respective owners.

## 1 Introduction

The data mapping this document highlights is the JEIDA format (also known as Format 1), where the most significant bits (MSB) for an 18-bit application are mapped exactly the same as the most significant bits in the 24-bit application from the VGA controllers. Only 3 LVDS serialized data lines are required for an 18-bit SerDes application, while a 24-bit application uses 4 LVDS data lines. The additional least significant bits (LSB) in the 24-bit application are mapped to the 4th LVDS data line. This mapping format is shown in Figure 1.

However, the VESA format (also known as Format 2, where the MSB are mapped to the 4th LVDS data line) and any other format can also be used. This just requires re-mapping the bits to the correct pins, as shown in Figure 2.

How to Read the Tables www.ti.com

The tables in the following pages show the connections needed when using LVDS SerDes chipsets for flat panel display applications. Starting from the left, the outputs of the VGA are noted from LSB (less significant bit) to MSB (most significant bit). VGA controllers typically name the LSB as R0, B0, and G0. The MSB remains the same from the VGA controller pin definition, but 24-bit and 18-bit colors are named differently. This confuses the connections needed, so careful review of the following tables is recommended to ensure correct color bit mapping.

Although the JEIDA format is utilized for the mapping pinout in the tables in this document, the SerDes are not limited to this format. The most important thing is to ensure that whatever mapping is used is compatible with what the display expects.

In short, follow the below steps to correctly map to a display:

- 1. Identify the input application (e.g. single pixel or dual pixel)

- 2. Identify the RGB mapping format on the display datasheet (e.g. the image on the left of Figure 1)

- 3. Identify the pin number mapping on the SerDes datasheet (e.g. the image on the right of Figure 1)

- 4. Map the RGB signals to the appropriate pins

## 2 How to Read the Tables

The tables are read from left to right. From the left, the R0, G0 and B0 bits are the least significant bits (LSB) as defined by the VGA controllers. These signals should be connected to the input data pins of the transmitters (i.e., color bit R0 in an 18-bit application must be connected to Txin0 or R10, depending on the transmitter being used). The output signals of the receiver are mirror images of the input signals to the transmitter. The DS90C387/DS90CF388 are capable of supporting single pixel, dual pixel, or single-in/dual-out pixel modes. Determine the mode to be used, and then review the corresponding table. Specific part numbers like the DS90C387 and DS90C385 are used as examples in this document, but the procedure is the same for every LVDS SerDes device. Consult the mapping diagrams (e.g. Figure 1) on the individual datasheets to map the pins to the correct bits.

## 3 Single Pixel per Clock Input Application

Table 1. Single Pixel per Clock Input Application

| VGA — TFT Data<br>Signal |        | Transmitter Input Data Pin |                     |                     | Receiver Output Data Pin |                       |                      | TFT Panel Data Signal |        |

|--------------------------|--------|----------------------------|---------------------|---------------------|--------------------------|-----------------------|----------------------|-----------------------|--------|

| 24-bit                   | 18-bit | 24-bit Tx<br>(C385)        | 18-bit Tx<br>(C365) | 48-bit Tx<br>(C387) | 24-bit Rx<br>(CF384A)    | 18-bit Rx<br>(CF364A) | 48-bit Rx<br>(CF388) | 18-bit                | 24-bit |

| R0 (LSB)                 |        | Txin27                     |                     | R16                 | Rxout27                  |                       | R16                  |                       | R0     |

| R1                       |        | Txin5                      |                     | R17                 | Rxout5                   |                       | R17                  |                       | R1     |

| R2                       | R0     | Txin0                      | Txin0               | R10                 | Rxout0                   | Rxout0                | R10                  | R0                    | R2     |

| R3                       | R1     | Txin1                      | Txin1               | R11                 | Rxout1                   | Rxout1                | R11                  | R1                    | R3     |

| R4                       | R2     | Txin2                      | Txin2               | R12                 | Rxout2                   | Rxout2                | R12                  | R2                    | R4     |

| R5                       | R3     | Txin3                      | Txin3               | R13                 | Rxout3                   | Rxout3                | R13                  | R3                    | R5     |

| R6                       | R4     | Txin4                      | Txin4               | R14                 | Rxout4                   | Rxout4                | R14                  | R4                    | R6     |

| R7 (MSB)                 | R5     | Txin6                      | Txin5               | R15                 | Rxout6                   | Rxout5                | R15                  | R5                    | R7     |

| G0 (LSB)                 |        | Txin10                     |                     | G16                 | Rxout10                  |                       | G16                  |                       | G0     |

| G1                       |        | Txin11                     |                     | G17                 | Rxout11                  |                       | G17                  |                       | G1     |

| G2                       | G0     | Txin7                      | Txin6               | G10                 | Rxout7                   | Rxout6                | G10                  | G0                    | G2     |

| G3                       | G1     | Txin8                      | Txin7               | G11                 | Rxout8                   | Rxout7                | G11                  | G1                    | G3     |

| G4                       | G2     | Txin9                      | Txin8               | G12                 | Rxout9                   | Rxout8                | G12                  | G2                    | G4     |

| G5                       | G3     | Txin12                     | Txin9               | G13                 | Rxout12                  | Rxout9                | G13                  | G3                    | G5     |

| G6                       | G4     | Txin13                     | Txin10              | G14                 | Rxout13                  | Rxout10               | G14                  | G4                    | G6     |

| G7 (MSB)                 | G5     | Txin14                     | Txin11              | G15                 | Rxout14                  | Rxout11               | G15                  | G5                    | G7     |

| B0 (LSB)                 |        | Txin16                     |                     | B16                 | Rxout16                  |                       | B16                  |                       | В0     |

| B1                       |        | Txin17                     |                     | B17                 | Rxout17                  |                       | B17                  |                       | B1     |

| VGA — TFT Data<br>Signal |        | Transmitter Input Data Pin |                     |                     | Recei                 | ver Output Da         | TFT Panel Data Signal |        |        |

|--------------------------|--------|----------------------------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|--------|--------|

| 24-bit                   | 18-bit | 24-bit Tx<br>(C385)        | 18-bit Tx<br>(C365) | 48-bit Tx<br>(C387) | 24-bit Rx<br>(CF384A) | 18-bit Rx<br>(CF364A) | 48-bit Rx<br>(CF388)  | 18-bit | 24-bit |

| B2                       | В0     | Txin15                     | Txin12              | B10                 | Rxout15               | Rxout12               | B10                   | В0     | B2     |

| В3                       | B1     | Txin18                     | Txin13              | B11                 | Rxout18               | Rxout13               | B11                   | B1     | В3     |

| B4                       | B2     | Txin19                     | Txin14              | B12                 | Rxout19               | Rxout14               | B12                   | B2     | B4     |

| B5                       | В3     | Txin20                     | Txin15              | B13                 | Rxout20               | Rxout15               | B13                   | В3     | B5     |

| B6                       | B4     | Txin21                     | Txin16              | B14                 | Rxout21               | Rxout16               | B14                   | B4     | B6     |

| B7 (MSB)                 | B5     | Txin22                     | Txin17              | B15                 | Rxout22               | Rxout17               | B15                   | B5     | B7     |

Table 1. Single Pixel per Clock Input Application (continued)

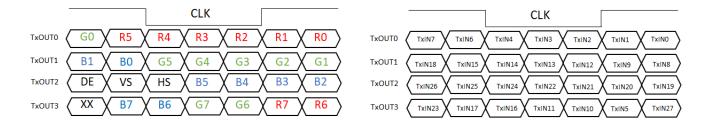

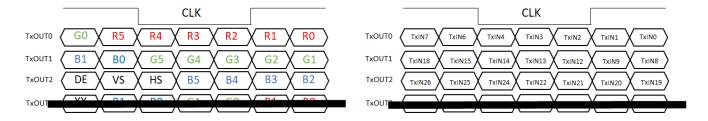

Figure 1. JEIDA/Format 1 Mapping for 24-bit, Single Pixel per Clock Input Applications

Figure 2. VESA/Format 2 Mapping for 24-bit, Single Pixel per Clock Input Applications

Figure 1 and Figure 2 illustrate JEIDA and VESA mapping and the corresponding pinout for 24-bit SerDes devices like the DS90C385 transmitter. "XX" is an extra general-purpose bit. You can choose to tie this input low if it will be unused, or you can send additional control information if necessary on this input.

The JEIDA format is very convenient for switching from 24-bits to 18-bits with 24-bit SerDes. When 24-bit SerDes is used in 18-bit applications, the LSB are dropped off. With the JEIDA format, the 4th LVDS data line (where RGB24[0:1] are) is ignored, and RGB18[0:5] maps to RGB24[2:7] without any user intervention. For example, what was previously R2 now becomes R0, and what was previously R7 now becomes R5. This can be seen in Figure 3 below.

Figure 3. JEIDA/Format 1 Mapping for 24-bit Transmitters in 18-bit Applications

# 4 Dual Pixel per Clock Input Application

Table 2. Dual Pixel per Clock Input Application

| VGA — Sig    |        | Trans                | mitter Input D       | ata Pin              | Recei                  | ver Output D           | TFT Panel Data<br>Signal |        |     |

|--------------|--------|----------------------|----------------------|----------------------|------------------------|------------------------|--------------------------|--------|-----|

| 48-bit       | 36-bit | 24-bit 2Tx<br>(C385) | 18-bit 2Tx<br>(C365) | 48-bit 1Tx<br>(C387) | 24-bit 2Rx<br>(CF384A) | 18-bit 2Rx<br>(CF364A) | 36-bit                   | 48-bit |     |

| OR0<br>(LSB) |        | Txin27               |                      | R16                  | Rxout27                |                        | R16                      |        | OR0 |

| OR1          |        | Txin5                |                      | R17                  | Rxout5                 |                        | R17                      |        | OR1 |

| OR2          | OR0    | Txin0                | Txin0                | R10                  | Rxout0                 | Rxout0                 | R10                      | OR0    | OR2 |

| OR3          | OR1    | Txin1                | Txin1                | R11                  | Rxout1                 | Rxout1                 | R11                      | OR1    | OR3 |

| OR4          | OR2    | Txin2                | Txin2                | R12                  | Rxout2                 | Rxout2                 | R12                      | OR2    | OR4 |

| OR5          | OR3    | Txin3                | Txin3                | R13                  | Rxout3                 | Rxout3                 | R13                      | OR3    | OR5 |

| OR6          | OR4    | Txin4                | Txin4                | R14                  | Rxout4                 | Rxout4                 | R14                      | OR4    | OR6 |

| OR7<br>(MSB) | OR5    | Txin6                | Txin5                | R15                  | Rxout6                 | Rxout5                 | R15                      | OR5    | OR7 |

| OG0<br>(LSB) |        | Txin10               |                      | G16                  | Rxout10                |                        | G16                      |        | OG0 |

| OG1          |        | Txin11               |                      | G17                  | Rxout11                |                        | G17                      |        | OG1 |

| OG2          | OG0    | Txin7                | Txin6                | G10                  | Rxout7                 | Rxout6                 | G10                      | OG0    | OG2 |

| OG3          | OG1    | Txin8                | Txin7                | G11                  | Rxout8                 | Rxout7                 | G11                      | OG1    | OG3 |

| OG4          | OG2    | Txin9                | Txin8                | G12                  | Rxout9                 | Rxout8                 | G12                      | OG2    | OG4 |

| OG5          | OG3    | Txin12               | Txin9                | G13                  | Rxout12                | Rxout9                 | G13                      | OG3    | OG5 |

| OG6          | OG4    | Txin13               | Txin10               | G14                  | Rxout13                | Rxout10                | G14                      | OG4    | OG6 |

| OG7<br>(MSB) | OG5    | Txin14               | Txin11               | G15                  | Rxout14                | Rxout11                | G15                      | OG5    | OG7 |

| OB0<br>(LSB) |        | Txin16               |                      | B16                  | Rxout16                |                        | B16                      |        | ОВ0 |

| OB1          |        | Txin17               |                      | B17                  | Rxout17                |                        | B17                      |        | OB1 |

| OB2          | OB0    | Txin15               | Txin12               | B10                  | Rxout15                | Rxout12                | B10                      | OB0    | OB2 |

| OB3          | OB1    | Txin18               | Txin13               | B11                  | Rxout18                | Rxout13                | B11                      | OB1    | OB3 |

| OB4          | OB2    | Txin19               | Txin14               | B12                  | Rxout19                | Rxout14                | B12                      | OB2    | OB4 |

| OB5          | OB3    | Txin20               | Txin15               | B13                  | Rxout20                | Rxout15                | B13                      | OB3    | OB5 |

| OB6          | OB4    | Txin21               | Txin16               | B14                  | Rxout21                | Rxout16                | B14                      | OB4    | OB6 |

| OB7<br>(MSB) | OB5    | Txin22               | Txin17               | B15                  | Rxout22                | Rxout17                | B15                      | OB5    | ОВ7 |

| ER0<br>(LSB) |        | Txin27               |                      | R26                  | Rxout27                |                        | R26                      |        | ER0 |

| ER1          |        | Txin5                |                      | R27                  | Rxout5                 |                        | R27                      |        | ER1 |

| ER2          | ER0    | Txin0                | Txin0                | R20                  | Rxout0                 | Rxout0                 | R20                      | ER0    | ER2 |

| ER3          | ER1    | Txin1                | Txin1                | R21                  | Rxout1                 | Rxout1                 | R21                      | ER1    | ER3 |

| ER4          | ER2    | Txin2                | Txin2                | R22                  | Rxout2                 | Rxout2                 | R22                      | ER2    | ER4 |

| ER5          | ER3    | Txin3                | Txin3                | R23                  | Rxout3                 | Rxout3                 | R23                      | ER3    | ER5 |

| ER6          | ER4    | Txin4                | Txin4                | R24                  | Rxout4                 | Rxout4                 | R24                      | ER4    | ER6 |

| ER7<br>(MSB) | ER5    | Txin6                | Txin5                | R25                  | Rxout6                 | Rxout5                 | R25                      | ER5    | ER7 |

| EG0<br>(LSB) |        | Txin10               |                      | G26                  | Rxout10                |                        | G26                      |        | EG0 |

| EG1          |        | Txin11               |                      | G27                  | Rxout11                |                        | G27                      |        | EG1 |

| EG2          | EG0    | Txin7                | Txin6                | G20                  | Rxout7                 | Rxout6                 | G20                      | EG0    | EG2 |

| EG3          | EG1    | Txin8                | Txin7                | G21                  | Rxout8                 | Rxout7                 | G21                      | EG1    | EG3 |

| EG4          | EG2    | Txin9                | Txin8                | G22                  | Rxout9                 | Rxout8                 | G22                      | EG2    | EG4 |

| rable 2. Buai i ixel per Glock input Application (continued) |        |                            |                      |                      |                        |                        |                          |        |        |  |  |

|--------------------------------------------------------------|--------|----------------------------|----------------------|----------------------|------------------------|------------------------|--------------------------|--------|--------|--|--|

| VGA — TFT Data<br>Signal                                     |        | Transmitter Input Data Pin |                      |                      | Recei                  | ver Output D           | TFT Panel Data<br>Signal |        |        |  |  |

| 48-bit                                                       | 36-bit | 24-bit 2Tx<br>(C385)       | 18-bit 2Tx<br>(C365) | 48-bit 1Tx<br>(C387) | 24-bit 2Rx<br>(CF384A) | 18-bit 2Rx<br>(CF364A) | 48-bit 1Rx<br>(CF388)    | 36-bit | 48-bit |  |  |

| EG5                                                          | EG3    | Txin12                     | Txin9                | G23                  | Rxout12                | Rxout9                 | G23                      | EG3    | EG5    |  |  |

| EG6                                                          | EG4    | Txin13                     | Txin10               | G24                  | Rxout13                | Rxout10                | G24                      | EG4    | EG6    |  |  |

| EG7<br>(MSB)                                                 | EG5    | Txin14                     | Txin11               | G25                  | Rxout14                | Rxout11                | G25                      | EG5    | EG7    |  |  |

| EB0<br>(LSB)                                                 |        | Txin16                     |                      | B26                  | Rxout16                |                        | B26                      |        | EB0    |  |  |

| EB1                                                          |        | Txin17                     |                      | B27                  | Rxout17                |                        | B27                      |        | EB1    |  |  |

| EB2                                                          | EB0    | Txin15                     | Txin12               | B20                  | Rxout15                | Rxout12                | B20                      | EB0    | EB2    |  |  |

| EB3                                                          | EB1    | Txin18                     | Txin13               | B21                  | Rxout18                | Rxout13                | B21                      | EB1    | EB3    |  |  |

| EB4                                                          | EB2    | Txin19                     | Txin14               | B22                  | Rxout19                | Rxout14                | B22                      | EB2    | EB4    |  |  |

| EB5                                                          | EB3    | Txin20                     | Txin15               | B23                  | Rxout20                | Rxout15                | B23                      | EB3    | EB5    |  |  |

| EB6                                                          | EB4    | Txin21                     | Txin16               | B24                  | Rxout21                | Rxout16                | B24                      | EB4    | EB6    |  |  |

| EB7                                                          | FB5    | Tyin22                     | Tyin17               | B25                  | Ryout22                | Ryout17                | B25                      | FB5    | FB7    |  |  |

Rxout22

Rxout17

B25

EB5

EB7

Table 2. Dual Pixel per Clock Input Application (continued)

B25

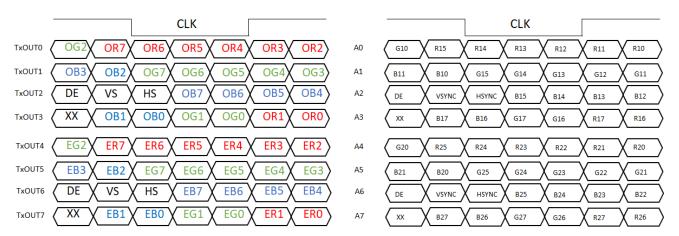

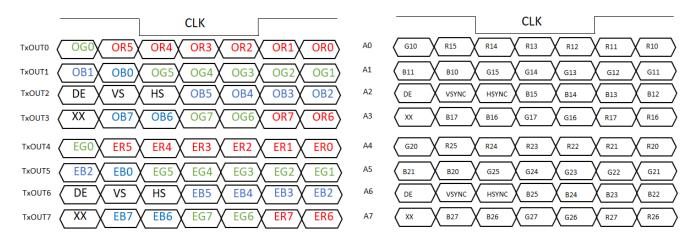

Figure 4. JEIDA/Format 1 Mapping for Dual Pixel per Clock Input Application

Figure 5. VESA/Format 2 Mapping for Dual Pixel per Clock Input Application

EB5

(MSB)

Txin22

Txin17

Figure 4 and Figure 5 illustrate JEIDA and VESA mapping for 48-bit SerDes with the DS90C387 transmitter as an example. Two 24-bit SerDes can also be used for this application. In this case, the odd data would be sent to one SerDes and the even data would be sent to the other SerDes.

## 5 Single Pixel per Clock Input to Dual Pixel per Clock Output Application

Table 3 shows how the input signals (single pixel) are split into odd (first) and even (second) pixels (dual pixels). This is only supported with an even number of cycles during blanking (blanking occurs when DE = low). A single input is split into odd and even pixel data starting with the odd (first) pixel outputs (A0-A3). The next pixel goes to the even pixel outputs (A4-A7). The splitting of the data signal also starts with DE (data enable) transitioning from logic low to high, indicating active data.

Table 3. Single Pixel per Clock Input to Dual Pixel per Clock Output Application

| VGA — TFT |        | Data Signal Input Data<br>Pin | Output Data Pin       | TFT Panel D | ata Signal |

|-----------|--------|-------------------------------|-----------------------|-------------|------------|

| 24-bit    | 18-bit | 48-bit 1Tx (C387)             | 48-bit 1Rx<br>(CF388) | 36-bit      | 48-bit     |

| R0 (LSB)  |        | R16                           | R16                   |             | OR0        |

| R1        |        | R17                           | R17                   |             | OR1        |

| R2        | R0     | R10                           | R10                   | OR0         | OR2        |

| R3        | R1     | R11                           | R11                   | OR1         | OR3        |

| R4        | R2     | R12                           | R12                   | OR2         | OR4        |

| R5        | R3     | R13                           | R13                   | OR3         | OR5        |

| R6        | R4     | R14                           | R14                   | OR4         | OR6        |

| R7 (MSB)  | R5     | R15                           | R15                   | OR5         | OR7        |

| G0 (LSB)  |        | G16                           | G16                   |             | OG0        |

| G1        |        | G17                           | G17                   |             | OG1        |

| G2        | G0     | G10                           | G10                   | OG0         | OG2        |

| G3        | G1     | G11                           | G11                   | OG1         | OG3        |

| G4        | G2     | G12                           | G12                   | OG2         | OG4        |

| G5        | G3     | G13                           | G13                   | OG3         | OG5        |

| G6        | G4     | G14                           | G14                   | OG4         | OG6        |

| G7 (MSB)  | G5     | G15                           | G15                   | OG5         | OG7        |

| B0 (LSB)  |        | B16                           | B16                   |             | OB0        |

| B1        |        | B17                           | B17                   |             | OB1        |

| B2        | В0     | B10                           | B10                   | OB0         | OB2        |

| В3        | B1     | B11                           | B11                   | OB1         | OB3        |

| B4        | B2     | B12                           | B12                   | OB2         | OB4        |

| B5        | B3     | B13                           | B13                   | OB3         | OB5        |

| B6        | B4     | B14                           | B14                   | OB4         | OB6        |

| B7 (MSB)  | B5     | B15                           | B15                   | OB5         | OB7        |

|           |        | R16                           | R26                   |             | ER0        |

|           |        | R17                           | R27                   |             | ER1        |

|           |        | R10                           | R20                   | ER0         | ER2        |

|           |        | R11                           | R21                   | ER1         | ER3        |

|           |        | R12                           | R22                   | ER2         | ER4        |

|           |        | R13                           | R23                   | ER3         | ER5        |

|           |        | R14                           | R24                   | ER4         | ER6        |

|           |        | R15                           | R25                   | ER5         | ER7        |

|           |        | G16                           | G26                   |             | EG0        |

|           |        | G17                           | G27                   |             | EG1        |

|           |        | G10                           | G20                   | EG0         | EG2        |

Table 3. Single Pixel per Clock Input to Dual Pixel per Clock Output Application (continued)

| VGA -  | — TFT  | Data Signal Input Data<br>Pin | Output Data Pin       | TFT Panel Data Signal |        |  |

|--------|--------|-------------------------------|-----------------------|-----------------------|--------|--|

| 24-bit | 18-bit | 48-bit 1Tx (C387)             | 48-bit 1Rx<br>(CF388) | 36-bit                | 48-bit |  |

|        |        | G11                           | G21                   | EG1                   | EG3    |  |

|        |        | G12                           | G22                   | EG2                   | EG4    |  |

|        |        | G13                           | G23                   | EG3                   | EG5    |  |

|        |        | G14                           | G24                   | EG4                   | EG6    |  |

|        |        | G15                           | G25                   | EG5                   | EG7    |  |

|        |        | B16                           | B26                   |                       | EB0    |  |

|        |        | B17                           | B27                   |                       | EB1    |  |

|        |        | B10                           | B20                   | EB0                   | EB2    |  |

|        |        | B11                           | B21                   | EB1                   | EB3    |  |

|        |        | B12                           | B22                   | EB2                   | EB4    |  |

|        |        | B13                           | B23                   | EB3                   | EB5    |  |

|        |        | B14                           | B24                   | EB4                   | EB6    |  |

|        |        | B15                           | B25                   | EB5                   | EB7    |  |

# 6 TFT Control Data Signal and CLK

Table 4 shows the mapping of the control signals (DE, HSYNC, VSYNC) for SerDes chipsets.

Table 4. TFT Control Data Signal and CLK

| VGA                     |                     | Input Data Pi       | n                   | C                     | Output Data Pi        | TFT Panel Data Signal |           |           |

|-------------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|-----------|-----------|

| — TFT<br>Data<br>Signal | 24-bit Tx<br>(C385) | 18-bit Tx<br>(C365) | 48-bit Tx<br>(C387) | 24-bit Rx<br>(CF384A) | 18-bit Rx<br>(CF364A) | 48-bit Rx<br>(CF388)  | 18/36-bit | 24/48-bit |

| HSYN<br>C               | Txin24              | Txin18              | HSYNC               | Rxout24               | Rxout18               | HSYNC                 | HSYNC     |           |

| VSYN<br>C               | Txin25              | Txin19              | VSYNC               | Rxout25               | Rxout19               | VSYNC                 | VSYNC     |           |

| DEN                     | Txin26              | Txin20              | DE                  | Rxout26               | Rxout20               | DE                    | DEN       |           |

| CLK                     | TxCLKin             | TxCLKin             | CLKIN               | TxCLKout              | TxCLKout              | CLKOUT                | CI        | _K        |

## 7 Conclusion

Using the recommended color mapping, interoperability is obtained between the LVDS display interface and 18-bit or 24-bit LVDS SerDes devices. It is also possible to directly interface a 24-bit VGA to an 18-bit panel as the additional LSB color bits are mapped to separate LVDS data lines.

Revision History www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <ul> <li>Formatted the user guide to Tl's latest documentation standard</li> <li>Changed the Introduction section</li> <li>Color-coded the Single Pixel per Clock Input Application and Dual Pixel per Clock Input Application gentables for the user</li> <li>Updated the VGA TFT Data Signal and TFT Panel Data Signal bit names for the 36-bit and 48-bit applications listed</li> </ul> | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Color-coded the Single Pixel per Clock Input Application and Dual Pixel per Clock Input Application gentables for the user                                                                                                                                                                                                                                                                  | 1    |

| user                                                                                                                                                                                                                                                                                                                                                                                        | 1    |

| <ul> <li>Undeted the VCA TET Data Signal and TET Data Signal bit names for the 26 bit and 49 bit applications listed</li> </ul>                                                                                                                                                                                                                                                             |      |

| Dual Pixel per Clock Input Application table                                                                                                                                                                                                                                                                                                                                                |      |

| <ul> <li>Updated the TFT Panel Data Signal bit names for the 36-bit and 48-bit applications listed in the Single Pixel per Clock Input to Dual Pixel per Clock Output Application table</li> </ul>                                                                                                                                                                                          |      |

| Changed the Conclusion section                                                                                                                                                                                                                                                                                                                                                              | 7    |

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated