# TPS7H1210EVM Evaluation Module (EVM)

## **ABSTRACT**

This user's guide describes operational use of the TPS7H1210EVM evaluation module (EVM) as a reference design for engineering demonstration and evaluation of the TPS7H1210-SEP, low-dropout (LDO) negative-voltage linear regulator in space enhanced plastic. This user's guide provides details about the EVM, its configuration, schematics, and bill of material (BOM).

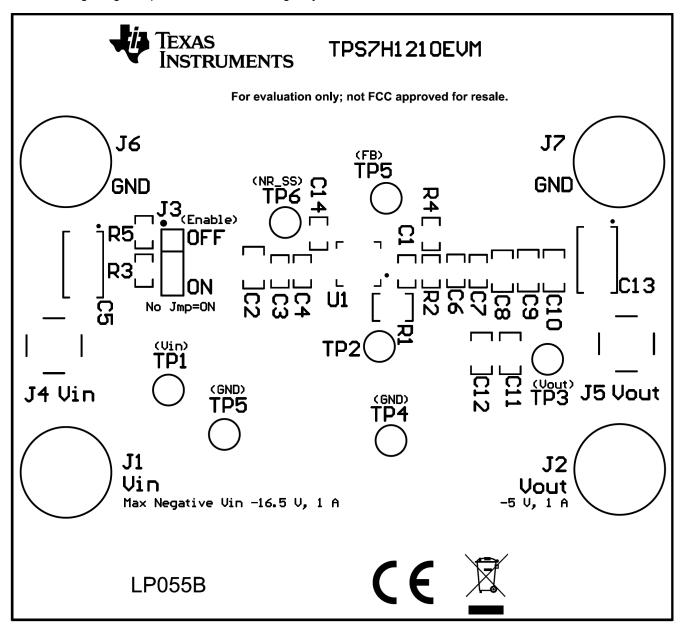

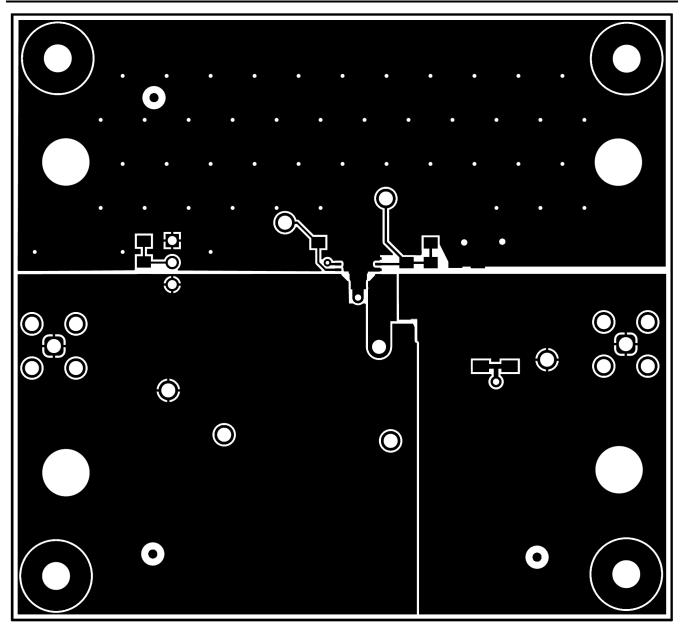

Figure 1-1. TPS7H1210EVM (LP055B)

# **Table of Contents**

| I Introduction                                      |                |

|-----------------------------------------------------|----------------|

| 1.1 Features                                        | 3              |

| 1.2 Applications.                                   | 3              |

| 2 Setup                                             | 4              |

| 2.1 Input/Output Connectors and Jumper Descriptions | 4              |

| 2.2 Equipment Setup                                 | 5              |

| 3 Operation                                         | 5              |

| Adjustable Operation                                | 6              |

| 5 Test Results                                      | <mark>7</mark> |

| 5.1 Enable, Disable, and Soft Start Timing          | <mark>7</mark> |

| 5.2 Output Load Transients                          |                |

|                                                     |                |

Trademarks www.ti.com

| 5.3 PSRR                                                             | 8  |

|----------------------------------------------------------------------|----|

| 5.4 Noise Spectral Density                                           | 9  |

| 6 Board Layout                                                       |    |

| 7 Schematic and Bill of Materials                                    |    |

|                                                                      |    |

| List of Figures                                                      |    |

| Figure 1-1. TPS7H1210EVM (LP055B)                                    |    |

| Figure 4-1. TPS7H1210-SEP LDO Schematic Showing Adjustment Resistors |    |

| Figure 5-1. Enable and Disable Timing                                | 7  |

| Figure 5-2. Load Step Transient Response Rising                      | 7  |

| Figure 5-3. Load Step Transient Response Falling                     | 8  |

| Figure 5-4. TPS7H1210EVM PSRR                                        | 8  |

| Figure 5-5. TPS7H1210EVM NSD                                         | 9  |

| Figure 6-1. Top Overlay Silkscreen                                   | 10 |

| Figure 6-2. Top Solder Mask                                          | 11 |

| Figure 6-3. Top Signal Layer                                         |    |

| Figure 6-4. Bottom Signal Layer                                      |    |

| Figure 7-1. TPS7H1210EVM (LP055B) Schematic                          |    |

|                                                                      |    |

| List of Tables                                                       |    |

| Table 2-1. Test Points                                               | 4  |

| Table 7-1. TPS7H1210EVM (LP055B) Bill of Materials                   | 14 |

# **Trademarks**

All trademarks are the property of their respective owners.

www.ti.com Introduction

#### 1 Introduction

The TPS7H1210-SEP negative voltage linear regulator is a low noise, high PSRR (power supply rejection ratio) regulator capable of sourcing a maximum load of 1 A.

The EVM is configured with a default feedback divider network to regulate to a -5-V  $V_{OUT}$ , with a usable  $V_{IN}$  range of  $(-5 \text{ V} - V_{DO})$  to -16.5 V. Worst case  $V_{DO}$  is 500 mV across recommended operating conditions. The EVM is intended to aid engineers in the evaluation of the operation and performance of the TPS7H1210-SEP linear regulator. The TPS7H1210-SEP low-dropout regulator allows input voltages from -3 V to -16.5 V and is capable of regulating any output voltage between -1.18 V and -15.5 V by changing the feedback resistor divider network. The EVM is capable of delivering up to 1 A to a load. Achieving the maximum load depends on multiple variables, including the input-output power dissipation, board thermal dissipation, and heat removal.

#### 1.1 Features

- · Low noise, high PSRR

- Input voltage range –3 V to –16.5 V

- Adjustable output range –1.18 V to –15.5 V

- Up to 1-A output

- Built-in current-limit and thermal shutdown

#### 1.2 Applications

- Supports low Earth orbit (LEO) space applications

- Satellite electrical power system (EPS)

- · Power for analog circuits

- Data converters: ADCs and DACs (analog-todigital and digital-to-analog converters

- Op amps (operational amplifiers)

- Imaging sensors

- · Post DC-DC converter regulation and ripple filtering

- Radiation-hardened ultra-clean analog supply for space constrained areas

TRUMENTS Setup www.ti.com

## 2 Setup

This section describes the jumpers and connectors on the EVM as well as how to properly connect, set up, and use the TPS7H1210EVM.

# 2.1 Input/Output Connectors and Jumper Descriptions

#### 2.1.1 J1, J4 (-)V<sub>IN</sub>

Negative input power supply voltage connectors. The negative input lead and ground return lead from the input power supply should be twisted and kept as short as possible to minimize EMI transmission. Additional bulk capacitance should be added between J1 and J6 if the supply leads are greater than six inches. For example, a 47-µF electrolytic capacitor can be populated at C5 to improve the transient response of the TPS7H1210 while eliminating unwanted ringing on the input due to long wire connections. An isolated (+) power supply may be used if the (+) lead is connected to J6 (GND) and the (-) lead is connected to J1 (-V<sub>IN</sub>). J1 is provided as a bananna jack input. J4 is provided as shielded coax SMA connection.

#### 2.1.2 J6 GND

Ground-return connector for the  $V_{\text{IN}}$  input power supply.

## 2.1.3 J2, J5 (-)V<sub>OUT</sub>

Regulated (-) output voltage connectors. J2 is provided as a bananna jack connector, and J5 is provided as shielded coax SMA connection.

#### 2.1.4 J7 GND

Output ground-return connector.

#### 2.1.5 J3 EN

Output enable. To enable the regulator output, connect a jumper to short between pins 2 and 3. To disable the output, connect a jumper to short between pins 1 and 2. Leaving J3 without a jumper, will enable the regulator through the resistor divider. The resistor divider allows an external signal to driven between pin 2 and pin 1.

The resistor divider will reduce V<sub>IN</sub> applied to the EN pin to approximately 40% of V<sub>IN</sub>. For lower V<sub>IN</sub> voltages, the voltage on EN may not be sufficient to meet the V<sub>EN(+HI)</sub> minimum threshold of 2 V to ensure the regulator is enabled. In this case connect jumper between pin 2 and pin 3 to pull the EN pin to V<sub>IN</sub>.

#### 2.1.6 TP1-5 Test Points

There are five test points on the EVM. Table 2-1 shows the connection and function for each test point.

#### Table 2-1. Test Points

| TEST POINT | CONNECTION       | FUNCTION                                                                                                                                                                                |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP1        | V <sub>IN</sub>  | Provides access to the negative input voltage (V <sub>IN</sub> ).                                                                                                                       |

| TP2        | V <sub>OUT</sub> | Provides access to the negative output voltage ( $V_{OUT}$ ) prior to R1 0- $\Omega$ resistor. R1 may be removed and replaced with wire, or precision resistor for current measurement. |

| TP3        | V <sub>OUT</sub> | Provides access to negative output voltage (V <sub>OUT</sub> ).                                                                                                                         |

| TP4        | GND              | Provides access to ground plane (GND) near V <sub>IN</sub> plane.                                                                                                                       |

| TP5        | GND              | Provides access to ground plane (GND) near V <sub>OUT</sub> plane.                                                                                                                      |

www.ti.com Setup

## 2.2 Equipment Setup

1. Before connecting power to J1, turn off the input power supply after verifying that its output voltage is set to a greater absolute value than -5.5 V (-6 V recommended; -16.5 V maximum). Connect the negative voltage lead from the input power supply to -V<sub>IN</sub>, at the J1 connector of the EVM. Connect the ground lead from the input power supply to GND at the J6 connector of the EVM. If using a (+) power supply, connect the (+) lead is to J6 (GND) and the negative lead to J1 (-V<sub>IN</sub>).

- 2. Connect oscilloscope coax cables to SMA jacks J4  $V_{IN}$ , and/or J5  $V_{OUT}$  if desired. Set scope channels to high impedance.

- 3. Connect desired (≤1 A) load between the –V<sub>OUT</sub> connector J2, and the GND at connector J7.

#### WARNING

Large  $|V_{IN} - V_{OUT}|$  differentials can lead to excessive internal power dissipation when operating at higher  $I_{LOAD}$  currents. Internal power dissipation can be calculated with  $|V_{IN} - V_{OUT}| \times I_{LOAD}$ .

# 3 Operation

- 1. Enable supply. If J3 has jumper set to disable (short between pin 1 and pin 2), remove jumper to enable, or place jumper on pin 2 and pin 3. For initial operation, it is recommended that the input power supply, -V<sub>IN</sub> on J1, be set to -6 V.

- 2. Vary the load and –V<sub>IN</sub> voltage as necessary for test purposes.

Adjustable Operation Www.ti.com

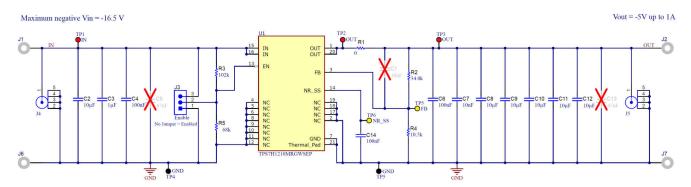

# 4 Adjustable Operation

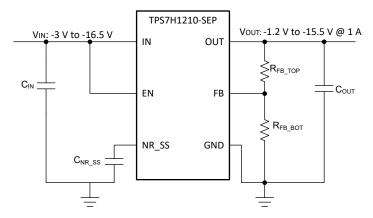

The nominal output voltage for the typical LDO circuit employing the TPS7H1210-SEP is set by two external resistors,  $R_{FB\_TOP}$  and  $R_{FB\_BOT}$ , as illustrated in Figure 4-1.  $R_{FB\_TOP}$  and  $R_{FB\_BOT}$  can be calculated for any output voltage using Equation 1 and Equation 2.  $V_{FB}$  is the Vref voltage found in the device data sheet under the Electrical Characteristics and is nominally 1.182 V.

Figure 4-1. TPS7H1210-SEP LDO Schematic Showing Adjustment Resistors

$$R_{FB\_BOT} = \frac{R_{FB\_TOP}}{\frac{V_{OUT}}{V_{FB}} - 1} \tag{1}$$

where

$$\frac{V_{OUT}}{R_{FB}} \frac{V_{OUT}}{T_{OP} + R_{FB}} \ge 5 \,\mu A \tag{2}$$

Once the resistor values have been calculated, the new resistors can be installed appropriately in the correct place using the PCB and schematic diagrams of Figure 6-1 through Figure 6-4 and Figure 7-1.

For additional information on adjustable operation, see the TPS7H1210-SEP data sheet (SBVS414).

www.ti.com Test Results

#### 5 Test Results

This section provides typical performance waveforms for the TPS7H1210EVM.

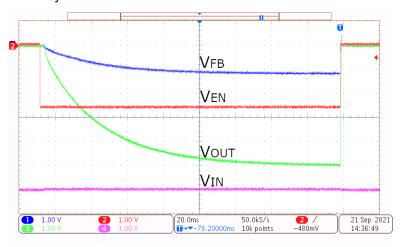

## 5.1 Enable, Disable, and Soft Start Timing

Figure 5-1 shows the enable and disable characteristic where  $-V_{IN}$  is -6 V, EN is toggled from ground to -2.4 V while the output drives a 1-A load. The waveform for  $V_{FB}$  is also shown for reference.  $C_{NR\_SS}$  of 100 nF results in a soft start time of approximately 120 ms.

Figure 5-1. Enable and Disable Timing

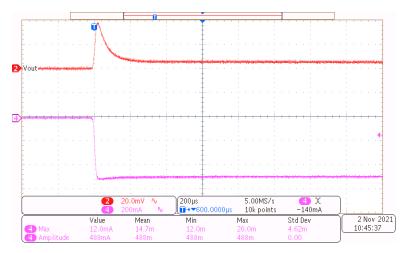

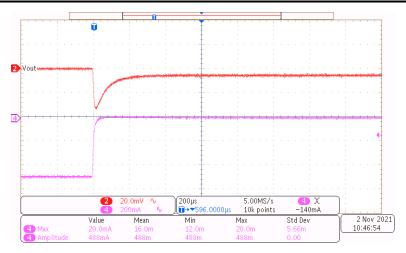

# 5.2 Output Load Transients

Figure 5-2 shows the load transient response (Chan 2  $V_{OUT}$ , red) for a load step transient from 1 mA to 500 mA (Chan 4  $V_{IN}$ , purple). The TPS7H1210EVM was operating at stock configuration with  $V_{IN}$  = -6 V,  $V_{OUT}$  = -5 V. Figure 5-2 shows the load transient from 500 mA to 1 mA.

Figure 5-2. Load Step Transient Response Rising

Test Results www.ti.com

Figure 5-3. Load Step Transient Response Falling

# **5.3 PSRR**

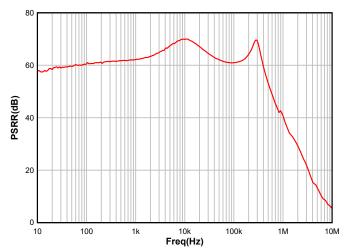

Figure 5-4 shows the typical PSRR performance of the TPS7H1210EVM operating with the following conditions:  $V_{IN}$  = -6 V,  $V_{OUT}$  = -5 V,  $I_{LOAD}$  = 1 A,  $C_{IN}$  removed, Vinjection = ±100 mV.

Figure 5-4. TPS7H1210EVM PSRR

www.ti.com Test Results

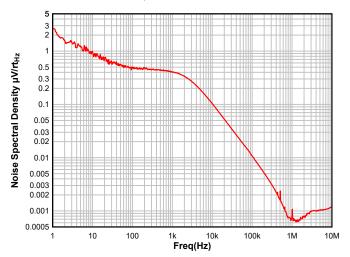

# **5.4 Noise Spectral Density**

Figure 5-5 shows the typical noise spectral density (NSD) performance of the TPS7H1210EVM operating with the following conditions:  $V_{IN} = -6 \text{ V}$ ,  $V_{OUT} = -5 \text{ V}$ ,  $I_{LOAD} = 1 \text{ A}$ .

10-Hz to 100-kHz integrated RMS noise  $V_N$  = 27.2  $\mu V_{RMS}$ .

Figure 5-5. TPS7H1210EVM NSD

# **6 Board Layout**

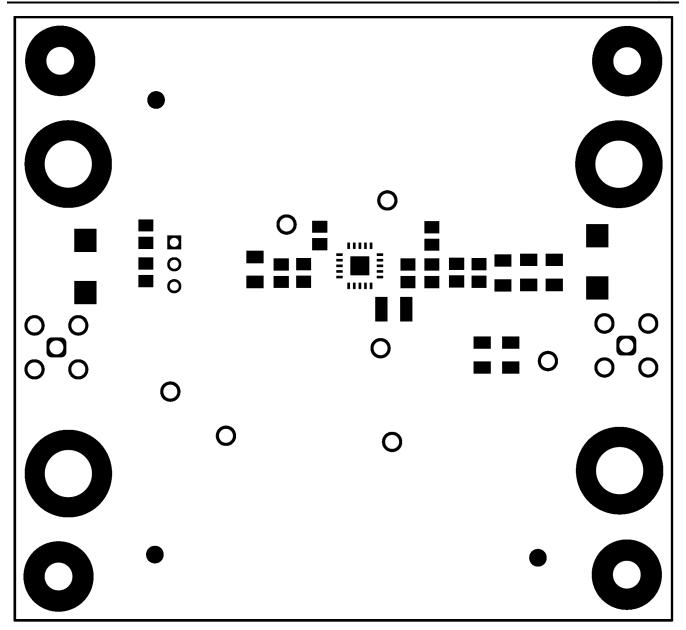

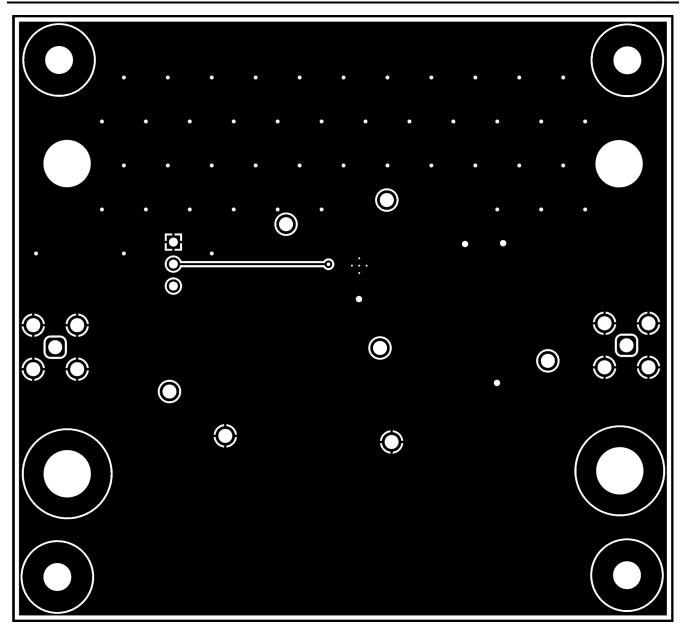

The following images represent the board design layers.

Figure 6-1. Top Overlay Silkscreen

www.ti.com Board Layout

Figure 6-2. Top Solder Mask

Board Layout www.ti.com

Figure 6-3. Top Signal Layer

www.ti.com Board Layout

Figure 6-4. Bottom Signal Layer

INSTRUMENTS Schematic and Bill of Materials www.ti.com

# 7 Schematic and Bill of Materials

Figure 7-1. TPS7H1210EVM (LP055B) Schematic

The TPS7H1210EVM schematic has a placeholder for use of a feed forward capacitance C1. Caution is encouraged when using a feed-forward (CFF) with the TPS7H1210-SEP device. While a feed-forward capacitor can provide some improvements in PSRR at certain frequencies, it also has additional risks. Specifically, a feed-forward capacitor can cause the FB pin to go to positive during shutdown, thus damaging the device. See Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator application report for additional information.

Table 7-1. TPS7H1210EVM (LP055B) Bill of Materials

| Designator                   | Qty | Value  | Description                                                    | Package-Ref                      | PartNumber           | Manufacturer                      |

|------------------------------|-----|--------|----------------------------------------------------------------|----------------------------------|----------------------|-----------------------------------|

| !PCB1                        | 1   |        | Printed Circuit Board                                          |                                  | LP055                | Any                               |

| C2, C8, C9,<br>C10, C11, C12 | 6   | 10uF   | CAP, CERM, 10 µF, 50 V,+/- 10%,<br>X7R, AEC-Q200 Grade 1, 1206 | 1206                             | CGA5L1X7R1H106K160AE | TDK                               |

| C3                           | 1   | 1uF    | CAP, CERM, 1 uF, 50 V, +/- 10%,<br>X7R, 0805                   | 805                              | C0805C105K5RACTU     | Kemet                             |

| C4, C6, C14                  | 3   | 0.1uF  | CAP, CERM, 0.1 uF, 50 V, +/- 5%, X7R, 0805                     | 805                              | C0805C104J5RACTU     | Kemet                             |

| C7                           | 1   | 0.01uF | CAP, CERM, 0.01 uF, 50 V, +/-<br>20%, X7R, 0805                | 805                              | C0805C103M5RACTU     | Kemet                             |

| H1, H2, H3, H4               | 4   |        | Machine Screw, Round, #4-40 x 1/4, Nylon, Philips panhead      | Screw                            | NY PMS 440 0025 PH   | B&F Fastener<br>Supply            |

| H5, H6, H7, H8               | 4   |        | Standoff, Hex, 0.5"L #4-40 Nylon                               | Standoff                         | 1902C                | Keystone                          |

| J1, J2, J6, J7               | 4   |        | Standard Banana Jack,<br>Uninsulated, 8.9mm                    | Keystone575-8                    | 575-8                | Keystone                          |

| J3                           | 1   |        | Header, 100mil, 3x1, Tin, TH                                   | Header, 3 PIN,<br>100mil, Tin    | PEC03SAAN            | Sullins<br>Connector<br>Solutions |

| J4, J5                       | 2   |        | SMA, 50 Ohm, Gold, TH                                          | SMA, TH                          | 32K101-400L5         | Rosenberger                       |

| R1                           | 1   | 0      | RES, 0, 1%, 0.5 W, AEC-Q200<br>Grade 0, 1210                   | 1210                             | CRCW12100000Z0EA     | Vishay-Dale                       |

| R2                           | 1   | 34.0k  | RES, 34.0 k, 1%, 0.125 W, AEC-<br>Q200 Grade 0, 0805           | 805                              | ERJ-6ENF3402V        | Panasonic                         |

| R3                           | 1   | 102k   | RES, 102 k, 1%, 0.125 W, AEC-<br>Q200 Grade 0, 0805            | 805                              | ERJ-6ENF1023V        | Panasonic                         |

| R4                           | 1   | 10.5k  | RES, 10.5 k, 1%, 0.125 W, AEC-<br>Q200 Grade 0, 0805           | 805                              | ERJ-6ENF1052V        | Panasonic                         |

| R5                           | 1   | 68k    | RES, 68 k, 5%, 0.125 W, AEC-<br>Q200 Grade 0, 0805             | 805                              | ERJ-6GEYJ683V        | Panasonic                         |

| TP1, TP2, TP3                | 3   |        | Test Point, Multipurpose, Red, TH                              | Red<br>Multipurpose<br>Testpoint | 5010                 | Keystone                          |

www.ti.com Schematic and Bill of Materials

Table 7-1. TPS7H1210EVM (LP055B) Bill of Materials (continued)

| Designator          | Qty | Value  | Description                                                            | Package-Ref                         | PartNumber       | Manufacturer         |

|---------------------|-----|--------|------------------------------------------------------------------------|-------------------------------------|------------------|----------------------|

| TP4, TP5            | 2   |        | Test Point, Multipurpose, Black,<br>TH                                 | Black<br>Multipurpose<br>Testpoint  | 5011             | Keystone             |

| TP5, TP6            | 2   |        | Test Point, Multipurpose, Yellow,<br>TH                                | Yellow<br>Multipurpose<br>Testpoint | 5014             | Keystone             |

| U1                  | 1   |        | 16.5-V, 1-A, Negative Linear<br>Regulator in Space Enhanced<br>Plastic | VQFN20                              | TPS7H1210MRGWSEP | Texas<br>Instruments |

| C1                  | 0   | 0.01uF | CAP, CERM, 0.01 uF, 50 V, +/-<br>20%, X7R, 0805                        | 805                                 | C0805C103M5RACTU | Kemet                |

| C5, C13             | 0   | 47uF   | CAP, TA, 47 uF, 35 V, +/- 20%, 0.9 ohm, AEC-Q200 Grade 1, SMD          | 7343-43                             | TAJE476M035RNJ   | AVX                  |

| FID1, FID2,<br>FID3 | 0   |        | Fiducial mark. There is nothing to buy or mount.                       | N/A                                 | N/A              | N/A                  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated