# AM62Lx Power Supply Implementation

#### Brenda Diaz

#### **ABSTRACT**

This application note describes the AM62L power supply implementation for different use cases and low power modes. The power delivery network (PDN) in this document can be used as a guide for integrating PMIC or discrete power designs into applications using the Texas Instruments AM62L Sitara Processor. Example supply and digital diagrams are provided to assist the design process. For any questions or technical support needed to assist the design process, use the TI E2E<sup>™</sup> design support forum.

### **Table of Contents**

| 1 Introduction                                                            | 3               |

|---------------------------------------------------------------------------|-----------------|

| 2 Power Management IC (PMIC) Overview                                     |                 |

| 3 Low Power Modes and Power Supply Optimization                           | 5               |

| 3.1 PDN#1: Optimized Power Design for BOM Size and Cost                   | 6               |

| 3.2 PDN#2: Optimized Power Design for Lowest Suspend Power                |                 |

| 3.3 PDN#3: Fully Flexible Power Design                                    | 11              |

| 3.4 PDN#4: Power Supply Implementation for DDR4                           | 13              |

| 4 Power-Up Sequence                                                       | 16              |

| 5 Power-Down Sequence                                                     | 17              |

| 6 Summary                                                                 | 18              |

| 7 References                                                              | 18              |

| A Appendix A: Discrete Power Implementation for PDN#1                     | 19              |

| B Revision History                                                        | 21              |

|                                                                           |                 |

| List of Figures                                                           |                 |

| Figure 2-1. TPS65214 Functional Block Diagram                             | 4               |

| Figure 3-1. AM62L PDN Optimized for BOM Size and Cost                     | 6               |

| Figure 3-2. SoC - PMIC Digital Connections for PDN#1                      |                 |

| Figure 3-3. PMIC BOM Example                                              |                 |

| Figure 3-4. AM62L PDN Optimized for Lowest Suspend Power                  |                 |

| Figure 3-5. SoC - PMIC Digital Connections for PDN#2                      |                 |

| Figure 3-6. AM62L Fully Flexible PDN                                      |                 |

| Figure 3-7. SoC - PMIC Digital Connections for PDN#3                      |                 |

| Figure 3-8. Power Supply Implementation for DDR4                          |                 |

| Figure 3-9. Digital connections for DDR4 use case                         | 14              |

| Figure 4-1. AM62L Power-Up Sequence                                       | 16              |

| Figure 5-1. AM62L Power-Down Sequence                                     | 17              |

| Figure A-1. PDN Optimized for BOM Size and Cost - Discrete Implementation | 19              |

| Figure A-2. Discrete BOM Example                                          | 20              |

| Figure A-3. Logic Implementation - Example                                | <mark>20</mark> |

|                                                                           |                 |

| List of Tables                                                            |                 |

| Table 1-1. AM62L Power Architecture Features.                             | 3               |

| Table 3-1. AM62L Power Delivery Network (PDN)                             |                 |

| Table 3-2. TPS6521401 Digital Config                                      |                 |

| Table 3-3. TPS6521402 Digital Config                                      |                 |

| Trademarks                                                                |                 |

|                                                                           |                 |

| TI E2E <sup>™</sup> is a trademark of Texas Instruments.                  |                 |

Trademarks www.ti.com

All trademarks are the property of their respective owners.

www.ti.com Introduction

#### 1 Introduction

The AM62L Arm-based processor is a low-cost, power-efficient system-on-chip (SoC) designed for a wide range of industrial and general-purpose applications. With two ARM Cortex-A53 cores, the AM62L processor provides robust computing with necessary security features such as secure boot. The device enables fast & efficient development with the scalable software development kits (SDK), open-source hardware and design tools. This SoC is designed for smart metering, EV charging, IOT gateways, industrial HMI, patient monitoring among others.

AM62L was developed with a power management architecture that enables lower power dissipation, lower BOM cost and flexible power design. This power architecture requires 4-5 external regulators to supply the main CORE (VDD\_CORE), RAM (VDDR\_CORE), DDR PHY IO (VDDS\_DDR), VDDA analog supply (can be combined with 1.8V IO with proper filtering) and 1.8V/3.3V IO supplies. Table 1-1 highlights some of the benefits of the SoC power architecture.

#### **Note**

In the event of any inconsistency between user's guide, application report, or other referenced material, the data sheet specification is the definitive sources.

#### Table 1-1. AM62L Power Architecture Features

| Power Architecture Features   | Benefits                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓ Low Power Modes             | 4 low power modes (RTC Only, RTC + IO + DDR, DeepSleep and Standby) significantly reduce power consumption and allows higher power efficiency and longer battery lifetime.                                                              |

| ✓ Active Power                | Low active power and OS Idle allows to reduce power during lower activity use cases.                                                                                                                                                    |

| ✓ CORE voltage                | Differentiated low power capability with 0.75V fixed core voltage supply supports up to 1.25GHz dual A53.                                                                                                                               |

| ✓ Voltage domain              | Single CORE voltage domain enables low cost power design and simpler software control for power management.                                                                                                                             |

| ✓ Internal dual voltage LDO   | Integrates a 3.3V LDO (SDIO) that can be switched to 1.8V to supply SD card interface and support UHS-I speed. This internal LDO allows designers to reduce BOM size and cost by eliminating the need for an external dual voltage LDO. |

| ✓ Power Supply Implementation | Flexible power sequencing and supply consolidation simplifies the PMIC or discrete power implementation and allows optimization for lower BOM size and cost.                                                                            |

| ✓ Companion PMIC              | TPS65214 is a 3.5mm x 3.5mm cost and space optimized power management IC (PMIC) developed to power the AM62L. This is integrated supervisor and sequencer allow to monitor all power rails and fully control the sequencing.            |

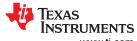

# 2 Power Management IC (PMIC) Overview

The TPS65214 PMIC contains five regulators; 3 Buck regulators and 2 Low Drop-out Regulators (LDOs). The Buck converters are capable of supporting up to 2A for Buck1, and 1A each for the remaining buck regulators. LDO1 can support a maximum output current of 300mA, and LDO2 can support a maximum output current of 500mA. Both LDOs can also be configured as load switches. With a VIN range of 2.5V to 5.5V, the PMIC can support a common 3.3V or 5V system voltage. Figure 2-1 shows a summary of the voltage and current capabilities for each of the analog resources. With an I2C interface, two GPIO pins, and three multi-function pins, the TPS65214 PMIC provides the full power package to supply the AM62L SoC and the principal peripherals.

There are different orderable part numbers (OPNs) of the TPS65214 device with unique OTP settings to support different application use cases. Each TPS65214 device is distinguished by the part number and TI\_DEV\_ID / NVM\_ID register fields. Digits #9-10 of the part number represent the default OTP configuration. For example, TPS6521401 has unique OTP settings to support the voltage and sequencing requirements of the AM62L SoC.

Figure 2-1. TPS65214 Functional Block Diagram

### 3 Low Power Modes and Power Supply Optimization

The AM62L offers the following low power modes: RTC only, RTC + IO + DDR, DeepSleep and Standby. Refer to the Power section of the *AM62L Technical Reference Manual* for a detailed description of each low power mode and the supported wakeup sources. At a high level, during *RTC only* the RTC rails (VDDS\_RTC / VDD\_RTC) stay ON and the remaining power rails are turned-off. During *RTC* + *IO* + *DDR* the main CORE (VDD\_CORE) and the 1.8V analog (VDDA) are turned-off while the remaining rails stay-ON. In contrast, when supporting DeepSleep and Standby all the external power rails stay ON. Table 3-1 shows three PDNs for different power optimization to power AM62L+LPDDR4 based on the required low power modes. This table also includes a PDN for a supply implementation with DDR4.

For applications not using low power modes: PDN#1 is recommended if the total 3.3V IO current is lower than 500mA, If total 3.3V IO current is higher than 500mA, PDN#2 is recommended.

Table 3-1. AM62L Power Delivery Network (PDN)

| Power Supply Optimization           | Memory | Supported Low Power Modes |                |           |         |  |

|-------------------------------------|--------|---------------------------|----------------|-----------|---------|--|

|                                     |        | RTC only                  | RTC + IO + DDR | DeepSleep | Standby |  |

| Lowest BOM size, cost (PDN#1) (1)   | LPDDR4 |                           |                | ✓         | ✓       |  |

| Lowest Suspend Power (PDN#2) (2)    | LPDDR4 |                           | 1              | 1         | ✓       |  |

| Fully Flexible Design (PDN#3) (2)   | LPDDR4 | 1                         | 1              | ✓         | ✓       |  |

| Supply diagram for DDR4 (PDN#4) (3) | DDR4   | 1                         | <b>✓</b>       | 1         | ✓       |  |

- (1) PDN#1 uses a custom PMIC configuration that is available upon request for high volume applications.

- (2) PDN#2 and PDN#3 use the TPS6521401 PMIC configuration.

- (3) PDN#4 uses the TPS6521402 PMIC configuration.

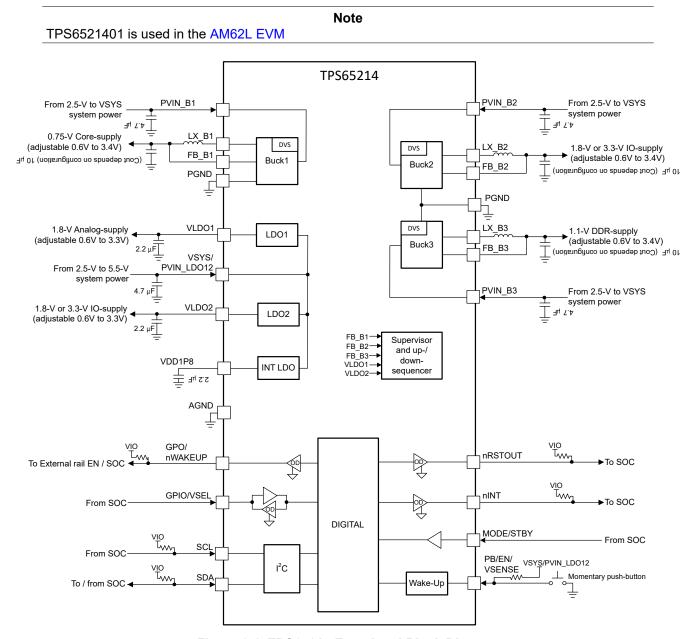

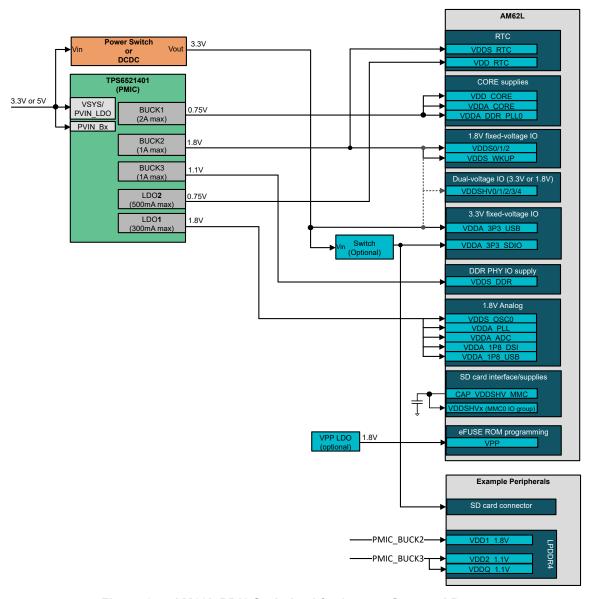

### 3.1 PDN#1: Optimized Power Design for BOM Size and Cost

The Power Delivery Network (PDN) described in this section offers a power design optimized for smaller BOM size and lower cost. The design uses a single  $3.5 \, \text{mm} \times 3.5 \, \text{mm}$  Power Management IC (PMIC) to supply all the SoC power domains. Alternatively, discrete components can be used to implement the power design. Figure 3-1 shows the PMIC implementation. This PDNs can be used for applications not using *RTC only* and *RTC* + *IO* + *DDR* low power modes.

### Highlights:

- Estimated BOM size: 36.97mm<sup>2</sup> (does not include PCB clearance).

- All SoC voltage domains are supplied with a single PMIC if total current on 3.3V IO (including AM62L + peripherals) is lower than 500mA.

- If total current on 3.3V IO (including AM62L + peripherals) is higher than 500mA, refer to Section 3.2

- When using 3.3V input supply (lowest power consumption), PMIC LDO2 is configured as 3.3V load-switch.

- When using 4V-5V input supply, PMIC LDO2 is configured as 3.3V LDO.

Figure 3-1. AM62L PDN Optimized for BOM Size and Cost

The power-switch connected to VDDA\_3P3\_SDIO is optional and only needed if the application uses SD card. The VPP 1.8V LDO is optional and only needed if on-board eFuse programming is required. Refer to Appendix A for an example discrete implementation.

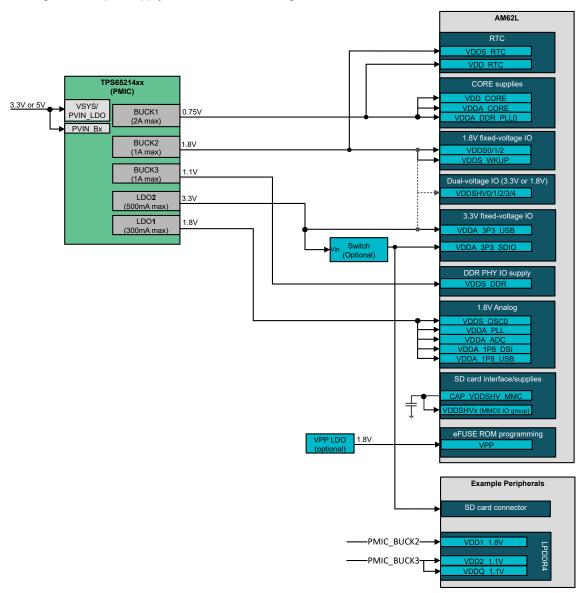

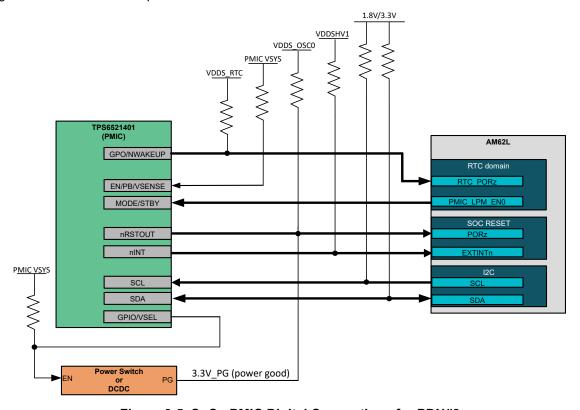

Figure 3-2 shows the digital connections between SoC and PMIC for PDN#1. This image also shows the digital pins that require external pull-up resistors. The PMIC enable pin (EN/PB/VSENSE) can be driven with the power-good signal of the pre-regulator. Alternatively, this signal can be pulled up to PMIC\_VSYS if the pre-regulator does not integrate a power-good signal. The PMIC nRSTOUT drives the RTC power-on reset (RTC\_PORz) and SoC main reset (PORz). This is allowed when not supporting *RTC only* and *RTC + IO + DDR* low power modes. The PMIC\_LPM\_EN0 drives the PMIC MODE/STBY pin to switch the DCDC switching mode from forced-PWM to auto-PFM and to improve power efficiency during DeepSleep and Standby/OS Idle low power modes. This is optional and require the PMIC MODE/STBY pin to be configured as "MODE".

Figure 3-2. SoC - PMIC Digital Connections for PDN#1

#### Note

PMIC\_LPM\_EN0 does not require an external pull-up resistor; The SoC has an internal pullup resistor that drives the signal high if VDDS\_RTC is powered. PORz is 3.3V tolerant and the external pull-up resistor can be connected to a 1.8V supply or 3.3V supply as long as VDDS\_OSC0 is powered.

| AM62L              | Powe       | r Supply            | Qty | Example component          | Component Value | Length (mm) | Width (mm) | Area (mm2) |

|--------------------|------------|---------------------|-----|----------------------------|-----------------|-------------|------------|------------|

|                    |            | PMIC IC package     | 1   | TPS65214                   | N/A             | 3.5         | 3.5        | 12.25      |

| NA                 |            | VSYS/PVIN_LDO       | 1   | C1608X7S1A475K080AC        | 4.7uF           | 1.6         | 0.8        | 1.28       |

|                    |            | VDD1P8 - Cout       | 1   | C1005X7S1A225K050BC        | 2.2uF           | 1           | 0.5        | 0.5        |

| VDD CORE           |            | BUCK1-L             | 1   | TFM201208BLE-R47MTCF       | 0.47μΗ          | 2           | 1.2        | 2.4        |

| _                  |            | BUCK1-Cin           | 1   | C1608X7S1A475K080AC        | 4.7μF           | 1.6         | 0.8        | 1.28       |

| VDD_RTC            |            | BUCK1-Cout          | 2   | GRM21BZ71A226ME15L         | 22μF            | 2           | 1.25       | 5          |

|                    |            | BUCK3-L             | 1   | TFM201208BLE-R47MTCF       | 0.47μΗ          | 2           | 1.2        | 2.4        |

| VDDS_DDR           |            | BUCK3-Cin           | 1   | C1608X7S1A475K080AC        | 4.7μF           | 1.6         | 0.8        | 1.28       |

|                    | PMIC rails | BUCK3-Cout          | 1   | GRM21BZ71A226ME15L         | 22μF            | 2           | 1.25       | 2.5        |

|                    |            | BUCK2-L             | 1   | TFM201208BLE-R47MTCF       | 0.47μΗ          | 2           | 1.2        | 2.4        |

| 1.8V IO            |            | BUCK2-Cin           | 1   | C1608X7S1A475K080AC        | 4.7μF           | 1.6         | 0.8        | 1.28       |

|                    |            | BUCK2-Cout          | 1   | GRM21BZ71A226ME15L         | 22μF            | 2           | 1.25       | 2.5        |

| 3.3V IO            |            | LDO1-Cin            | 0   | shares Cin with VSYS       | NA              | 0           | 0          | 0          |

| 3.30 10            |            | LDO1-Cout           | 1   | C1005X7S1A225K050BC        | 2.2μF           | 1           | 0.5        | 0.5        |

| VDDA (1.8V analog) |            | LDO2-Cin            | 0   | shares Cin with VSYS       | NA              | 0           | 0          | 0          |

|                    |            | LDO2-Cout           | 1   | C1005X7S1A225K050BC        | 2.2uF           | 1           | 0.5        | 0.5        |

| Resistors          |            | Digital Pull-up Res | 5   | Example: 0201 10K pull-ups | NA              | 0.6         | 0.3        | 0.9        |

|                    |            |                     |     |                            |                 |             | Total Size | 36.97      |

Figure 3-3. PMIC BOM Example

### 3.2 PDN#2: Optimized Power Design for Lowest Suspend Power

The Power Delivery Network (PDN) described in this section is optimized for the lowest suspend power and supports all low power modes except *RTC only* mode. The PDN uses a 3.5mm x 3.5mm PMIC and an external 3.3V discrete regulator to supply all the SoC power domains. This PDN is recommended for applications using *RTC* + *IO* + *DDR* low power mode or requiring more than 500mA current on the 3.3V IO. This PDN is designed to turn-OFF VDD\_CORE and VDDA when entering *RTC* + *IO* + *DDR* low power mode to reduce power consumption. Figure 3-4 shows the PMIC implementation using TPS6521401 configuration.

#### **Highlights:**

- Uses TPS6521401 PMIC. This PMIC configuration is used in the AM62L EVM. Hardware design files available.

- Estimated BOM size for 3.3V input supply (PMIC + 3.3V power-switch): 41.69mm<sup>2</sup> (does not include PCB clearance). Power-switch example: TPS22954.

- Estimated BOM size for 4V-5V input supply (PMIC + 3.3V Buck): 58.68mm<sup>2</sup> (does not include PCB clearance). Buck example: TPS62A01.

- External 3.3V discrete is scalable based on the total current needed for 3.3V IO (including SoC + peripherals).

Figure 3-4. AM62L PDN Optimized for Lowest Suspend Power

The power-switch connected to VDDA\_3P3\_SDIO is optional and only needed if the application uses SD card. The VPP 1.8V LDO is optional and only needed if on-board eFuse programming is required.

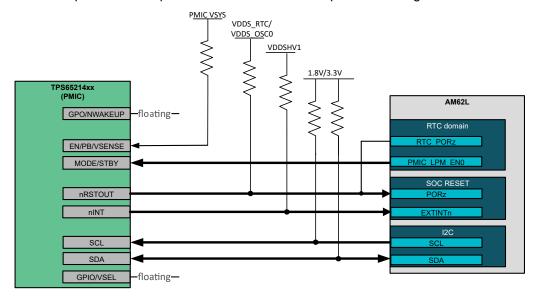

Figure 3-5 shows the digital connections between SoC and PMIC for PDN#2. The image also shows the digital signals that require external pull-up resistors. The PMIC enable pin (EN/PB/VSENSE) can be driven with the power-good signal of the pre-regulator. Alternatively, this signal can be pulled up to PMIC\_VSYS if the pre-regulator does not integrate a power-good signal. The PMIC nRSTOUT and the power-good signal of the 3.3V IO drives the main SoC reset (PORz). PMIC GPO is configured to act as the power-good signal of the RTC rails (BUCK2 and LDO2) and drives the RTC power-on reset (RTC\_PORz). The PMIC\_LPM\_EN0 drives the PMIC MODE/STBY pin to pull PORz low and turn-off VDD\_CORE (BUCK1) as well as VDDA (LDO1) when entering "RTC + IO + DDR" low power modes.

Figure 3-5. SoC - PMIC Digital Connections for PDN#2

### Note

PMIC\_LPM\_EN0 does not require an external pull-up resistor; The SoC has an internal pullup resistor that drives the signal high if VDDS\_RTC is powered. PORz is 3.3V tolerant and the external pull-up resistor can be connected to a 1.8V supply or 3.3V supply as long as VDDS\_OSC0 is powered.

### Table 3-2. TPS6521401 Digital Config

| Tubic o E. 11 Cool 1401 Digital Coming |                             |                                                                                                                                                                                                    |  |  |  |  |

|----------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        | OTP Config                  | Polarity                                                                                                                                                                                           |  |  |  |  |

| EN/PB/VSENSE                           | Configured as <i>Enable</i> | High: PMIC executes power-on sequence.     Low: PMIC executes power-down sequence.                                                                                                                 |  |  |  |  |

| MODE/STBY                              | Mode and Standby            | High: PMIC in Active state. All rails enabled. Bucks operate in forced-PWM.  Low: PMIC in Standby state. Buck1 and LDO1 are turned-OFF. Bucks operate in auto-PFM.                                 |  |  |  |  |

| GPIO/nWAKEUP                           | Open-drain GPO              | Configured to act as the <i>power-good</i> signal of Buck2 and LDO2. This digital pin drives RTC_PORz and stays high/Z when PMIC enters Standby state to support the AM62L RTC+DDR low power mode. |  |  |  |  |

| GPIO/VSEL                              | Open-drain GPO              | Configured to enable/disable external 3.3V discrete device.                                                                                                                                        |  |  |  |  |

#### Note

Refer to the *TPS6521401 Technical Reference Manual* to access the full list of default PMIC OTP register settings.

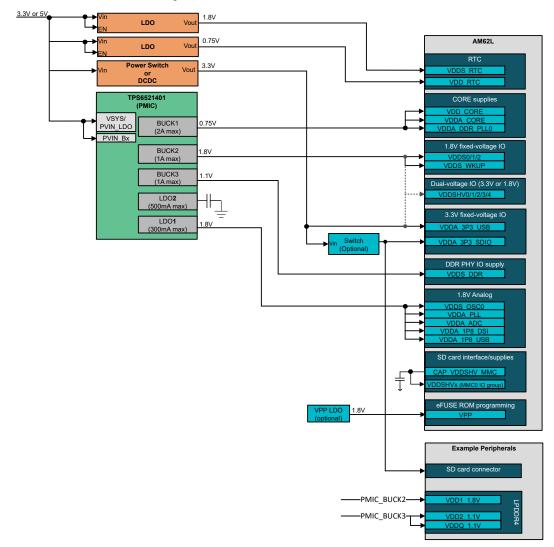

### 3.3 PDN#3: Fully Flexible Power Design

The Power Delivery Network (PDN) described in this section offers a flexible PMIC + discrete power design that allows supporting all the SoC low power modes. This PDN supports *RTC only* low power mode by isolating VDDS\_RTC (1.8V) and VDD\_RTC (0.75V) from the remaining power rails. Supplying the RTC domain with always-ON discrete devices allows to significantly reduce power consumption during *RTC only* low power mode by turning-OFF the entire PMIC and the external 3.3V discrete while only keeping the RTC rails ON. When entering *RTC only* low power mode, the AM62L PMIC\_LPM\_EN signal drives the PMIC enable pin low. Figure 3-6 shows the PMIC + discrete power implementation.

### Highlights:

- This PDN can be implemented with the TPS6521401 PMIC (PMIC OTP configuration used in the AM62L EVM).

- Supports all AM62L low power modes.

- BOM size is highly dependent on the selected discrete devices for the RTC rails and the 3.3 IO.

- When using 3.3V input supply (lower power consumption), external 3.3V power switch is used. Example IC: TPS22954.

- When using 4V-5V input supply, external 3.3V DCDC is used. Example IC: TPS62A01.

- External 3.3V discrete current rating is scalable based on the total current needed for 3.3V IO.

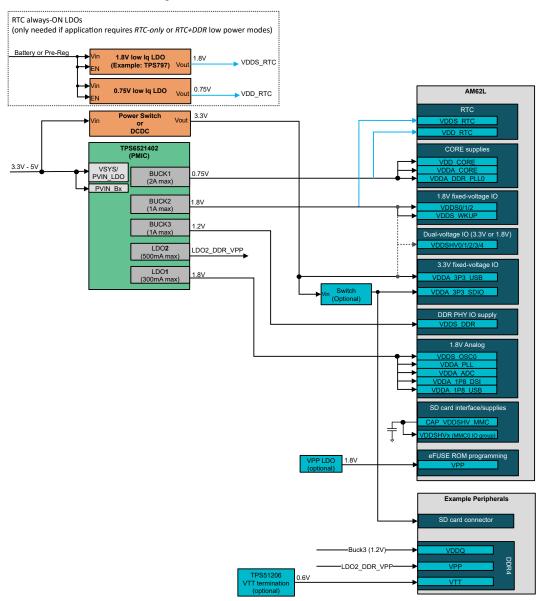

Figure 3-6. AM62L Fully Flexible PDN

The power-switch connected to VDDA\_3P3\_SDIO is optional and only needed if the application uses SD card. The VPP 1.8V LDO is optional and only needed if on-board eFuse programming is required.

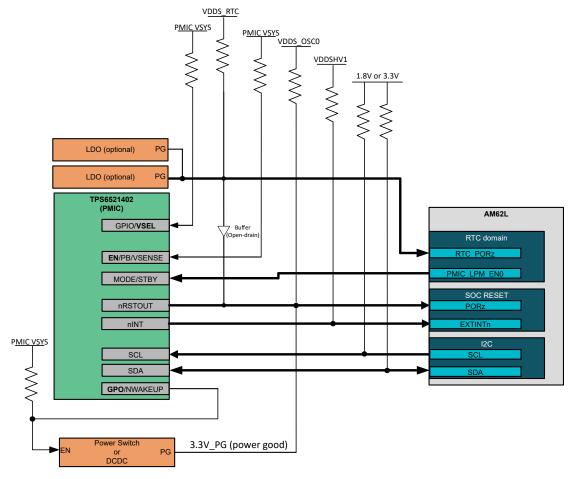

Figure 3-7 shows the digital connections between SoC and PMIC for PDN#3. The image also shows the digital signals that require external pull-up resistors. The SoC PMIC\_LPM\_EN0 drives the PMIC enable pin (EN/PB/VSENSE) to turn-OFF the PMIC when entering *RTC only* low power mode. The combined power-good signals of the discrete LDOs that supply the RTC rails drive RTC\_PORz. Additionally, an open-drain buffer between the two power-on resets allows to pull the PORz low and keep the SoC in reset if a fault is detected on the external discrete LDOs. The PMIC nRSTOUT, the power-good signal of the 3.3V IO and the output of the open-drain buffer drive the main SoC reset (PORz).

Figure 3-7. SoC - PMIC Digital Connections for PDN#3

#### Note

PMIC\_LPM\_EN0 does not require an external pull-up resistor; The SoC has an internal pullup resistor that drives the signal high if VDDS\_RTC is powered. PORz is 3.3V tolerant and the external pull-up resistor can be connected to a 1.8V supply or 3.3V supply as long as VDDS\_OSC0 is powered.

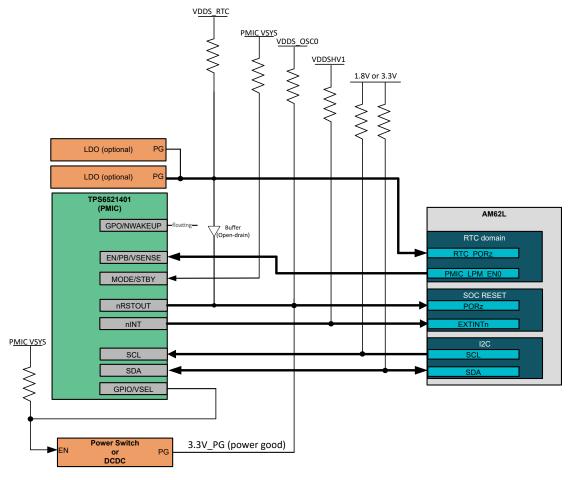

### 3.4 PDN#4: Power Supply Implementation for DDR4

The Power Delivery Network (PDN) described in this section supports AM62L + DDR4. If *RTC-only* or *RTC+IO+DDR* low power modes are not requires, VDD\_RTC can be tied to VDD\_CORE (Buck1) and VDDS\_RTC can be tied to the 1.8V IO (Buck2). Figure 3-8 shows the PMIC implementation using TPS6521402 configuration.

### Highlights:

- Uses TPS6521402 PMIC.

- The two external 1.8V/0.75V discrete LDOs are only needed if the application uses RTC-only or RTC+IO+DDR low power modes.

- BOM size is highly dependent on the selected discrete devices for the RTC rails and the 3.3 IO.

- When using 3.3V input supply (lower power consumption), external 3.3V power switch is used. Example IC: TPS22954.

- When using 4V-5V input supply, external 3.3V DCDC is used. Example IC: TPS62A01.

- External 3.3V discrete current rating is scalable based on the total current needed for 3.3V IO.

Figure 3-8. Power Supply Implementation for DDR4

The power-switch connected to VDDA\_3P3\_SDIO is optional and only needed if the application uses SD card. The VPP 1.8V LDO is optional and only needed if on-board eFuse programming is required. If the application uses low power modes that require turning-OFF external supplies (i.e. RTC-only or RTC+DDR low power modes), VDDS\_RTC and VDD\_RTC must be supplied by discrete always-ON regulators. This is a requirement for the AM62L + DDR4 PDN).

Figure 3-9 shows the digital connections between SoC and PMIC along with the required pull-up resistors. The SoC PMIC\_LPM\_EN0 drives the PMIC enable pin (EN/PB/VSENSE) when supporting *RTC-only* low power mode. Otherwise, this signal drives the PMIC MODE/STBY pin.

Figure 3-9. Digital connections for DDR4 use case

### Table 3-3. TPS6521402 Digital Config

|              | OTD Confin                  | Palacito.                                                                                          |

|--------------|-----------------------------|----------------------------------------------------------------------------------------------------|

|              | OTP Config                  | Polarity                                                                                           |

| EN/PB/VSENSE | Configured as <i>Enable</i> | High: PMIC executes power-on sequence.                                                             |

|              |                             | Low: PMIC executes power-down sequence.                                                            |

| MODE/STBY    | Mode and Standby            | High: PMIC in Active state. All rails enabled. Bucks operate in forced-PWM.                        |

|              |                             | Low: PMIC in Standby state. Buck1 and LDO1 are turned-OFF. Bucks operate in auto-PFM.              |

| GPIO/nWAKEUP | Open-drain GPO              | Configured to enable/disable external 3.3V discrete device.                                        |

| GPIO/VSEL    | Open-drain GPO              | This pin is configured to set the voltage on BUCK3 and requires a pull-up to output 1.2V for DDR4. |

|              |                             | DDR4.                                                                                              |

#### Note

Refer to the *TPS6521402 Technical Reference Manual* to access the full list of default PMIC OTP register settings.

# 4 Power-Up Sequence

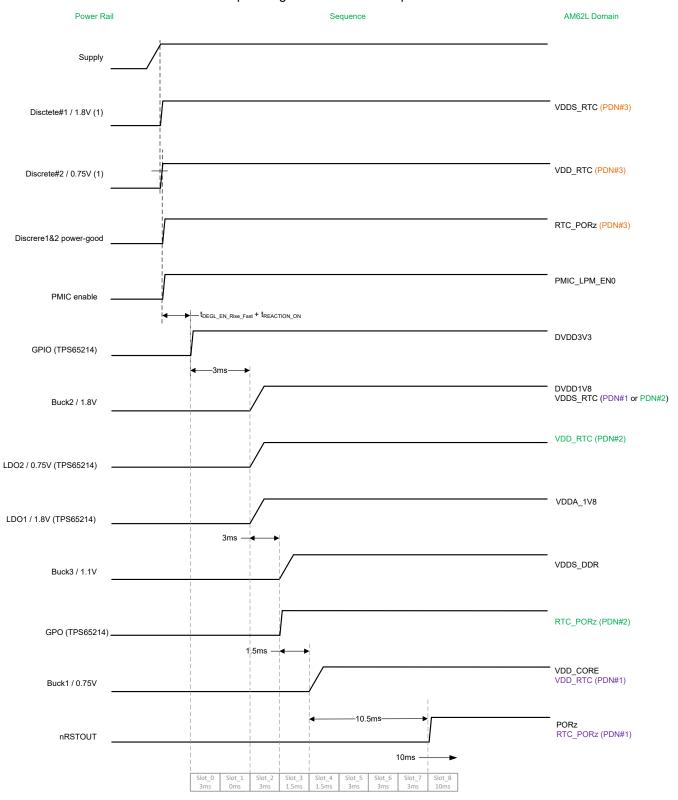

Figure 4-1 shows the power-up sequencing using the TPS6521401 OTP configuration as a reference. Refer to the AM62L data sheet for a detailed sequencing waveforms and requirements.

Figure 4-1. AM62L Power-Up Sequence

# **5 Power-Down Sequence**

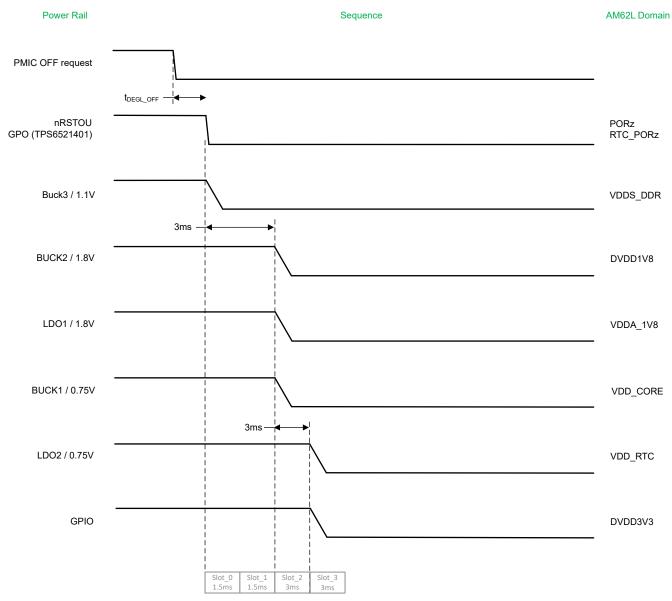

Figure 5-1 shows the power-down sequencing using the TPS6521401 OTP configuration as a reference. This power-down sequence do not cover the SoC sequencing from Active to Low Power Modes. The diagram only represents the power-down sequence when an OFF request is sent to the PMIC by hardware (pulling the enable pin low) or by software (I2C OFF request). Refer to the AM62L data sheet for a detailed sequencing waveforms and requirements.

Figure 5-1. AM62L Power-Down Sequence

Summary Www.ti.com

# **6 Summary**

The AM62L power architecture was developed with features that allow designers to reduce power consumption as well as BOM area and cost. The three power delivery network (PDNs) described in this application note show examples of how the power design can be optimized to meet system level requirements that include lowering BOM area, cost and power consumption during low activity.

#### 7 References

- Texas Instruments, *AM62Lx Sitara™ Processors*, data sheet.

- Texas Instruments, AM62L Technical Reference Manual, technical reference manual.

- Texas Instruments, TPS65214 Integrated Power Management IC Processors, data sheet.

- Texas Instruments, TPS6521401 Technical Reference Manual, technical reference manual.

- Texas Instruments, TPS6521402 Technical Reference Manual, technical reference manual.

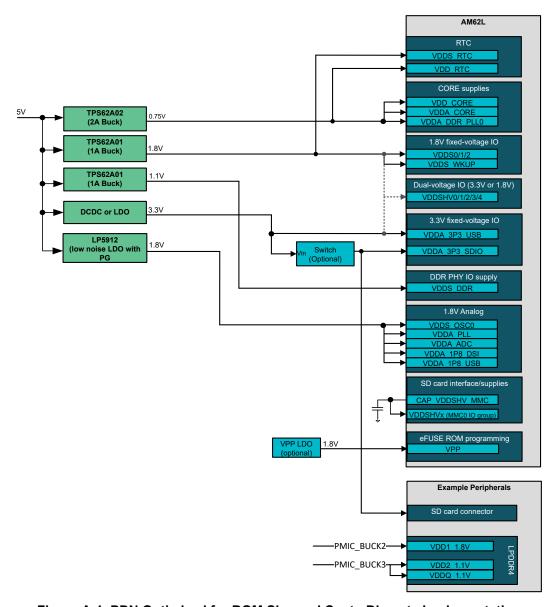

### A Appendix A: Discrete Power Implementation for PDN#1

This section describes the discrete power implementation for PDN#1. The Optimized Power Solution for BOM size and cost can also be implemented using discrete components with attributes equivalent to the devices listed below. Figure A-1 shows an example supply diagram for a 5V input supply and LPDDR4 use case.

- VDD\_CORE (0.75V): TPS62A02

- VDDS\_DDR (1.1V): TPS62A01

- VDDSHV (3.3V IO / 1.8V IO)

- if total current > 500mA: TPS62A01 (DCDC)

- if total current < 500mA: TPS74501 (LDO)</li>

- VDDA (1.8V analog): LP5912 (low noise LDO)

#### **Note**

This discrete PDN is an example supply implementation and has not been tested or validated by TI.

Figure A-1. PDN Optimized for BOM Size and Cost - Discrete Implementation

The power-switch connected to VDDA\_3P3\_SDIO is optional and only needed if the application uses SD card. The VPP 1.8V LDO is optional and only needed if on-board eFuse programming is required.

| AM62L               | Discrete Power | Qty | Example component         | Component Value   | Length (mm) | Width (mm) | Area (mm2) |

|---------------------|----------------|-----|---------------------------|-------------------|-------------|------------|------------|

|                     | Buck IC        | 1   | TPS62A02DRLR              | 2A Buck           | 1.6         | 1.6        | 2.56       |

| VDD CORE            | BUCK1-L        | 1   | XGL3520-102MEC            | 1.0uH             | 3.5         | 3.2        | 11.2       |

| VDD_COKE<br>VDD_RTC | BUCK1-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5        |

| VDD_KTC             | BUCK1-Cout     | 2   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 5          |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84       |

|                     | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56       |

|                     | BUCK3-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2       |

| VDDS_DDR            | BUCK3-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5        |

|                     | BUCK3-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5        |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84       |

|                     | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56       |

|                     | BUCK2-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2       |

| 1.8V IO             | BUCK2-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5        |

|                     | BUCK2-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5        |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84       |

|                     | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56       |

|                     | BUCK2-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2       |

| 3.3V IO             | BUCK2-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5        |

|                     | BUCK2-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5        |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84       |

|                     | IC             | 1   | LP5912                    | low noise LDO     | 2           | 2          | 4          |

| VDDA (1.8V analog)  | LDO - Cin      | 1   | GRT033C81A105ME13D        | 1uF               | 0.6         | 0.3        | 0.18       |

|                     | LDO - Cout     | 1   | GRT033C81A105ME13D        | 1uF               | 0.6         | 0.3        | 0.18       |

|                     |                |     |                           |                   |             | Total Size | 97.26      |

Figure A-2. Discrete BOM Example

A proper logic implementation is required to meet the SoC sequencing requirements and reset architecture. Figure A-3 shows an example using LM3380 sequencer and a 6 channel open-drain buffer. The connections highlighted in orange represent the power-good signals of the devices that supply the SoC rails and the system power.

Figure A-3. Logic Implementation - Example

www.ti.com Revision History

# **9 Revision History**

| Changes from Revision A (September 2025) to Revision B (October 2025)                          | Page |

|------------------------------------------------------------------------------------------------|------|

| Added power supply implementation to support DDR4                                              | 5    |

| Fixed link to TPS6521401 TRM                                                                   |      |

| Changes from Revision * (March 2025) to Revision A (September 2025)                            | Page |

| Updated the numbering format for tables, figures, and cross-references throughout the document | 1    |

| Added "x" to device in title to include device family                                          | 1    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated