# ESR, Stability, and the LDO Regulator

Jeff Falin, John Cummings

Linear Power

### **ABSTRACT**

Choosing an output capacitor for LDO  $_{\rm regulators}$  with PNP or PMOS pass element can be difficult due to specific ESR requirements. This application report explains how ESR impacts stability and how to determine whether or not the regulator is stable.

|   | Contents                                                              |   |

|---|-----------------------------------------------------------------------|---|

| 1 | Introduction                                                          |   |

| 2 | Conclusion                                                            | 6 |

|   | List of Figures                                                       |   |

| 1 | Open Loop Response of Typical PMOS or PNP LDO Regulator               | 2 |

| 2 | Typical ESR vs Output Current                                         | 2 |

| 3 | Load Transient Setup                                                  | 3 |

| 4 | TPS76050 Load Transient With 2.2-μF Ceramic Capacitor                 | 4 |

| 5 | TPS76050 Load Transient With 2.2-μF Ceramic Capacitor and 1-Ω ESR     | 5 |

| 6 | Load Transient (0.5 A) With 1-μF Output Capacitor                     | 5 |

| 7 | TPS7A26 Load Transient Response With a 100-µF Capacitor at the Output | 6 |

## **Trademarks**

All trademarks are the property of their respective owners.

## 1 Introduction

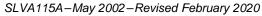

As the typical PMOS or PNP open loop gain plot of Figure 1 shows, there are three important poles in a PMOS or PNP pass element based LDO regulator. The dominant pole, P(DOM), is set in the error amplifier of the regulator. The load pole, P(LOAD), is formed by the output capacitor and load and therefore varies with load current. The pass device pole, P(PASS), is formed by the parasitic capacitance of the pass element. In order for any negative feedback system to be stable, the open loop gain of the system must be below 0 dB when the phase is 360° (180° of the fed-back signal plus the 180° from the inverting input of the error amplifier). Stated another way, the system must have sufficient phase margin, that is,, the amount of phase shift remaining until 360° degree when the gain is at 0 dB. Since each pole contributes 90° of phase shift and 20 dB/decade (or –1) roll off in gain, a three-pole, high gain system requires compensation in order to be stable. A regulator is unconditionally stable (that is, has sufficient phase margin) if the open loop gain curve rolls off at 20 dB/decade (that is, like a single pole system) before crosses 0 dB. The most common method of compensation is to insert a zero in the system to cancel the phase shift and roll off of one of the poles. Since an LDO already requires an output capacitor for normal operation, using the ESR of the output capacitor is typically the simplest and least expensive method for generating this zero, see f<sub>Z(ESR)</sub> in Figure 1.

Introduction www.ti.com

Figure 1. Open Loop Response of Typical PMOS or PNP LDO Regulator

The challenge is choosing a capacitor with the correct amount of ESR. The ESR must be high enough to lower the  $f_{Z(ESR)}$  frequency so that the gain slope is -20 dB/decade instead of -40 dB/decade (-2) when it crosses 0 dB, but low enough so that the  $f_{Z(ESR)}$  frequency is high enough for the gain to be below 0 dB before  $P_{(PASS)}$ .

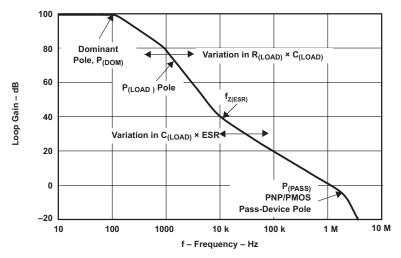

In TI's older regulator data sheets that were designed when tantalum or high-ESR capacitors were more common, a minimum capacitor value is specified and an ESR vs output current for that output capacitor (and usually another capacitor) is provided. Figure 2 shows a typical curve for the TPS76050 device.

**NOTE:** The ESR used in these plots is the minimum ESR of the capacitor as ESR does vary over frequency.

Figure 2. Typical ESR vs Output Current

www.ti.com Introduction

The curve of this device requires that, for the minimum 2.2- $\mu$ F of output capacitance, the ESR must be between 0.1  $\Omega$  and 20  $\Omega$ . Few capacitors have more than 2  $\Omega$  of ESR, so the upper limit on the ESR can usually be ignored. The lower limit actually sets the maximum value for the  $f_{Z(ESR)}$ . For the case of 2.2- $\mu$ F capacitor referenced in Figure 2, use Equation 1 to calculate the maximum value:

$$f_{Z(ESR)} = 1/(2 \times \pi \times R_{ESR} \times C_{OUT}) = 72.3 \text{ kHz}$$

where

•  $R_{ESR}$  is 0.1  $\Omega$ •  $C_{OUT}$  is 2.2  $\mu F$

For an older LDO which depended on higer ESR for stability like the TPS760 device, a capacitance and ESR product larger than  $0.1~\Omega \times 2.2 \times 10^{-6} F = 2.2 \times 10^{-7}~\Omega F$  (but less than  $20 \times 2.2 \times 10^{-6}~\Omega F = 4.4 \times 10^{-5}~\Omega F$ ) is stable, as long as the capacitance is above the minimum required capacitance value.

The TPS760 was designed when tantalum capacitors were common and 1.1 mA was considered low  $I_Q$ . For newer LDOs like the TPS7A25 device which have been designed to be optimized with low ESR or ceramic capacitors, there is no need to be concerned about ESR unless you wish to use very large capacitors for hold up.

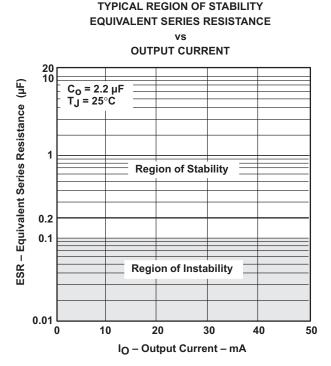

Performing a load transient test and observing the amount of ringing on the output is the best way to determine if the capacitor selected is stable. Figure 3 shows a test setup for a load transient test using a MOSFET switch and function generator. This setup is preferable to most electronic loads because the simulated transient is much faster.

Figure 3. Load Transient Setup

Introduction www.ti.com

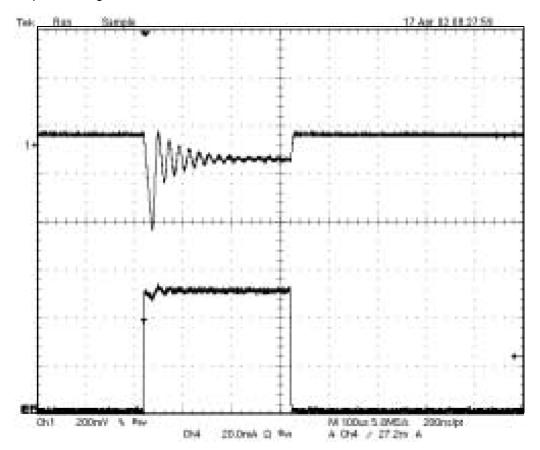

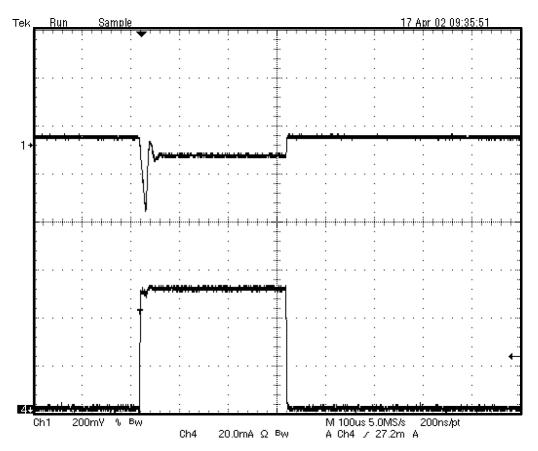

Figure 4 shows the measured results using a TPS76050 device with a 2.2- $\mu$ F ceramic (low ESR) capacitor. Figure 5 shows the measured results of a TPS76050 device with a 2.2- $\mu$ F and a 1- $\Omega$  series resistor. The results in Figure 4 show multiple oscillations or rings after the initial spike, indicating instability, while the results in Figure 5 shows a stable load transient. Typically, four rings or less indicate sufficient phase margin for the device to be stable.

Figure 4. TPS76050 Load Transient With 2.2-μF Ceramic Capacitor

www.ti.com Introduction

Figure 5. TPS76050 Load Transient With 2.2- $\mu$ F Ceramic Capacitor and 1- $\Omega$  ESR

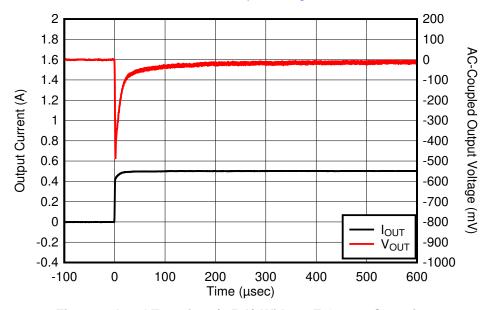

Comparing to the TPS7A25 device which is stable with a minimum of 1.0-µF ceramic capacitor with no additional ESR, there are no oscillations at the output as Figure 6 shows.

Figure 6. Load Transient (0.5 A) With 1-μF Output Capacitor

Conclusion www.ti.com

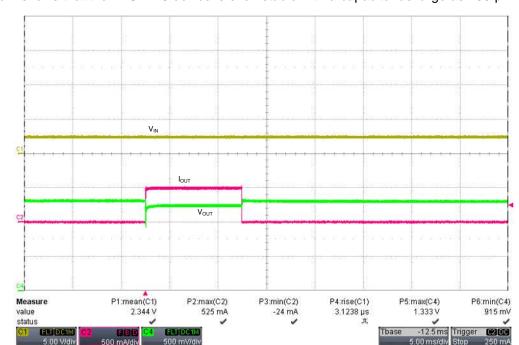

Figure 7 shows that the TPS7A26 device is even stable with a capacitor as large as 100 μF.

Figure 7. TPS7A26 Load Transient Response With a 100-µF Capacitor at the Output

# 2 Conclusion

When designing with older linear regulators, ESR is very important to consider when selecting the output capacitor. As the ESR is a function of frequency, the minimum ESR is used in simulations. Newer LDOs like the TPS7A26 device are inherently ceramic capacitor stable which helps to improve cost, size, and performance in the application.

Post ESR and stability questions to TI's E2E Community.

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (May 2002) to A Revision |                                                                                                                                                                           | Page |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •                                              | Deleted TPS7A25 capability and removed the Example Output Capacitance vs ESR and General Shape of an Imperourve for a Capacitor images.                                   |      |

| •                                              | Added Load Transient (0.5 A) With 1-μF Output Capacitor image.  Added TPS7A26 Load Transient Response With a 100-μF Capacitor at the Output image.  Added the Conclusion. | 6    |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated