# Functional Safety Manual for MSPM0Lx22x-Q1

Functional Safety Information

Literature Number: SFFS948 MAY 2025

# Table of Contents

# TEXAS INSTRUMENTS

| 1 Introduction                                                                                                                    | 5  |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 2 MSPM0Lx22x-Q1 Hardware Component Functional Safety Capability                                                                   | 6  |

| 3 Development Process for Management of Systematic Faults                                                                         |    |

| 3.1 TI New-Product Development Process                                                                                            |    |

| 3.2 TI Functional Safety Development Process                                                                                      | 8  |

| 4 MSPM0Lx22x-Q1 Component Overview                                                                                                | 9  |

| 4.1 Targeted Applications                                                                                                         | 10 |

| 4.2 Hardware Component Functional Safety Concept                                                                                  | 10 |

| 4.3 Functional Safety Constraints and Assumptions                                                                                 | 10 |

| 5 Description of Hardware Component Parts                                                                                         |    |

| 5.1 ADC                                                                                                                           | 13 |

| 5.2 Comparator                                                                                                                    |    |

| 5.3 CPU                                                                                                                           |    |

| 5.4 RAM                                                                                                                           |    |

| 5.5 FLASH                                                                                                                         |    |

| 5.6 GPIO                                                                                                                          |    |

| 5.7 DMA                                                                                                                           |    |

| 5.8 SPI                                                                                                                           |    |

| 5.9 I2C                                                                                                                           |    |

| 5.10 UART                                                                                                                         |    |

| 5.11 Timers (TIMx)                                                                                                                |    |

| 5.12 Power Management Unit (PMU)                                                                                                  |    |

| 5.13 Clock Module (CKM)                                                                                                           |    |

| 5.14 Events                                                                                                                       |    |

| 5.15 IOMUX                                                                                                                        |    |

| 5.16 VREF                                                                                                                         |    |

| 5.17 WWDT and IWDT                                                                                                                |    |

| 5.18 CRC                                                                                                                          |    |

| 6 MSPM0Lx22x-Q1 Management of Random Faults                                                                                       |    |

| 6.1 Fault Reporting                                                                                                               |    |

| 6.2 Functional Safety Mechanism Categories                                                                                        |    |

| 6.3 Description of Functional Safety Mechanisms.                                                                                  |    |

| A Summary of Recommended Functional Safety Mechanism Usage                                                                        |    |

| B Distributed Developments.<br>B.1 How the Functional Safety Lifecycle Applies to TI Functional Safety Products                   |    |

| B.1 How the Functional Salety Lifecycle Applies to 11 Functional Salety Products<br>B.2 Activities Performed by Texas Instruments |    |

| B.2 Activities Performed by Texas Instruments.                                                                                    |    |

| C Revision History                                                                                                                |    |

|                                                                                                                                   |    |

# List of Figures

| Figure 3-1. TI New-Product Development Process | . 7 |

|------------------------------------------------|-----|

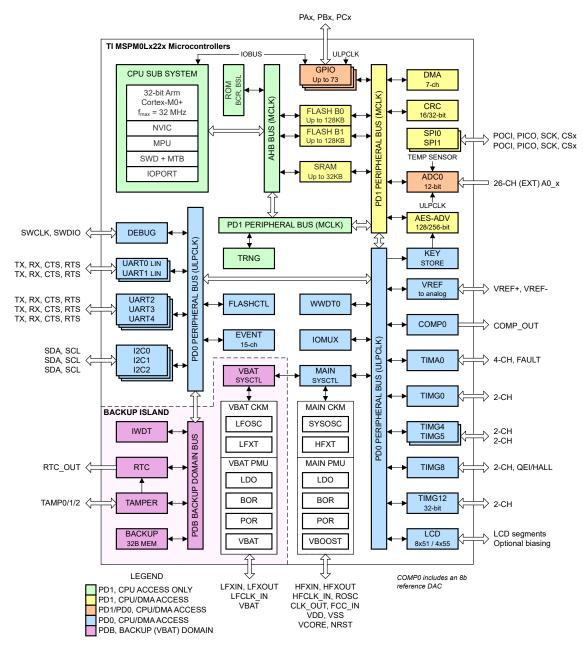

| Figure 4-1. MSPM0Lx22x-Q1 Device Block Diagram | 9   |

| Figure 4-2. MSPM0Lx22x-Q1 Typical Application  | 10  |

# List of Tables

| Table 3-1. Functional Safety Activities Overlaid on top of TI's Standard Development Process | 8  |

|----------------------------------------------------------------------------------------------|----|

| Table 5-1. ADC Safety Mechanisms                                                             |    |

| Table 5-2. Comparator Safety Mechanisms                                                      | 15 |

| Table 5-3. CPU Safety Mechanisms                                                             |    |

| Table 5-4. RAM Safety Mechanisms                                                      | 17 |

|---------------------------------------------------------------------------------------|----|

| Table 5-5. Flash Safety Mechanisms                                                    | 17 |

| Table 5-6. GPIO Safety Mechanisms                                                     |    |

| Table 5-7. DMA Safety Mechanisms                                                      | 19 |

| Table 5-8. SPI Safety Mechanisms                                                      | 20 |

| Table 5-9. I2C Safety Mechanisms                                                      | 21 |

| Table 5-10. UART Features                                                             | 22 |

| Table 5-11. UART Safety Mechanisms                                                    |    |

| Table 5-12. TIMx Instance Configuration                                               |    |

| Table 5-13. TIMx Cross Trigger Map (PD0)                                              |    |

| Table 5-14. Timers Safety Mechanisms                                                  |    |

| Table 5-15. PMU Safety Mechanisms                                                     | 25 |

| Table 5-16. CKM Safety Mechanisms                                                     | 27 |

| Table 5-17. Events Safety Mechanisms                                                  | 27 |

| Table 5-18. IOMUX Safety Mechanisms                                                   |    |

| Table 5-19. VREF Safety Mechanisms                                                    |    |

| Table 5-20. WWDT and IWDT Safety Mechanisms                                           |    |

| Table 5-21. CRC Safety Mechanisms                                                     |    |

| Table 6-1. Configuration Registers Associated With Different Safety Mechanisms        | 32 |

| Table 6-2. IOMUX Coverage                                                             |    |

| Table 6-3. Safety Mechanisms Covering Common Cause Failures                           |    |

| Table A-1. Legend of Functional Safety Mechanisms                                     |    |

| Table A-2. Summary of Safety Features and Diagnostics                                 | 43 |

| Table B-1. Activities Performed by Texas Instruments Versus Performed by the Customer |    |

| Table B-2. Product Functional Safety Documentation.                                   |    |

|                                                                                       |    |

This document is a functional safety manual for the Texas Instruments MSPM0Lx22x-Q1 component. The specific orderable part numbers supported by this functional safety manual are as follows:

- MSPM0L2228-Q1 (Orderable Part Numbers: M0L2228QPTRQ1, M0L2228QPNRQ1, M0L2228QPMRQ1)

- MSPM0L1228-Q1 (Orderable Part Numbers: M0L1228QRGZRQ1, M0L1228QRGERQ1, M0L1228QRHBRQ1, M0L1228QPNRQ1, M0L1228QPMRQ1, M0L1228QPTRQ1)

- MSPM0L2227-Q1 (Orderable Part Numbers: M0L2227QPMRQ1, M0L2227QPTRQ1, M0L2227QPNRQ1)

- MSPM0L1227-Q1 (Orderable Part Numbers: M0L1227QRGERQ1, M0L1227QPMRQ1, M0L1227QPTRQ1, M0L1227QRGZRQ1, M0L1227QPNRQ1, M0L1227QRHBRQ1)

This functional safety manual provides information needed by system developers to help in the creation of a functional safety system using a MSPM0Lx22x-Q1 component. This document includes:

- An overview of the component architecture

- · An overview of the development process used to decrease the probability of systematic failures

- An overview of the functional safety architecture for management of random failures

- · The details of architecture partitions and implemented functional safety mechanisms

The following information is documented in the MSPM0Lx22x-Q1 Functional Safety Analysis Report and is not repeated in this document:

- Summary of failure in time (FIT) rates of the component

- Summary of functional safety metrics of the hardware component for targeted standards (for example IEC-61508, ISO-26262)

- Quantitative functional safety analysis (also known as FMEDA, Failure Modes, Effects, and Diagnostics Analysis) with detail of the different parts of the component, allowing for customized application of functional safety mechanisms

- · Assumptions used in the calculation of functional safety metrics

The following information is documented in the Functional Safety Report and is not repeated in this document:

· Results of assessments of compliance to targeted standards

The user of this document needs a general familiarity with the MSPM0Lx22x-Q1 component. For more information, refer to the MSPM0Lx22x-Q1 data sheets. This document is intended to be used in conjunction with the pertinent data sheets, technical reference manuals, and other component documentation.

For information that is beyond the scope of the listed deliverables, contact your TI sales representative or go to TI Functional Safety.

#### Trademarks

Microwire<sup>™</sup> and TI E2E<sup>™</sup> are trademarks of Texas Instruments.

FlexRay<sup>™</sup> is a trademark of FlexRay Consortium.

Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Motorola<sup>®</sup> is a registered trademark of MOTOROLA TRADEMARK HOLDINGS, LLC.

All trademarks are the property of their respective owners.

# Chapter 2 MSPM0Lx22x-Q1 Hardware Component Functional Safety Capability

This section summarizes the component functional safety capability.

This hardware component:

- Was developed as a functional Safety Element out of Context (SEooC)

- Was developed according to the relevant requirements of ISO 26262:2018

- Achieves systematic integrity level of ASIL-D

- · Includes sufficient functional safety mechanisms for random fault integrity up to ASIL-B

# Chapter 3 Development Process for Management of Systematic Faults

For functional safety development, it is necessary to manage both systematic and random faults. Texas Instruments follows a new-product development process for all of its components which helps to decrease the probability of systematic failures. This new-product development process is described in Section 3.1. Components being designed for functional safety applications will additionally follow the requirements of TI's functional safety development process, which is described in Section 3.2.

# 3.1 TI New-Product Development Process

Texas Instruments has been developing components for automotive and industrial markets since 1996. Automotive markets have strong requirements regarding quality management and product reliability. The TI new-product development process features many elements necessary to manage systematic faults. Additionally, the documentation and reports for these components can be used to assist with compliance to a wide range of standards for customer's end applications including automotive and industrial systems (for example, ISO 26262-4, IEC 61508-2).

This component was developed using TI's new product development process which has been certified as compliant to ISO 9001 / IATF 16949 as assessed by Bureau Veritas (BV).

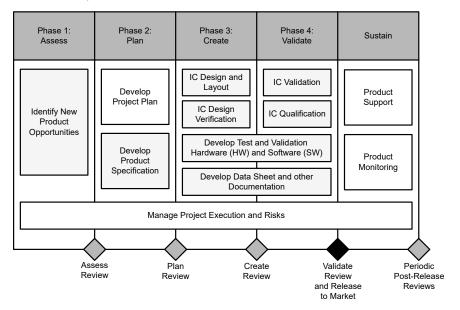

The standard development process breaks development into phases:

- Assess

- Plan

- Create

- Validate

Section 3.1 shows the standard process.

Figure 3-1. TI New-Product Development Process

# 3.2 TI Functional Safety Development Process

The TI functional safety development flow derives from ISO 26262 and IEC 61508 a set of requirements and methodologies to be applied to semiconductor development. This flow is combined with TI's standard new product development process to develop TI functional safety components. The details of this functional safety development flow are described in the TI internal specification - TI Functional Safety Hardware.

Key elements of the TI functional safety-development flow are as follows:

- Assumptions on system level design, functional safety concept, and requirements based on TI's experience with components in functional safety applications

- Qualitative and quantitative functional safety analysis techniques including analysis of silicon failure modes and application of functional safety mechanisms

- · Base FIT rate estimation based on multiple industry standards and TI manufacturing data

- Documentation of functional safety work products during the component development

- Integration of lessons learned through multiple functional safety component developments, functional safety standard working groups, and the expertise of TI customers

Table 3-1 lists these functional safety development activities which are overlaid atop the standard development flow in Figure 3-1.

Refer to Appendix B for more information about which functional safety lifecycle activities TI performs.

The customer facing work products derived from this TI functional safety process are applicable to many other functional safety standards beyond ISO 26262 and IEC 61508.

| Assess                                                             | Plan                                                                                        | Create                                                                    | Validate                                                   | Sustain and End-of-Life                                               |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|

| Determine if functional<br>safety process execution<br>is required | Define component target<br>SIL/ASIL capability                                              | Develop component<br>level functional safety<br>requirements              | Validate functional safety design in silicon               | Document any reported issues (as needed)                              |

| Nominate a functional safety manager                               | Generate functional safety plan                                                             | Include functional safety<br>requirements in design<br>specification      | Characterize the functional safety design                  | Perform incident reporting<br>of sustaining operations<br>(as needed) |

| End of Phase Audit                                                 | Verify the functional safety plan                                                           | Verify the design specification                                           | Qualify the functional<br>safety design (per AEC-<br>Q100) | Update work products (as needed)                                      |

|                                                                    | Initiate functional safety case                                                             | Start functional safety design                                            | Finalize functional safety case                            |                                                                       |

|                                                                    | Analyze target<br>applications to generate<br>system level functional<br>safety assumptions | Perform qualitative<br>analysis of design (i.e.<br>failure mode analysis) | Perform assessment of project                              |                                                                       |

|                                                                    | End of Phase Audit                                                                          | Verify the qualitative analysis                                           | Release functional safety manual                           |                                                                       |

|                                                                    |                                                                                             | Verify the functional safety design                                       | Release functional safety<br>analysis report               |                                                                       |

|                                                                    |                                                                                             | Perform quantitative<br>analysis of design (i.e.<br>FMEDA)                | Release functional safety report                           |                                                                       |

|                                                                    |                                                                                             | Verify the quantitative analysis                                          | End of Phase Audit                                         |                                                                       |

|                                                                    |                                                                                             | Iterate functional safety design as necessary                             |                                                            |                                                                       |

|                                                                    |                                                                                             | End of Phase Audit                                                        |                                                            |                                                                       |

# Table 3-1. Functional Safety Activities Overlaid on top of TI's Standard Development Process

# Chapter 4 MSPM0Lx22x-Q1 Component Overview

# Texas Instruments

# 4.1 Targeted Applications

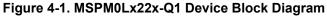

The MSPM0Lx22x-Q1 component is targeted at general-purpose functional safety applications. This is called Safety Element out of Context (SEooC) development according to ISO 26262-10:2018. In this case, the development is done based on assumptions on the conditions of the semiconductor component usage, and then the assumptions are verified at the system level. This section describes some of the target applications for this component, the component safety concept, and then describes the assumptions about the systems (also know as Assumptions of Use or AoU) that were made in performing the safety analysis.

Example target applications include, but are not limited to, the following:

- Automotive Person occupancy detection

- Automotive Lighting

- Automotive Seat heaters

- Automotive Window control

Figure 4-2 shows a typical block diagram in which the MSPM0 MCUs can be used. This diagram is only an example and does not necessarily represent a complete system.

Figure 4-2. MSPM0Lx22x-Q1 Typical Application

# 4.2 Hardware Component Functional Safety Concept

In case of internal errors in the component, one or more of the following actions can be taken:

- Take the actuator output pins to a safe state (for example, the fault logic in timers can take the outputs to a safe state).

- · Reset the device.

- Communicate the error to the host CPU and let system take the appropriate action.

# 4.3 Functional Safety Constraints and Assumptions

In creating a functional Safety Element out of Context (SEooC) concept and doing the functional safety analysis, TI generates a series of assumptions on system level design, functional safety concept, and requirements. These assumptions (sometimes called Assumptions of Use) are listed below. Additional assumptions about the detailed implementation of safety mechanisms are separately located in Section 6.3.

The MSPM0Lx22x-Q1 Functional Safety Analysis was done under the following system assumptions:

- [SA\_1] The MSPM0Lx22x-Q1 MCU has interfaces to external sensors.

- [SA\_2] The MSPM0Lx22x-Q1 MCU has interfaces to external actuators.

- [SA\_3] The MSPM0Lx22x-Q1 MCU has interfaces to communicate with an external host controller.

- **[SA\_4]** The MSPM0Lx22x-Q1 MCU has a programmable CPU to execute a controller function taking sensor inputs and controlling an actuator.

TEXAS

NSTRUMENTS

- **[SA\_5]** The system integrator reviews the recommended diagnostics in the safety analysis report (FMEDA) and safety manual and determines the appropriate diagnostics to include in the system. These diagnostics are implemented according to the device safety manual and data sheet.

- **[SA\_6]** The external power supply provides the appropriate power on for each of the power inputs. These rails are monitored for deviations outside the device specifications and a reset asserts, if the voltage is outside the range.

- [SA\_7] The MSPM0Lx22x-Q1 MCU monitors failures on the external clock (if present).

- [SA\_8] The MSPM0Lx22x-Q1 MCU monitors failures on external sensors.

- [SA\_9] The MSPM0Lx22x-Q1 MCU monitors failures on external actuators.

- **[SA\_10]** In case of internal errors in the MSPM0Lx22x-Q1 MCU or the interfacing sensors and actuators, the MSPM0Lx22x-Q1 MCU can be reset. The host controller monitors communication loss and determines that the MSPM0Lx22x-Q1 MCU is in a faulted state.

- **[SA\_11]** The system integrator provisions an actuator disable-mechanism controller by the host controller.

- **[SA\_12]** The system is assumed to require architectural metrics (random fault) complying to (up to) ASIL-B.

- [SA\_14] The system is assumed to have a FTTI > 10ms.

- [SA\_15] The system integrator connects VBAT and VDD power pins to the same power source.

- **[SA\_16]** The system integrator considers all potential failure modes and mitigation measures associated with communication interfaces while implementing any end-to-end communication protection diagnostics techniques.

- [SA\_16] The DEBUG function is considered as not safety critical.

- [SA\_17] The RTC function is considered as not safety critical.

- [SA\_18] The AES function is considered as not safety critical.

- [SA\_19] The TRNG function is considered as not safety critical.

- [SA\_20] The TAMPER function is considered as not safety critical.

- [SA\_21] The BACKUP function is considered as not safety critical.

- [SA\_22] The LCD function is considered as not safety critical.

- [SA\_23] The KEYSTORE function is considered as not safety critical.

- **[SA\_24]** The QM IPs are not used in safety-critical applications.

- [SA\_25] TI assumes that the internal low power modes are not used in safety-critical applications.

- **[SA\_26]** The system integrator considers all potential failure modes and mitigation measures associated with communication interfaces while implementing any end-to-end communication protection diagnostics techniques.

- [COEX0] The following components are assumed not safety related (NSR components):

- RTC

- TRNG

- AES

- TAMPER

- BACKUP RAM

- LCD

- KEYSTORE

- DFT

- DEBUG

- [COEX1] TI recommends that unused components are disabled in the application software.

- **[COEX2]** TI recommends that the unused interrupt sources of components are disabled.

- **[COEX3]** TI recommends that DMA unused triggers of components are disabled.

- [COEX4] TI recommends that unused fault inputs in timers are disabled.

- **[COEX5]** If external safety mechanisms are used, the system integrator is responsible for completing a dependent failure analysis at the system level.

- [COEX6] TI assumes that the NSR components are not used in the safety context.

- [COEX7] TI recommends that debug is disabled in safety-critical applications.

- **[COEX8]** TI recommends that a default interrupt service routine is coded for even the unused interrupts.

- **[COEX9]** TI recommends that the application does not use IPs as the trigger source of other IPs when those IPs are not safety related.

- [COEX10] TI recommends that the application does not program flash during safety-critical tasks.

There are some safety mechanisms required to cover dependent failures, refer to section on Section 6.3.63 for more details.

During integration activities these assumptions of use and integration guidelines described for this component shall be considered. Use caution if one of the above functional safety assumptions on this component cannot be met, as some identified gaps can be unresolvable at the system level.

# Chapter 5 Description of Hardware Component Parts

A semiconductor component can be divided into parts to enable a more granular functional safety analysis. This can be useful to help assign specific functional safety mechanisms to portions of the design where the mechanisms provide coverage ending up with a more complete and customizable functional safety analysis. This section includes a brief description of each hardware part of this component and lists the functional safety mechanisms that must be applied to attain ASIL-B. This section is intended to provide additional details about the assignment of functional safety mechanisms that can be found in the Safety Analysis Report. The content in this section is also summarized in Appendix A.

More details of the hardware components can be found in *MSPM0Lx22x-Q1 Microcontrollers Technical Reference Manual*.

# 5.1 ADC

The 12-bit analog-to-digital converter (ADC) module in these devices supports fast, 12-bit conversions with single-ended inputs. ADC features include:

- 12-bit output resolution at up to 1.68Msps with greater than 11-bit ENOB

- · Hardware averaging enables a 14-bit conversion resolution at 105ksps

- Up to 26 external input channels

- Internal channels for temperature sensing, supply monitoring, and analog signal chain

- Software selectable reference:

- Configurable internal dedicated ADC reference voltage of 1.4V and 2.5V (VREF)

- MCU supply voltage (VDD)

- External reference supplied to the ADC through the VREF+ and VREF- pins

- Operates in RUN, SLEEP, and STOP modes and supports triggers from STANDBY mode

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism             | Description                                                      | Faults   Failure Modes                                                                                                                                                                                                                                        |

|------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC1                         | Periodic software read back of static<br>configuration registers | Targeted toward configuration registers in ADC.                                                                                                                                                                                                               |

| ADC2                         | Software Test for Functionality                                  | Targeted toward the ADC functionality,<br>including the sample pulse generation, ADC<br>conversion, logic which captures the result,<br>interrupt flag setting, DMA trigger generation,<br>proper function of the analog-to-digital circuit,<br>and so forth. |

| ADC3                         | ADC trigger overflow                                             | Targeted toward ADC triggering circuit related faults.                                                                                                                                                                                                        |

| ADC4                         | ADC window comparator                                            | Covers faults in analog-to-digital conversion<br>logic, and also covers faults in ADC inputs<br>which result in the converted result going out<br>of range.                                                                                                   |

| ADC5 (latent fault coverage) | Test of window comparator                                        | This is a test to cover faults in the window<br>comparator (the window comparator being a<br>safety mechanism). This test covers latent<br>faults within the window comparator.                                                                               |

| Table 5-1. ADC Safety | Mechanisms |

|-----------------------|------------|

|-----------------------|------------|

| Table 5-1. ADC Salety Mechanisms (continued) |                                           |                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Safety Mechanism                             | Description                               | Faults   Failure Modes                                                                                                                                                                                                                                                                                   |  |

| ADC6                                         | ADC trigger and output plausibility check | This is an application-specific check. Based<br>on the application, software can check on<br>signal properties, like range, bandwidth,<br>sampling rate, and so forth. This check can<br>potentially cover faults in ADC sampling and<br>conversion, triggering logic, interrupt logic,<br>and so forth. |  |

| WDT                                          | Windowed watchdog event                   | Used to cover faults in sample generation,<br>interrupt generation, DMA trigger generation,<br>and event triggering to other IPs. Any<br>periodic event which does not occur, or<br>occurs at a different rate than expected, can<br>be covered.                                                         |  |

| IWDT                                         | Independent watchdog timer                | Used to cover faults in sample generation,<br>interrupt generation, DMA trigger generation,<br>and event triggering to other IPs. Any<br>periodic event which does not occur.                                                                                                                            |  |

### Table 5-1. ADC Safety Mechanisms (continued)

•

# 5.2 Comparator

The comparator peripheral in the device compares the voltage levels on two input terminals and provides a digital output (based on this comparison). The comparator supports the following key features:

- Programmable hysteresis

- Programmable reference voltage:

- External reference voltage (VREF I/O)

- Dedicated Internal reference voltage (1.4V, 2.5V) available in RUN, SLEEP, STOP, and STANDBY modes.

- Integrated 8-bit reference DAC

- Configurable operation modes:

- High-speed mode

- Lower-power mode (not to be used in safety critical applications)

- Programmable output glitch filter delay

- Supports output wake-up device from all low power modes (not to be used in safety critical applications)

- · Output is connected to an advanced timer fault handling mechanism

- The IPSEL and IMSEL bits in comparator registers can be used to select the comparator channel inputs from device pins or from internal analog modules.

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism | Description                                                      | Faults   Failure Modes                                                                                                                                                                     |

|------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMP1            | Periodic software read back of static<br>configuration registers | Targeted toward configuration registers in comparator.                                                                                                                                     |

| COMP3            | Comparator test using an external pin as a test input            | Targeted to test the comparator functioning using an external pin as test input.                                                                                                           |

| COMP4            | Comparator hysteresis                                            | This is a fault avoidance technique, which<br>can be used to filter the noise on the input<br>to the comparator.                                                                           |

| WDT              | Windowed watchdog event                                          | Targeted toward interrupt generation logic.<br>If a periodic interrupt is expected from the<br>comparator watchdog, this mechanism can<br>be used to detect faults in the interrupt logic. |

#### Table 5-2. Comparator Safety Mechanisms

# 5.3 CPU

The CPU subsystem (MCPUSS) implements an Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ CPU, an instruction prefetch and cache, a system timer, a memory protection unit, and interrupt management features. The Arm Cortex-M0+ is a 32-bit CPU which delivers high performance and low power to embedded applications. Key features of the CPU subsystem includes:

- Arm Cortex-M0+ CPU supporting clock frequencies up to 32MHz

- ARMv6-M thumb instruction set (little endian) with single-cycle 32×32 multiply instruction

- Single-cycle access to GPIO registers through Arm single-cycle I/O port

- Prefetch logic to improve sequential code execution, and I-cache with four 64-bit cache lines

- System timer (SysTick) with 24-bit down counter and automatic reload

- Memory protection unit (MPU) with eight programmable regions

- · Nested vectored interrupt controller (NVIC) with four programmable priority levels and tail-chaining

- Interrupt groups, for expanding the total interrupt sources, with jump index for low-interrupt latency

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism | Description                                                                                                    | Faults   Failure Modes                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU1             | ARM software test library                                                                                      | Targeted toward the Cortex-M0+ CPU and NVIC.                                                                                                                                                    |

| CPU2             | Writes and reads back data to different regions of memory to detect faults in the bus interconnect components. | Targeted toward the bus decoders and<br>interface logic in the CPU subsystem. These<br>decoders route the CPU access to different<br>components based on the address.                           |

| CPU3             | Software diversified redundancy                                                                                | Used to target CPU functioning. This is<br>an application-specific check, in which the<br>same computation is performed in two<br>different software functions and the results<br>are compared. |

| CPU4             | Periodic software read back of static configuration registers                                                  | Targeted toward the configuration registers in the CPU subsystem (registers in the interrupt grouping logic, and so forth).                                                                     |

| SYSCTL11         | Boot process timeout                                                                                           | Targeted toward boot ROM.                                                                                                                                                                       |

| WDT              | Windowed watchdog event                                                                                        | Targeted toward CPU control flow, any CPU bus related faults, faults in the CPU interrupt logic, and so forth.                                                                                  |

#### Table 5-3. CPU Safety Mechanisms

# 5.4 RAM

The MSPM0 MCUs include a low-power, high-performance SRAM with zero wait state access across the supported CPU frequency range of the device. The MSPM0 MCUs also provide up to 32KB of ECC protected SRAM with hardware parity. SRAM can be used for storing volatile information, such as, the call stack, heap, global data, and code. The SRAM content is fully retained in RUN, SLEEP, STOP, and STANDBY modes and is lost in shutdown mode. A write-execute, mutual-exclusion mechanism is provided to allow the application to partition the SRAM into two sections:

- 1. A read-write (RW) partition

- 2. A read-execute (RX) partition

The RX partition occupies the upper portion of the SRAM address space. Write protection is useful when placing executable code into SRAM, as the write protection provides a level of protection against unintentional overwrites of code by either the CPU or DMA. Placing code in SRAM can improve performance of critical loops by enabling a zero wait state operation and lower power consumption.

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism                | Description                 | Faults   Failure Modes                                                                                             |

|---------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------|

| SYSMEM1                         | Software read of memory DMA | Targeted toward the DMA bus decoder in the SRAM controller and the arbitration logic.                              |

| SYSMEM2                         | Software read of memory CPU | Targeted toward the CPU bus decoder in the SRAM controller and the arbitration logic.                              |

| SYSMEM7                         | RAM ECC                     | Targeted toward the faults in SRAM.                                                                                |

| SYSMEM9                         | RAM software test           | Targeted towards multipoint latent faults in SRAM.                                                                 |

| SYSMEM8 (latent fault coverage) | ECC logic test              | This is a test of diagnostic. This test is used to test the function of the ECC checker logic.                     |

| WDT                             | Windowed watchdog event     | Targeted toward arbitration logic. Any fault<br>which leads to a CPU bus hang can be<br>covered by this mechanism. |

#### Table 5-4. RAM Safety Mechanisms

# 5.5 FLASH

A dual bank of nonvolatile flash memory (up to 128KB or 256KB total) is provided for storing executable program code and application data. Key features of the flash include:

- Hardware ECC protection (encode and decode) with single-bit error correction and double-bit error detection

- In-circuit program and erase operations supported across the entire recommended supply range

- Small 1KB sector sizes (minimum erase resolution of 1KB)

- Up to 100000 program and erase cycles on the lower 32KB of the flash memory, with up to 10000 program and erase cycles on the remaining flash memory (devices with 32KB support 100000 cycles on the entire flash memory)

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism               | Description                               | Faults   Failure Modes                                                                                                                                                                                     |

|--------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU3                           | Software diversified redundancy           | Targeted toward the arbitration logic. If due to fault in arbitration logic, incorrect data is returned, this test can be used to cover such faults.                                                       |

| DMA2                           | Software DMA transfer test                | Targeted toward DMA bus decoder and the arbitration logic.                                                                                                                                                 |

| FLASH1                         | Flash ECC                                 | Targeted toward the faults in the flash memory.                                                                                                                                                            |

| FLASH2                         | Flash CRC                                 | Targeted towards multipoint latent faults in the flash memory.                                                                                                                                             |

| FXBAR2                         | Periodic software read back of flash data | Targeted toward the decoding logic on the CPU read bus.                                                                                                                                                    |

| FXBAR3 (latent fault coverage) | Software check of ECC checker logic       | This is a test of diagnostic, used to check the function of the ECC checker.                                                                                                                               |

| FXBAR4                         | Write protection of flash                 | Targeted toward the faults in the programming interface.                                                                                                                                                   |

| WDT                            | Windowed watchdog event                   | Targeted toward the arbitration logic and<br>flash read interface. Any fault in this logic<br>which results in incorrect data being returned<br>to CPU causing a CPU decoding an incorrect<br>instruction. |

#### Table 5-5. Flash Safety Mechanisms

# 5.6 GPIO

The general purpose input output (GPIO) peripheral provides the user with a means to write data out, read data into the device pins, and read data from the device pins. Through the use of the Port A and Port B GPIO peripherals, these devices support up to 60 GPIO pins.

The key features of the GPIO module include:

- Zero wait state MMR access from the CPU

- · Set, clear, and toggle, multiple bits without the need of a read-modify-write construct in software

- GPIOs with Standard with Wake drive functionality able to wake the device from SHUTDOWN mode

- The FastWake feature enables low-power wakeup from STOP and STANDBY modes for any GPIO port

- User controlled input filtering

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism | Description                                                  | Faults   Failure Modes                                                                                                                                                                                                                                           |  |

|------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO1            | Online monitoring using I/O loopback                         | Targeted toward the GPIO DOUT register and the interface to I/O.                                                                                                                                                                                                 |  |

| GPIO2            | Periodic Software Readback of Static Configuration Registers | Targeted toward GPIO configuration registers.                                                                                                                                                                                                                    |  |

| GPIO3            | GPIO multiple (redundant) inputs and outputs                 | This is an application-level test. For critical GPIOs, a redundancy mechanism can be employed to get high coverage.                                                                                                                                              |  |

| WDT              | Windowed watchdog event                                      | This is targeted toward the interrupt<br>generation logic in GPIO. If an interrupt<br>is expected to occur periodically, this<br>mechanism can be used.<br>WDT is also used to cover pin failures in<br>case the pin is used as an external interrupt<br>source. |  |

### Table 5-6. GPIO Safety Mechanisms

# 5.7 DMA

The direct memory access (DMA) controller allows movement of data from one memory address to another without CPU intervention. For example, the DMA can be used to move data from ADC conversion memory to SRAM. The DMA reduces system power consumption by allowing the CPU to remain in low-power mode, without having to wake to move data to or from a peripheral.

The DMA in these devices support the following key features:

- Seven independent DMA transfer channels

- Four basic channel supports (single transfer modes)

- Three full-feature channel supports (repeated transfer modes)

- Configurable DMA channel priorities

- Byte (8-bit), short word (16-bit), word (32-bit), and long word (64-bit) or mixed byte and word transfer capability

- Transfer counter block size supports up to 64k transfers of any data type

- Configurable DMA transfer trigger selection

- · Active channel interruption to service other channels

- Early interrupt generation for ping-pong buffer architecture

- · Cascading channels upon completion of activity on another channel

- Stride mode to support data reorganization, such as 3-phase metering applications

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

TEXAS INSTRUMENTS

www.ti.com

|                  | Table 5-7. DMA Safety Mechanisms                              |                                                                                                                                                                                                                                                        |  |  |  |

|------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Safety Mechanism | Description                                                   | Faults   Failure Modes                                                                                                                                                                                                                                 |  |  |  |

| DMA1             | Periodic software read back of static configuration registers | Targeted toward configuration registers of DMA.                                                                                                                                                                                                        |  |  |  |

| DMA2             | Software DMA transfer test                                    | Targeted toward DMA bus interface logic<br>and the DMA channel which sequences the<br>read and write access based on the channel<br>configuration.                                                                                                     |  |  |  |

| DMA3             | Software DMA channel test                                     | Targeted toward the channels used in the application context.                                                                                                                                                                                          |  |  |  |

| DMA4             | CRC check of the transferred data                             | Targeted toward DMA bus interface which results in data corruption.                                                                                                                                                                                    |  |  |  |

| SYSCTL11         | Boot process timeout                                          | DMA is used to transfer trims during the<br>boot process. This test targets the DMA logic<br>which is used for this.                                                                                                                                   |  |  |  |

| WDT              | Windowed watchdog event                                       | Target faults which result in either DMA<br>transfer not starting (triggers not getting<br>generated, for example) or transfers not<br>completing (DMA channel faults and bus<br>hangs) resulting in the CPU program<br>sequence also malfunctioning.  |  |  |  |

| IWDT             | Independent watchdog timer.                                   | Target faults which result in either DMA<br>transfer not starting (triggers not getting<br>generated, for example) or transfers not<br>completing (DMA channel faults and bus<br>hangs); resulting in the CPU program<br>sequence also malfunctioning. |  |  |  |

# Table 5-7. DMA Safety Mechanisms

# 5.8 SPI

The serial peripheral interface (SPI) peripherals in these devices support the following key features:

- Support ULPCLK/2 bit rate and up to 16Mbit/s in both controller and peripheral mode

- · Configurable as a controller or a peripheral

- Configurable chip select for both controller and peripheral

- Programmable clock prescaler and bit rate

- Programmable data frame size from

- Programmable data frame size from 7-bits to 16-bits (peripheral mode)

- · Separated transmit and receive FIFOs support DMA data transfer

- Supports TI mode, Motorola<sup>®</sup> mode, and National Microwire<sup>™</sup> format

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism | Description                                                      | Faults   Failure Modes                                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI1             | Software test of function using I/O loopback                     | Targets the transmit and receive function,<br>including the clocking, shift registers, FIFOs,<br>and the associated control logic.                                                                                                                                                                             |

| SPI2             | Periodic software read back of static<br>configuration registers | Targets the static configuration registers in SPI.                                                                                                                                                                                                                                                             |

| SPI3             | SPI periodic safety message checks                               | This is an application-level check, in<br>which safety messages can be exchanged<br>periodically. This mechanism covers faults,<br>which result in communication breakdown.<br>These faults can be in the external line,<br>I/Os, the transmit and receive logic, interrupt<br>generation logic, and so forth. |

| SPI4             | Information redundancy techniques including end-to-end safing    | This is an application-level check, in which<br>additional information (for example, the CRC<br>of the message) is included along with the<br>message. These checks can be used to<br>cover faults resulting in data corruption. For<br>example, faults in FIFO, in the shift registers,<br>and so forth.      |

| SPI5             | Transmission redundancy                                          | This test is an application-level check, in<br>which the same message is transmitted<br>multiple times. This test is effective for<br>detecting transient faults resulting in some<br>messages getting corrupted. For example,<br>transient faults in FIFOs.                                                   |

| WDT              | Windowed watchdog event                                          | Targeted toward faults which result in missing<br>interrupts (periodic interrupts) affecting the<br>program sequence of the CPU. These faults<br>can be faults in the interrupt logic, the logic<br>which sets the interrupt flags, and so forth.                                                              |

# Table 5-8. SPI Safety Mechanisms

# 5.9 I2C

The inter-integrated circuit interface (I2C) peripherals, in these devices, provide bidirectional data transfers with other I2C devices on the bus and support the following key features:

- 7-bit and 10-bit addressing mode with multiple 7-bit target addresses

- Multiple-controller transmitter or receiver mode

- Target receiver or transmitter mode with configurable clock stretching

- Support standard-mode (Sm), with a bit rate up to 100kbit/s

- Support fast-mode (Fm), with a bit rate up to 400kbit/s

- · Support fast-mode plus (Fm+), with a bit rate up to 1 Mbit/s

- Separated transmit and receive FIFOs support DMA data transfer

- Support SMBus 3.0 with PEC, ARP, timeout detection, and host support

- Wakeup from low-power mode on address match

- Support analog and digital glitch filter for input signal glitch suppression

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

| Safety Mechanism | Description                                                   | Faults   Failure Modes                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C1             | Software test of function using I/O loopback                  | Targets the transmit and receive function,<br>including the clocking, shift registers, FIFOs,<br>and the associated control logic.                                                                                                                                                                         |

| I2C2             | Periodic software read back of static configuration registers | Targets the static configuration registers in I2C.                                                                                                                                                                                                                                                         |

| I2C3             | Information redundancy techniques including end-to-end safing | This is an application-level check, in which<br>additional information (for example, the CRC<br>of the message) is included along with the<br>message. These checks can be used to<br>cover faults resulting in data corruption. For<br>example, a fault in FIFO, in the shift registers,<br>and so forth. |

| I2C4             | Transmission redundancy                                       | This test is an application-level check, in<br>which the same message is transmitted<br>multiple times. This test is effective to detect<br>transient faults resulting in some messages<br>getting corrupted. For example, transient<br>faults in FIFOs.                                                   |

| I2C5             | Timeout monitoring                                            | This is an application-level check, in<br>which safety messages can be exchanged<br>periodically. This covers faults which result in<br>communication breakdown. These faults can<br>be in the external line, I/Os, the transmit and<br>receive logic, interrupt generation logic, and<br>so forth.        |

| I2C6             | Test of CRC function                                          | I2C has a CRC checker when configured<br>in the SMBUS mode. This checker checks<br>the proper function of the CRC checker logic<br>by sending corrupt messages as part of the<br>application.                                                                                                              |

| 12C7             | Packet error check in SMBUS mode                              | This targets faults which result in data corruption, for example, faults on the external line, in the FIFOs, shift registers, and so forth.                                                                                                                                                                |

| WDT              | Windowed watchdog event                                       | Targeted toward faults which result in missing<br>interrupts (periodic interrupts) affecting the<br>program sequence of the CPU. These faults<br>can be faults in the interrupt logic, the logic<br>which sets the interrupt flags, and so forth.                                                          |

# 5.10 UART

The UART peripherals (UART0, UART1, UART2, UART3, and UART4) provide the following key features:

- Standard asynchronous communication bits for start, stop, and parity

- Fully programmable serial interface

- Five, six, seven, or eight data bits

- Even, odd, stick, or no-parity bit generation and detection

- One or two stop bit generation

- Line-break detection

- Glitch filter on the input signals

- Programmable baud rate generation with oversampling by 16, 8, or 3

- Local interconnect network (LIN) mode support

- Separated transmit and receive FIFOs support DAM data transfer

- · Support transmit and receive loopback mode operation

- See Table 5-10 for detailed information on supported protocols

#### Table 5-10. UART Features

| UART Features                       | UART0, UART1 (Extend) | UART2, UART3, and UART4 (Main) |  |  |  |  |

|-------------------------------------|-----------------------|--------------------------------|--|--|--|--|

| Active in stop and standby mode     | Yes                   | Yes                            |  |  |  |  |

| Separate transmit and receive FIFOs | Yes                   | Yes                            |  |  |  |  |

| Supports hardware flow control      | Yes                   | Yes                            |  |  |  |  |

| Supports 9-bit configuration        | Yes                   | Yes                            |  |  |  |  |

| Supports LIN mode                   | Yes                   | -                              |  |  |  |  |

| Supports DALI                       | Yes                   | -                              |  |  |  |  |

| Supports IrDA                       | Yes                   | -                              |  |  |  |  |

| Supports ISO7816 Smart Card         | Yes                   | -                              |  |  |  |  |

| Supports Manchester coding          | Yes                   | -                              |  |  |  |  |

|                                     |                       |                                |  |  |  |  |

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

#### Table 5-11. UART Safety Mechanisms

| Safety Mechanism | Description                                                      | Faults   Failure Modes                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART1            | Software test of function using I/O loopback                     | Targets the transmit and receive function,<br>including the clocking, shift registers, FIFOs,<br>and the associated control logic.                                                                                                                                                                       |

| UART2            | Periodic software read back of static<br>configuration registers | Targets the static configuration registers in UART.                                                                                                                                                                                                                                                      |

| UART3            | Information redundancy techniques including end-to-end safing    | This is an application-level check, in which<br>additional information (for example, the CRC<br>of the message) is included along with the<br>message. These checks can be used to<br>cover faults resulting in data corruption. For<br>example, fault in FIFO, in the shift registers,<br>and so forth. |

| UART4            | Transmission redundancy                                          | This test is an application-level check, in<br>which the same message is transmitted<br>multiple times. This test is effective to detect<br>transient faults resulting in some messages<br>getting corrupted. For example, transient<br>faults in FIFOs.                                                 |

| Safety Mechanism | Description             | Faults   Failure Modes                                                                                                                                                                                                                                                                              |

|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART5            | Timeout monitoring      | This is an application-level check, in<br>which safety messages can be exchanged<br>periodically. This covers faults which result in<br>communication breakdown. These faults can<br>be in the external line, I/Os, the transmit and<br>receive logic, interrupt generation logic, and<br>so forth. |

| UART6            | UART error flags        | This safety mechanism provides detection for<br>some typical failures which result in protocol<br>violations and can cover faults in the transmit<br>and receive control logic or on the external<br>line.                                                                                          |

| UART7            | UART glitch filter      | This mechanism is a fault-avoidance measure against glitches on the RX line.                                                                                                                                                                                                                        |

| WDT              | Windowed watchdog event | Targeted toward faults which result in missing<br>interrupts (periodic interrupts) affecting the<br>program sequence of the CPU. These faults<br>can be faults in the interrupt logic, the logic<br>which sets the interrupt flags, and so forth.                                                   |

#### Table 5-11. UART Safety Mechanisms (continued)

# 5.11 Timers (TIMx)

There are two timer peripherals in these devices (which support the following key features); (1) TIMGx (generalpurpose timer) and (2) TIMAx (advanced timer). The TIMGx is a subset of TIMAx, which means these timers share many common features that are compatible in software. For specific configuration, see Table 5-12:

Specific features for the general-purpose timer (TIMGx) include:

- 16-bit and 32-bit timers with up, down, or up-down counting modes, with repeat-reload mode

- Selectable and configurable clock source

- 8-bit programmable prescaler to divide the counter clock frequency

- Two independent CC channels for

- Output compare

- Input capture

- PWM output

- One-shot mode

- Support quadrature encoder interface (QEI) for positioning and movement sensing available in TIMG8

- Support synchronization and cross trigger among different TIMx instances in the same power domain

- Support interrupt and DMA trigger generation and cross peripherals (such as ADC) trigger capability

- Cross trigger event logic for Hall sensor inputs (TIMG8)

Specific features for the advanced timer (TIMAx) include:

- 16-bit timer with up, down, or up-down counting modes, with repeat-reload mode

- Selectable and configurable clock source

- · 8-bit programmable prescaler to divide the counter clock frequency

- Repeat counter to generate an interrupt or event only after a given number of cycles of the counter

- · Up to four independent CC channels for

- Output compare

- Input capture

- PWM output

- One-shot mode

- Two additional capture and compare channels for internal events (CC4 and CC5)

- Shadow register for load and CC register available in TIMA0

- Complementary output PWM

- Asymmetric PWM with programmable dead band insertion

- Fault handling mechanism to verify the output signals in a safe user-defined state when a fault condition is encountered

- Support synchronization and cross trigger among different TIMx instances in the same power domain

- Support interrupt and DMA trigger generation and cross peripherals (such as ADC) trigger capability

- Two additional capture and compare channels for internal events

|          |                 |                       |           |                   |                                            |                             |               | <b>j</b>       |               |          |                  |                             |

|----------|-----------------|-----------------------|-----------|-------------------|--------------------------------------------|-----------------------------|---------------|----------------|---------------|----------|------------------|-----------------------------|

| Instance | Power<br>Domain | Counter<br>Resolution | Prescaler | Repeat<br>Counter | CCP<br>Channels<br>(External/<br>Internal) | External<br>PWM<br>Channels | Phase<br>Load | Shadow<br>Load | Shadow<br>CCs | Deadband | Fault<br>Handler | QEI / Hall<br>Input<br>Mode |

| TIMG0    | PD0             | 16-bit                | 8-bit     | -                 | 2                                          | 2                           | -             | -              | -             | -        | -                | -                           |

| TIMG4    | PD0             | 16-bit                | 8-bit     | -                 | 2                                          | 2                           | -             | Yes            | Yes           | -        | -                | -                           |

| TIMG5    | PD0             | 16-bit                | 8-bit     | -                 | 2                                          | 2                           | -             | Yes            | Yes           | -        | -                | -                           |

| TIMG8    | PD0             | 16-bit                | 8-bit     | -                 | 2                                          | 2                           | -             | -              | -             | -        | -                | Yes                         |

| TIMG12   | PD0             | 32-bit                | -         | -                 | 2                                          | 2                           | -             | -              | Yes           | -        | -                | -                           |

| TIMA0    | PD0             | 16-bit                | 8-bit     | Yes               | 4/2                                        | 8                           | Yes           | Yes            | Yes           | Yes      | Yes              | -                           |

# Table 5-12. TIMx Instance Configuration

# Table 5-13. TIMx Cross Trigger Map (PD0)

| TSEL.ETSEL<br>Selection | TIMA0                           | TIMG0        | TIMG4        | TIMG5        | TIMG8        | TIMG12       |

|-------------------------|---------------------------------|--------------|--------------|--------------|--------------|--------------|

| 0                       | TIMA0.TRIGO                     | TIMA0.TRIGO  | TIMA0.TRIGO  | TIMA0.TRIGO  | TIMA0.TRIGO  | TIMA0.TRIGO  |

| 1                       | TIMG0.TRIGO                     | TIMG0.TRIGO  | TIMG0.TRIGO  | TIMG0.TRIGO  | TIMG0.TRIGO  | TIMG0.TRIGO  |

| 2                       | TIMG4.TRIGO                     | TIMG4.TRIGO  | TIMG4.TRIGO  | TIMG4.TRIGO  | TIMG4.TRIGO  | TIMG4.TRIGO  |

| 3                       | TIMG5.TRIGO                     | TIMG5.TRIGO  | TIMG5.TRIGO  | TIMG5.TRIGO  | TIMG5.TRIGO  | TIMG5.TRIGO  |

| 4                       | TIMG8.TRIGO                     | TIMG8.TRIGO  | TIMG8.TRIGO  | TIMG8.TRIGO  | TIMG8.TRIGO  | TIMG8.TRIGO  |

| 5                       | TIMG12.TRIGO                    | TIMG12.TRIGO | TIMG12.TRIGO | TIMG12.TRIGO | TIMG12.TRIGO | TIMG12.TRIGO |

| 6 to 15                 | Reserved                        |              |              |              |              |              |

| 16                      | Event Subscriber Port 0 (FSUB0) |              |              |              |              |              |

| 17                      | Event Subscriber Port 1 (FSUB1) |              |              |              |              |              |

| 18-31                   |                                 |              | Rese         | erved        |              |              |

The following tests must be applied for the targeted ASIL as functional safety mechanisms for this module (to provide diagnostic coverage on a specific function):

#### Table 5-14. Timers Safety Mechanisms

| Safety Mechanism             | Description                                                         | Faults   Failure Modes                                                                                                                                                              |