## Optimizing Data Transfer on High-Resolution, High-Throughput Data Converters

Many of today's data acquisition systems in industrial, medical and precision measurement applications incorporate high resolution and high throughput analog-to-digital converters (ADCs). Higher resolution data conversion requires more bits of data per sample, while higher throughput ADCs provide more samples per second. These attributes result in the demand for high data transfer rates between the ADC and the host, producing constraints that may be difficult to resolve. This article focuses on the Enhanced-SPI's Clock Re-Timer data transfer operation supported by some precision SAR ADCs.

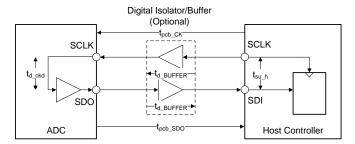

The Serial Peripheral Interface (SPI) is a synchronous serial communication interface commonly used with ADCs where the device sends data in response to serial clock. Figure 1 illustrates the typical timing delays involved between the host and the ADC. The various delays encountered in the system can lead to a set of constraints that can make supporting high data rates difficult.

Figure 1. Typical Data Transfer Delays between Host and ADC

In this figure, the  $t_{pcb\_CK}$  and  $t_{pcb\_SDO}$  are the delays introduced by the printed circuit board (PCB) traces for the serial clock and SDO signals,  $t_{d\_CKDO}$  is the clock-to-data delay of the device,  $t_{d\_BUFFER}$  is the propagation delay introduced by any bus buffers, level translators or digital isolators, and  $t_{su\_h}$  is the setup time specification of the host controller. The total delay in the path is given by,

$$t_{d \text{ total}} = t_{pcb \text{ CK}} + t_{d \text{ BUFFER}} + t_{d \text{ CKDO}} + t_{pcb \text{ SDO}} + t_{su \text{ h}}$$

A relation to calculate the maximum SCLK rate as a function of the total data transfer delay is given below:

$$f_{clk\_SPI} \le 1 / t_{d\_total}$$

These equations stipulate that the maximum SCLK frequency cannot exceed the constraints imposed by the sum of the delays, limiting the application throughput.

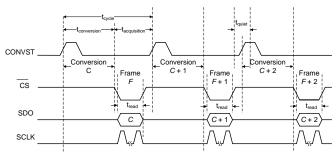

Consider an application requiring communication between the ADS8920B and a host controller through a digital buffer over 1-ft distance of PCB microstrip. The ADS8900B is a 16-B, 1-MSPS, SAR ADC, where the data is available for read-out after the end of conversion. There is a minimum quiet time delay which must be allowed in order to settle the inputs of the ADC before start of next conversion. Figure 2 shows the typical read time interval.

Figure 2. Standard 3-wire SPI Interface with ADS8920B

Hence the total time available for data read is:

$$\mathbf{t}_{\mathrm{read}} = \mathbf{t}_{\mathrm{cycle}}$$

-  $\mathbf{t}_{\mathrm{conversion}}$  -  $\mathbf{t}_{\mathrm{quiet}}$

The ADS8920B has 640-ns conversion time period and a 30-ns quiet time. In order to operate the ADC at 1-MSPS, 16-bits of data must be read in 330-ns. The minimum required SPI clock speed can be computed as:

$$f_{clk\_SPI} = N_{bits} / t_{read} = 16 \ bits / 330 \ ns = 48.5 \ MHz$$

However, the maximum SCLK frequency for this system is constrained to 30.75-MHz due to the delays of the 1ft PCB traces and buffers as calculated in Table 1:

**Table 1. Calculation of Total Transfer Delay**

| t <sub>pcb_CK</sub> | t <sub>d_BUFFER</sub> | t <sub>d_ckdo</sub> | t <sub>pcb_SDO</sub> | t <sub>su_h</sub> | t <sub>d_total</sub> |

|---------------------|-----------------------|---------------------|----------------------|-------------------|----------------------|

| 1.36 ns             | 6.9 ns<br>(2x)        | 13 ns               | 1.36 ns              | 3 ns              | 32.52 ns             |

Therefore, the system is restricted to a maximum SCLK frequency of 30.75-MHz and is unable to support the SCLK frequency required to achieve 1-MSPS sample rate.

## **Enhanced-SPI's Clock Re-Timer Data Transfer**

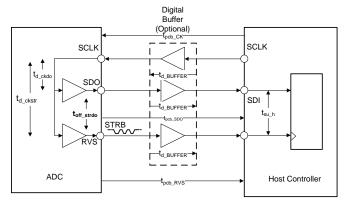

Some TI ADCs such as the ADS8920B and ADS9110 have a dedicated pin to provide a return clock back to the processor. This mode of operation is called the Clock Re-Timer. This Enhanced-SPI mode of operation solves the SCLK frequency limitation problem by moving the timing control of the data transfer from the host to the ADC. As illustrated in Figure 3, in Clock Re-Timer data transfer, the device provides a synchronous output clock on the RVS pin along with the output data on the SDO pin.

Figure 3. Signals Used for Clock Re-Timer Mode Data Transfer

The RVS pin of the ADC functions as a strobe (STRB) acting as an accompanying clock for the data. Each new data bit on the SDO pin is launched with a corresponding positive edge of the STRB. The host can use the STRB as a clock to capture the SDO data. The total delay in the path for a Clock Re-Timer data transfer is greatly reduced, allowing much higher SCLK frequencies:

$$\mathbf{t}_{\text{d\_total\_Timer}} = \mathbf{t}_{\text{pcb\_RVS}}$$

-  $\mathbf{t}_{\text{pcb\_SDO}} + \mathbf{t}_{\text{SU\_h}}$

The Clock Re-Timer data transfer completely eliminates the effect of buffer delays ( $t_{d\_BUFFER}$ ) and clock-to-data delays ( $t_{d\_CKDO}$ ); typically, the largest contributors in the overall delay computation. Furthermore, the actual values of  $t_{pcb\_RVS}$  and  $t_{pcb\_SDO}$

will get cancelled since they are routed through matched length traces. When using the Clock Re-Timer data transfer, the maximum SCLK frequency is limited by the ADC and the set up time  $(t_{SU\_h})$  of the host.

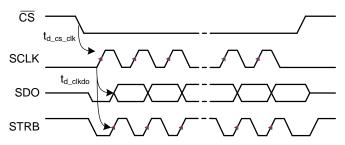

The waveform in Figure 4 illustrates the Clock Re-Timer data transfer. From the beginning, the SDO and STRB signals are aligned from the ADC even though they will have a delay with respect to the SCLK at the input of the ADC. As long as the SDO and the STRB are routed with matched traces, they will be aligned at the host. The STRB negative edge can be used reliably as the clock for capturing the SDO.

Figure 4. Clock Re-Timer Data Transfer

Clock Re-Timer can also be used to reflect SLCK and the following equation approximately shows the total time required for the overall data transfer, or the time for the CSn to be held active:

$$\mathbf{t}_{\text{data\_transfer}} = \mathbf{N} \cdot \mathbf{T}_{\text{clk}}$$

-  $\mathbf{t}_{\text{d\_ckdo}} + \mathbf{t}_{\text{d\_CS\_clk}}$

Where N is the number of bits,  $T_{clk}$  is the SCLK period, and  $t_{d\_cs\_clk}$  is the CS-to-SCLK delay. In the ADS8920B case, the STRB clock period is 15-ns, and  $t_{d\_cs\_clk}$  is 12-ns, resulting on a required data transfer period of 239-ns; meeting the maximum 330-ns read time supporting maximum throughput of 1-MSPS.

In summary, the Enhanced-SPI's Clock Re-Timer eliminates the effect of buffer or isolation delays and eases board layout as there is no need to locate the controller and the ADC extremely close. The SCLK frequency can be as high as the rates supported by the ADC, the host and intermediate buffers, allowing full-throughput data transfer.

Table 2. SAR ADCs Supporting Enhanced SPI's Clock Re-Timer

| Device   | Resolution | Data Rate | Description                                               |

|----------|------------|-----------|-----------------------------------------------------------|

| ADS8920B | 16-Bit     | 1-MSPS    | SAR ADC with integrated reference buffer and Enhanced-SPI |

| ADS8910B | 18-Bit     | 1-MSPS    | SAR ADC with integrated reference buffer and Enhanced-SPI |

| ADS8900B | 20-Bit     | 1-MSPS    | SAR ADC with integrated reference buffer and Enhanced-SPI |

| ADS9120  | 16-Bit     | 2.5-MSPS  | SAR ADC with Enhanced-SPI                                 |

| ADS9110  | 18-Bit     | 2-MSPS    | SAR ADC with Enhanced-SPI                                 |

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated