# Radiation Report

# Single-Event Effects Characterization of ADS1282-SP High-Resolution ADC

Sriram Narayanan, Wade VonBergen, Joel Cruz-Colon, Veera Narayanan

#### **ABSTRACT**

The single-event effects behavior of the ADS1282-SP, a high dynamic range analog-to-digital converter (ADC), is presented. No latch-up events were detected up to a linear energy transfer (LET) of 50.5MeV  $\times$  cm<sup>2</sup>/ mg at 85°C and 125°C, nor were any latch-up events detected up to an LET of 60.4MeV  $\times$  cm<sup>2</sup>/ mg at 85°C. The device exhibits a single event transient (SET) saturated cross-section of 3.7  $\times$  10<sup>-4</sup> cm<sup>2</sup>. For register upsets, the device exhibited a saturated cross-section of 1.3  $\times$  10<sup>-5</sup> cm<sup>2</sup>.

## **Table of Contents**

| 1 Overview                         |    |

|------------------------------------|----|

| 2 SEE Mechanisms                   | 3  |

| 3 Test Device and Evaluation Board |    |

| 4 Irradiation Facility and Setup   |    |

| 5 Test Setup and Procedures        | 11 |

| 6 SET Test Results                 |    |

| 7 SEL Test Results                 |    |

| 8 Conclusions                      | 19 |

| 9 Acknowledgment                   | 20 |

| 10 References                      |    |

| 11 Revision History                | 22 |

#### **Trademarks**

Kevlar® is a registered trademark of DuPont de Nemours. All trademarks are the property of their respective owners.

Overview INSTRUMENTS

www.ti.com

#### 1 Overview

High-resolution analog-to-digital converters (ADCs) play a critical role in signal conditioning for sensors with wide dynamic range. Examples of such applications include monitoring thermocouples, accelerometers, and precision instrumentation. However, the lack of space-grade high-dynamic range analog-to-digital converters has often been cited as an impediment to developing important space applications [1].

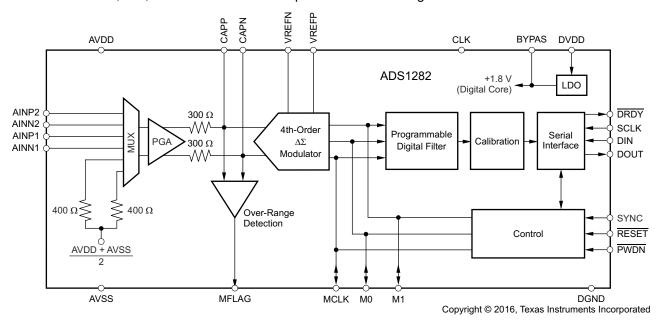

The ADS1282-SP is a high-resolution delta-sigma ADC for space applications. It offers up to 122dB SNR with a total harmonic distortion of –102dB, and integral nonlinearity (INL) of 0.5ppm [2]. The block diagram shown in Figure 1-1 includes a front-end programmable gain amplifier (PGA) with a gain range up to 64×, to fully exploit the wide dynamic range available in the ADC. The fast-responding overrange detection circuit provides indication if the differential input voltage exceeds the ADC full scale. Programmable digital filters include user-selectable Sinc filter, FIR, and an IIR filter. The output is available through an SPI interface.

Figure 1-1. ADS1282-SP Block Diagram

There are two power supplies on the ADS1282-SP: AVDD and DVDD. The supplies can be powered up in any sequence. The device requires a clock input to be supplied on the CLK pin. A 4MHz clock is used for the testing described in this document.

www.ti.com SEE Mechanisms

#### 2 SEE Mechanisms

This document presents an overview of the single event effect (SEE) testing and a summary of the observed results. Testing for single-event latch-up (SEL), single-event functional interrupt (SEFI) and single-event transient (SET) events was performed at the Cyclotron Institute at Texas A&M University using the K500 Cyclotron and the 15 MeV/n beam. The ASTM F1192 [4] and EIA/JESD57 [5] standards were used as reference for this testing. The test plan was outlined by Texas Instruments and the task was contracted to Aeroflex RAD [6].

The SEL testing was performed to determine the threshold for latch-up under worst-case temperature and voltage operating conditions, up to a LET of  $81 \text{MeV} \times \text{cm}^2/\text{mg}$ . Maximum fluence of  $10^7$  ions / cm² was used to irradiate at temperatures of  $85^{\circ}\text{C}$  and  $125^{\circ}\text{C}$ . The SEU rates were characterized for a given LET range between  $2.7 \text{MeV} \times \text{cm}^2/\text{mg}$  and  $52.3 \text{ MeV} \times \text{cm}^2/\text{mg}$  at a maximum fluence of  $10^6$  ions / cm² or until 100 SETs were recorded. Since the ADS1282-SP has configuration registers, the register SEU rates were characterized in addition to the data conversion SEU rates.

| Table 2 1. Overview information |                                                                              |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION                     | DEVICE INFORMATION                                                           |  |  |  |  |

| Ti Part Number                  | ADS1282-SP                                                                   |  |  |  |  |

| SMD Number                      | 5962-14231                                                                   |  |  |  |  |

| Device Function                 | Analog-to-digital conversion                                                 |  |  |  |  |

| Technology                      | 50HPA07                                                                      |  |  |  |  |

| Exposure Facility               | Radiation Effects Facility, Cyclotron, Texas A&M University                  |  |  |  |  |

| Heavy Ion Fluence per run       | 10 <sup>6</sup> ions/cm <sup>2</sup> to 10 <sup>7</sup> ions/cm <sup>2</sup> |  |  |  |  |

| Irradiation Temperature         | 85°C, and 125°C (for SEL testing)                                            |  |  |  |  |

Table 2-1. Overview Information (1)

Since the ADS1282-SP device does not operate at high voltages or high currents, single-event burn-out (SEB) and single-event gate-rupture (SEGR) events are not expected to be an issue. The primary single-event effect (SEE) events of interest in the ADS1282-SP are SEL, SEFI, and SET.

From a risk and impact point-of-view, the occurrence of an SEL is potentially the most disruptive SEE event and the biggest concern for space applications. In mixed technologies such as BiCMOS HPA07 250nm process used for the ADS1282-SP, the CMOS circuitry introduces a potential SEL susceptibility. SEL can occur if excess current injection caused by the passage of an energetic ion is high enough to trigger the formation of a parasitic cross-coupled PNP and NPN bipolar structure (formed between the p-substrate and n-well and n+ and p+ contacts) [7], [8]. The parasitic bipolar structure creates a high-conductance path (creating a steady-state current that is typically orders-of-magnitude higher than the normal operating current) between power and ground that persists (is *latched*) until power is removed or until the device is destroyed by the high-current state. For the design of the ADS1282-SP, SEL-susceptibility was reduced by maximizing the number of well and substrate ties in the CMOS portions of the layout. The design techniques applied for latch-up mitigation were sufficient as the ADS1282-SP exhibited no signs of SEL with heavy-ions of LET<sub>eff</sub> = 50.5 MeV×cm²/ mg at a fluence of 10<sup>7</sup> ions / cm² and a chip temperature of 125°C nor were any latch-up events detected up to an LET<sub>eff</sub> = 60.4MeV×cm²/ mg at 85°C.

In devices such as the ADS1282-SP delta-sigma ADC single events large enough to effect a circuit is expected to manifest either as an upset in the control logic or the signal chain itself causing either a system reset or misoperation, or, more likely, an error in the ADC output. SEFIs might occur if sequential circuits in the control logic, calibration or serial interface are upset by a single-event. Single-events occurring in the signal chain, preamplifier, modulator, LDO are likely to cause a short-lived error on output samples (a single sample or a small set of contiguous samples) with no other operational changes in the device performance.

<sup>(1)</sup> TI may provide technical, applications, or design advice, quality characterization, and reliability data or service providing these items shall not expand or otherwise affect Tl's warranties as set forth in the Texas Instruments Incorporated Standard Terms and Conditions of Sale for Semiconductor Products and no obligation or liability shall arise from Semiconductor Products and no obligation or liability shall arise from Tl's provision of such items.

## 3 Test Device and Evaluation Board

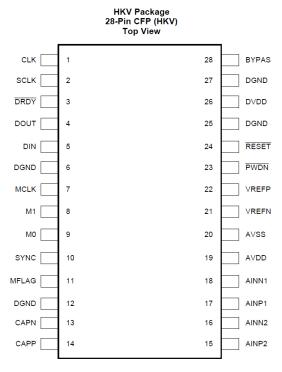

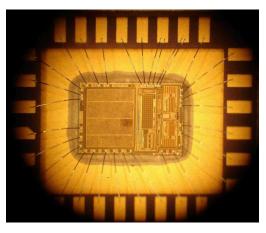

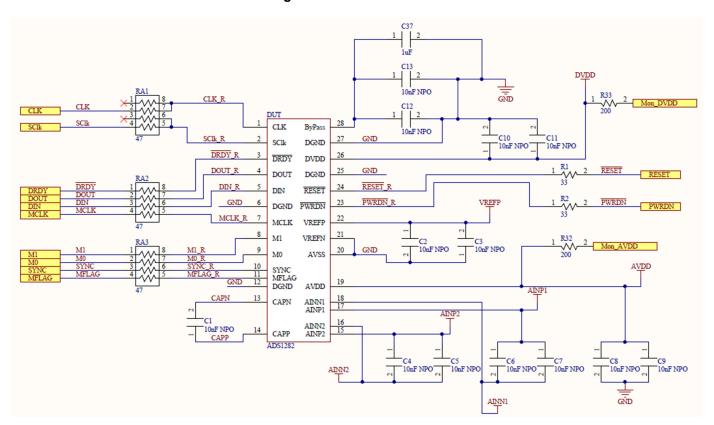

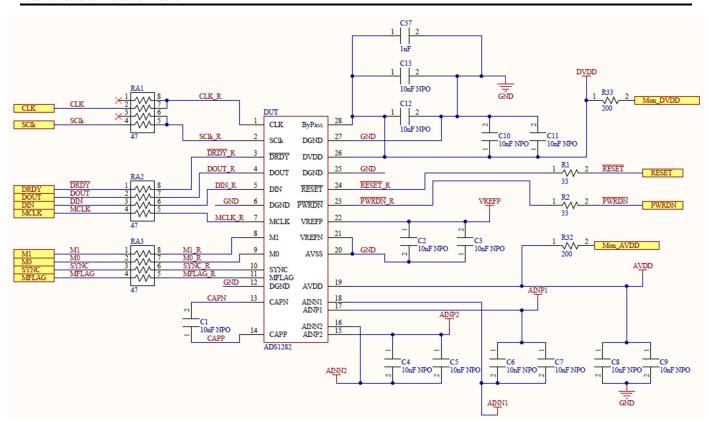

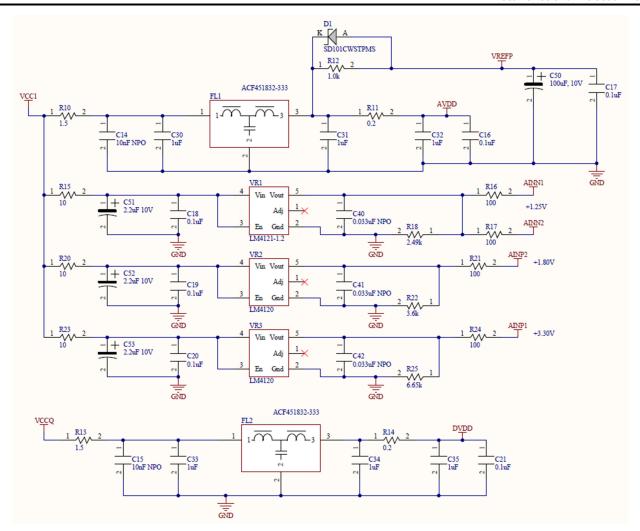

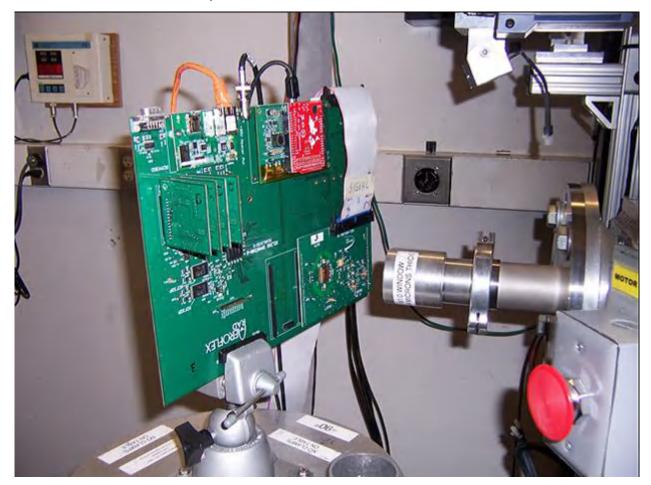

The ADS1282-SP is packaged in a 28-pin dual ceramic flat-pack (HKV) package. The pinout of this device is shown in Figure 3-1. Photographs of the device with and without the lid are shown in Figure 3-2. The test board used for the SEE testing is shown in Figure 3-3. The schematics of the device under test (DUT) test-board configurations are shown in Figure 3-4, Figure 3-5, and Figure 3-6.

Figure 3-1. ADS1282-SP Pinout Diagram

Figure A-1. De-processed ADS1282 DUT

Figure A-2. Received ADS1282 DUTs

Figure 3-2. Device Under Test (DUT) With and Without Lid

Figure 3-3. DUT Test Board

Figure 3-4. DUT Schematic, DVDD > 2.25V

Figure 3-5. DUT Schematic, DVDD < 2.25V

Figure 3-6. Input Power Circuit

# 4 Irradiation Facility and Setup

The SEE testing described in this test report was performed at the Cyclotron Institute at Texas A&M University (TAMU) using their K500 Cyclotron. The testing was performed in air using the 15 MeV/n beam. When necessary, beam degraders were inserted into the beam line to achieve the desired LET and a wider LET range for a given ion. The beam characteristics and dosimetry were provided by the Texas A&M heavy ion test facility. TAMU delivered the beam with a high degree of uniformity over a 1in diameter circular cross sectional area using the in-air test system. Uniformity was achieved by magnetic defocusing and by thin foil scattering. The beam uniformity and flux are determined using an array of five plastic scintillators coupled to photo multiplier tubes, located in the diagnostic chamber adjacent to and upstream from the target. Four of the five detectors are fixed in position and set up to measure beam particle counting rates continuously at four characteristic points 1.64 inches (41.7mm) away from the beam axis center. The fifth scintillator is inserted to measure the beam particle counting rate right at the beam axis and was removed to provide an unobstructed beam during testing. The control software determines the beam uniformity (ranging from 0% to 100%), axial gain (%), and beam flux (in particles/cm²/s) based on the scintillator counting rates. The parameters are displayed on the computer screen in the control room and are updated about once every second. For all beam experiments the air gap between the die surface and the ion port window was 40mm.

Figure 4-1. Test Fixture for SEE Testing

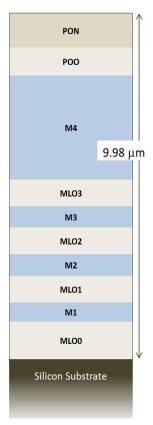

Figure 4-1 shows a photograph of the test fixture used for SEE testing. All DUT were de-lidded prior to testing and all exposures took place from the top surface providing a distance to the active layer in silicon, through the passivation and metallization layers of approximately 10µm.

## 4.1 Depth, Range, and LET<sub>eff</sub> Calculation

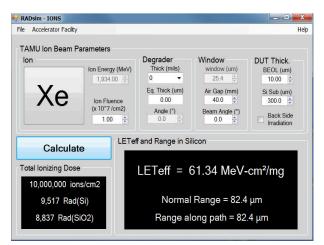

The ADS1282-SP is fabricated in the Texas Instruments high-performance analog 130-nm BiCMOS process (HPA07) with a back-end-of-line (BEOL) stack consisting of X levels of standard thickness aluminum metal on a Y-µm pitch, and a fourth level of thick aluminum. The total stack height from the surface of the passivation to the silicon surface is 10µm, based on nominal layer thickness as shown in Figure 4-2. No polyimide or other coating was present so the uppermost layer was the nitride passivation layer (PON). Accounting for energy loss through the 1-mil thick Aramica (Kevlar®) beam port window, the 40mm air gap, and the BEOL stack over the ADS1282-SP, the effective LET (LET<sub>eff</sub>) at the surface of the substrate and the depth and ion range was determined with the custom RADsim-IONS application (custom tool developed at Texas Instruments based on SRIM 2013 [9]) simulations for the two primary ions used for the experiments. The results are shown in Table 4-1. The stack was modeled as a homogeneous layer of silicon dioxide.

Figure 4-3. RADsim-IONS Application GUI

Figure 4-2. HPA07 Technology BEOL Stack Cross-Section on the ADS1282-SP

Generalized cross-section (left) of the HPA07 technology BEOL stack on the ADS1282-SP. GUI of RADsim-IONS application (right) used to determine key ion parameters: LET<sub>eff</sub>, depth, and range for a given ion type, energy, and stack. LET<sub>eff</sub> has been adjusted to account for beam degraders inserted into the beam line.

Irradiation Facility and Setup www.ti.com

# Table 4-1. lons and Angles Used in SEE Experiments

| ION TYPE | ANGLE OF INCIDENCE | DEPTH IN SILICON (μm) | RANGE IN SILICON (µm) | LET <sub>eff</sub> (MeV × cm <sup>2</sup> / mg) |

|----------|--------------------|-----------------------|-----------------------|-------------------------------------------------|

| Ne       | 0°                 | 250.1                 | 250.1                 | 2.7                                             |

| Ar       | 0°                 | 169.5                 | 169.5                 | 8.4                                             |

| Kr       | 0°                 | 106.8                 | 106.8                 | 28.3                                            |

| Ag       | 0°                 | 87.8                  | 87.8                  | 42.8                                            |

| Ag       | 32°                | 72.9                  | 86.0                  | 50.5                                            |

| Xe       | 0°                 | 82.4                  | 82.4                  | 52.3                                            |

| Xe       | 30°                | 70.0                  | 80.8                  | 60.4                                            |

# **5 Test Setup and Procedures**

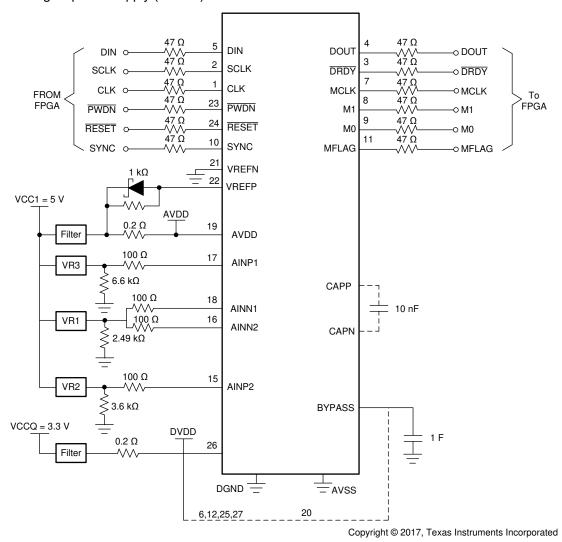

Figure 5-1 shows the test circuit that was used. The positive voltage reference, VREFP, and the analog power supply, AVDD, are driven by a filtered VCC1 power supply. The VCC1 power supply also provides input power to three voltage regulators: 3.3V, 1.25V, and 1.8V. The VCCQ1 power supply is filtered and provides the input power for the digital power supply (DVDD.)

Figure 5-1. Test Circuit

Test Setup and Procedures www.ti.com

## 5.1 SEE Testing Block Diagram

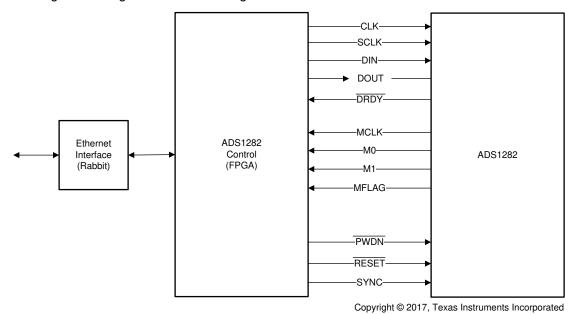

Figure 5-2 shows a block diagram of the test setup used for SEE testing. The inputs to the ADS1282-SP (DIN, SCLK, PWRDN\_N, RESET\_N, and SYNC) are connected to I/O pins on a Spartan 6 FPGA. The CLK operates at 4MHz and the SCLK operates at 2MHz. The outputs of the ADS1282-SP (DOUT, DRDY\_N, MCLK, M1, M0, and MFLAG) are also connected to I/O pins on the FPGA. The FPGA sends commands to the ADS1282-SP and executes reading and writing to ADS1282-SP registers.

Figure 5-2. SEE Testing Block Diagram

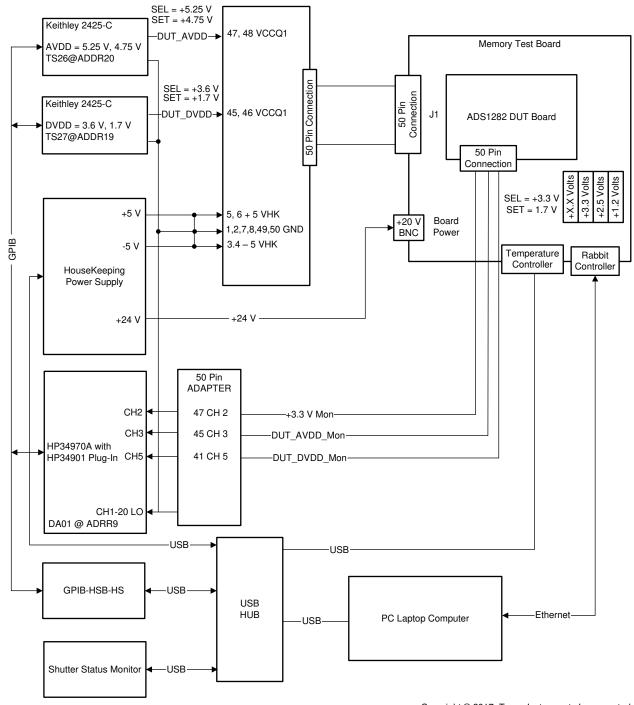

The SEE Test Setup for the TI ADS1282-SP is shown in Figure 5-3. Each TI ADS1282-SP is mounted on an individual DUT board that interfaces to the Memory Test Board. The Keithley 2425-C and 2420 Source Meters provide the DUT AVDD and DUT DVDD voltages and measures the associated currents. The Housekeeping Power Supply provides the ±5V and +24V for the Memory Test Board. The Agilent 34970A Data Acquisition Unit and Agilent 34901A Multiplexer Plug-in provide the capability to measure the DUT AVDD, DUT DVDD and 3.3V voltages at the DUT board. The Shutter Status Monitor records the beam shutter position. The laptop personal computer (PC) controls the test equipment and records the test data [6].

Copyright © 2017, Texas Instruments Incorporated

Figure 5-3. SEE Test Circuit

#### 5.2 Test Parameters

The following parameters were measured during SEL and SET testing at approximately 1-second intervals:

- DUT temperature

- AVDD voltage and AVDD current

- DVDD voltage and DVDD current

- 3.3V supply on the memory test board

- Beam shutter status

Table 5-1 lists the settings used for various parameters of the DUT and ion beam. Additionally, data conversion output was measured for SET testing.

Table 5-1. Settings Used for See Testing Parameters

| PARAMETER       | SEL                                  | SET                                                |

|-----------------|--------------------------------------|----------------------------------------------------|

| DUT temperature | 85°C and 125°C                       | Ambient                                            |

| AVDD            | +5.25V                               | +4.75V                                             |

| DVDD            | +3.6V                                | +1.7V                                              |

| Maximum fluence | 10 <sup>7</sup> ions/cm <sup>2</sup> | 10 <sup>6</sup> ions/cm <sup>2</sup> or 100 events |

#### **5.3 Test Conditions**

The register configuration for the ADS1282-SP used the default settings with the exception of the MUX Select bits in the Configuration 1 Register, and the Digital Filter Select bits in the Configuration 0 Register. For SEL testing, the MUX Select was configured to the default value of AINP1 and AINN1. For SET testing, the MUX Select was configured for the default value of AINP1 and AINN1, AINP2 and AINN2, and Internal Short via  $400\Omega$  as required [6].

For SEL testing, the Digital Filter Select was configured for the default value of Sinc + LPF Filter Blocks. For SET testing, the Digital Filter Select was configured for the default value of Sinc + LPF Filter Blocks and On-Chip Bypassed, Modulator Output Mode, as required [6].

Since SEE testing is performed in a noisy environment, a number of bits of conversion data were masked until no error events occurred without irradiating the ADS1282-SP [6]. The signals monitored during the test were routed to the control room (approximately 20-feet away) using shielded coaxial cable. Table 5-2 lists the ions, angles, and LETs used to characterize the SEE response of the ADS1282-SP devices.

Table 5-2. lons Used for SEL Characterization

| ION | ANGLE | LET <sub>eff</sub> (MeV × cm <sup>2</sup> /mg) |

|-----|-------|------------------------------------------------|

| Ne  | 0°    | 2.7                                            |

| Ar  | 0°    | 8.4                                            |

| Kr  | 0°    | 28.3                                           |

| Ag  | 0°    | 42.8                                           |

| Ag  | 32°   | 50.5                                           |

| Xe  | 0°    | 52.3                                           |

| Xe  | 30°   | 60.4                                           |

www.ti.com SET Test Results

## **6 SET Test Results**

A SET event is defined as the duration when the absolute value of the (sample – reference) is greater than the mask threshold [6]. As an example, if ten consecutive samples exceed the reference sample by greater than the mask threshold, then this is one error event and ten errors. The number of error events were used to determine the number of transients collected until the run is stopped [6].

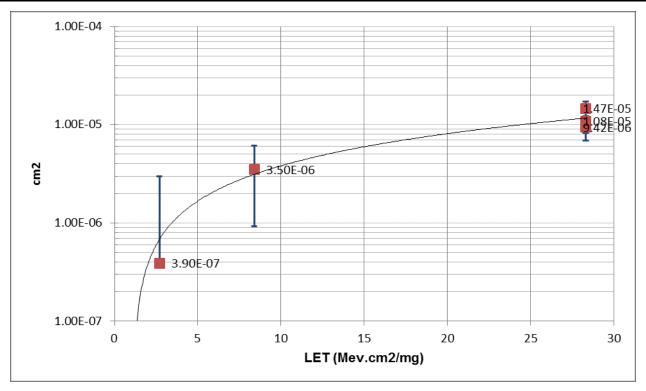

SET testing was performed with AVDD set to 4.75V and DVDD set to 1.7V. Figure 6-1 shows the cross-section for register upsets. Weibull fit parameters are shown in Table 6-1.

Table 6-1. Weibull Fit Parameters for Register Upsets

| - <b>I</b>                                    |         |  |  |  |

|-----------------------------------------------|---------|--|--|--|

| PARAMETER                                     | VALUE   |  |  |  |

| LET <sub>th</sub> (MeV × cm <sup>2</sup> /mg) | 1.4     |  |  |  |

| σ sat (cm <sup>2</sup> )                      | 1.3E-05 |  |  |  |

| Width, W (MeV × cm <sup>2</sup> /mg)          | 15      |  |  |  |

| Exponent, s                                   | 1.4     |  |  |  |

Table 6-2 lists the runs and test conditions as well as the result of the runs for DUT serial numbers 11 and 14. Note the DUT board with serial number 14 was configured with the bypass pin connected directly to DVDD.

Table 6-2. SET Run Log

|     | Table 0-2. SET Kull Log |             |                                                |                                   |                 |                 |        |        |                 |                  |                                     |

|-----|-------------------------|-------------|------------------------------------------------|-----------------------------------|-----------------|-----------------|--------|--------|-----------------|------------------|-------------------------------------|

| Run | SN                      | lon         | LET <sub>eff</sub> (MeV × cm <sup>2</sup> /mg) | Effective<br>Fluence<br>(ion/cm²) | AVDD<br>(Volts) | DVDD<br>(Volts) | Config | Errors | Error<br>Events | DRDY_N<br>Errors | Comments                            |

| 26  | 11                      | Ag at 0°    | 42.8                                           | 9.65E+05                          | 4.75            | 3               | AIN1   | 6306   | 400             | 2455             |                                     |

| 27  | 11                      | Ag at 0°    | 42.8                                           | 9.75E+05                          | 4.75            | 3               | AIN2   |        |                 |                  | Configuration Registers<br>Reset    |

| 28  | 11                      | Ag at 0°    | 42.8                                           | 1.02E+06                          | 5.25            | 3               | AIN1   | 5593   | 183             | 1661             |                                     |

| 29  | 11                      | Ag at 0°    | 42.8                                           | 9.44E+05                          | 5.25            | 3               | AIN2   |        |                 |                  | Configuration Registers<br>Reset    |

| 38  | 11                      | Xe at 0°    | 52.3                                           | 1.03E+06                          | 5.25            | 3               | AIN1   | 6679   | 222             | 1323             |                                     |

| 49  | 14                      | Xe at 0°    | 52.3                                           | 1.05E+06                          | 4.75            | 1.7             | AIN1   | 4288   | 176             | 4308             |                                     |

| 50  | 14                      | Xe at 0°    | 52.3                                           | 9.85E+05                          | 4.75            | 1.7             | AIN2   |        |                 |                  | Configuration Registers<br>Reset    |

| 51  | 14                      | Ar at 0°    | 8.4                                            | 9.67E+05                          | 4.75            | 1.7             | AIN1   | 6269   | 58              | 134              |                                     |

| 52  | 14                      | Ar at 0°    | 8.4                                            | 1.06E+06                          | 4.75            | 1.7             | AIN2   |        |                 |                  | Configuration Registers<br>Reset    |

| 53  | 14                      | Ne at<br>0° | 2.7                                            | 1.02E+06                          | 4.75            | 1.7             | AIN1   | 1      | 1               | 0                |                                     |

| 54  | 14                      | Ne at 0°    | 2.7                                            | 1.03E+06                          | 4.75            | 1.7             | AIN2   | 4      | 4               | 0                | No Configuration<br>Registers Reset |

| 55  | 14                      | Kr at 0°    | 28.3                                           | 1.00E+06                          | 4.75            | 1.7             | AIN1   | 3746   | 364             | 1010             |                                     |

| 56  | 14                      | Kr at 0°    | 28.3                                           | 1.01E+06                          | 4.75            | 1.7             | AIN2   |        |                 |                  | Configuration Registers<br>Reset    |

SET Test Results www.ti.com

Figure 6-1. Cross-Section for Register Upsets

To disambiguate noise from bit errors, the least significant bits of the data conversion output were masked until no error events were observed under no irradiation. The ion beam was subsequently turned on, and the output was observed until the specified number of transients were recorded or the fluence reached 10<sup>6</sup> ions/cm<sup>2</sup>.

During SEL testing and during some of the SET runs, single-event functional interrupts (SEFI) were observed, which required the device to be reset to restore functionality. Cross-section data on this error mode cannot be calculated with any confidence as the device reset under irradiation and some SEFI may clear before they are detected. At the same time, runs that exhibited a SEFI mode would inhibit the collection of further SET and thus will underestimate the error cross section [6].

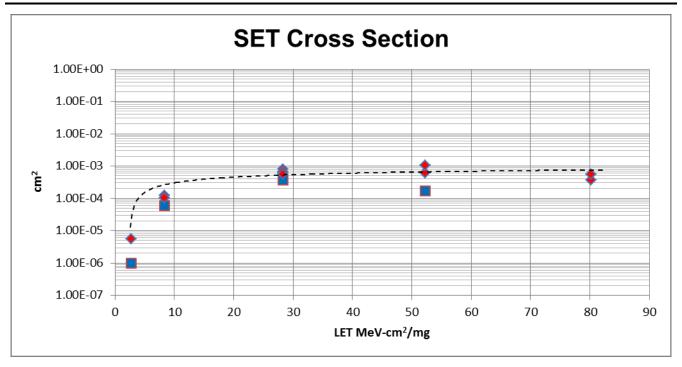

To avoid confounding of multiple error sources, the test runs in which register SEU's were observed were excluded when calculating the SET cross section. Figure 6-2 shows the resulting cross section, and the Weibull fit parameters are listed in Table 6-3.

Table 6-3. Weibull Fit Parameters

| PARAMETER                                     | VALUE   |

|-----------------------------------------------|---------|

| LET <sub>th</sub> (MeV × cm <sup>2</sup> /mg) | 2.7     |

| σ sat (cm²)                                   | 3.7E-04 |

| Width, W (MeV·cm²/mg)                         | 27      |

| Exponent, s                                   | 0.9     |

www.ti.com SET Test Results

Figure 6-2. SET Cross Section

SEL Test Results www.ti.com

#### 7 SEL Test Results

The device is SEL-free up to 50.5MeV × cm<sup>2</sup>/mg at 125°C. At 85°C, the device did not exhibit latch-up up to 60.4 MeV × cm<sup>2</sup>/ma.

Table 7-1 lists the runs and test conditions as well as the result of the runs for DUT serial numbers 11, 12, and 13. The SEL runs for serial numbers 11, 12, and 13 indicate the ADS1282-SP is latch-up immune to an LET of 50.5MeV × cm<sup>2</sup>/ mg at temperatures of 85°C and 125°C.

| Run | SN | lon       | LET <sub>eff</sub> (MeV × cm <sup>2</sup> /mg) | Effective Fluence (ion/<br>cm <sup>2</sup> ) | Temp (°C) | Result                                                                                                                                                                                 |

|-----|----|-----------|------------------------------------------------|----------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | 11 | Ag at 0°  | 42.8                                           | 1.00E+07                                     | 85        | No Latch-up.                                                                                                                                                                           |

| 31  | 11 | Ag at 32° | 50.5                                           | 9.97E+06                                     | 85        | No Latch-up                                                                                                                                                                            |

| 32  | 12 | Ag at 32° | 50.5                                           | 9.95E+06                                     | 85        | No Latch-up                                                                                                                                                                            |

| 33  | 13 | Ag at 32° | 50.5                                           | 9.99E+06                                     | 85        | No Latch-up                                                                                                                                                                            |

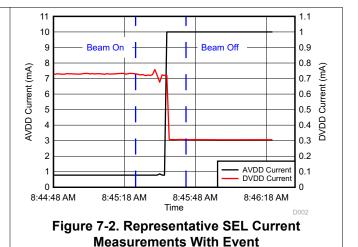

| 34  | 13 | Ag at 0°  | 42.8                                           | 1.00E+07                                     | 125       | No Latch-up. AVDD Current changed from 7.8mA to 8.6mA and the data output was 0x7FFFFFFF. After reset, the AVDD Current returned to normal and there was no degradation to the device. |

| 35  | 13 | Ag at 32° | 50.5                                           | 9.96E+06                                     | 125       | No Latch-up                                                                                                                                                                            |

| 36  | 12 | Ag at 32° | 50.5                                           | 1.00E+07                                     | 125       | No Latch-up                                                                                                                                                                            |

| 37  | 11 | Ag at 32° | 50.5                                           | 9.96E+06                                     | 125       | No Latch-up                                                                                                                                                                            |

| 39  | 11 | Xe at 0°  | 52.3                                           | 9.99E+06                                     | 85        | No Latch-up                                                                                                                                                                            |

| 40  | 11 | Xe at 30° | 60.4                                           | 1.00E+07                                     | 85        | No Latch-up                                                                                                                                                                            |

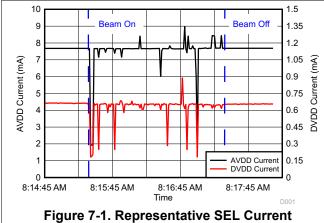

For SEL testing, the analog power supply, AVDD was set to 5.25V, and the digital power supply, DVDD, was set to 3.6V. Testing was performed at 85°C and 125°C with a control tolerance of ±5°C.

The observed results indicate that the ADS1282-SP is immune to latch-up to a LET of 50.5MeV × cm<sup>2</sup>/mg at a temperature of 125°C and up to 60.4MeV × cm<sup>2</sup>/mg at a temperature of 85°C.

Figure 7-1 and Figure 7-2 illustrate representative SEL current measurements for a run without event, and a run with an event.

**Measurements Without Event**

www.ti.com Conclusions

# **8 Conclusions**

TI's ADS1282-SP was tested for single-event effects. No latch-up was detected up to a LET of  $50.5 \text{MeV} \times \text{cm}^2/\text{mg}$  and temperatures of  $85^{\circ}\text{C}$  and  $125^{\circ}\text{C}$ . The device exhibited single-event upsets in the data converter output with a threshold of  $2.7 \text{MeV} \times \text{cm}^2/\text{mg}$ , and the saturated cross section was  $3.7 \text{E}-4 \text{ cm}^2$ .

Acknowledgment www.ti.com

# 9 Acknowledgment

The tests described in this paper were performed by Aeroflex RAD, Inc. The results from their testing are summarized in a report (see [6]), serving as the basis for the material reported in this application report.

www.ti.com References

## 10 References

1. L. Scheick, G. Allen and L. Edmonds, "Single-event effect qualification of 24-bit analog-to-digital converters," in IEEE Radiation Effects Data Workshop, San Francisco, CA, 2013.

- ADS1282-SP Radiation Tolerant High-Resolution Delta Sigma ADC (SBAS691).

- 3. Texas A&M University, Cyclotron Institute

- 4. Standard Guide for the Measurement of Single-Event Phenomena (SEP) Induced by Heavy Ion Irradiation of Semiconductor Devices, webpage.

- 5. JEDEC, Test Procedure for the Management of Single-Event Effects in Semiconductor Devices From Heavy Ion Irradiation, webpage.

- 6. Inc, Aeroflex RAD, SEE Test Report for Texas Instruments ADS1282-SP high resolution analog-to-digital converter (ADC), Aeroflex RAD Inc, Colorado Springs, CO, 1025.

- 7. M. Shoga and D. Binder, *Theory of single event latchup in complementary metal-oxide semiconductor integrated circuits* IEEE Trans. Nucl. Sci., vol. 33, no. 6, pp. 1714--1717, 1986.

- 8. G. Bruguier and J. Palau, "Single particle-induced latchup," IEEE Trans. Nucl. Sci, , vol. 43, no. 2, pp. 522-532, 1996.

- 9. Texas Instruments, Single Event Effects (SEE) Test Report of the TPS7H3301-SP, radiation report.

Revision History Www.ti.com

# 11 Revision History

| CI | hanges from Revision * (October 2017) to Revision A (April 2025)                               | Page |

|----|------------------------------------------------------------------------------------------------|------|

| •  | Updated the numbering format for tables, figures, and cross-references throughout the document | 1    |

| •  | Updated Table 4-1 with correct LET values                                                      | 9    |

| •  | Updated Table 7-1 with added runs 39 and 40                                                    | 18   |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated