#### UCD9222-EP

ZHCSBS2-OCTOBER 2013

# 具有 4 位, 6 位 或 8 位电压识别 (VID) 支持的数字脉宽调制 (PWM) 系统控制器

#### 查询样片: UCD9222-EP

#### 特性

- 完全可配置双输出非隔离直流/直流 PWM 控制器, 此控制器支持 TMS320C6670™ 和 TMS320C6678™ 数字信号处理器 (DSP) VID 接口

- 支持高达 2MHz 的开关频率,此时占空比分辨率为 250ps

- 高达 1mV 的闭环分辨率

- 用于改进瞬态性能的具有非线性增益的硬件加速,3级/3零补偿器

- 支持多个包含预偏置启动的软启动和软停止配置

- 支持电压裕度和定序

- 同步输入/输出引脚使多个 UCD92xx 器件之间的 DPWM 时钟保持一致

- 电源参数的 12 位数字监控包括:

- 输入电流和电压

- 输出电流和电压

- 每个功率级上的温度

- 辅助模数转换器 (ADC) 输入

- 多电平过流故障保护:

- 外部电流故障输入

- 模拟比较器监控电流感测电压

- 被持续数字监控的电流

- 过压和欠压故障保护

- 过热故障保护

#### 说明

UCD9222 是一款设计用于非隔离式直流/直流电源应用的双轨同步降压数字 PWM 控制器。 这个器件集成了用于直流/直流环路管理的专用电路,支持多达两个 VID 接口。 此外,UCS9222 具有闪存存储器和一个串口以支持可配置性、监控和管理。

支持几个电压识别 (VID) 模式,其中包括一个 4 位并口,一个 6 位接口和一个 8 位串口。

UCD9222 被设计用于提供针对非隔离式直流/直流转换器应用的多种所需特性,与此同时,通过减少外部电路来最 大限度地减少总体系统组件数量。此解决方案集成具有定序、裕度和跟踪的多环路管理,以针对总体系统效率进行 优化。此外,在无需添加额外组件的情况下,支持环路补偿和校准。

为了简化器件配置,提供德州仪器 (TI) Fusion Digital Power™ 设计工具。 这个基于 PC 的图形用户界面为该器件 提供了一个直观的界面。 这个工具使得设计人员能够为应用配置系统运行参数、将配置存储至片上非易失性存储器 并且观察每个功率级输出的频域和时域仿真。

TI还开发了多个互补功率级解决方案 - 从 UCD7k 系列中的离散驱动器到 PTD 系列中经完全测试的电源传动模块。这些解决方案已被开发用于为 UCD92xx 系列系统电源控制器提供补充。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. TMS320C6670, TMS320C6678, Fusion Digital Power, Auto-ID are trademarks of Texas Instruments.

• 支持纠错码 (ECC) 的增强型非易失性存储器

- 由具有一个内部稳压器控制器的单电源供电运行的 器件可实现宽电源电压范围内的运行

- 由 Fusion Digital Power™ 设计工具,一个基于 全功能 PC 的设计工具提供支持,以模拟、配置和 监控电源性能

应用范围

- 网络设备

- 电信设备

- 现场可编程门阵列 (FPGA), DSP 和存储器电源

#### 支持国防、航空航天、和医疗应用

- 受控基线

- 同一组装和测试场所

- 同一制造场所

- 在扩展(-55°C 至 115°C)温度范围内可用

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

### UCD9222-EP

FXAS **NSTRUMENTS**

www.ti.com.cn

ZHCSBS2-OCTOBER 2013

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

|      | ORDERING INFORMATION                        |                          |              |              |         |                     |                |  |  |  |  |

|------|---------------------------------------------|--------------------------|--------------|--------------|---------|---------------------|----------------|--|--|--|--|

| OPER | RATING TEMPERATURE<br>RANGE, T <sub>J</sub> | ORDERABLE PART<br>NUMBER | PIN<br>COUNT | SUPPLY       | PACKAGE | TOP SIDE<br>MARKING | VID NUMBER     |  |  |  |  |

|      | –55°C to 115°C                              | UCD9222WRGZREP           | 48-pin       | Reel of 2500 | QFN     | UCD9222EP           | V62/13622-01XE |  |  |  |  |

####

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                             | VALUE       | UNIT |

|---------------------------------------------|-------------|------|

| Voltage applied at V <sub>33D</sub> to DGND | -0.3 to 3.8 | V    |

| Voltage applied at V <sub>33A</sub> to AGND | -0.3 to 3.8 | V    |

| Voltage applied to any pin <sup>(2)</sup>   | -0.3 to 3.8 | V    |

| Storage temperature (T <sub>STG</sub> )     | –55 to 150  | °C   |

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings (1)only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages referenced to GND. (2)

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|         |                                                                      | MIN | NOM | MAX | UNIT |

|---------|----------------------------------------------------------------------|-----|-----|-----|------|

| V       | Supply voltage during operation, $V_{33D}$ , $V_{33DIO}$ , $V_{33A}$ | 3   | 3.3 | 3.6 | V    |

| $T_{J}$ | Operating junction temperature range                                 | -55 |     | 115 | °C   |

|         | Maximum junction temperature                                         |     |     | 125 | °C   |

#### THERMAL INFORMATION

|                    |                                                             | UCD9222-EP |        |

|--------------------|-------------------------------------------------------------|------------|--------|

|                    | THERMAL METRIC <sup>(1)</sup>                               | RGZ        | UNITS  |

|                    |                                                             | 48 PINS    |        |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 27.1       |        |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 12.9       |        |

| $\theta_{JB}$      | Junction-to-board thermal resistance <sup>(4)</sup>         | 4.3        | °C 111 |

| Ψυτ                | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.2        | °C/W   |

| ΨЈВ                | Junction-to-board characterization parameter <sup>(6)</sup> | 4.3        |        |

| $\theta_{JCbot}$   | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.6        |        |

有关传统和全新热度量的更多信息,请参阅 *IC 封装热度量* 应用报告 (文献号:ZHCA543)。 (1)

在 JESD51-2a 描述的环境中,按照 JESD51-7 的规定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然对流条件下的结至环 (2)境热阻抗。

通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-(3)88 中找到内容接近的说明。

(4)按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结至电路板的热阻。

结至顶部的特征参数,(ψ<sub>JT</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中描述的程序从仿真数据中提取出该 (5) 参数以便获得 θ」Α

\_ 结至电路板的特征参数,(ψ<sub>JB</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第7 章)中描述的程序从仿真数据中提取出该 (6) 参数以便获得 θ<sub>JA</sub>。 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI

(7)标准 G30-88 中找到了内容接近的说明。

**ELECTRICAL CHARACTERISTICS**

over operating junction temperature range (unless otherwise noted)

|                                                                 | PARAMETER                                                      | TEST CONDITIONS                                                      | MIN   | NOM   | MAX | UNIT |

|-----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------|-------|-------|-----|------|

| SUPPLY CURRE                                                    |                                                                |                                                                      |       |       |     |      |

| I <sub>V33</sub>                                                |                                                                | Total V33 supply current,<br>$V_{33A} = V_{33DIO} = 3.3 V$           |       | 54    | 80  | mA   |

| I <sub>V33DIO</sub>                                             | Supply surrent                                                 | V <sub>33DIO</sub> = 3.3 V                                           |       | 42    | 55  | mA   |

| I <sub>V33A</sub>                                               | Supply current                                                 | V <sub>33A</sub> = 3.3 V                                             |       | 8     | 15  | mA   |

| I <sub>V33DIO</sub>                                             |                                                                | $V_{33DIO} = 3.3$ V storing configuration parameters in flash memory |       | 52    | 65  | mA   |

| INTERNAL REG                                                    | ULATOR CONTROLLER INPUTS/OU                                    | TPUTS                                                                |       |       |     |      |

| V <sub>33</sub>                                                 | 3.3-V linear regulator                                         | Emitter of NPN transistor                                            | 3.25  | 3.3   | 3.6 | V    |

| V <sub>33FB</sub>                                               | 3.3-V linear regulator feedback                                |                                                                      |       | 4     | 4.6 | V    |

| I <sub>V33FB</sub>                                              | Series pass base drive                                         | V <sub>IN</sub> = 12 V                                               | 0.2   | 0.4   | 8   | mA   |

| Beta                                                            | Series NPN pass device                                         |                                                                      | 40    | 100   |     |      |

| EXTERNALLY S                                                    | UPPLIED 3.3 V POWER                                            |                                                                      | 1     |       |     |      |

| V <sub>33D</sub> , V <sub>33DIO1</sub> ,<br>V <sub>33DIO2</sub> | Digital 3.3-V power                                            | $T_J = 25^{\circ}C$                                                  | 3.0   |       | 3.6 | V    |

| V33A                                                            | Analog 3.3-V power                                             | $T_J = 25^{\circ}C$                                                  | 3.0   |       | 3.6 | V    |

| ERROR AMPLIF                                                    | IER INPUTS EAPn, EANn                                          |                                                                      | L.    |       |     | -    |

| V <sub>CM</sub>                                                 | Common mode voltage each pin                                   |                                                                      | 0     |       | 1.8 | V    |

| V <sub>ERROR</sub>                                              | Internal error voltage range                                   | AFE_GAIN field of CLA_GAINS = 1X <sup>(1)</sup>                      | -256  |       | 248 | mV   |

| EAP-EAN                                                         | Error voltage digital resolution                               | AFE_GAIN field of CLA_Gains = 8X                                     |       | 1     |     | mV   |

| R <sub>EA</sub>                                                 | Input impedance                                                | Ground reference, $T_J = 25^{\circ}C$                                |       | 1.5   |     | MΩ   |

| IOFFSET                                                         | Input offset current                                           | 1 kΩ source impedance, $T_J = 25^{\circ}C$                           | -5    |       | 5   | μA   |

| Vref 10-bit DAC                                                 |                                                                |                                                                      |       |       | 1   |      |

| V <sub>ref</sub>                                                | Reference voltage setpoint                                     |                                                                      | 0     |       | 1.7 | V    |

| V <sub>refres</sub>                                             | Reference voltage resolution                                   |                                                                      |       | 1.56  |     | mV   |

|                                                                 | S CS1A, CS2A, VinMon, linMon, Vtra                             | ack, Temp1, Temp2, Addr0, Addr1                                      |       |       | 1   |      |

| V <sub>ADC_RANGE</sub>                                          | Measurement range for voltage monitoring                       | Inputs: VinMon, IinMon, Vtrack, Temp1,<br>Temp2, CS1A, CS2A          | 0     |       | 2.6 | V    |

| Voffset                                                         | input offset voltage                                           |                                                                      | -27   |       | 27  | mV   |

| V <sub>OC_THRS</sub>                                            | Over-current comparator threshold voltage range <sup>(2)</sup> | Inputs: CS1A, CS2A                                                   | 0.032 |       | 2   | V    |

| V <sub>OC_RES</sub>                                             | Over-current comparator threshold voltage range                | Inputs: CS1A, CS2A                                                   |       | 31.25 |     | mV   |

| Temp <sub>internal</sub>                                        | Internal temperature sense accuracy                            | Over range from 0°C to 100°C                                         | -15   |       | 15  | °C   |

| INL                                                             | ADC integral nonlinearity                                      | $T_{J} = -40^{\circ}C \text{ to } 115^{\circ}C$                      | -2.5  |       | 2.5 | mV   |

| l <sub>ikg</sub>                                                | Input leakage current                                          | 3 V applied to pin                                                   |       |       | 100 | nA   |

| R <sub>IN</sub>                                                 | Input impedance                                                | Ground reference                                                     |       | 8     |     | MΩ   |

| C <sub>IN</sub>                                                 | Current sense input capacitance                                |                                                                      |       | 10    |     | pF   |

(1) See the UCD92xx PMBus Command Reference for the description of the AFE\_GAIN field of CLA\_GAINS command.

(2) Can be disabled by setting to '0'

ZHCSBS2-OCTOBER 2013

www.ti.com.cn

STRUMENTS

EXAS

### **ELECTRICAL CHARACTERISTICS (Continued)**

over operating junction temperature range (unless otherwise noted)

|                         | PARAMETER                                            | TEST CONDITIONS                                                                                         | MIN                         | NOM MAX                       | UNIT     |

|-------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|----------|

| DIGITAL INPL            | JTS/OUTPUTS                                          | · · · · ·                                                                                               |                             |                               |          |

| V <sub>OL</sub>         | Low-level output voltage                             | I <sub>OL</sub> = 6 mA <sup>(1)</sup> , V <sub>33DIO</sub> = 3 V                                        |                             | Dgnd<br>+0.3                  | V        |

| V <sub>OH</sub>         | High-level output voltage                            | $I_{OH}$ = -6 mA <sup>(2)</sup> , V <sub>33DIO</sub> = 3 V                                              | V <sub>33DIO</sub><br>-0.6V |                               | V        |

| V <sub>IH</sub>         | High-level input voltage                             | $V_{33DIO} = 3V$                                                                                        | 2.1                         | 3.6                           | V        |

| V <sub>IL</sub>         | Low-level input voltage                              | V <sub>33DIO</sub> = 3.5 V                                                                              |                             | 1.4                           | V        |

| SYSTEM PER              | FORMANCE                                             |                                                                                                         |                             |                               |          |

| V <sub>RESET</sub>      | Voltage where device comes out of reset              | V <sub>33D</sub> Pin                                                                                    | 2.3                         | 2.4                           | V        |

| t <sub>RESET</sub>      | Pulse width needed for reset                         | nRESET pin                                                                                              | 2                           |                               | μs       |

| V <sub>RefAcc</sub>     | Setpoint reference accuracy                          | Vref commanded to be 1V, at 25°C AFEgain = 4, 1V input to EAP/N measured at output of the EADC $^{(3)}$ | -10                         | 10                            | mV       |

|                         | Setpoint reference accuracy over temperature         | –55°C to 115°C                                                                                          | -40                         | 40                            | mV       |

| V <sub>DiffOffset</sub> | Differential offset between gain settings            | AFEgain = 4 compared to<br>AFEgain = 1, 2, or 8                                                         | -4                          | 4                             | mV       |

| t <sub>Delay</sub>      | Digital compensator delay                            |                                                                                                         | 240                         | 240 + 1<br>switching<br>cycle | ns       |

| F <sub>SW</sub>         | Switching frequency                                  |                                                                                                         | 15.260                      | 2000                          | kHz      |

|                         | Accuracy                                             |                                                                                                         | -5%                         | 5%                            |          |

| Duty                    | Maximum and minimum duty cycle                       |                                                                                                         | 0%                          | 100%                          |          |

| V <sub>33</sub> Slew    | Minimum V <sub>33</sub> slew rate                    | V33 slew rate between 2.3V and 2.9V,T_J = -40°C to 115°C                                                | 0.25                        |                               | V/ms     |

| t <sub>retention</sub>  | Retention of configuration parameters <sup>(4)</sup> | T <sub>J</sub> = 25 °C                                                                                  | 100                         |                               | Years    |

| Write_Cycles            | Number of nonvolatile erase/write cycles             | T <sub>J</sub> = 25 °C                                                                                  | 20                          |                               | K cycles |

|                         |                                                      | All rails configured to accept 4-bit VID messages <sup>(5)</sup>                                        |                             | 1                             |          |

| Rate <sub>VID</sub>     | Max VID message rate                                 | All rails configured to accept 6-bit VID messages <sup>(5)</sup>                                        |                             | 4                             | msg/msec |

|                         |                                                      | All rails configured to accept 8-bit VID messages <sup>(6)</sup>                                        |                             | 4                             |          |

The maximum I<sub>OL</sub>, for all outputs combined, should not exceed 12 mA to hold the maximum voltage drop specified. (1)

The maximum I<sub>OL</sub>, for all outputs combined, should not exceed 48 mA to hold the maximum voltage drop specified. With default device calibration. PMBus calibration can be used to improve the regulation tolerance. The data retention specification is based on accelerated stress testing at 170°C for 420 hours and using an Arrhenius model with (2) (3) (4) activation energy of 0.6 eV.

VID message rate on each interface. Measured over a 1.0 msec interval (5)

VID message rate on PMBus interface. (6)

#### ADC MONITORING INTERVALS AND RESPONSE TIMES

The ADC operates in a continuous conversion sequence that measures each rail's output voltage and output current, plus six other variables (input voltage, input current, internal temperature, tracking source, and two external temperature sensors). The length of the sequence is determined by the number of output rails (NumRails) configured for use. The time to complete the monitoring sampling sequence is give by the formula:  $t_{ADC} = t_{ADC} \times (2 \times \text{NumRAILS} + 6)$

|                      | PARAMETER              | TEST CONDITIONS                                                                          | MIN   | TYP  | MAX   | UNIT |

|----------------------|------------------------|------------------------------------------------------------------------------------------|-------|------|-------|------|

| t <sub>ADC</sub>     | ADC single-sample time |                                                                                          |       | 3.84 |       | μs   |

| t <sub>ADC_SEQ</sub> | ADC sequencer interval | Min = $2 \times 1$ Rail + $6 = 8$ samples<br>Max = $2 \times 2$ Rails + $6 = 10$ samples | 30.72 |      | 38.40 | μs   |

The most recent ADC conversion results are periodically converted into the proper measurement units (volts, amperes, degrees), and each measurement is compared to its corresponding fault and warning limits. The monitoring operates asynchronously to the ADC, at intervals shown in the table below.

|                     | PARAMETER                          | TEST CONDITIONS | MIN TYP                | MAX | UNIT |

|---------------------|------------------------------------|-----------------|------------------------|-----|------|

| t <sub>Vout</sub>   | Output voltage monitoring interval |                 | 200                    |     | μs   |

| t <sub>lout</sub>   | Output current monitoring interval |                 | 200×N <sub>Rails</sub> |     | μs   |

| t <sub>Vin</sub>    | Input voltage monitoring interval  |                 | 1                      |     | ms   |

| t <sub>lin</sub>    | Input current monitoring interval  |                 | 1                      |     | ms   |

| t <sub>TEMP</sub>   | Temperature monitoring interval    |                 | 100                    |     | ms   |

| t <sub>AUXADC</sub> | Auxiliary ADC monitoring interval  |                 | 100                    |     | ms   |

Because the ADC sequencer and the monitoring comparisons are asynchronous to each other, the response time to a fault condition depends on where the event occurs within the monitoring interval and within the ADC sequence interval. Once a fault condition is detected, some additional time is required to determine the correct action based on the FAULT\_RESPONSE code, and then to perform the appropriate response. The following table lists the worse-case fault response times.

|                                        | PARAMETER                                                                   | TEST CONDITIONS                                                                                      | ТҮР  | MAX<br>no VID           | MAX<br>/w VID <sup>(1)</sup> | UNIT |

|----------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|-------------------------|------------------------------|------|

| t <sub>OVF</sub> ,<br>t <sub>UVF</sub> | Over-/under-voltage fault response time during normal operation             | Normal regulation, no PMBus activity, 4 stages enabled                                               |      | 250                     | 800                          | μs   |

| t <sub>OVF</sub> ,<br>t <sub>UVF</sub> | Over-/under-voltage fault response time, during data logging                | During data logging to nonvolatile memory <sup>(2)</sup>                                             |      | 800                     | 1000                         | μs   |

| t <sub>OVF</sub> ,<br>t <sub>UVF</sub> | Over-/under-voltage fault response time, when tracking or sequencing enable | During tracking and soft-start ramp.                                                                 |      | 400                     |                              | μs   |

| t <sub>OCF</sub> ,<br>t <sub>UCF</sub> | Over-/under-current fault response time during normal operation             | Normal regulation, no PMBus activity,<br>4 stages enabled 75% to 125% current<br>step <sup>(3)</sup> |      | 100 +<br>(600 × NRails) | 5000                         | μs   |

| t <sub>OCF</sub> ,<br>t <sub>UCF</sub> | Over-/under-current fault response time, during data logging                | During data logging to nonvolatile<br>memory 75% to 125% current step                                |      | 600 +<br>(600 × NRails) | 5000                         | μs   |

| t <sub>OTF</sub>                       | Over-temperature fault response time                                        | Temperature rise of 10°C/sec, at OT threshold                                                        | 1.60 |                         |                              | sec  |

| t <sub>3-State</sub>                   | Time to tristate the PWM output after a shutdown is initiated               | DRIVER_CONFIG = 0x01                                                                                 | 5.5  |                         |                              | μs   |

(1) Controller receiving VID commands at a rate of 4000 msg/sec.

<sup>(2)</sup> During a STORE\_DEFAULT\_ALL command, which stores the entire configuration to nonvolatile memory, the fault detection latency can be up to 10 ms.

<sup>(3)</sup> Because the current measurement is averaged with a smoothing filter, the response time to an over-current condition depends on a combination of the time constant (T) from Table 3, the recent measurement history, and how much the measured value exceeds the over-current limit.

#### HARDWARE FAULT DETECTION LATENCY

The controller contains hardware fault detection circuits that are independent of the ADC monitoring sequencer.

|                    | PARAMETER                                                             | TEST CONDITIONS                           | MAX TIME | UNIT             |

|--------------------|-----------------------------------------------------------------------|-------------------------------------------|----------|------------------|

| t <sub>FAULT</sub> | Time to disable DPWM output base on active FAULT pin signal           | High level on FAULT pin                   | 18       | μs               |

| t <sub>CLF</sub>   | Time to disable the DPWM A output based on internal analog comparator | Step change in CS voltage from 0V to 2.5V | 4        | Switch<br>Cycles |

#### PMBUS/SMBUS/I<sup>2</sup>C

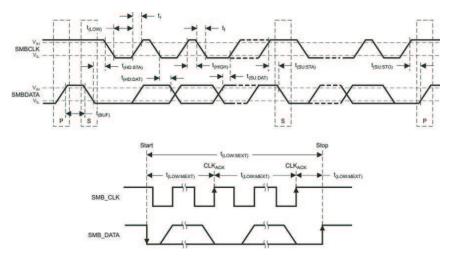

The timing characteristics and timing diagram for the communications interface that supports I2C, SMBus and PMBus are shown below.

Figure 1. I<sup>2</sup>C/SMBus/PMBus Timing in Extended Mode Diagram

#### I<sup>2</sup>C/SMBus/PMBus TIMING REQUIREMENTS

$T_{\rm J}$  = –55°C to 115°C, 3 V <  $V_{33}$  < 3.6 V, typical values at  $T_{\rm J}$  = 25°C

|                         | PARAMETER                              | TEST CONDITIONS                                                                                   | MIN  | TYP | MAX  | UNIT |

|-------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|------|-----|------|------|

| f <sub>SMB</sub>        | SMBus/PMBus operating frequency        | Slave mode; SMBC 50% duty cycle                                                                   | 10   |     | 1000 | kHz  |

| f <sub>I2C</sub>        | I C operating frequency                | Slave mode; SCL 50% duty cycle                                                                    | 10   |     | 1000 | kHz  |

| t <sub>(BUF)</sub>      | Bus free time between start and stop   |                                                                                                   | 5    |     |      | μs   |

| t <sub>(HD:STA)</sub>   | Hold time after (repeated) start       |                                                                                                   | 0.3  |     |      | μs   |

| t <sub>(SU:STA)</sub>   | Repeated start setup time              |                                                                                                   | 0.3  |     |      | μs   |

| t <sub>(SU:STO)</sub>   | Stop setup time                        |                                                                                                   | 0.3  |     |      | μs   |

| t <sub>(HD:DAT)</sub>   | Data hold time                         | Receive mode                                                                                      | 0    |     |      | ns   |

| t <sub>(SU:DAT)</sub>   | Data setup time                        |                                                                                                   | 55   |     |      | ns   |

| t(TIMEOUT)              | Error signal/detect                    | See <sup>(1)</sup>                                                                                |      |     | 35   | ms   |

| t <sub>(LOW)</sub>      | Clock low period                       |                                                                                                   | 0.55 |     |      | μs   |

| t <sub>(HIGH)</sub>     | Clock high period                      | See <sup>(2)</sup>                                                                                | 0.3  |     | 50   | μs   |

| t <sub>(LOW:SEXT)</sub> | Cumulative clock low slave extend time | See <sup>(3)</sup>                                                                                |      |     | 25   | ms   |

| t <sub>FALL</sub>       | Clock/data fall time                   | Rise time $t_{RISE}$ = $V_{ILMAX}$ – 0.15) to $(V_{IHMIN}$ + 0.15) , $T_{\rm J}$ = -40°C to 115°C |      |     | 1000 | ns   |

<sup>(1)</sup>

The UCD9222 times out when any clock low exceeds  $t_{(TIMEOUT)}$ .  $t_{(HIGH)}$ , max, is the minimum bus idle time. SMBC = SMBD = 1 for t > 50 ms causes reset of any transaction involving UCD9222 that is (2)in progress.

t<sub>(LOW:SEXT)</sub> is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop. (3)

#### I<sup>2</sup>C/SMBus/PMBus TIMING REQUIREMENTS (continued)

$T_{J} = -55^{\circ}C$  to 115°C, 3 V <  $V_{33}$  < 3.6 V, typical values at  $T_{J} = 25^{\circ}C$

|                   | PARAMETER            | TEST CONDITIONS                                                                     | MIN | TYP | MAX  | UNIT |

|-------------------|----------------------|-------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>RISE</sub> | Clock/data rise time | Fall time $t_{FALL}$ = 0.9 $V_{33}$ to $(V_{ILMAX}-0.15)$ , $T_J$ = - 40°C to 115°C |     |     | 1000 | ns   |

| C <sub>IN</sub>   |                      |                                                                                     |     |     |      |      |

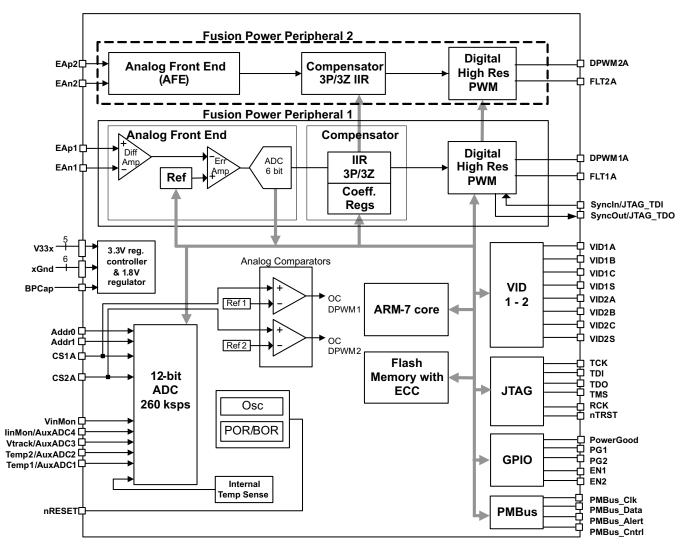

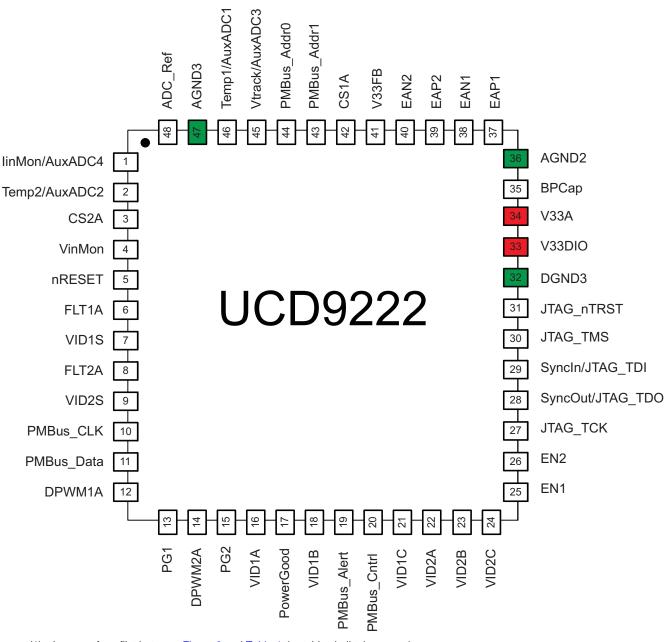

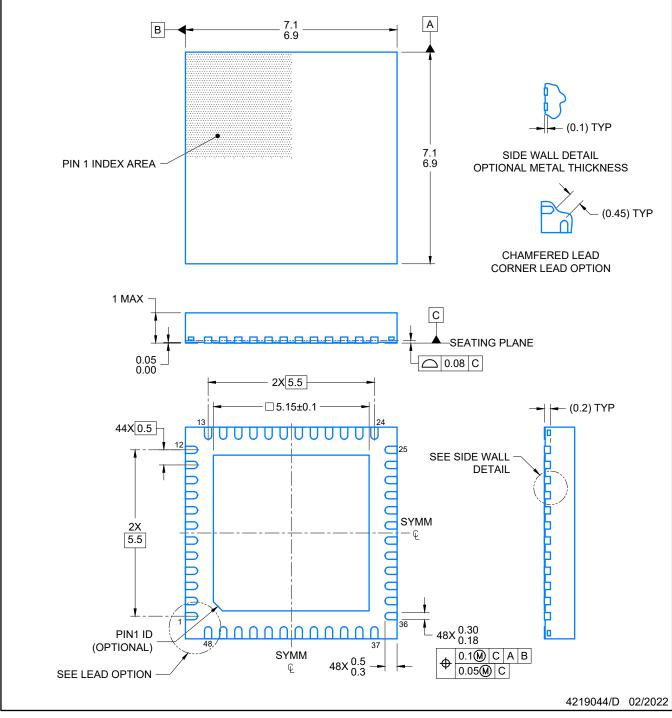

#### FUNCTIONAL BLOCK DIAGRAM

(1) In case of conflict between Figure 2 and Table 1 the table shall take precedence

(2) Preliminary versions of this data sheet prior to June 14, 2010 had a different definition for pins 17, 18, and 21. Board designs made with that earlier pinout should be updated.

Figure 2. Pin Assignment Diagram

www.ti.com.cn

### UCD9222-EP ZHCSBS2-OCTOBER 2013

#### Table 1. PIN FUNCTIONS

| PIN NO. | PIN LABEL        | DESCRIPTION                                                                       |  |  |  |  |  |

|---------|------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | linMon/AuxADC4   | Input current monitor, or Auxiliary ADC input 4                                   |  |  |  |  |  |

| 2       | Temp2/AuxADC2    | Temperature sense input for Rail 2, or Auxiliary ADC input 2                      |  |  |  |  |  |

| 3       | CS2A             | Power stage 2A current sense input and input to analog comparator 2               |  |  |  |  |  |

| 4       | VinMon           | Input voltage monitor                                                             |  |  |  |  |  |

| 5       | nRESET           | Active low device reset input. Pull up to 3.3V with a 10k ohm resistor            |  |  |  |  |  |

| 6       | FLT1A            | Fault indicator for stage 1A                                                      |  |  |  |  |  |

| 7       | VID1S            | VID Select pin for Rail 1                                                         |  |  |  |  |  |

| 8       | FLT2A            | Fault indicator for stage 2A                                                      |  |  |  |  |  |

| 9       | VID2S            | VID Select pin for Rail 2                                                         |  |  |  |  |  |

| 10      | PMBus_Clk        | PMBus Clock. Pull up to 3.3V with a 2k ohm resistor                               |  |  |  |  |  |

| 11      | PMBus_Data       | PMBus Data. Pull up to 3.3V with a 2k ohm resistor                                |  |  |  |  |  |

| 12      | DPWM1A           | Digital Pulse Width Modulator output 1A                                           |  |  |  |  |  |

| 13      | PG1              | Rail 1 Power Good Indicator                                                       |  |  |  |  |  |

| 14      | DPWM2A           | Digital Pulse Width Modulator output 2A                                           |  |  |  |  |  |

| 15      | PG2              | Rail 2 Power Good Indicator                                                       |  |  |  |  |  |

| 16      | VID1A            | VID input pin for Rail 1 – least significant bit                                  |  |  |  |  |  |

| 17      | PowerGood        | Power Good Indication                                                             |  |  |  |  |  |

| 18      | VID1B            | VID input pin for Rail 1                                                          |  |  |  |  |  |

| 19      | PMBus_Alert      | PMBus Alert. Pull up to 3.3V with a 10k ohm resistor                              |  |  |  |  |  |

| 20      | PMBus_Cntrl      | PMBus Control. Pull up to 3.3V with a 10k ohm resistor                            |  |  |  |  |  |

| 21      | VID1C            | VID input pin for Rail 1 – most significant bit                                   |  |  |  |  |  |

| 22      | VID2A            | VID input pin for Rail 2 – least significant bit                                  |  |  |  |  |  |

| 23      | VID2B            | VID input pin for Rail 2                                                          |  |  |  |  |  |

| 24      | VID2C            | VID input pin for Rail 2 – most significant bit                                   |  |  |  |  |  |

| 25      | EN1              | Rail 1 Enable                                                                     |  |  |  |  |  |

| 26      | EN2              | Rail 2 Enable                                                                     |  |  |  |  |  |

| 27      | JTAG_TCK         | JTAG Test Clock                                                                   |  |  |  |  |  |

| 28      | SyncOut/JTAG_TDO | Mux'ed pin JTAG Test Data Output, DPWM Sync Output                                |  |  |  |  |  |

| 29      | Syncln/JTAG_TDI  | Mux'ed pin – JTAG Test Data In, DPWM Sync Input                                   |  |  |  |  |  |

| 30      | JTAG_TMS         | JTAG Test mode select. Pull up to 3.3V with a 10k ohm resistor                    |  |  |  |  |  |

| 31      | (JTAG) nTRST     | JTAG Test Reset – Tie to ground with a 10k ohm resistor                           |  |  |  |  |  |

| 32      | Dgnd3            | Digital Ground                                                                    |  |  |  |  |  |

| 33      | V33DIO           | 3.3V supply for Digital I/O and Core                                              |  |  |  |  |  |

| 34      | V33A             | Analog 3.3V supply                                                                |  |  |  |  |  |

| 35      | BPCap            | 1.8V Bypass Capacitor – tie 0.1 µF cap to analog ground                           |  |  |  |  |  |

| 36      | Agnd2            | Analog ground                                                                     |  |  |  |  |  |

| 37      | EAp1             | Error analog, differential voltage, Positive channel 1 input                      |  |  |  |  |  |

| 38      | EAn1             | Error analog, differential voltage, Negative channel 1 input                      |  |  |  |  |  |

| 39      | EAp2             | Error analog, differential voltage, Positive channel 2 input                      |  |  |  |  |  |

| 40      | EAn2             | Error analog, differential voltage, Negative channel 2 input                      |  |  |  |  |  |

| 41      | V33FB            | Connection to the base of 3.3V linear regulator transistor (no connect if unused) |  |  |  |  |  |

| 42      | CS1A             | Power stage 1A current sense input and input to analog comparator 1               |  |  |  |  |  |

| 42      | Addr1            | Power stage TA content sense input and input to analog comparator T               |  |  |  |  |  |

| 43      | Addr0            | PMBus Address sense. Channel 0.                                                   |  |  |  |  |  |

| 44      | Vtrack/AuxADC3   | Tracking voltage input, or Auxiliary ADC input 3                                  |  |  |  |  |  |

| 45      | Temp1/AuxADC1    |                                                                                   |  |  |  |  |  |

| 40      |                  | Temperature sense input for Rail 1, or Auxiliary ADC input 1                      |  |  |  |  |  |

UCD9222-EP ZHCSBS2-OCTOBER 2013

www.ti.com.cn

**INSTRUMENTS**

**Texas**

#### Table 1. PIN FUNCTIONS (continued)

| PIN NO.  | PIN LABEL                                                              | DESCRIPTION                                                 |  |  |  |

|----------|------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| 48       | ADC_Ref                                                                | ADC Reference. Tie to analog ground through 0.1µF capacitor |  |  |  |

| PowerPad | PowerPad It is recommended that this pad be connected to analog ground |                                                             |  |  |  |

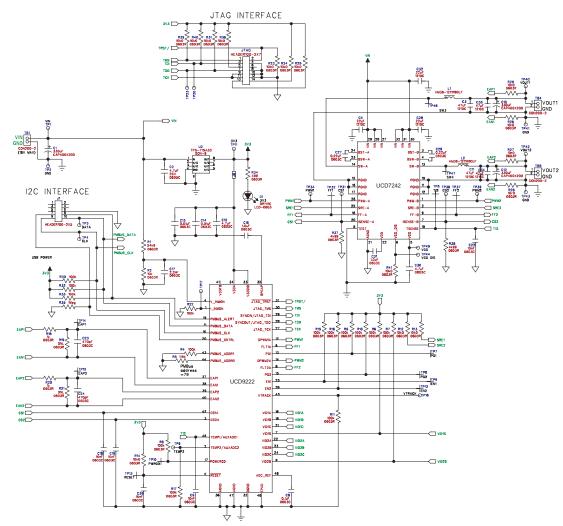

#### **TYPICAL APPLICATION SCHEMATIC**

Figure 3 shows the UCD9222 power supply controller as part of a system that provides the regulation of two independent power supplies. The loop for each power supply is created by the respective voltage outputs feeding into the differential voltage error ADC (EADC) inputs, and completed by DPWM outputs feeding into the gate drivers for each power stage.

The  $\pm V_{sense}$  rail signals must be routed to the EAp/EAn input that matches the DPWM number that controls the output power stage. For example, the power stage driven by DPWM1A must have its feedback routed to EAP1 and EAN1.

Figure 3. Typical Application Schematic

#### FUNCTIONAL OVERVIEW

The UCD9222 contains two Fusion Power Peripherals (FPP). Each FPP consists of:

- A differential input error voltage amplifier.

- A 10-bit DAC used to set the output regulation reference voltage.

- A fast ADC with programmable input gain to digitally measure the error voltage.

- A dedicated 3-pole/3-zero digital filter to compensate the error voltage

- A digital PWM (DPWM) engine that generates the PWM pulse width based on the compensator output.

Each controller is configurable through the PMBus serial interface.

#### **PMBus Interface**

The PMBus is a serial interface specifically designed to support power management. It is based on the SMBus interface that is built on the I<sup>2</sup>C physical specification. The UCD9222 supports revision 1.2 of the PMBus standard. Wherever possible, standard PMBus commands are used to support the function of the device. For unique features of the UCD9222, MFR\_SPECIFIC commands are defined to configure or activate those features. These commands are defined in the UCD92xx PMBUS Command Reference.

The UCD9222 is PMBus compliant, in accordance with the "Compliance" section of the PMBus specification. The firmware is also compliant with the SMBus 2.0 specification, including support for the SMBus ALERT function. The hardware can support 100 kHz, 400 kHz, or 1 MHz PMBus operation.

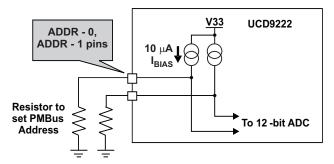

#### **Resistor Programmed PMBus Address Decode**

The PMBus Address is selected using resistors attached to the ADDR0 and ADDR1 pins. At power-up, the device applies a bias current to each address detect pin. The measured voltage on each pin determines the PMBus address as defined in Table 2. For example, a  $133k\Omega$  resistor on ADDR1 and a  $75k\Omega$  on ADDR0 will select PMBus address = 100. Resistors are chosen from the standard EIA-E96 series, and should have accuracy of 1% or better.

Figure 4. PMBus Address Detection Method

A short or open on either address pin causes the PMBus address to default to address 126. To avoid potential conflicts between multiple devices, it is best to avoid using address 126.

Some addresses should be avoided; see Table 2 for details.

UCD9222-EP ZHCSBS2-OCTOBER 2013

### UCD9222-EP

ZHCSBS2-OCTOBER 2013

|       |                    |                    |                    | 10    | able z. |       | 15 Aut | iress i | 51115 |                    |      |      |      |                   |                  |

|-------|--------------------|--------------------|--------------------|-------|---------|-------|--------|---------|-------|--------------------|------|------|------|-------------------|------------------|

|       |                    |                    | ADDR0              |       |         |       |        |         |       |                    |      |      |      |                   |                  |

|       |                    | (short)<br>< 36.5k | 42.2k              | 48.7k | 56.2k   | 64.9k | 75k    | 86.6k   | 100k  | 115k               | 133k | 154k | 178k | 205k              | (open)<br>> 237k |

|       | < 36.5k<br>(short) | 126                | 126                | 126   | 126     | 126   | 126    | 126     | 126   | 126                | 126  | 126  | 126  | 126               | 126              |

|       | 42.2k              | 126                | 126 <sup>(2)</sup> | 1     | 2       | 3     | 4      | 5       | 6     | 7                  | 8    | 9    | 10   | 11 <sup>(3)</sup> | 126              |

|       | 48.7k              | 126                | 126 <sup>(2)</sup> | 13    | 14      | 15    | 16     | 17      | 18    | 19                 | 20   | 21   | 22   | 33                | 126              |

|       | 56.2k              | 126                | 24                 | 25    | 26      | 27    | 28     | 29      | 30    | 31                 | 32   | 33   | 34   | 35                | 126              |

|       | 64.9k              | 126                | 36                 | 37    | 38      | 39    | 40     | 41      | 42    | 43                 | 44   | 45   | 46   | 47                | 126              |

|       | 75k                | 126                | 48                 | 49    | 50      | 51    | 52     | 53      | 54    | 55                 | 56   | 57   | 58   | 59                | 126              |

| 5     | 86.6k              | 126                | 60                 | 61    | 62      | 63    | 64     | 65      | 66    | 67                 | 68   | 69   | 70   | 71                | 126              |

| ADDR1 | 100k               | 126                | 72                 | 73    | 74      | 75    | 76     | 77      | 78    | 79                 | 80   | 81   | 82   | 83                | 126              |

| 4     | 115k               | 126                | 84                 | 85    | 86      | 87    | 88     | 89      | 90    | 91                 | 92   | 93   | 94   | 95                | 126              |

|       | 133k               | 126                | 96                 | 97    | 98      | 99    | 100    | 101     | 102   | 103                | 104  | 105  | 106  | 107               | 126              |

|       | 154k               | 126                | 108                | 109   | 110     | 111   | 112    | 113     | 114   | 115                | 116  | 117  | 118  | 119               | 126              |

|       | 178k               | 126                | 120                | 121   | 122     | 123   | 124    | 125     | 126   | 126 <sup>(2)</sup> | 126  | 126  | 126  | 126               | 126              |

|       | 205k               | 126                | 126                | 126   | 126     | 126   | 126    | 126     | 126   | 126                | 126  | 126  | 126  | 126               | 126              |

|       | > 237k<br>(open)   | 126                | 126                | 126   | 126     | 126   | 126    | 126     | 126   | 126                | 126  | 126  | 126  | 126               | 126              |

Table 2. PMBus Address Bins<sup>(1)</sup>

(1) Shaded addresses are not recommended as they will cause conflict when multiple devices are used.

(2) Reserved. Do not use.

(3) Conflicts with ROM. Do not use.

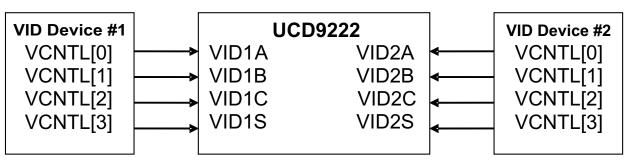

### **VID Interface**

The UCD9222 supports VID (Voltage Identification) inputs from up to two external VID enabled devices. The VID codes may be 4-, 6-, or 8-bit values; the format is selected using the VID\_CONFIG PMBus command. In 4- and 6-bit mode, each host uses four VID input signals (VID\_A, VID\_B, VID\_C, and VID\_S) to send VID codes to the UCD9222. In 8-bit mode, the PMBus input is used to receive VID commands from the VID devices' I<sup>2</sup>C interfaces.

Regardless of which VID mode is used, the commanded output voltage reference is set according to this formula:

Vref\_cmd = (VID\_CODE × VID\_Slope) + VID\_Offset,

where

VID\_Slope = (VID\_Vout\_High - VID\_Vout\_Low) / ((2^VID\_Format) -1),

and

VID\_Offset = VID\_Vout\_Low.

FXAS

**ISTRUMENTS**

www.ti.com.cn

The VID\_Vout\_High, VID\_Vout\_Low, and VID\_Format values are set using the VID\_CONFIG PMBus command. The same command is used to set the initial VID code that will be used at power-up. In addition, the VID\_CONFIG command also sets the initial voltage that the device ramps to at the end of the soft start; and defines a lockout interval over which the VID is ignored during the soft start.

**VID Lockout Interval:** Because the VID signals may be originating from a device that is being powered by the UCD9222, the voltage levels on the VID signal may not be valid logic levels until the supply voltage at the powered device has stabilized. For this reason a configurable lockout interval is applied each time the regulated output voltage is turned on. The lockout interval timer starts when the output voltage reaches the top of the softstart ramp. Positive values range from 1 to 32767 ms, with 1 ms resolution. A value of 0 will enable the VID inputs immediately at the top of the start ramp. Negative values disable the lockout, allowing the VID inputs to remain active all the time regardless of the output voltage state. The default value is 0.

**4-Bit VID Mode:** In 4-bit VID mode, the four VID input signals are used to provide the four bits of VID data, as shown in the table below. The VID lines are level-sensitive, and are periodically polled every 400µs. When the VID lines are changed to command a new voltage, there may be a delay of 500 to 600µs while the UCD9222 confirms that the VID signal levels are stable. The output voltage will then slew to the new setpoint voltage at the rate specified by the PMBus VOUT\_TRANSITION\_RATE command.

| PIN   | PURPOSE                            | RAIL 1 | RAIL 2 |

|-------|------------------------------------|--------|--------|

| VID_A | Data bit 0 (least significant bit) | VID1A  | VID2A  |

| VID_B | Data bit 1                         | VID1B  | VID2B  |

| VID_C | Data bit 2                         | VID1C  | VID2C  |

| VID_S | Data bit 3 (most significant bit)  | VID1S  | VID2S  |

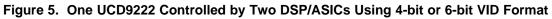

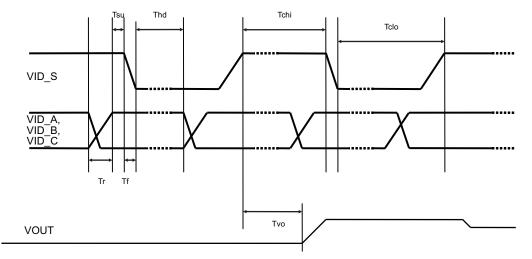

**6-Bit VID Mode:** In 6-bit VID mode, the four VID input signals are used to provide the six bits of VID data, as shown in the table below. Each of the three data lines (VID\_A, VID\_B, and VID\_C) carries two bits of data per VID code. The bits are clocked and selected by the VID\_S select line.

| PIN   | PURPOSE                                                        | RAIL 1 | RAIL 2 |

|-------|----------------------------------------------------------------|--------|--------|

| VID_A | Data bit 0 when VID_S is low,<br>Data bit 3 when VID_S is high | VID1A  | VID2A  |

| VID_B | Data bit 1 when VID_S is low,<br>Data bit 4 when VID_S is high | VID1B  | VID2B  |

| VID_C | Data bit 2 when VID_S is low,<br>Data bit 5 when VID_S is high | VID1C  | VID2C  |

| VID_S | Select Line:<br>Low= LSB, High = MSB                           | VID1S  | VID2S  |

UCD9222-EP

ZHCSBS2-OCTOBER 2013

www.ti.com.cn

The falling edge of the VID\_S line triggers the UCD9222 to read bits 2:0 on the three VID data lines. The rising edge of VID\_S triggers the UCD9222 to read bits 5:3 on the three VID data lines and calculate a new VOUT setpoint. This calculation takes from 35 to 135µs. The output voltage will then slew to the new setpoint voltage at the rate specified by the VOUT\_TRANSITION\_RATE PMBus command.

Figure 6. 6-Bit VID Data Transfer

The set-up time on the data lines is 0 µs. All four VID lines must hold at the same level for some time after a change in the VID\_S line to allow the UCD9222 to read and validate the data signals and perform necessary voltage calculations. The UCD9222 can tolerate single hold times as short as 70µs, but does not have sufficient computation power to sustain continuous VID messaging that quickly. It is expected that the hold time will be at least 125µs for sustained operations. It is recommended that the DSP only send VID messages when the regulated voltage needs to change; sending the same VID code repeatedly and continuously provides no benefit.

Figure 7 and Table 3 illustrate the critical timing measurements as they apply to the 6-bit VID interface.

Figure 7. 6-bit VID Timing

#### Table 3. 6-bit VID Timing

| SYMBO<br>L | PARAMETER                                                                           | MIN | ТҮР | MAX | UNITS |

|------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Tr         | Data and clock rise time                                                            | -   |     | 2.5 | μs    |

| Tf         | Data and clock fall time                                                            | -   |     | 0.3 | μs    |

| Tsu        | Data setup before changing clock                                                    | 0   |     |     | μs    |

| Thd        | Data hold until next clock change                                                   | 70  |     |     | μs    |

| Tchi       | Clock high time                                                                     | 70  | 125 |     | μs    |

| Tclo       | Clock low time                                                                      | 70  | 125 |     | μs    |

| Тvo        | Response time from rising edge of VID_S to start of<br>Vout slewing to new setpoint | 35  |     | 135 | μs    |

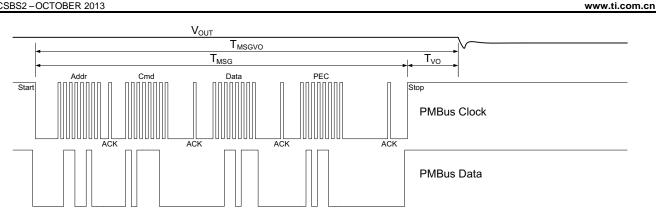

**8-Bit VID Mode:** In 8-bit VID mode, the four VID input signals are not used. Instead, an 8-bit VID code is transmitted to the UCD9222 through the PMBus / I2C port using one of the VID\_CODE\_RAILn commands, where n is the rail number from 1 to 2.

| NAME           | NAME DESCRIPTION <sup>(1)</sup>                                                                           |      |

|----------------|-----------------------------------------------------------------------------------------------------------|------|

| VID_CONFIG     | Selects the VID mode, sets the upper and lower voltage limits, and the starting voltage code at power-up. | 0xBB |

| VID_CODE_RAIL1 | Selects the VID code used to set the output voltage for Rail 1.                                           | 0xBC |

| VID_CODE_RAIL2 | Selects the VID code used to set the output voltage for Rail 2.                                           | 0xBD |

(1) For a complete description of the serial VID commands, see the UCD92xx PMBus Command Reference (SLUU337)

NSTRUMENTS

**EXAS**

Figure 8. PMBus Timing for VID\_CODE\_RAILn Command

| SYMBOL              | PARAMETER                                  | CONDITIONS                  | TYP       | UNITS |

|---------------------|--------------------------------------------|-----------------------------|-----------|-------|

| T <sub>msgPEC</sub> | Message Transmit Time, with PEC            | 400 kHz clock, PEC enabled  | 162 – 256 |       |

|                     | Message Transmit Time, without PEC         | 400 kHz clock, PEC enabled  | 126 – 221 | μs    |

| T <sub>vo</sub>     | End of message until Vout starts changing  |                             | 28 – 140  | μs    |

| T <sub>msgvo</sub>  | Start of message until Vout start changing | 400 kHz clock, PEC disabled | 169 – 314 | μs    |

The total time to transmit the serial VID command will vary depending on the other tasks that the UCD92xx processor is performing. Typical packet times varied from 162 to 256µs when the PMBus is configured for a 400 kb/s transfer rate running and the optional PEC byte is enabled. Disabling the PEC byte saves about 35µs and the transfer times are from 126 to 221µs. Note that these are **not** specified best-case/worst-case timings, but indicate a range given the typical acknowledge overhead in the host and controller.

After the VID packet has been received by the controller there is a delay before the set-point reference DAC is updated. This delay time varies from ~28 $\mu$ s to 140 $\mu$ s (typical ) depending on the existing priority of updating set-point reference DAC when the command is received.

With a 221µs packet transfer time, it would seem possible to send 4500 VID messages per second to the device. Very short bursts at this rate might be acceptable, but doing so for sustained periods could overwhelm the available processing resources in the UCD92xx, causing it to be delayed in performing its other monitoring and fault response tasks. In addition, if multiple hosts are trying to talk on the PMBus at such high rates then bus contention will occur with great regularity.

To prevent these issues, it is prudent to limit the total VID messaging rate to less than 4 messages per millisecond. In a system with four independent hosts, each host might need to be limited to less than 1 message per millisecond. Therefore, to minimize PMBus traffic, it is best to only issue the VID command when a voltage change is required. There is no benefit to sending the same VID code continuously and repeatedly.

### JTAG Interface

The JTAG interface can provide an alternate interface for programming the device. Two of the JTAG pins (TDI and TDO) are shared with the SyncIn and SyncOut function. JTAG is disabled by default. There are three conditions under which the JTAG interface is enabled:

- 1. When the ROM\_MODE PMBus command is issued.

- 2. On power-up if the Data Flash is blank. This allows JTAG to be used for writing the configuration parameters to a programmed device with no PMBus interaction.

- 3. When an invalid address is detected at power-up. By opening or shorting one of the address pins to ground, an invalid address can be generated that enables JTAG.

When the JTAG port is enabled the shared pins are not available for use as Sync pins.

If JTAG is to be used, an external mechanism such as jumpers or a mux must be used to prevent conflict between JTAG and the Sync pins.

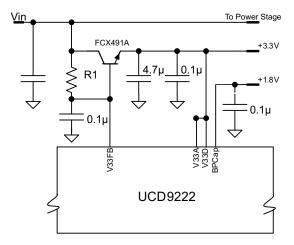

#### **Bias Supply Generator (Shunt Regulator Controller)**

The I/O and analog circuits in the UCD9222 require 3.3V to operate. This can be provided using a stand-alone external 3.3V supply, or it can be generated from the main input supply using an internal shunt regulator and an external transistor. Regardless of which method is used to generate the 3.3V supply, bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F should be connected from V33A and V33D to ground near the device. An additional bypass capacitor from 0.1 to 1  $\mu$ F must be connected from the BPCap pin to ground for the internal 1.8V supply to the device's logic circuits.

Figure 9 shows a typical application using the external transistor. The base of the transistor is driven by a resistor R1 to Vin and a transconductance amplifier whose output is on the V33FB pin. The NPN emitter becomes the 3.3V supply for the chip.

Figure 9. 3.3V Shunt Regulator Controller I/O

In order to generate the correct voltage on the base of the external pass transistor, the internal transconductance amplifier sinks current into the V33FB pin and a voltage is produced across R1. This resistor value should be chosen so that ISINK is in the range from 0.2 to 0.4mA. R1 is defined as

$$R_{1} = \frac{V_{in} - 3.3 - V_{be}}{\frac{I_{E}}{(\beta + 1)} + I_{SINK}}$$

(1)

Where  $I_{SINK}$  is the current into the V33FB pin;  $V_{in}$  is the power supply input voltage, typically 12V;  $I_E$  is the current draw of the device and any pull up resistors tied to the 3.3V supply; and  $\beta$  is the beta of the pass transistor. For  $I_{SINK} = 0.3 \text{ mA}$ ,  $V_{in}=12V$ ,  $\beta=99$ ,  $V_{be} = 0.7V$  and  $I_E=50\text{mA}$ , this formula selects R1 = 10k $\Omega$ . Weaker transistors or larger current loads will require less resistance to maintain the desired  $I_{SINK}$  current. For example, lowering  $\beta$  to 40 would require R1 = 5.23 k $\Omega$ ; likewise, an input voltage of 5V requires a value of 1.24 k $\Omega$  for R1.

#### **Power-On Reset**

The UCD9222 has an integrated power-on reset (POR) circuit that monitors the supply voltage. At power-up, the POR circuit detects the V33D rise. When V33D is greater than  $V_{RESET}$ , the device initiates an internal startup sequence. At the end of the startup sequence, the device begins normal operation, as defined by the downloaded device PMBus configuration.

#### **External Reset**

The device can be forced into the reset state by an external circuit connected to the nRESET pin. A logic low voltage on this pin holds the device in reset. To avoid an erroneous trigger caused by noise, a  $10k\Omega$  pull up resistor to 3.3V is recommended.

UCD9222-EP ZHCSBS2-OCTOBER 2013

### ON\_OFF\_CONFIG

The ON\_OFF\_CONFIG command is used to select the method of turning rails on and off. It can be configured so that the rail:

- stays off,

- turns on automatically,

- responds to the PMBus\_Cntrl pin,

- responds to OPERATION command, or

- responds to logical-AND of the PMBus\_Cntrl pin and the OPERATION command.

The ON\_OFF\_CONFIG command also sets the active polarity of the PMBus\_Cntrl pin.

#### EN1/EN2

In addition to the PMBus\_Cntrl pin supported by all UCD92xx products, the UCD9222 also supports separate Enable pins for each rail. The polarity of the EN1/EN2 pin is user-configurable, and will be the same as the polarity chosen for the PMBus\_Cntrl pin by the ON\_OFF\_CONFIG command. When the ON\_OFF\_CONFIG setting is configured to respond the PMBus\_Cntrl pin, the PMBus\_Cntrl pin signal will be logically ANDed with the rail's EN pin signal.

#### PG1/PG2

In addition to the PowerGood output signal supported by all UCD92xx products, the UCD9222 also supports separate PG indicators for each rail. The PowerGood signal is the logical-AND of all rails, while PG1 and PG2 indicate the status of a single rail. All three of these indicators are open-drain outputs, so they require pull-up resistors. When driving external circuits with logic voltages less than 3.3V, the pull-ups may be tied to that lower supply voltage, thus avoiding the need for level-shifters.

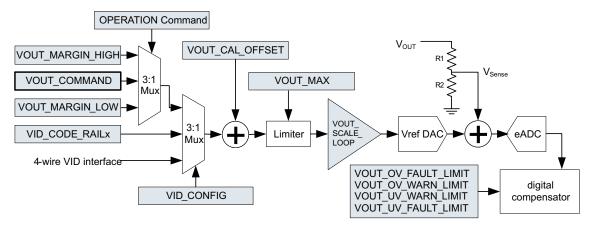

#### **Output Voltage Adjustment**

The output voltage may be set to maintain a steady voltage or it may be controlled dynamically by the VID interface, depending on the VID\_CONFIG setting. When not being commanded by the VID interface, the nominal output voltage is programmed by a combination of PMBus settings: VOUT\_COMMAND, VOUT\_CAL\_OFFSET, VOUT\_SCALE\_LOOP, and VOUT\_MAX. Their relationship is shown in Figure 10. These PMBus parameters need to be set such that the resulting Vref DAC value does not exceed the maximum value of V<sub>ref</sub>.

Output voltage margining is configured by the VOUT\_MARGIN\_HIGH and VOUT\_MARGIN\_LOW commands. The OPERATION command selects between the nominal output voltage and either of the margin voltages. The OPERATION command also includes an option to suppress certain voltage faults and warnings while operating at the margin settings.

Figure 10. PMBus Voltage Adjustment Mechanisms

For a complete description of the commands supported by the UCD9222 see the UCD92xx PMBUS Command Reference (SLUU337). Each of these commands can also be issued from the Texas Instruments Fusion Digital Power<sup>™</sup> Designer program. This Graphical User Interface (GUI) PC program issues the appropriate commands to configure the UCD9222 device.

#### Calibration

To optimize the operation of the UCD9222, PMBus commands are supplied to enable fine calibration of output voltage, output current, and temperature measurements. The supported commands and related calibration formulas may be found in the UCD92xx PMBUS Command Reference (SLUU337).

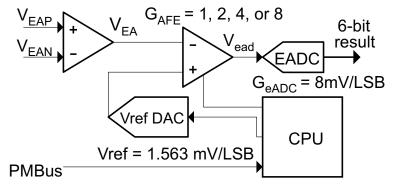

#### Analog Front End (AFE)

Figure 11. Analog Front End Block Diagram

The UCD9222 senses the power supply output voltage differentially through the EAP and EAN pins. The error amplifier utilizes a switched capacitor topology that provides a wide common mode range for the output voltage sense signals. The fully differential nature of the error amplifier also ensures low offset performance.

The output voltage is sampled at a programmable time (set by the EADC\_SAMPLE\_TRIGGER PMBus command). When the differential input voltage is sampled, the voltage is captured in internal capacitors and then transferred to the error amplifier where the value is subtracted from the set-point reference which is generated by the 10-bit Vref DAC as shown in Figure 11. The resulting error voltage is then amplified by a programmable gain circuit before the error voltage is converted to a digital value by the error ADC (EADC). This programmable gain is configured through the PMBus and affects the dynamic range and resolution of the sensed error voltage as shown in Table 5. The internal reference gains and offsets are factory-trimmed at the 4x gain setting, so it is recommended that this setting be used whenever possible.

| AFE_GAIN for<br>PMBus Command | AFE Gain | EFFECTIVE ADC<br>RESOLUTION (mV) | DIGITAL ERROR VOLTAGE<br>DYNAMIC RANGE (mV) |

|-------------------------------|----------|----------------------------------|---------------------------------------------|

| 0                             | 1x       | 8                                | -256 to 248                                 |

| 1                             | 2x       | 4                                | -128 to 124                                 |

| 2 (Recommended)               | 4x       | 2                                | -64 to 62                                   |

| 3                             | 8x       | 1                                | -32 to 31                                   |

| Table 5. | Analog | Front | End | Resolution |

|----------|--------|-------|-----|------------|

|----------|--------|-------|-----|------------|

The AFE variable gain is one of the compensation coefficients that are stored when the device is configured by issuing the CLA\_GAINS PMBus command. Compensator coefficients are arranged in several banks: one bank for start/stop ramp or tracking, one bank for normal regulation mode and one bank for light load mode. This allows the user to trade-off resolution and dynamic range for each operational mode.

The EADC, which samples the error voltage, has high accuracy, high resolution, and a fast conversion time. However, its range is limited as shown in Table 5. If the output voltage is different from the reference by more than this, the EADC repo<sup>o</sup>rts a saturated value at -32 LSBs or 31 LSBs. The UCD9222 overcomes this limitation by adjusting the Vref DAC up or down in order to bring the error voltage out of saturation. In this way, the effective range of the ADC is extended. When the EADC saturates, the Vref DAC is slewed at a rate of 0.156 V/ms, referred to the EA differential inputs.

Copyright © 2013, Texas Instruments Incorporated

UCD9222-EP ZHCSBS2-OCTOBER 2013

(2)

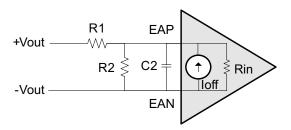

The differential feedback error voltage is defined as  $V_{EA} = V_{EAP} - V_{EAN}$ . An attenuator network using resistors R1 and R2 (Figure 12) should be used to ensure that  $V_{EA}$  does not exceed the maximum value of Vref when operating at the commanded voltage level. The commanded voltage level is determined by the PMBus settings described in the *Output Voltage Adjustment* section.

Figure 12. Input Offset Equivalent Circuit

#### Voltage Sense Filtering

Conditioning should be provided on the EAP and EAN signals. Figure 12 shows a divider network between the output voltage and the voltage sense input to the controller. The resistor divider is used to bring the output voltage within the dynamic range of the controller. When no attenuation is needed, R2 can be left open and the signal conditioned by the low-pass filter formed by R1 and C2.

As with any power supply system, maximize the accuracy of the output voltage by sensing the voltage directly across an output capacitor as close to the load as possible. Route the positive and negative differential sense signals as a balanced pair of traces or as a twisted pair cable back to the controller. Put the divider network close to the controller. This ensures that there is low impedance driving the differential voltage sense signal from the voltage rail output back to the controller. The resistance of the divider network is a trade-off between power loss and minimizing interference susceptibility. A parallel resistance ( $R_p$ ) of 1k $\Omega$  to 4k $\Omega$  is a good compromise. Once RP is chosen, R1 and R2 can be determined from the following formulas.

$$R_{1} = \frac{R_{P}}{K}$$

$$R_{2} = \frac{R_{P}}{1-K}$$

where K =  $\frac{V_{EA}}{V_{OUT}} \cong VOUT\_SCALE\_LOOP$

It is recommended that a capacitor be placed across the lower resistor of the divider network. This acts as an additional pole in the compensation and as an anti-alias filter for the EADC. To be effective as an anti-alias filter, the corner frequency should be 35% to 40% of the switching frequency. Then the capacitor is calculated as:

$$C2 = \frac{1}{2\pi \times 0.35 \times F_{SW} \times R_{P}}$$

<sup>(3)</sup>

To obtain the best possible accuracy, the input resistance and offset current on the device should be considered when calculating the gain of a voltage divider between the output voltage and the EA sense inputs of the UCD9222. The input resistance and input offset current are specified in the parametric tables in this datasheet.  $V_{EA} = V_{EAP} - V_{EAN}$  in the equation below.

$$V_{EA} = \frac{R_2}{R_1 + R_2 + \left(\frac{R_1R_2}{R_{EA}}\right)} V_{OUT} + \frac{R_1R_2}{R_1 + R_2 + \left(\frac{R_1R_2}{R_{EA}}\right)} I_{OFFSET}$$

(4)

The effect of the offset current can be reduced by making the resistance of the divider network low.

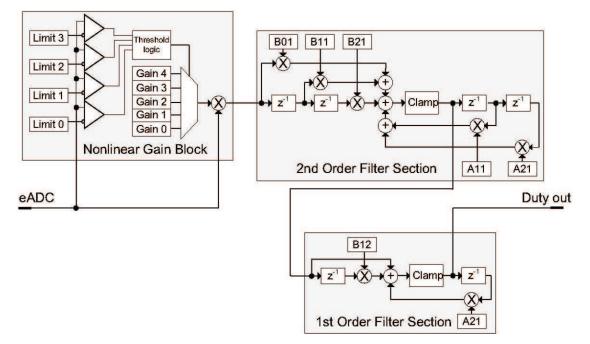

#### **Digital Compensator**

Each voltage rail controller in the UCD9222 includes a digital compensator. The compensator consists of a nonlinear gain stage, followed by a digital filter consisting of a second order infinite impulse response (IIR) filter section cascaded with a first order IIR filter section.

The Texas Instruments Fusion Digital Power<sup>™</sup> Designer development tool can be used to assist in defining the compensator coefficients. The design tool allows the compensator to be described in terms of the pole frequencies, zero frequencies and gain desired for the control loop. In addition, the Fusion Digital Power<sup>™</sup> Designer can be used to characterize the power stage so that the compensator coefficients can be chosen based on the total loop gain for each feedback system. The coefficients of the filter sections are generated through modeling the power stage and load.

Additionally, the UCD9222 has three banks of filter coefficients: Bank-0 is used during the soft start/stop ramp or tracking; Bank-1 is used while in regulation mode; and Bank-2 is used when the measured output current is below the configured light load threshold.

Figure 13. Digital Compensator

To calculate the values of the digital compensation filter continuous-time design parameters  $K_{DC}$ ,  $F_Z$  and  $Q_Z$  are entered into the Fusion Digital Power Designer software (or it calculates them automatically). Where the compensating filter transfer function is

$$H(s) = K_{DC} \frac{\frac{S^{2}}{\omega_{Z}^{2}} + \frac{s}{\omega_{Z}Q_{Z}} + 1}{s\left(\frac{s}{\omega_{P2}} + 1\right)}$$

(5)

There are approximate limits the design parameters  $K_{DC}$ ,  $F_Z$  and  $Q_Z$ . Though design parameters beyond these upper a lower bounds can be used to calculate the discrete-time filter coefficients, there will be significant round-off error when the continuous-time floating-point design parameters are converted to the discrete-time fixed-point integer coefficients to be downloaded to the controller.

#### UCD9222-EP ZHCSBS2-OCTOBER 2013

www.ti.com.cn

|                  | APPRO       |             |       |

|------------------|-------------|-------------|-------|

| DESIGN PARAMETER | LOWER BOUND | UPPER BOUND | UNITS |

| K <sub>DC</sub>  | 60          | 103         | dB    |

| Fz               | 3 kHz       | Fsw/5       | kHz   |

| QZ               | 0.1         | 5.0         | n/a   |

The nonlinear gain block allows a different gain to be applied to the system when the error voltage deviates from zero. Typically Limit 0 and Limit 1 would be configured with negative values between –1 and –32 and Limit 2 and Limit 3 would be configured with positive values between 1 and 31. However, the gain thresholds do not have to be symmetrical. For example, the four limit registers could all be set to positive values causing the Gain 0 value to set the gain for all negative errors and a nonlinear gain profile would be applied to only positive error voltages.

The cascaded 1<sup>st</sup> order filter section is used to generate the third zero and third pole.

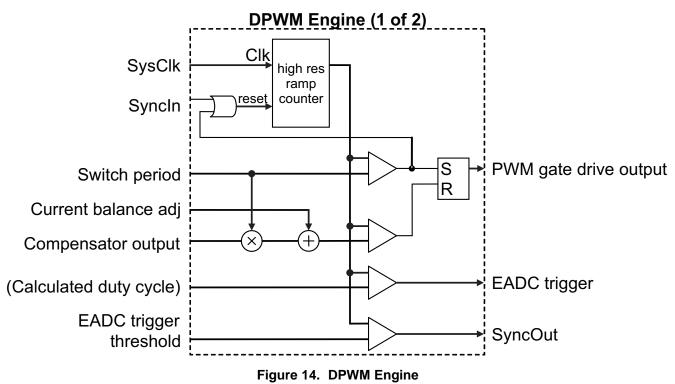

#### **DPWM Engine**

The output of the compensator feeds the high resolution DPWM engine. The DPWM engine produces the pulse width modulated gate drive output from the device. In operation, the compensator calculates the necessary duty cycle as a digital number representing a percentage from 0 to 100%. The duty cycle value is multiplied by the configured period to generate a comparator threshold value. This threshold is compared against the high speed switching period counter to generate the desired DPWM pulse width. This is shown in Figure 14.

Each DPWM engine can be synchronized to another DPWM engine or to an external sync signal via the Synclin and SyncOut pins. Configuration of the synchronization function is done through a MFR\_SPECIFIC PMBus command. See the *DPWM Synchronization* section for more details.

#### **Rail/Power Stage Configuration**

Unlike many other products in the UCD92xx family, the UCD9222 does not support assigning power stages to arbitrary rails, or combining multiple power stages on the same rail. The UCD9222 supports up to two single-phase rails, and the channel number of each rail's DPWM output must match that of its EAP/EAN feedback inputs.

#### **DPWM Phase Synchronization**

DPWM synchronization provides a method to link the timing between voltage rails controlled by the UCD92xx

device--either internally or between devices. The configuration of the synchronization between rails is performed by the issuing the SYNC CONFIG command. For details of issuing this command, see the UCD92xx PMBUS Command Reference (SLUU337). The synchronization behavior can also be configured using the Fusion Digital Power Designer software. Below is a summary of the function.

Each digital pulse width modulator (PWM) engine in the UCD92xx controller can accept a sync signal that resets the PWM ramp generator. The ramp generator can be set to free-run, accept a reset signal from another internal PWM engine, or accept a reset signal from the external SyncIn pin (UCD9222 only). In addition, each digital PWM engine can generate a phase delayed sync signal that can be directed to another PWM reset input or directed to the external SyncOut pin. In this way the PWM timers can be "daisy-chained" to set up the desired phase relationship between power stages.

The PWM engine reset input can accept the following inputs

| None (free run) |

|-----------------|

| DPWM 1          |

| DPWM 2          |

| SyncIn Pin      |

**Table 6. Sync Trigger Inputs**

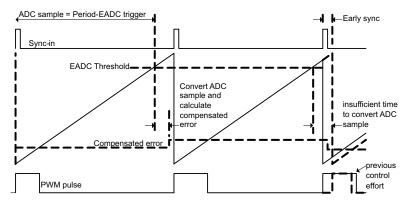

When configuring a PWM engine to run synchronous to another internal PWM output, set the switching frequency of each PWM output to the same value using the FREQUENCY\_SWITCH PMBus command. Set the time point where the controller samples the voltage to be regulated by setting the EADC SAMPLE TRIGGER value to the minimum value (228-240 nsec before the end of the switching period).

When configuring a PWM engine to run synchronous to run an external sync signal, the switching period must be set to be longer than the period of the sync signal by setting the value of the FREQUENCY\_SWITCH command to be lower than the frequency of the sync signal. This way the external sync signal will reset the PWM ramp counter before it is internally reset. In this operating condition, the error ADC sample trigger time must be set to:

EADC\_SAMPLE\_TRIGGER

$$\ge \frac{1}{F_{sw}} - \frac{0.95}{F_{sync}} + 248ns$$

(6)

where F<sub>SW</sub> is the switching frequency set by FREQUENCY\_SWITCH and F<sub>sync</sub> is the minimum synchronization frequency. The factor of 0.95 is due to the 5% tolerance on the internal clock in the controller. This will ensure that the regulation voltage is sampled "just in time" to calculate the appropriate control effort for each switching period. This is shown in Figure 15.

Figure 15. Relationship of EADC Trigger to external Sync

UCD9222-EP ZHCSBS2 -OCTOBER 2013

If two rails share a common sync source other than the SyncIn pin, they **must** have the same delay. When the SyncIn pin is used as a sync source, the delay is applied using a different register (EV1) than when using the other sources (which use the PhaseTrig registers). Using the EV1 register introduces delay in the control loop calculation that will introduce phase loss that must be taken into consideration when calculating the loop compensation. Therefore, under most conditions it will be desirable to set the delay to zero for the PWM signal synchronized by the SyncIn pin.

#### **Output Current Measurement**