# 带有初级端调节的恒定电压、恒定电流控制器

查询样品: UCC28720

### 特性

- <10mW 的无负载功率</li>

- 初级端调节 (PSR) 免除了对光耦合器的需要

- ±5% 电压和电流调节在线路和负载范围内

- 700V 启动开关

- 80kHz 最大开关频率可实现高功率密度充电器设计

- 针对最高总体效率的准谐振谷值开关运行

- 宽 VDD 范围允许使用小型偏置电容器

- 动态双极性结型晶体管 (BJT) 驱动

- 过压、低线路和过流保护功能

- 可编程电缆补偿

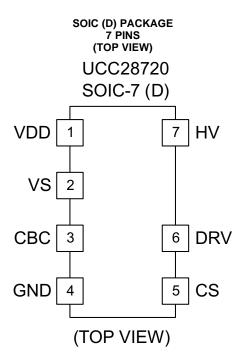

- 小外形尺寸集成电路 (SOIC)-7 封装

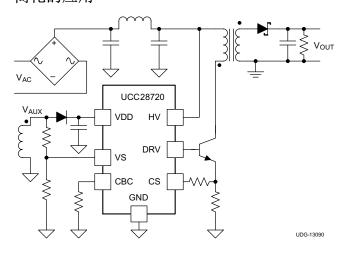

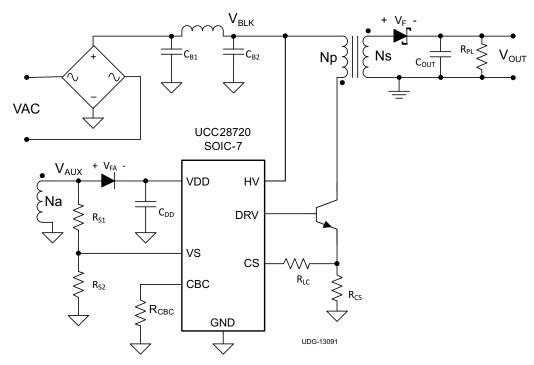

## 简化的应用

### 应用范围

- 用于消费类电子产品的 USB 兼容适配器和充电器

- 智能电话

- 平板电脑

- 照相机

- 针对电视和台式机的待机电源

- 大型家用电器

#### 说明

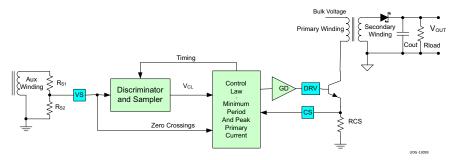

UCC28720 反激式电源控制器在不使用光耦合器的情况下可提供隔离输出恒定电压 (CV) 和恒定电流 (CC) 输出稳压。 此器件处理来自初级电源开关和一个辅助反激式绕组的信息以实现对输出电压和电流的精确控制。

一个内部 **700V** 启动开关、动态控制的工作状态和一个 定制的调制配置文件在不牺牲启动时间或输出瞬态响应 的同时支持超低待机功耗。

UCC28720 中的控制算法使得运行效率满足或者超过适用标准。输出驱动接至一个双极晶体管电源开关。带有谷值开关的断续传导模式 (DCM) 减少了开关损耗。 开关频率的调制和初级电流峰值振幅 (FM 和 AM) 在整个负载和线路范围内保持较高的转换效率。

此控制器有一个 80kHz 的最大开关频率并且一直保持对变压器内峰值初级电流的控制。 保护特性有助于抑制初级和次级应力分量。 UCC28720 可由一个外部电阻器设定为对电缆中的压降进行补偿。

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## Table 1. PRODUCT INFORMATION<sup>(1)</sup> (2)

| PACKAGE  | PINS | ORDERABLE<br>DEVICES |

|----------|------|----------------------|

| SOIC (D) | 7    | UCC28720D            |

- (1) See Orderable Addendum for specific device ordering information.

- (2) For other fixed cable compensation options, please consult the factory.

## **ABSOLUTE MAXIMUM RATINGS**(1)

|                                                  |                            | MIN   | MAX            | UNIT |

|--------------------------------------------------|----------------------------|-------|----------------|------|

| Start-up pin voltage, HV                         | V <sub>HV</sub>            |       | 700            | V    |

| Bias supply voltage, VDD                         | $V_{VDD}$                  |       | 38             | V    |

| Continuous base current sink                     | I <sub>DRV</sub>           |       | 50             |      |

| Continuous base current source                   | I <sub>DRV</sub>           |       | Self- limiting | mA   |

| Peak current, VS                                 | I <sub>VS</sub>            |       | -1.2           |      |

| Base drive voltage at DRV                        | V <sub>DRV</sub>           | -0.5  | Self- limiting |      |

| Valtage                                          | VS                         | -0.75 | 7              | V    |

| Voltage range                                    | CS, CBC                    | -0.5  | 5              |      |

| Operating junction temperature range             | T <sub>J</sub>             | -55   | 150            |      |

| Storage temperature                              | T <sub>STG</sub>           | -65   | 150            | °C   |

| Lead temperature 0.6 mm from case for 10 seconds |                            |       | 260            |      |

| ECD rating                                       | Human-body model (HBM)     |       | 2000           | V    |

| ESD rating                                       | Charged-device model (CDM) |       | 500            | V    |

(1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. These ratings apply over the operating ambient temperature ranges unless otherwise noted.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN | TYP MAX | UNIT |

|------------------|--------------------------------|-----|---------|------|

| VDD              | Bias supply operating voltage  | 9   | 35      | V    |

| $C_{VDD}$        | VDD bypass capacitor           | 1.0 | 10      | μF   |

| R <sub>CBC</sub> | Cable-compensation resistance  | 10  |         | kΩ   |

| I <sub>VS</sub>  | VS pin current                 | -1  |         | mA   |

| TJ               | Operating junction temperature | -40 | 125     | °C   |

### THERMAL INFORMATION

|                  |                                                             | UCC28720 |       |

|------------------|-------------------------------------------------------------|----------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | D        | UNITS |

|                  |                                                             | 7 PINS   |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 141.5    |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 73.8     |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 89.0     | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 23.5     |       |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 88.2     |       |

- (1) 有关传统和新的热 度量的更多信息,请参阅*IC 封装热度量*应用报告, SPRA953。 (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环

- (3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

- 结至顶部特征参数,  $ψ_{JT}$ ,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参 (5) 数以便获得  $\theta_{JA}$ 。

- 结至电路板特征参数, ΨJB,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该 参数以便获得  $\theta_{JA}$  。

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{VDD}$  = 25 V, HV = open,  $R_{CBC}$  = open,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$  (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS                                                          | MIN   | TYP  | MAX  | UNITS |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------|-------|------|------|-------|

| HIGH-VO               | LTAGE START UP                    |                                                                          |       |      |      |       |

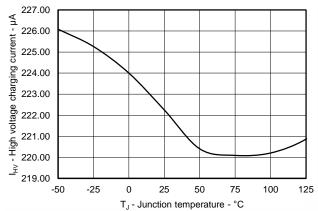

| I <sub>HV</sub>       | Start-up current out of VDD       | $V_{HV} = 100 \text{ V}, V_{VDD} = 0 \text{ V}, \text{ start state}$     | 100   | 225  | 500  |       |

| I <sub>HVLKG</sub>    | Leakage current at HV             | $V_{HV} = 400 \text{ V}$ , run state, $T_J = 25 ^{\circ}\text{C}$        |       | 0.01 | 0.25 | μΑ    |

| BIAS SUF              | PPLY INPUT                        |                                                                          |       |      |      |       |

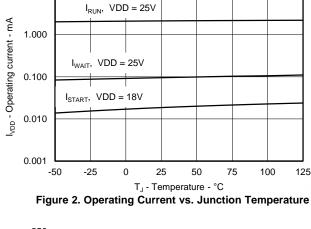

| I <sub>RUN</sub>      | Supply current, run               | I <sub>DRV</sub> = 0, run state                                          |       | 2.00 | 2.65 | mA    |

| I <sub>WAIT</sub>     | Supply current, wait              | I <sub>DRV</sub> = 0, wait state                                         |       | 95   | 150  |       |

| I <sub>START</sub>    | Supply current, start             | $I_{DRV} = 0$ , $V_{VDD} = 18$ V, start state, $I_{HV} = 0$              |       | 18   | 30   | μΑ    |

| I <sub>FAULT</sub>    | Supply current, fault             | I <sub>DRV</sub> = 0, fault state                                        |       | 95   | 150  |       |

| UNDERV                | OLTAGE LOCKOUT                    |                                                                          |       |      |      |       |

| V <sub>VDD(on)</sub>  | VDD turn-on threshold             | V <sub>VDD</sub> low to high                                             | 19    | 21   | 23   |       |

| V <sub>VDD(off)</sub> | VDD turn-off threshold            | V <sub>VDD</sub> high to low                                             | 7.35  | 7.7  | 8.15 | V     |

| VS INPUT              | Г                                 | '                                                                        |       |      |      |       |

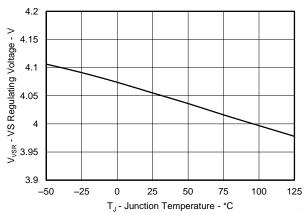

| $V_{VSR}$             | Regulating level                  | Measured at no-load condition, T <sub>J</sub> = 25°C (1)                 | 4.01  | 4.05 | 4.09 | V     |

| V <sub>VSNC</sub>     | Negative clamp level              | $I_{VS}$ = -300 $\mu$ A, volts below ground                              | 190   | 250  | 325  | mV    |

| I <sub>VSB</sub>      | Input bias current                | V <sub>VS</sub> = 4 V                                                    | -0.25 | 0    | 0.25 | μA    |

| CS INPUT              | Г                                 |                                                                          | *     |      |      |       |

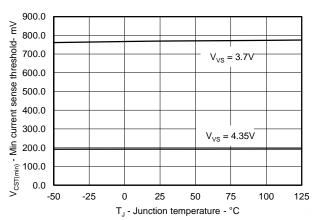

| V <sub>CST(max)</sub> | Max CS threshold voltage          | V <sub>VS</sub> = 3.7 V                                                  | 735   | 780  | 815  |       |

| V <sub>CST(min)</sub> | Min CS threshold voltage          | V <sub>VS</sub> = 4.35 V                                                 | 175   | 190  | 215  | mV    |

| K <sub>AM</sub>       | AM control ratio                  | V <sub>CST(max)</sub> / V <sub>CST(min)</sub>                            | 3.6   | 4.0  | 4.4  | V/V   |

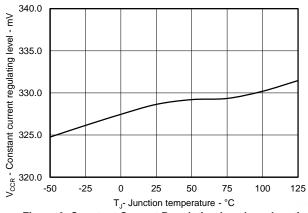

| V <sub>CCR</sub>      | Constant current regulating level | CC regulation constant                                                   | 317   | 330  | 344  | mV    |

| K <sub>LC</sub>       | Line compensation current ratio   | $I_{VSLS}$ = -300 $\mu$ A, $I_{VSLS}$ / current out of CS pin            | 24.0  | 25.0 | 28.6 | A/A   |

| T <sub>CSLEB</sub>    | Leading-edge blanking time        | DRV output duration, V <sub>CS</sub> = 1 V                               | 230   | 290  | 355  | ns    |

| DRIVER                |                                   |                                                                          |       |      |      |       |

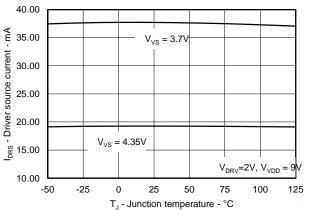

| I <sub>DRS(max)</sub> | Maximum DRV source current        | V <sub>DRV</sub> = 2 V, V <sub>VDD</sub> = 9 V, V <sub>VS</sub> = 3.85 V | 32    | 37   | 41   | A     |

| I <sub>DRS(min)</sub> | Minimum DRV source current        | V <sub>DRV</sub> = 2 V, V <sub>VDD</sub> = 9 V, V <sub>VS</sub> = 4.30 V | 16    | 19   | 22   | mA    |

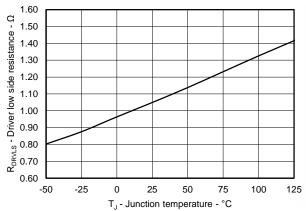

| R <sub>DRVLS</sub>    | DRV low-side drive resistance     | I <sub>DRV</sub> = 10 mA                                                 |       | 1    | 2.4  | Ω     |

| V <sub>DRCL</sub>     | DRV clamp voltage                 | V <sub>VDD</sub> = 35 V                                                  |       | 5.9  | 7    | V     |

| R <sub>DRVSS</sub>    | DRV pull-down in start state      |                                                                          |       | 20   | 25   | kΩ    |

| TIMING                |                                   |                                                                          | ·     |      |      |       |

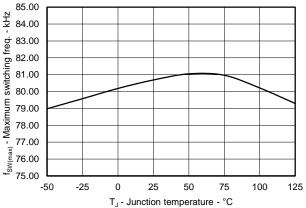

| f <sub>SW(max)</sub>  | Maximum switching frequency       | V <sub>VS</sub> = 3.7 V                                                  | 74    | 80   | 87   | kHz   |

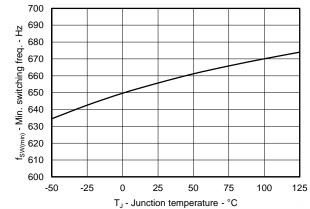

| f <sub>SW(min)</sub>  | Minimum switching frequency       | V <sub>VS</sub> = 4.35 V                                                 | 580   | 650  | 740  | Hz    |

| t <sub>ZTO</sub>      | Zero-crossing timeout delay       |                                                                          | 2.5   | 3.1  | 3.6  | μs    |

|                       |                                   | •                                                                        |       |      |      |       |

<sup>(1)</sup> The regulating level and over voltage at VS decreases with temperature by 0.8 mV/°C. This compensation is included to reduce the power supply output voltage variance over temperature.

## **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range,  $V_{VDD}$  = 25 V, HV = open,  $R_{CBC}$  = open,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$  (unless otherwise noted)

| (                      | norwide netea)                     |                                                                     |      |      |      |       |

|------------------------|------------------------------------|---------------------------------------------------------------------|------|------|------|-------|

|                        | PARAMETER                          | TEST CONDITIONS                                                     | MIN  | TYP  | MAX  | UNITS |

| PROTECT                | TION                               |                                                                     |      |      |      |       |

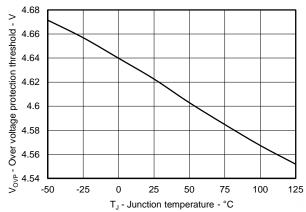

| V <sub>OVP</sub>       | Over-voltage threshold             | At VS input, $T_J = 25^{\circ}C^{(2)}$                              | 4.51 | 4.60 | 4.73 |       |

| V <sub>OCP</sub>       | Over-current threshold             | At CS input                                                         | 1.4  | 1.5  | 1.6  | V     |

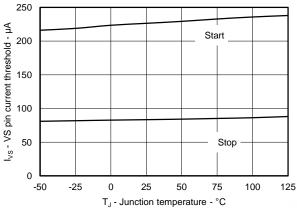

| I <sub>VSL(run)</sub>  | VS line-sense run current          | Current out of VS pin increasing                                    | 190  | 225  | 275  |       |

| I <sub>VSL(stop)</sub> | VS line-sense stop current         | Current out of VS pin decreasing                                    | 70   | 80   | 100  | μA    |

| K <sub>VSL</sub>       | VS line sense ratio                | I <sub>VSL(run)</sub> / I <sub>VSL(stop)</sub>                      | 2.45 | 2.80 | 3.05 | A/A   |

| T <sub>J(stop)</sub>   | Thermal shut-down temperature      | Internal junction temperature                                       |      | 165  |      | °C    |

| CABLE C                | OMPENSATION                        |                                                                     |      |      |      |       |

| V <sub>CBC(max)</sub>  | Cable compensation maximum voltage | Voltage at CBC at full load                                         | 2.9  | 3.1  | 3.5  | V     |

| V <sub>CVS(min)</sub>  | Minimum compensation at VS         | V <sub>CBC</sub> = open, change in VS regulating level at full load | -55  | -15  | 25   | m)/   |

| V <sub>CVS(max)</sub>  | Maximum compensation at VS         | V <sub>CBC</sub> = 0 V, change in VS regulating level at full load  | 275  | 320  | 380  | mV    |

<sup>(2)</sup> The regulating level and over voltage at VS decreases with temperature by 0.8 mV/°C. This compensation is included to reduce the power supply output voltage variance over temperature.

Instruments

ZHCSB14 -MAY 2013 www.ti.com.cn

## **DEVICE INFORMATION**

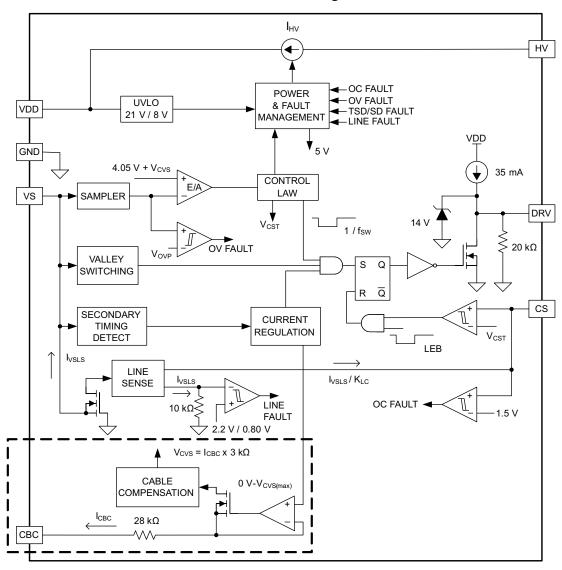

## **Functional Block Diagram**

UDG-13094

## **PIN FUNCTIONS**

| NAME | NUMBER | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                            |

|------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBC  | 3      | ı   | Cable compensation is a programming pin for compensation of cable voltage drop. Cable compensation is programmed with a resistor to GND.                                                                                                                                                                               |

| CS   | 5      | ı   | Current sense input connects to a ground-referenced current-sense resistor in series with the power switch. The resulting voltage is used to monitor and control the peak primary current. A series resistor can be added to this pin to compensate the peak switch current levels as the AC-mains input varies.       |

| DRV  | 6      | 0   | Drive is an output used to drive the base of an external high voltage NPN transistor.                                                                                                                                                                                                                                  |

| GND  | 4      |     | The ground pin is both the reference pin for the controller and the low-side return for the drive output. Special care should be taken to return all AC decoupling capacitors as close as possible to this pin and avoid any common trace length with analog signal return paths.                                      |

| HV   | 7      | ı   | The high-voltage pin connects directly to the rectified bulk voltage and provides charge to the VDD capacitor for start-up of the power supply.                                                                                                                                                                        |

| NTC  | _      | ı   | NTC an interface to an external negative temperature coefficient resistor for remote temperature sensing. Pulling this pin low shuts down PWM action.                                                                                                                                                                  |

| VDD  | 1      | ı   | VDD is the bias supply input pin to the controller. A carefully-placed bypass capacitor to GND is required on this pin.                                                                                                                                                                                                |

| VS   | 2      | I   | Voltage sense is an input used to provide voltage and timing feedback to the controller. This pin is connected to a voltage divider between an auxiliary winding and GND. The value of the upper resistor of this divider is used to program the AC-mains run and stop thresholds and line compensation at the CS pin. |

### **Detailed Pin Description**

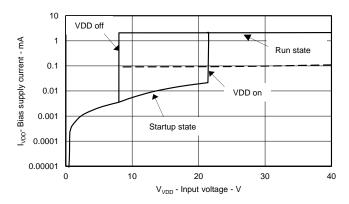

**VDD** (Device Bias Voltage Supply): The VDD pin is connected to a bypass capacitor to ground. The VDD turnon UVLO threshold is 21 V and turn-off UVLO threshold is 8.1 V, with an available operating range up to 35 V on VDD. The USB charging specification requires the output current to operate in constant-current mode from 5 V to a minimum of 2 V; this is easily achieved with a nominal VDD of approximately 25 V. The additional VDD headroom up to 35 V allows for VDD to rise due to the leakage energy delivered to the VDD capacitor in highload conditions.

**GND (Ground):** There is a single ground reference external to the device for the base drive current and analog signal reference. Place the VDD bypass capacitor close to GND and VDD with short traces to minimize noise on the VS and CS signal pins.

**HV** (High Voltage Startup): The HV pin is connected directly to the bulk capacitor to provide startup current to the VDD capacitor. The typical startup current is  $\sim 300~\mu A$  which provides fast charging of the VDD capacitor. The internal HV start-up device is active until VDD exceeds the turn-on UVLO threshold at which time the HV start-up device is turned off. In the off state the leakage current is very low to minimize standby losses of the controller. When VDD falls below the UVLO turn-off threshold the HV start-up device is turned on.

**VS (Voltage-Sense):** The VS pin is connected to a resistor divider from the auxiliary winding to ground. The output-voltage feedback information is sampled at the end of the transformer secondary current demagnetization time to provide an accurate representation of the output voltage. Timing information to achieve valley-switching and to control the duty cycle of the secondary transformer current is determined by the waveform on the VS pin. Avoid placing a filter capacitor on this input which would interfere with accurate sensing of this waveform.

The VS pin also senses the bulk capacitor voltage to provide for AC-input run and stop thresholds, and to compensate the current-sense threshold across the AC-input range. During the transistor on-time the VS pin is clamped to approximately 250 mV below GND and the current out of the VS pin is sensed. For the AC-input run/stop function, the run threshold on VS is 225  $\mu$ A and the stop threshold is 80  $\mu$ A. The values for the auxilliary voltage divider upper-resistor R<sub>S1</sub> and lower-resistor R<sub>S2</sub> can be determined by the equations below.

$$R_{\text{S1}} = \frac{V_{\text{IN(run)}} \times \sqrt{2}}{N_{\text{PA}} \times I_{\text{VSL(run)}}}$$

where

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio,

- V<sub>IN(run)</sub> is the AC RMS voltage to enable turn-on of the controller (run),

- I<sub>VSL(run)</sub> is the run-threshold for the current pulled out of the VS pin during the switch on-time. (see ELECTRICAL CHARACTERISTICS)

$$R_{S2} = \frac{R_{S1} \times V_{VSR}}{N_{AS} \times (V_{OCV} + V_F) - V_{VSR}}$$

where

- V<sub>OCV</sub> is the converter regulated output voltage,

- V<sub>F</sub> is the output rectifier forward drop at near-zero current,

- N<sub>AS</sub> is the transformer auxiliary to secondary turns ratio,

- R<sub>S1</sub> is the VS divider high-side resistance,

- V<sub>VSR</sub> is the CV regulating level at the VS input (see ELECTRICAL CHARACTERISTICS).

**DRV (Base Drive):** The DRV pin is connected to the NPN transistor base pin. The driver provides a base drive signal limited to 7 V. The turn-on characteristic of the driver is a 15 mA to 35-mA current source that is scaled with the current sense threshold dictated by the operating point in the control scheme. When the minimum current sense threshold is being used, the base drive current is also at its minimum value. As the current sense threshold is increased to the maximum, the base drive current scales linearly with it to its maximum of 35 mA typical. The turn-off current is determined by the low-side driver R<sub>DS(on)</sub>

(1)

(3)

www.ti.com.cn ZHCSB14 -MAY 2013

CS (Current Sense): The current-sense pin is connected through a series resistor ( $R_{LC}$ ) to the current-sense resistor ( $R_{CS}$ ). The current-sense threshold is 0.78 V for  $I_{PP(max)}$  and 0.195 V for  $I_{PP(min)}$ . The series resistor  $R_{LC}$  provides the function of feed-forward line compensation to eliminate change in  $I_{PP}$  due to change in di/dt and the propagation delay of the internal comparator and NPN transistor turn-off time. There is an internal leading-edge blanking time of approximately 300 ns to eliminate sensitivity to the turn-on current spike. It should not be necessary to place a bypass capacitor on the CS pin. The value of  $R_{CS}$  is determined by the target output current in Constant Current (CC) regulation. The values of  $R_{CS}$  and  $R_{LC}$  can be determined by the equations below. The term  $\eta_{XFMR}$  is intended to account for the energy stored in the transformer but not delivered to the secondary. This includes transformer resistance and core loss, bias power, and primary-to-secondary leakage ratio.

**Example:** With a transformer core and winding loss of 5%, primary-to-secondary leakage inductance of 3.5%, and bias power to output power ratio of 1.5%. The  $\eta_{XFMR}$  value is approximately: 1 - 0.05 - 0.035 - 0.015 = 0.9.

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2l_{OCC}} \times \sqrt{\eta_{XFMR}}$$

#### where

- V<sub>CCR</sub> is a current regulation constant (see ELECTRICAL CHARACTERISTICS),

- N<sub>PS</sub> is the transformer primary-to-secondary turns ratio (a ratio of 13 to 15 is recommended for 5-V output),

- I<sub>OCC</sub> is the target output current in constant-current regulation,

- n<sub>XFMR</sub> is the transformer efficiency.

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times t_D \times N_{PA}}{L_P}$$

#### where

- R<sub>S1</sub> is the VS pin high-side resistor value,

- R<sub>CS</sub> is the current-sense resistor value,

- t<sub>D</sub> is the current-sense delay including NPN transistor turn-off delay, add ~50 ns to transistor delay,

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio,

- L<sub>P</sub> is the transformer primary inductance,

- K<sub>LC</sub> is a current-scaling constant (see ELECTRICAL CHARACTERISTICS).

**CBC (Cable Compensation):** The cable compensation pin is connected to a resistor to ground to program the amount of output voltage compensation to offset cable resistance. The cable compensation block provides a 0-V to 3-V voltage level on the CBC pin corresponding to  $I_{OCC(max)}$  output current. Connecting a resistance from CBC to GND programs a current that is summed into the VS feedback divider, increasing the regulation voltage as  $I_{OUT}$  increases. There is an internal series resistance of 28 k $\Omega$  to the CBC pin which sets a maximum cable compensation of a 5-V output to 400 mV when CBC is shorted to ground. The CBC resistance value can be determined by the equation below.

$$R_{\text{CBC}} = \frac{V_{\text{CBC(max)}} \times 3 \text{ k}\Omega \times \left(V_{\text{OCV}} + V_{\text{F}}\right)}{V_{\text{VSR}} \times V_{\text{OCBC}}} - 28 \text{ k}\Omega$$

#### where

- V<sub>OCV</sub> is the regulated output voltage,

- V<sub>F</sub> is the diode forward voltage in V,

- V<sub>OCBC</sub> is the target cable compensation voltage at the output terminals,

- V<sub>CBC(max)</sub> is the maximum voltage at the cable compensation pin at the maximum converter output current (see ELECTRICAL CHARACTERISTICS),

- V<sub>VSR</sub> is the CV regulating level at the VS input (see ELECTRICAL CHARACTERISTICS).

#### TYPICAL CHARACTERISTICS

VDD = 25 V, unless otherwise noted.

10.000

Figure 1. Bias Supply Current vs. VDD Voltage

Figure 3. VS Pin Regulation Voltage vs. Junction Temperature

Figure 4. VS Pin Start and Stop Thresholds vs. Junction Temperature

Figure 5. Current Sense Threshold vs. Temperature

Figure 6. Constant Current Regulation Level vs. Junction Temperature

## TYPICAL CHARACTERISTICS (continued)

VDD = 25 V, unless otherwise noted.

Figure 7. Minimum Switching Frequency vs. Junction Temperature

Figure 9. Driver Output Source Current vs. Junction Temperature

Figure 11. Over Voltage Protection Threshold vs. Junction Temperature

Figure 8. Maximum Switching Frequency vs. Junction Temperature

Figure 10. Driver Pull Down Resistance vs. Junction Temperature

Figure 12. HV Charging Current vs. Junction Temperature

#### **FUNCTIONAL DESCRIPTION**

The UCC28720 is a flyback power supply controller which provides accurate voltage and constant current regulation with primary-side feedback, eliminating the need for opto-coupler feedback circuits. The controller operates in discontinuous conduction mode with valley-switching to minimize switching losses. The modulation scheme is a combination of frequency and primary peak current modulation to provide high conversion efficiency across the load range. The control law provides a wide-dynamic operating range of output power which allows the power designer to achieve the <10-mW stand-by power requirement.

During low-power operating ranges the device has power management features to reduce the device operating current at operating frequencies below 28 kHz. Accurate voltage and constant current regulation, fast dynamic response, and fault protection are achieved with primary-side control. A complete charger solution can be realized with a straightforward design process, low cost and low component count.

## **Primary-Side Voltage Regulation**

Figure 13 illustrates a simplified flyback convertor with the main voltage regulation blocks of the device shown. The power train operation is the same as any DCM flyback circuit but accurate output voltage and current sensing is the key to primary-side control.

Figure 13. Simplified Flyback Convertor (with the main voltage regulation blocks)

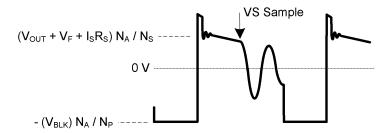

In primary-side control, the output voltage is sensed on the auxiliary winding during the transfer of transformer energy to the secondary. As shown in Figure 14 it is clear there is a down slope representing a decreasing total rectifier  $V_F$  and resistance voltage drop ( $I_SR_S$ ) as the secondary current decreases to zero. To achieve an accurate representation of the secondary output voltage on the auxiliary winding, the discriminator reliably recognizes the leakage inductance reset and ringing and ingores it, continuously samples the auxiliary voltage during the down slope after the ringing is diminished, and captures the error signal at the time the secondary winding reaches zero current. The internal reference on VS is 4.05 V. Temperature compensation on the VS reference voltage of -0.8-mV/°C offsets the change in the output rectifier forward voltage with temperature. The resistor divider is selected as outlined in the VS pin description.

Figure 14. Auxiliary Winding Voltage

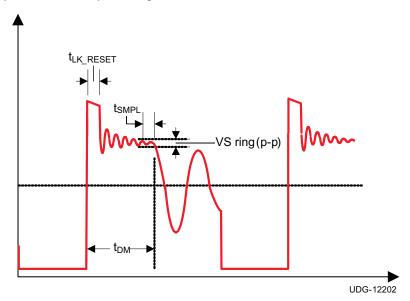

The UCC28720 includes a VS signal sampler that uses discrimination methods to ensure an accurate sample of the output voltage from the auxiliary winding. There are some conditions that must be met on the auxiliary winding signal to ensure reliable operation. These conditions are the reset time of the leakage inductance and the duration of any subsequent leakage inductance ring. Refer to Figure 15 below for a detailed illustration of waveform criteria to ensure a reliable sample on the VS pin. The first detail to examine is the duration of the leakage inductance reset pedestal,  $t_{LK\_RESET}$  in Figure 15. Because this can mimic the waveform of the secondary current decay, followed by a sharp downslope, it is important to keep the leakage reset time less than 600 ns for  $I_{PRI}$  minimum, and less than 2.2 µs for  $I_{PRI}$  maximum. The second detail is the amplitude of ringing on the  $V_{AUX}$  waveform following  $t_{LK\_RESET}$ . The peak-to-peak voltage at the VS pin should be less than approximately 100 mV $_{p-p}$  at least 200 ns before the end of the demagnetization time,  $t_{DM}$ . If there is a concern with excessive ringing, it usually occurs during light or no-load conditions, when  $t_{DM}$  is at the minimum. The tolerable ripple on VS scales up when measured at the auxiliary winding by  $R_{S1}$  and  $R_{S2}$ , and is equal to 100 mV x ( $R_{S1} + R_{S2}$ ) /  $R_{S2}$  when measured directly at the auxilliary winding.

Figure 15. Auxiliary Waveform Details

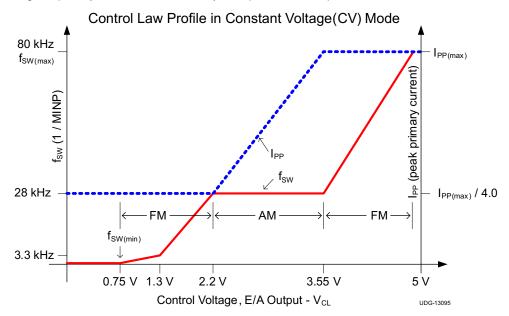

During voltage regulation, the controller operates in frequency modulation mode and amplitude modulation mode as illustrated in Figure 16 below. The internal operating frequency limits of the device are 80 kHz,  $f_{SW(max)}$  and 65 Hz,  $f_{SW(min)}$ . The transformer primary inductance and primary peak current chosen sets the maximum operating frequency of the converter. The output preload resistor and efficiency at low power determines the converter minimum operating frequency. There is no stability compensation required for the UCC28720.

Figure 16. Frequency and Amplitude Modulation Modes (during voltage regulation)

### **Primary-Side Current Regulation**

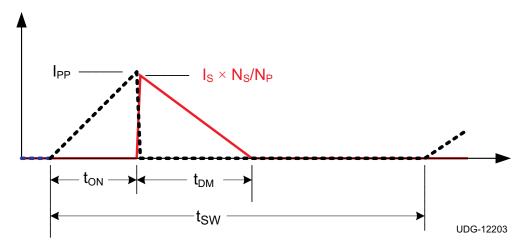

Timing information at the VS pin and current information at the CS pin allow accurate regulation of the secondary average current. The control law dictates that as power is increased in CV regulation and approaching CC regulation the primary-peak current is at  $I_{PP(max)}$ . Referring to Figure 17 below, the primary-peak current, turns ratio, secondary demagnetization time  $(t_{DM})$ , and switching period  $(t_{SW})$  determine the secondary average output current. Ignoring leakage inductance effects, the average output current is given by Equation 6. When the average output current reaches the regulation reference in the current control block, the controller operates in frequency modulation mode to control the output current at any output voltage at or below the voltage regulation target as long as the auxiliary winding can keep VDD above the UVLO turn-off threshold.

Figure 17. Transformer Currents

$$I_{OUT} = \frac{I_{PP}}{2} \times \frac{N_P}{N_S} \times \frac{t_{DM}}{t_{SW}}$$

$$5$$

$$6$$

$$6$$

$$6$$

$$6$$

$$6$$

$$6$$

$$7$$

$$6$$

$$9$$

$$9$$

$$9$$

$$9$$

$$1$$

$$1$$

$$1$$

$$1$$

$$1$$

Figure 18. Typical Target Output V-I Characteristic

**Output Current**

UDG-12201

locc

### **Valley Switching**

The UCC28720 utilizes valley switching to reduce switching losses in the transistor, to reduce induced-EMI, and to minimize the turn-on current spike at the sense resistor. The controller operates in valley-switching in all load conditions unless the collector voltage (V<sub>C</sub>) ringing has subsided.

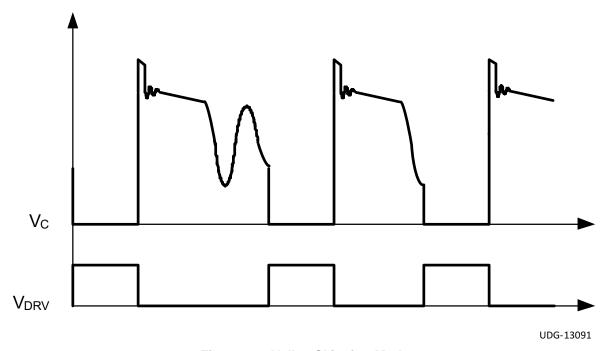

Referring to Figure 19 below, the UCC28720 operates in a valley-skipping mode in most load conditions to maintain an accurate voltage or current regulation point and still switch on the lowest available  $V_C$ .

Figure 19. Valley-Skipping Mode

## **Start-Up Operation**

The internal high-voltage start-up switch connected to the bulk capacitor voltage ( $V_{BLK}$ ) through the HV pin charges the VDD capacitor. During start up there is typically 300  $\mu$ A available to charge the VDD capacitor. When VDD reaches the 21-V UVLO turn-on threshold, the controller is enabled, the converter starts switching and the start-up switch is turned off. The initial three cycles are limited to  $I_{PP(min)}$ . After the initial three cycles at minimum  $I_{PP(min)}$ , the controller responds to the condition dictated by the control law. The converter will remain in discontinuous mode during charging of the output capacitor(s), maintaining a constant output current until the output voltage is in regulation.

#### **Fault Protection**

The UCC28720 provides comprehensive fault protection. Protection functions include:

- Output over-voltage fault

- Input under-voltage fault

- Internal over-temperature fault

- Primary over-current fault

- CS pin fault

- VS pin fault

A UVLO reset and restart sequence applies for all fault protection events.

The output over-voltage function is determined by the voltage feedback on the VS pin. If the voltage sample on VS exceeds 115% of the nominal  $V_{OUT}$ , the device stops switching and the internal current consumption is  $I_{FAULT}$  which discharges the VDD capacitor to the UVLO turn-off threshold. After that, the device returns to the start state and a start-up sequence ensues.

The UCC28720 always operates with cycle-by-cycle primary peak current control. The normal operating range of the CS pin is 0.78 V to 0.195 V. There is additional protection if the CS pin reaches 1.5 V. This results in a UVLO reset and restart sequence.

The line input run and stop thresholds are determined by current information at the VS pin during the transistor on-time. While the VS pin is clamped close to GND during the transistor on-time, the current through  $R_{S1}$  is monitored to determine a sample of the bulk capacitor voltage. A wide separation of run and stop thresholds allows clean start-up and shut-down of the power supply with the line voltage. The run current threshold is 225  $\mu$ A and the stop current threshold is 80  $\mu$ A.

The internal over-temperature protection threshold is 165°C. If the junction temperature reaches this threshold the device initiates a UVLO reset cycle. If the temperature is still high at the end of the UVLO cycle, the protection cycle repeats.

Protection is included in the event of component failures on the VS pin. If complete loss of feedback information on the VS pin occurs, the controller stops switching and restarts.

TEXAS INSTRUMENTS

ZHCSB14 -MAY 2013 www.ti.com.cn

#### **DESIGN PROCEDURE**

This procedure outlines the steps to design a constant-voltage, constant-current flyback converter using the UCC28720 controller. Refer to the Figure 20 for component names and network locations. The design procedure equations use terms that are defined below.

Figure 20. Design Procedure Application Example

### **Definition of Terms**

#### **Capacitance Terms in Farads**

- C<sub>BULK</sub>: total input capacitance of C<sub>B1</sub> and C<sub>B2</sub>.

- C<sub>DD</sub>: minimum required capacitance on the VDD pin.

- C<sub>OUT</sub>: minimum output capacitance required.

#### **Duty Cycle Terms**

- **D**<sub>MAGCC</sub>: secondary diode conduction duty cycle in CC, 0.425.

- D<sub>MAX</sub>: transistor on-time duty cycle.

#### **Frequency Terms in Hertz**

- **f**LINE: minimum line frequency.

- f<sub>MAX</sub>: target full-load maximum switching frequency of the converter.

- f<sub>MIN</sub>: minimum switching frequency of the converter, add 15% margin over the f<sub>SW(min)</sub> limit of the device.

- f<sub>SW(min)</sub>: minimum switching frequency (see ELECTRICAL CHARACTERISTICS).

## **Current Terms in Amperes**

- I<sub>occ</sub>: converter output constant-current target.

- I<sub>PP(max)</sub>: maximum transformer primary current.

- I<sub>START</sub>: start-up bias supply current (see ELECTRICAL CHARACTERISTICS).

- I<sub>TRAN</sub>: required positive load-step current.

- I<sub>VSL(run)</sub>: VS pin run current (see ELECTRICAL CHARACTERISTICS).

- I<sub>DRS</sub>: Driver source current (see ELECTRICAL CHARACTERISTICS).

#### **Current and Voltage Scaling Terms**

- K<sub>AM</sub>: maximum-to-minimum peak primary current ratio (see ELECTRICAL CHARACTERISTICS).

- K<sub>LC</sub>: current-scaling constant (see ELECTRICAL CHARACTERISTICS).

#### **Transformer Terms**

- L<sub>P</sub>: transformer primary inductance.

- N<sub>AS</sub>: transformer auxiliary-to-secondary turns ratio.

- N<sub>PA</sub>: transformer primary-to-auxiliary turns ratio.

- N<sub>PS</sub>: transformer primary-to-secondary turns ratio.

#### **Power Terms in Watts**

- P<sub>IN</sub>: converter maximum input power.

- Pout: full-load output power of the converter.

- PRSTR: VDD start-up resistor power dissipation.

- P<sub>SB</sub>: total stand-by power.

- P<sub>SB\_CONV</sub>: P<sub>SB</sub> minus start-up resistor and snubber losses.

### Resistance Terms in $\Omega$

- R<sub>cs</sub>: primary current programming resistance.

- R<sub>ESR</sub>: total ESR of the output capacitor(s).

- R<sub>PL</sub>: preload resistance on the output of the converter.

- R<sub>S1</sub>: high-side VS pin resistance.

- R<sub>S2</sub>: low-side VS pin resistance.

#### **Timing Terms in Seconds**

- t<sub>D</sub>: current-sense delay including transistor turn-off delay; add 50 ns to transistor delay.

- t<sub>DMAG(min)</sub>: minimum secondary rectifier conduction time.

- **t**<sub>ON(min)</sub>: minimum transistor on time.

- t<sub>R</sub>: resonant frequency during the DCM (discontinuous conduction mode) time.

#### **Voltage Terms in Volts**

- V<sub>BLK</sub>: highest bulk capacitor voltage for stand-by power measurement.

- V<sub>BULK(min)</sub>: minimum voltage on C<sub>B1</sub> and C<sub>B2</sub> at full power.

- V<sub>OCBC</sub>: target cable compensation voltage at the output terminals.

- V<sub>CBC(max)</sub>: maximum voltage at the CBC pin at the maximum converter output current (see ELECTRICAL CHARACTERISTICS).

- V<sub>CCR</sub>: constant-current regulating voltage (see ELECTRICAL CHARACTERISTICS).

- V<sub>CST(max)</sub>: CS pin maximum current-sense threshold (see ELECTRICAL CHARACTERISTICS).

- V<sub>CST(min)</sub>: CS pin minimum current-sense threshold (see ELECTRICAL CHARACTERISTICS).

- V<sub>DD(off)</sub>: UVLO turn-off voltage (see ELECTRICAL CHARACTERISTICS).

- V<sub>DD(on)</sub>: UVLO turn-on voltage (see ELECTRICAL CHARACTERISTICS).

- V<sub>OA</sub>: output voltage drop allowed during the load-step transient.

- V<sub>CPK</sub>: peak transistor collector to emitter voltage at high line.

- V<sub>F</sub>: secondary rectifier forward voltage drop at near-zero current.

- V<sub>FA</sub>: auxiliary rectifier forward voltage drop.

- V<sub>LK</sub>: estimated leakage inductance energy reset voltage.

- **V<sub>ocv</sub>:** regulated output voltage of the converter.

- **V<sub>occ</sub>:** target lowest converter output voltage in constant-current regulation.

- V<sub>REV</sub>: peak reverse voltage on the secondary rectifier.

- V<sub>RIPPLE</sub>: output peak-to-peak ripple voltage at full-load.

- V<sub>VSR</sub>: CV regulating level at the VS input (see ELECTRICAL CHARACTERISTICS).

## AC Voltage Terms in V<sub>RMS</sub>

- V<sub>IN(max)</sub>: maximum input voltage to the converter.

- V<sub>IN(min)</sub>: minimum input voltage to the converter.

- V<sub>IN(run)</sub>: converter input start-up (run) voltage.

### **Efficiency Terms**

- η<sub>SB</sub>: estimated efficiency of the converter at no-load condition, not including start-up resistance or bias losses.

For a 5-V USB charger application, 60% to 65% is a good initial estimate.

- η: converter overall efficiency.

- n<sub>xFMR</sub>: transformer primary-to-secondary power transfer efficiency.

#### **Stand-by Power Estimate**

Assuming no-load stand-by power is a critical design parameter, determine estimated no-load power based on target converter maximum switching frequency and output power rating.

The following equation estimates the stand-by power of the converter.

$$P_{SB\_CONV} = \frac{P_{OUT} \times f_{MIN}}{\eta_{SB} \times K_{AM}^2 \times f_{MAX}}$$

(7)

For a typical USB charger application, the bias power during no-load is approximately 2.5 mW. This is based on 25-V VDD and 100- $\mu$ A bias current. The output preload resistor can be estimated by  $V_{OCV}$  and the difference in the converter stand-by power and the bias power. The equation for output preload resistance accounts for bias power estimated at 2.5 mW.

$$R_{PL} = \frac{V_{OCV}^2}{P_{SB\_CONV} - 2.5 \text{ mW}}$$

(8)

The capacitor bulk voltage for the loss estimation is the highest voltage for the stand-by power measurement, typically 325  $V_{DC}$ .

For the total stand-by power estimation add an estimated 2.5 mW for snubber loss to the converter stand-by power loss.

$$P_{SB} = P_{SB\_CONV} + 2.5 \,\text{mW} \tag{9}$$

### Input Bulk Capacitance and Minimum Bulk Voltage

Determine the minimum voltage on the input capacitance,  $C_{B1}$  and  $C_{B2}$  total, in order to determine the maximum Np to Ns turns ratio of the transformer. The input power of the converter based on target full-load efficiency, minimum input RMS voltage, and minimum AC input frequency are used to determine the input capacitance requirement.

Maximum input power is determined based on V<sub>OCV</sub>, I<sub>OCC</sub>, and the full-load efficiency target.

$$P_{IN} = \frac{V_{OCV} \times I_{OCC}}{\eta}$$

(10)

The below equation provides an accurate solution for input capacitance based on a target minimum bulk capacitor voltage. To target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance.

$$C_{\text{BULK}} = \frac{2P_{\text{IN}} \times \left(0.25 + \frac{1}{2\pi} \times \arcsin\left(\frac{V_{\text{BULK(min)}}}{\sqrt{2} \times V_{\text{IN(min)}}}\right)\right)}{\left(2V_{\text{IN(min)}}^2 - V_{\text{BULK(min)}}^2\right) \times f_{\text{LINE}}}$$

(11)

### Transformer Turns Ratio, Inductance, Primary-Peak Current

The maximum primary-to-secondary turns ratio can be determined by the target maximum switching frequency at full load, the minimum input capacitor bulk voltage, and the estimated DCM quasi-resonant time.

Initially determine the maximum available total duty cycle of the on time and secondary conduction time based on target switching frequency and DCM resonant time. For DCM resonant time, assume 500 kHz if you do not have an estimate from previous designs. For the transition mode operation limit, the period required from the end of secondary current conduction to the first valley of the  $V_{CE}$  voltage is  $\frac{1}{2}$  of the DCM resonant period, or 1  $\mu$ s assuming 500-kHz resonant frequency.  $D_{MAX}$  can be determined using the equation below.

$$D_{MAX} = 1 - \left(\frac{t_R}{2} \times f_{MAX}\right) - D_{MAGCC}$$

(12)

Once  $D_{MAX}$  is known, the maximum turns ratio of the primary to secondary can be determined with the equation below.  $D_{MAGCC}$  is defined as the secondary diode conduction duty cycle during constant-current, CC, operation. It is set internally by the UCC28720 at 0.425. The total voltage on the secondary winding needs to be determined; which is the sum of  $V_{OCV}$ , the secondary rectifier  $V_F$ , and the cable compensation voltage ( $V_{OCBC}$ ). For the 5-V USB charger applications, a turns ratio range of 13 to 15 is typically used.

$$N_{PS(max)} = \frac{D_{MAX} \times V_{BULK(min)}}{D_{MAGCC} \times (V_{OCV} + V_F + V_{OCBC})}$$

(13)

Once an optimum turns ratio is determined from a detailed transformer design, use this ratio for the following parameters.

The UCC28720 constant-current regulation is achieved by maintaining a maximum  $D_{MAG}$  duty cycle of 0.425 at the maximum primary current setting. The transformer turns ratio and constant-current regulating voltage determine the current sense resistor for a target constant current.

Since not all of the energy stored in the transformer is transferred to the secondary, a transformer efficiency term is included. This efficiency number includes the core and winding losses, leakage inductance ratio, and bias power ratio to rated output power. For a 5-V, 1-A charger example, bias power of 1.5% is a good estimate. An overall transformer efficiency of 0.9 is a good estimate to include 3.5% leakage inductance, 5% core and winding loss, and 1.5% bias power.

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2l_{OCC}} \times \sqrt{\eta_{XFMR}}$$

(14)

The primary transformer inductance can be calculated using the standard energy storage equation for flyback transformers. Primary current, maximum switching frequency and output and transformer power losses are included in the equation below. Initially determine transformer primary current.

Primary current is simply the maximum current sense threshold divided by the current sense resistance.

$$I_{PP(max)} = \frac{V_{CST(max)}}{R_{CS}}$$

(15)

$$L_{P} = \frac{2(V_{OCV} + V_{F} + V_{OCBC}) \times I_{OCC}}{\eta_{XFMR} \times I_{PP(max)}^{2} \times f_{MAX}}$$

(16)

The secondary winding to auxiliary winding transformer turns ratio ( $N_{AS}$ ) is determined by the lowest target operating output voltage in constant-current regulation and the VDD UVLO of the UCC28720. There is additional energy supplied to VDD from the transformer leakage inductance energy which allows a lower turns ratio to be used in many designs.

$$N_{AS} = \frac{V_{DD(off)} + V_{FA}}{V_{OCC} + V_{F}}$$

(17)

### **Transformer Parameter Verification**

The transformer turns ratio selected affects the transistor  $V_C$  and secondary rectifier reverse voltage so these should be reviewed. The UCC28720 does require a minimum on time of the transistor  $(t_{ON})$  and minimum  $D_{MAG}$  time  $(t_{DMAG})$  of the secondary rectifier in the high line, minimum load condition. The selection of  $f_{MAX}$ ,  $L_P$  and  $R_{CS}$  affects the minimum  $t_{ON}$  and  $t_{DMAG}$ .

The secondary rectifier and transistor voltage stress can be determined by the equations below.

$$V_{REV} = \frac{V_{IN(max)} \times \sqrt{2}}{N_{PS}} + V_{OCV} + V_{OCBC}$$

(18)

For the transistor V<sub>C</sub> voltage stress, an estimated leakage inductance voltage spike (V<sub>LK</sub>) needs to be included.

$$V_{CPK} = \left(V_{IN(max)} \times \sqrt{2}\right) + \left(V_{OCV} + V_F + V_{OCBC}\right) \times N_{PS} + V_{LK}$$

(19)

Equation 20 and Equation 21 are used to determine if the minimum t<sub>ON</sub> target of 300 ns and minimum t<sub>DMAG</sub> target of 1.2 µs is achieved.

$$t_{ON(min)} = \frac{L_{P}}{V_{IN(max)} \times \sqrt{2}} \times \frac{I_{PP(max)} \times V_{CST(min)}}{V_{CST(max)}}$$

(20)

$$t_{DMAG(min)} = \frac{t_{ON} \times V_{IN(max)} \times \sqrt{2}}{N_{PS} \times (V_{OCV} + V_F)}$$

(21)

## **Output Capacitance**

The output capacitance value is typically determined by the transient response requirement from no-load. For example, in some USB charger applications there is a requirement to maintain a minimum  $V_O$  of 4.1 V with a load-step transient of 0 mA to 500 mA . The equation below assumes that the switching frequency can be at the UCC28720 minimum of  $f_{SW(min)}$ .

$$C_{OUT} = \frac{I_{TRAN} \left( \frac{1}{f_{SW(min)}} + 150 \,\mu\text{s} \right)}{V_{O\Delta}}$$

(22)

Another consideration of the output capacitor(s) is the ripple voltage requirement which is reviewed based on secondary peak current and ESR. A margin of 20% is added to the capacitor ESR requirement in the equation below.

$$R_{ESR} = \frac{V_{RIPPLE} \times 0.8}{I_{PP(max)} \times N_{PS}}$$

(23)

### VDD Capacitance, C<sub>DD</sub>

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage in constant-current regulation. At this time the auxiliary winding can sustain the voltage to the UCC28720. The total output current available to the load and to charge the output capacitors is the constant-current regulation target. The equation below assumes the output current of the flyback is available to charge the output capacitance until the minimum output voltage is achieved. There is 1 V of margin added to VDD in the calculation.

$$C_{DD} = \frac{\left(I_{RUN} + L_{DRS(max)} \times \left(I - D_{magec}\right)\right) \times \frac{C_{OUT} \times V_{OCC}}{I_{O}}}{\left(V_{DD(on)} - V_{DD(off)}\right) - 1V}$$

(24)

## VS Resistor Divider, Line Compensation, and Cable Compensation

The VS divider resistors determine the output voltage regulation point of the flyback converter, also the high-side divider resistor ( $R_{S1}$ ) determines the line voltage at which the controller enables continuous DRV operation.  $R_{S1}$  is initially determined based on transformer auxiliary to primary turns ratio and desired input voltage operating threshold.

$$R_{S1} = \frac{V_{IN(run)} \times \sqrt{2}}{N_{PA} \times I_{VSL(run)}}$$

(25)

The low-side VS pin resistor is selected based on desired V<sub>O</sub> regulation voltage.

$$R_{S2} = \frac{R_{S1} \times V_{VSR}}{N_{AS} \times (V_{OCV} + V_F) - V_{VSR}}$$

(26)

The UCC28720 can maintain tight constant-current regulation over input line by utilizing the line compensation feature. The line compensation resistor ( $R_{LC}$ ) value is determined by current flowing in  $R_{S1}$  and expected base drive and transistor turn-off delay. Assume a 50-ns internal delay in the UCC28720.

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times t_D \times N_{PA}}{L_P}$$

(27)

The UCC28720 has adjustable cable drop compensation. The resistance for the desired compensation level at the output terminals can be determined using Equation 28.

$$R_{CBC} = \frac{V_{CBC(max)} \times 3 k\Omega \times (V_{OCV} + V_F)}{V_{VSR} \times V_{OCBC}} - 28 k\Omega$$

(28)

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| UCC28720D             | Active | Production    | SOIC (D)   7   | 75   TUBE             | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | U28720           |

| UCC28720D.B           | Active | Production    | SOIC (D)   7   | 75   TUBE             | -    | Call TI                       | Call TI                    | -40 to 125   |                  |

| UCC28720DR            | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | U28720           |

| UCC28720DR.B          | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | -    | Call TI                       | Call TI                    | -40 to 125   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

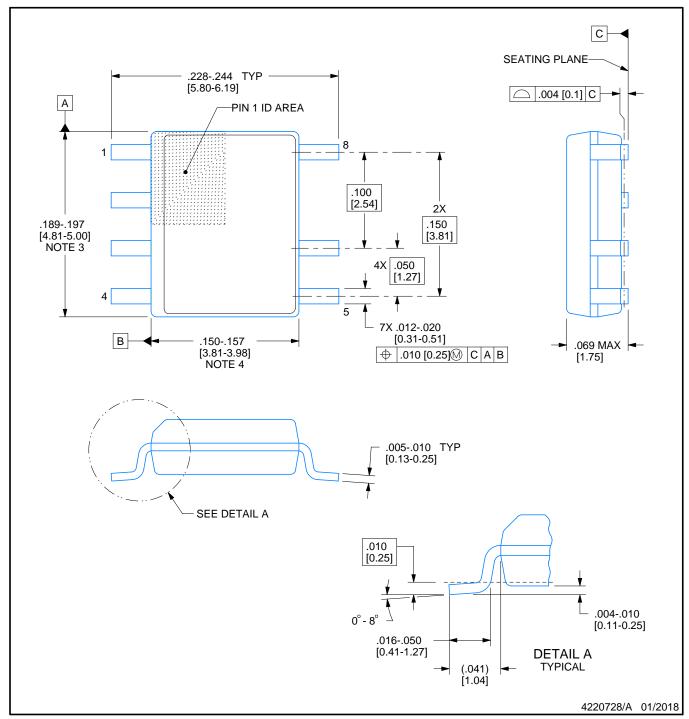

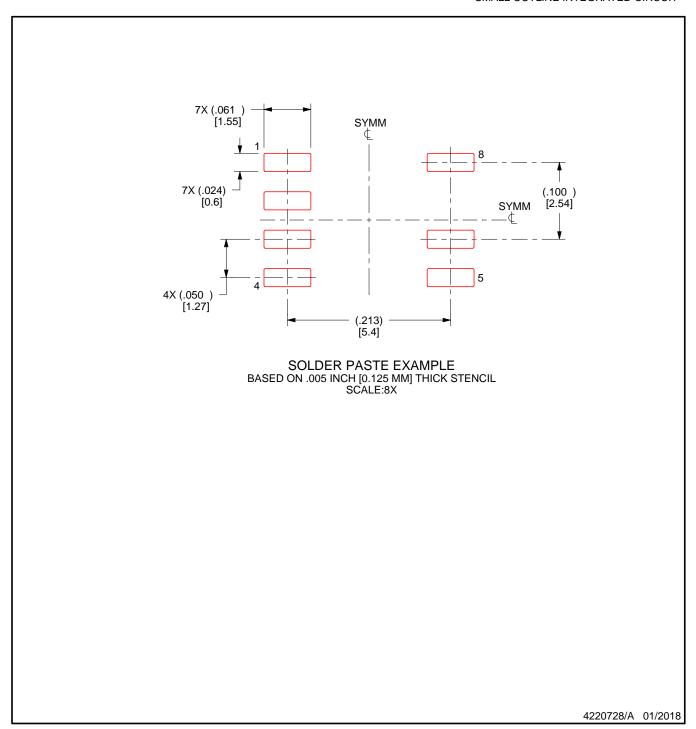

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

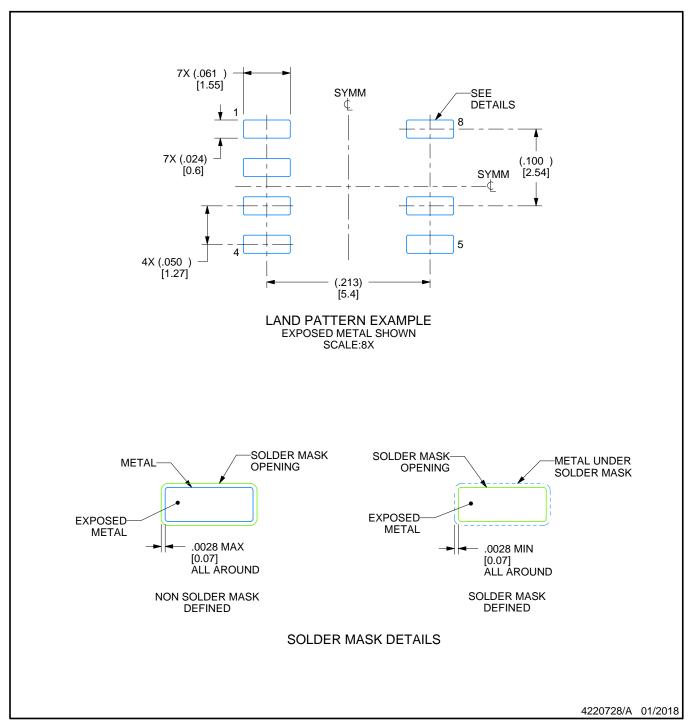

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月