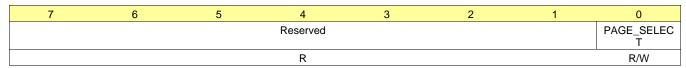

TUSB422

ZHCSFQ2C -NOVEMBER 2016-REVISED JUNE 2018

# TUSB422 具有供电功能的 USB Type-C™ 端口控制

## 1 特性

- 支持 USB Type-C™1.2 和电源供电 (PD) 规范

- 支持 I<sup>2</sup>C 接口 (TCPCi) 的 USB PD 物理层

- 5V 至 24V 拉灌电压

- 2.5W VCONN 开关

- 交替模式协商

- 针对支持 自主双角色端口 (DRP) 的 应用进行了优化。

- 软件可配置为专用主机、专用器件或兼具两种角色

- 下行数据端口 (DFP)、上行数据端口 (UFP) 和 双角色端口 (DRP)

- 连接/断开 USB 端口

- 电缆方向检测

- 电流模式通告与检测

- 调试和音频附件支持

- 有源电缆检测

- 为有源电缆提供 VCONN

- 支持电量耗尽的电池

- 集成过热检测二极管 (OTSD)

- VBUS 检测与放电控制

- 电源电压: 2.7V 至 5.5V

- 低电流消耗

- -40°C 至 85°C 的工业温度范围

#### 2 应用

- 智能手机

- 平板电脑、笔记本电脑、台式机

- 墙式充电器、移动电源

#### 3 说明

TUSB422 是一款 USB PD PHY,可在 USB Type-C 端口中实现 USB Type-C 生态系统所需的配置通道 (CC)逻辑。该器件集成 USB 双相标记编码 (BMC)供电 (PD)协议的物理层,允许使用功率高达 100W 的电源并支持备用模式接口。具备 USB Type-C端口管理器 (TCPM)的外部处理器通过 I<sup>2</sup>C 接口与 TUSB422 进行通信。

在 TCPM 的控制下,TUSB322 使用 CC 引脚确定端口连接状态、电缆方向并进行角色检测和 USB Type-C电流模式控制。TUSB422 可根据应用配置为 DFP、UFP 或 DRP。TUSB422 应用 VBUS 检测和放电功能,从而实现兼容性 USB Type-C 端口。

TUSB422 集成 2.5W 开关,可为有源电缆提供 VCONN 电源。该器件还提供 VCONN 放电功能。 TUSB422 还支持 USB Type-C 可选 功能, 例如音频 和调试附件。

该器件能够在宽电源范围内工作,功耗较低。 TUSB422 可在工业级温度范围内运行。

#### 器件信息(1)

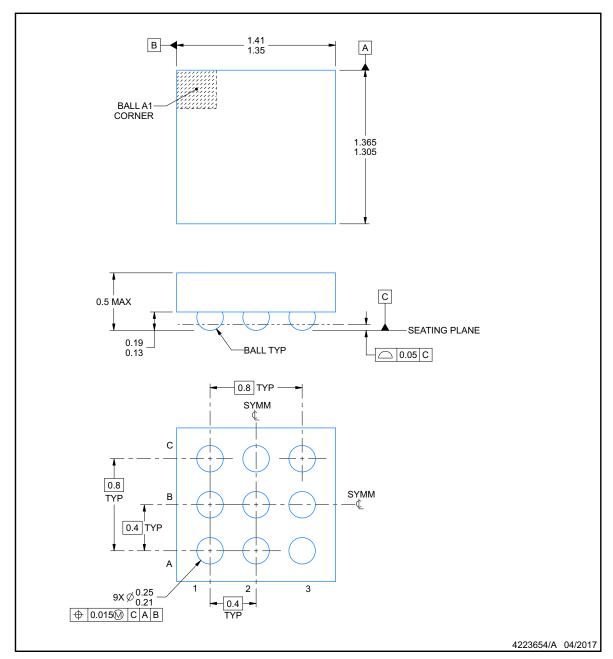

| 器件型号    | 封装       | 封装尺寸 (标称值)                      |

|---------|----------|---------------------------------|

| TUSB422 | WCSP (9) | 1.335mm x 1.380mm,<br>间距为 0.4mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

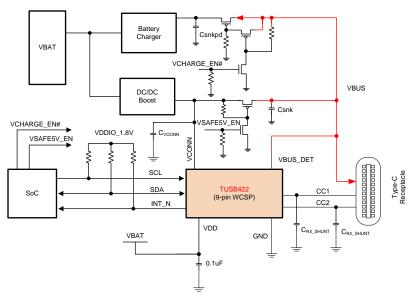

#### 简化电路原理图

#### USB Type-C 智能手机

| 目录 |

|----|

|----|

| 1 | 特性1                                  |    | 7.4 Device Functional Modes    | 17 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                 |    | 7.5 Programming                | 19 |

| 3 | 说明 1                                 |    | 7.6 Register Maps              | 22 |

| 4 | 修订历史记录                               | 8  | Application and Implementation | 63 |

| 5 | Pin Configuration and Functions      |    | 8.1 Application Information    | 63 |

| 6 |                                      |    | 8.2 Typical Application        | 63 |

| O | Specifications                       | 9  | Power Supply Recommendations   | 65 |

|   | 6.2 ESD Ratings                      | 10 | Layout                         |    |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines         |    |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example            |    |

|   | 6.5 Electrical Characteristics 5     | 11 | 器件和文档支持                        |    |

|   |                                      |    | 11.1 接收文档更新通知                  |    |

|   | 6.6 Timing Requirements              |    | 11.2 社区资源                      |    |

| - | 6.7 Typical Characteristics 10       |    | 11.3 商标                        |    |

| 7 | Detailed Description                 |    | 11.4 静电放电警告                    |    |

|   | 7.1 Overview 11                      |    | 11.5 术语表                       |    |

|   | 7.2 Functional Block Diagram 11      | 40 |                                |    |

|   | 7.3 Feature Description              | 12 | 机械、封装和可订购信息                    | 68 |

|   |                                      |    |                                |    |

# 4 修订历史记录

| Cr       | nanges from Revision B (August 2017) to Revision C                                                                                                                                                           | Page |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Changed the VCONN pin description in the Pin Functions table                                                                                                                                                 | 3    |

| •        | Deleted V <sub>RX(FRS PD)</sub> from electrical characteristics                                                                                                                                              | 6    |

| •        | Deleted t <sub>FRSWAPRX</sub> from timing requirements section                                                                                                                                               | 8    |

| •        | Added NOTE: "The TUSB422 supports all PD2.0 and PD 3.0" to the USB PD BMC PHY section                                                                                                                        |      |

| •        | Deleted text from the first paragraph of the Fast Role Swap secton.                                                                                                                                          | 16   |

| •        | From: Once VBUS is at VSafe0V, change To: Once VBUS is at VSafe0V, disable AUTO_DISCHARGE_DISCONNECT in Power Control Register and change                                                                    | 17   |

| •        | From: Once VBUS is at vSafe5V, the TCPM should then send PS_RDY to its port partner. To: Once VBUS is at vSafe5V, the TCPM should update message header information and then send PS_RDY to its port partner | 17   |

| •        | Added NOTE: "During Power-role swap, the TUSB422" to the Power Role Swap section                                                                                                                             | 18   |

| •        | Added NOTE: "When exiting dead battery mode" to the Dead Battery Mode section                                                                                                                                | 18   |

| •        | Changed bit 0 From: VCONN_OC_FAULT To Reserved in 图 31 and 表 28                                                                                                                                              | 37   |

| •        | Added text: "VBUS present status may be invalid" to the Bit 2 VBUS_PRESENT description in 表 31                                                                                                               | 40   |

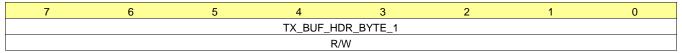

| •        | Added text: "Before attempting to transmit" to the <i>Transmit Register (address = 0x50) [reset = 0x00]</i> register                                                                                         | 51   |

| •        | Changed bit 0 From: FAST_ROLE_SWAP_STAT To Reserved in 图 65 and 表 62                                                                                                                                         | 56   |

| •        | Changed bit 0 From: FAST_ROLE_SWAP_MASK To Reserved in 图 66 and 表 63                                                                                                                                         | 57   |

| <u>•</u> | Changed bit 3 From: FASTROLE_RX_EN To Reserved in 图 69 and 表 66                                                                                                                                              | 59   |

| Cł       | nanges from Revision A (April 2017) to Revision B                                                                                                                                                            | Page |

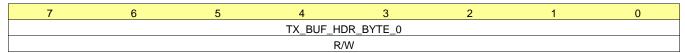

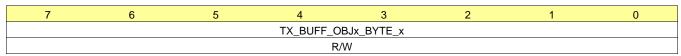

| •        | Changed Bit TX_BUFF_OBJx_BYTE_x From: Read Only To Read/Wright in 图 54 and 表 51                                                                                                                              | 52   |

| Cł       | nanges from Original (November 2016) to Revision A                                                                                                                                                           | Page |

| •        | Deleted text: "Following sentence optional" from the ESD Ratings table notes                                                                                                                                 | 4    |

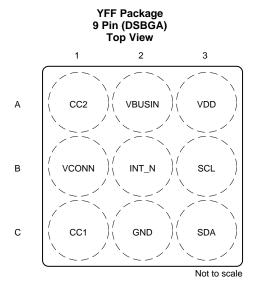

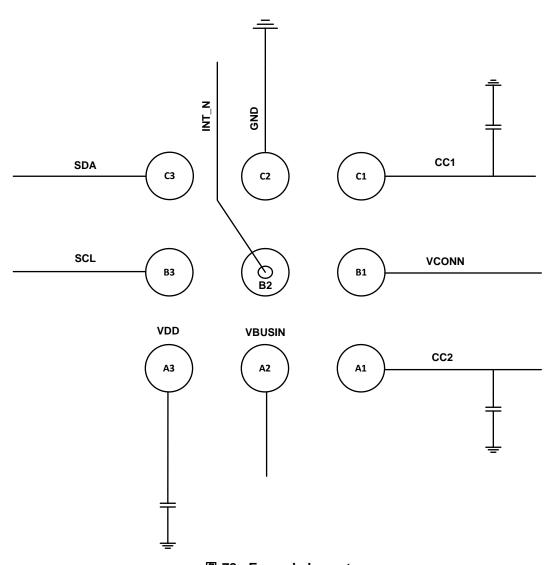

# **5 Pin Configuration and Functions**

## **Pin Functions**

| PIN I/O  |        |                         | DESCRIPTION                                                                                                                                                                                                   |  |  |

|----------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. NAME |        | 1/0                     | DESCRIPTION                                                                                                                                                                                                   |  |  |

| A1       | CC2    | I/O (FS)                | Type-C Configuration channel signal 2. Used for connector orientation, connection detection and removal, current capabilities, and PD communication. This pin requires an external $C_{RX(SHUNT)}$ capacitor. |  |  |

| A2       | VBUSIN | 1                       | 5-24 V VBUS input voltage. Tie directly to VBUS at Type-C connector.                                                                                                                                          |  |  |

| A3       | VDD    | Р                       | 2.7 V to 5.5 V Positive supply voltage                                                                                                                                                                        |  |  |

| B1       | VCONN  | Р                       | 2.7 V to 5.5 V VCONN. VCONN voltage should be at a valid stable value before software closes the VCONN switch. If VCONN support is not required in the system, then this pin can be left floating.            |  |  |

| B2       | INT_N  | O (FS)                  | Open drain output. Asserted low to indicate status change occurred. Requires an external pull-up resistor.                                                                                                    |  |  |

| В3       | SCL    | I/O Open-<br>drain (FS) | SCL - I2C communication clock signal. Requires an external pull-up resistor.                                                                                                                                  |  |  |

| C1       | CC1    | I/O (FS)                | Type-C Configuration channel signal 1. Used for connector orientation, connection detection and removal, current capabilities, and PD communication. This pin requires an external $C_{RX(SHUNT)}$ capacitor. |  |  |

| C2       | GND    | G                       | Ground                                                                                                                                                                                                        |  |  |

| С3       | SDA    | I/O Open-<br>drain (FS) | SDA - I2C communication data signal. Requires an external pull-up resistor.                                                                                                                                   |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                                       | MIN  | MAX | UNIT |

|----------------------|---------------------------------------|------|-----|------|

| Supply Voltage       | $V_{DD}$                              | -0.3 | 6   | V    |

| VCONN Switch voltage | VCONN                                 | -0.3 | 6   | V    |

|                      | INT_N, SDA, SCL                       | -0.3 | 6   | V    |

| Control pins         | CC1, CC2                              | -0.3 | 6   | V    |

|                      | VBUSIN                                | -0.3 | 26  | V    |

| Storage temperatu    | Storage temperature, T <sub>stg</sub> |      | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±1500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                      |                                                                       | MIN  | NOM | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------|------|-----|-----|------|

| $V_{DD}$             | Supply voltage range                                                  | 2.7  | 3.7 | 5.5 | V    |

| VCONN                | VCONN voltage range                                                   | 2.7  | 5   | 5.5 | V    |

| VBUSIN               | System VBUS voltage                                                   | 0    | 5   | 24  | V    |

| V <sub>I2C_SYS</sub> | System I2C voltage range that SDA and SCL are pulled up to            | 1.65 | 1.8 | 3.6 | V    |

| т                    | Operating Free air temperature with VCONN not supported in the system | -40  | 25  | 105 | °C   |

| T <sub>A</sub>       | Operating Free air temperature with VCONN supported in the system     | -40  | 25  | 85  | °C   |

| T <sub>J</sub>       | Junction temperature                                                  | -40  |     | 125 | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | TUSB422<br>YFF (DSBGA) | UNIT   |

|-----------------------|----------------------------------------------|------------------------|--------|

|                       |                                              | 9 PINS                 | C.I.I. |

| $R_{\Theta JA}$       | Junction-to-ambient thermal resistance       | 114.3                  | °C/W   |

| R <sub>⊕JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.7                    | °C/W   |

| $R_{\Theta JB}$       | Junction-to-board thermal resistance         | 24.9                   | °C/W   |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3                    | °C/W   |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 24.9                   | °C/W   |

| R <sub>⊕JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | NA                     | °C/W   |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

|                                   | PARAMETER                                                                                                                             | TEST CONDITIONS                          | MIN  | TYP | MAX  | UNIT |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|-----|------|------|

| Power Consu                       | ımption                                                                                                                               |                                          |      |     |      |      |

| I <sub>(UNATTACHED_</sub><br>UFP) | UFP Current consumption in<br>Unattached.SNK when port is<br>unconnected and waiting for<br>connection                                | VDD = 3.7V                               |      | 10  |      | μΑ   |

| I <sub>(UNATTACHED_</sub><br>DRP) | DRP Current consumption while toggling between Unattached.SNK and Unattached.SRC when port is unconnected and waiting for connection. | VDD = 3.7V                               |      | 12  |      | μΑ   |

| I <sub>(UNATTACHED_</sub><br>DFP) | DFP Current consumption in<br>Unattached.SRC when port is<br>unconnected and waiting for<br>connection                                | VDD = 3.7V                               |      | 11  |      | μΑ   |

| I <sub>(ACTIVE_UFP)</sub>         | UFP Current consumption in attached.SNK Active Mode. PD Disabled.                                                                     | VDD = 3.7V                               |      | 330 |      | μΑ   |

| I <sub>(ACTIVE_UFP_P</sub> D)     | UFP current consumption in attached.SNK with PD enabled and transmitting continuous BIST Carrier Mode 2.                              | VDD = 3.7V;<br>TX_CARRIER_MODE2_SEL = 1; |      | 5.2 |      | mA   |

| CC pins (CC1                      | and CC2)                                                                                                                              |                                          |      |     | ·    |      |

| V <sub>CC(USB_DB)</sub>           | Voltage on both CC pins when in dead<br>battery and the attached DFP is<br>presenting default current<br>advertisement                | VDD = 0V                                 | 0.25 |     | 1.5  | V    |

| V <sub>CC(MED_DB)</sub>           | Voltage on both CC pins when in dead<br>battery and the attached DFP is<br>presenting medium current (1.5A)<br>advertisement          | VDD = 0V                                 | 0.45 |     | 1.5  | V    |

| V <sub>CC(HIGH_DB)</sub>          | Voltage on both CC pins when in dead<br>battery and the attached DFP is<br>presenting high current (3.0A)<br>advertisement            | VDD = 0V                                 | 0.88 |     | 2.18 | V    |

| R <sub>(CC_RD)</sub>              | Pull-down resistor when in UFP or DRP mode                                                                                            | VDD = 2.7V to 5.5V                       | 4.6  | 5.1 | 5.6  | kΩ   |

| R <sub>(CC_RA)</sub>              | Pull-down resistor for active cable                                                                                                   | VDD = 2.7V to 5.5V                       | 0.8  | 1   | 1.2  | kΩ   |

| I <sub>CC(LKG)</sub>              | Leakage current through CC pins                                                                                                       | VDD = 0V; VCONN = 0V; CC pin = 5.5V      |      |     | 1.36 | mA   |

| V <sub>(UFP_CC_USB</sub> )        | Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising default current source capability      |                                          | 0.25 |     | 0.61 | V    |

# **Electrical Characteristics (continued)**

|                                  | PARAMETER                                                                                                                                       | TEST CONDITIONS | MIN     | TYP   | MAX    | UNIT |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-------|--------|------|

| V <sub>(UFP_CC_MED</sub> )       | Voltage level range for detecting a<br>DFP attach when configured as a UFP<br>and DFP is advertising medium (1.5A)<br>current source capability |                 | 0.7     |       | 1.16   | V    |

| V <sub>(UFP_CC_HIG</sub>         | Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising high (3.0A) current source capability            |                 | 1.31    |       | 2.04   | V    |

| V <sub>TH(DFP_CC_U</sub>         | Voltage threshold for detecting a UFP attach when TUSB422 is advertising default current source capability.                                     |                 | 1.51    | 1.6   | 1.64   | V    |

| V <sub>TH(DFP_CC_M</sub><br>ED)  | Voltage threshold for detecting a UFP attach when TUSB422 is advertising medium current (1.5A) source capability.                               |                 | 1.51    | 1.6   | 1.64   | V    |

| V <sub>TH(DFP_CC_HI</sub><br>GH) | Voltage threshold for detecting a UFP attach when TUSB422 is advertising high current (3.0A) source capability.                                 |                 | 2.46    | 2.6   | 2.74   | V    |

| V <sub>TH(AC_CC_US</sub>         | Voltage threshold for detecting a active cable attach when advertising default current                                                          |                 | 0.15    | 0.2   | 0.25   | V    |

| V <sub>TH(AC_CC_ME</sub>         | Voltage threshold for detecting a active cable attach when advertising medium current                                                           |                 | 0.35    | 0.4   | 0.45   | V    |

| V <sub>TH(AC_CC_HI</sub><br>GH)  | Voltage threshold for detecting a active cable attach when advertising high current.                                                            |                 | 0.76    | 0.8   | 0.84   | V    |

| I <sub>CC(DEFAULT_P</sub> )      | Default mode pull-up current source when advertising default current.                                                                           |                 | 64      | 80    | 96     | μΑ   |

| I <sub>CC(MED_P)</sub>           | Medium (1.5A) mode pull-up current source when advertising medium current.                                                                      |                 | 166     | 180   | 194    | μA   |

| I <sub>CC(HIGH_P)</sub>          | High (3.0A) mode pull-up current source when advertising high current.                                                                          | VDD > 3.0V      | 304     | 330   | 356    | μΑ   |

| R <sub>TX(PD)</sub>              | Output impedance of CC1/CC2 during TX when operating in PD mode and driving the CC line.                                                        | At 750KHz       | 33      | 48    | 75     | Ω    |

| R <sub>TX(FRS_PD)</sub>          | Fast Role Swap request transmit<br>driver resistance (excluding cable<br>resistance)                                                            |                 |         |       | 5      | Ω    |

| $V_{OH(PD)}$                     | Transmit high voltage when operating in PD mode                                                                                                 |                 | 1.05    | 1.125 | 1.2    | V    |

| V <sub>OL(PD)</sub>              | Transmit low voltage when operating in PD mode.                                                                                                 |                 |         |       | 0.07   | V    |

| R <sub>RX(PD)</sub>              | Receiver input impedance. Does Not include pull-up or pulldown resistance from cable detect.                                                    | TX is Hi-Z      | 1       |       |        | ΜΩ   |

| V <sub>IH(PD_SRC)</sub>          | Input high voltage when sourcing power. Selected when POWER_ROLE = 1.                                                                           |                 | 0.8925  |       | 1.5325 | V    |

| V <sub>IH(PD_SNK)</sub>          | Input high voltage when sinking power. Selected when POWER_ROLE = 0.                                                                            |                 | 0.6425  |       | 1.5325 | V    |

| V <sub>IL(PD_SRC)</sub>          | Input low voltage when sourcing power. Selected when POWER_ROLE = 1.                                                                            |                 | -0.3325 |       | 0.4825 | V    |

| V <sub>IL(PD_SNK)</sub>          | Input low voltage when sinking power. Selected when POWER_ROLE = 0.                                                                             |                 | -0.3325 |       | 0.2325 | V    |

# **Electrical Characteristics (continued)**

|                                     | PARAMETER                                                                    | TEST CONDITIONS                 | MIN | TYP  | MAX  | UNIT  |

|-------------------------------------|------------------------------------------------------------------------------|---------------------------------|-----|------|------|-------|

| C <sub>RX(SHUNT)</sub>              | External shunt capacitance on both CC1 and CC2.                              |                                 | 200 |      | 450  | pF    |

| Control pins:                       | INT_N                                                                        |                                 |     |      |      |       |

| (INTN_LEAK)                         | INT_N leakage                                                                | VDD = 0V; 0 < INT_N < 3.3V      | -1  |      | 1    | μΑ    |

| $V_{OL}$                            | Low-level signal output voltage                                              | IOL = -2mA                      |     |      | 0.4  | V     |

| 2C (SDA and                         | SCL). VDD must be above 3V to opera                                          | ate at 3.3V I2C levels          |     |      |      |       |

| V <sub>IH(I2C)</sub>                | High-level input signal voltage                                              |                                 | 1.2 |      |      | V     |

| V <sub>IL(I2C)</sub>                | Low-level input signal voltage                                               |                                 |     |      | 0.4  | V     |

| V <sub>OL(I2C)</sub>                | Low-level signal output voltage (opendrain)                                  |                                 |     |      | 0.4  | V     |

| OL(I2C)                             | Low level output current                                                     |                                 | 6   |      |      | mA    |

| (I2C_LKG)                           | Leakage through SDA and SCL pins                                             | VDD = 0V; pin pulled up to 3.6V | -1  |      | 1    | μΑ    |

| C <sub>(I2C)</sub>                  | Capacitance for SDA and SCL pins                                             |                                 |     |      | 10   | pF    |

| C <sub>(I2C_FM+_BUS</sub>           | I2C bus capacitance for FM+ (1MHz)                                           |                                 |     |      | 150  | pF    |

| C <sub>(I2C_FM_BUS)</sub>           | I2C bus capacitance for FM (400KHz)                                          |                                 |     |      | 150  | pF    |

| R <sub>(EXT_I2C_FM+</sub>           | External resistors on both SDA and SCL when operating at FM+ (1MHz)          | $C_{(I2C\_FM+\_BUS)} = 150pF$   | 620 | 820  | 910  | Ω     |

| R <sub>(EXT_I2C_FM)</sub>           | External resistors on both SDA and SCL when operating at FM (400KHz)         | $C_{(I2C\_FM\_BUS)} = 150pF$    | 620 | 1500 | 2200 | Ω     |

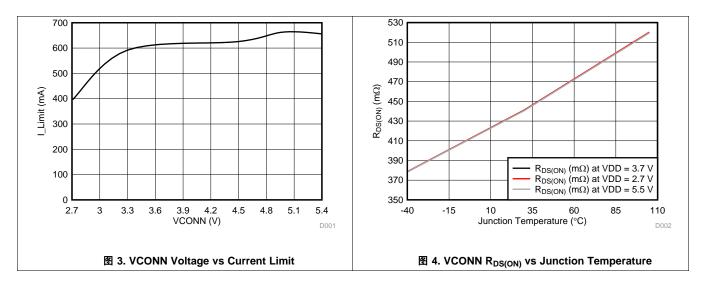

| VCONN                               |                                                                              |                                 |     |      |      |       |

| R <sub>DS(ON)</sub>                 | ON resistance of the VCONN power FET.                                        |                                 |     | 0.4  | 0.75 | Ω     |

| V <sub>(PASS)</sub>                 | Voltage to pass through VCONN power FET                                      |                                 |     |      | 5    | V     |

| I <sub>(VCONN)</sub>                | VCONN current limit; VCONN is disconnected above this voltage.               |                                 | 500 | 650  | 850  | mA    |

| V <sub>(VCONN_PRES</sub> )          | Threshold for detecting Vconn present.                                       |                                 | 2   |      | 2.4  | V     |

| C <sub>(VCONN)</sub>                | Bulk capacitance on VCONN; Placed on VCONN pin supply                        |                                 | 10  |      | 200  | μF    |

| R <sub>(VCONN_DIS)</sub>            | Resistance to GND when Vconn discharge is enabled                            |                                 | 4.6 | 5.1  | 5.6  | ΚΩ    |

| VBUSIN                              |                                                                              |                                 |     |      |      |       |

| C <sub>(BULK_SRC)</sub>             | Source External bulk capacitance when operating as VBUS Source.              |                                 | 10  |      | 150  | μF    |

| C <sub>(SNK)</sub>                  | Sink External bulk capacitance on VBUS at connector                          |                                 | 1   |      | 10   | μF    |

| C <sub>(SNKPD)</sub>                | Sink External bulk capacitance on VBUS after success PD negotiation          |                                 | 1   |      | 100  | μF    |

| R <sub>(BLEED)</sub>                | Resistance to gnd when bleed discharge is enabled                            |                                 | 8   | 10   | 12.5 | ΚΩ    |

| V <sub>(SRCSLEWNE</sub><br>G)       | VBUS discharge maximum slew rate                                             |                                 |     |      | -30  | mV/μs |

| V <sub>(VBUS_MEASU</sub><br>RE_ACC) | VBUS_VOLTAGE register measurement accuracy                                   |                                 | -2  |      | 2    | %     |

| OTSD                                |                                                                              |                                 |     |      |      |       |

| T <sub>(OTSD1)</sub>                | TJ over temperature trip threshold resulting in VCONN turn off and flag set. |                                 |     | 150  |      | °C    |

| Set.                                |                                                                              |                                 |     |      |      |       |

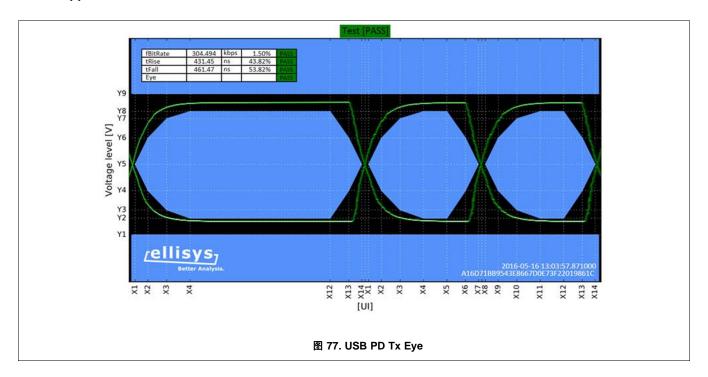

# 6.6 Timing Requirements

|                      |                                                                                                                 |                                                              | MIN          | NOM M | AX  | UNIT |

|----------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------|-------|-----|------|

| CC pins in PI        | O mode                                                                                                          |                                                              |              |       |     |      |

| F <sub>br_PD</sub>   | Bit Rate                                                                                                        |                                                              | 270          | 300   | 330 | Kbps |

| UI_PD                | Unit Interval                                                                                                   |                                                              | 3.03         | 3.3   | 3.7 | μs   |

| RISE_PD              | Rise time                                                                                                       | 10% to 90%; C <sub>RX(SHUNT)</sub> = 200pF                   | 300          |       |     | ns   |

| FALL_PD              | Fall time                                                                                                       | 90% to 10%; C <sub>RX(SHUNT)</sub> = 200pF                   | 300          |       |     | ns   |

| RxFilter             | Rx Bandwidth limiting filter                                                                                    |                                                              | 100          |       |     | ns   |

| InterFrameCap        | Time from the end of last bit of a frame until the state of the first bit of the next pre-amble                 |                                                              | 25           |       | 50  | μs   |

| StartDrive           | Time before the start of the first bit of<br>the preamble when the transmitter<br>shall start driving the line. |                                                              | -1           |       | 1   | μs   |

| EndDriveBMC          | Time to cease driving the line after the end of the last bit of a frame                                         |                                                              |              |       | 23  | μs   |

| HoldLowBMC           | Time to cease driving the line after the final high-to-low transition                                           |                                                              | 1            |       | 23  | μs   |

| nTransitionC<br>ount | Transitions for signal detect                                                                                   | Number of transitions to be detected to declare bus non-idle | 3            |       |     |      |

| FRSWAPTX             | Fast Role Swap request transmit duration                                                                        |                                                              | 60           |       | 120 | μs   |

| 2C (SDA and          | SCL)                                                                                                            |                                                              | 1            |       |     |      |

| SCL                  | SCL clock frequency                                                                                             |                                                              | 0.001        |       | 1   | MHz  |

| HD;STA               | Hold time (repeated) start condition                                                                            |                                                              | 0.26         |       |     | μs   |

| LOW                  | Low period of SCL                                                                                               |                                                              | 0.5          |       |     | μs   |

| HIGH                 | High period of SCL                                                                                              |                                                              | 0.26         |       |     | μs   |

| SU;STA               | Setup time for a repeated start condition                                                                       |                                                              | 0.26         |       |     | μs   |

| HD;DAT               | Data Hold Time                                                                                                  |                                                              | 0            |       |     | μs   |

| SU;DAT               | Data setup time                                                                                                 |                                                              | 50           |       |     | μs   |

| SU;STOP              | Setup time for STOP condition                                                                                   |                                                              | 0.26         |       |     | μs   |

| BUF                  | Bus free time between STOP and START condition                                                                  |                                                              | 0.5          |       |     | μs   |

| VD;DAT               | Data valid time                                                                                                 |                                                              |              | C     | .45 | μs   |

| VD;ACK               | Data valid acknowledge time                                                                                     |                                                              |              | C     | .45 | μs   |

| R_I2C                | Rise time of both SDA and SCL                                                                                   | 30% to 70%                                                   |              |       | 120 | ns   |

| F_I2C                | Fall time of both SDA and SCL                                                                                   | 70% to 30%                                                   | 14           |       | 120 | ns   |

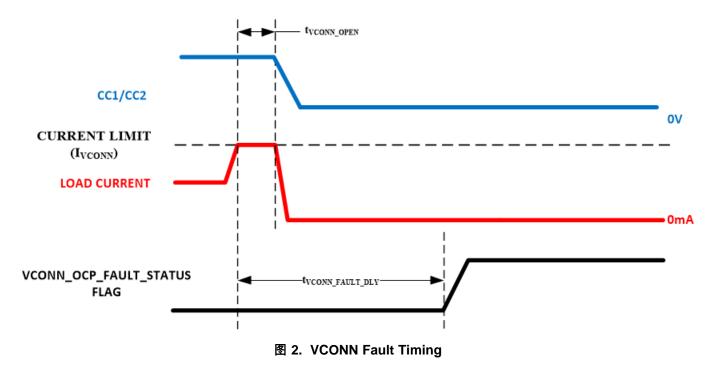

| /CONN Fault          |                                                                                                                 |                                                              | +            |       |     |      |

| VCONN_FAULT          | Delay from Vconn fault detected to Vconn fault status flag set                                                  |                                                              |              |       | 20  | μs   |

| VCONN_OPEN           | Delay from Vconn fault detected to Vconn switch opened                                                          |                                                              |              |       | 50  | ns   |

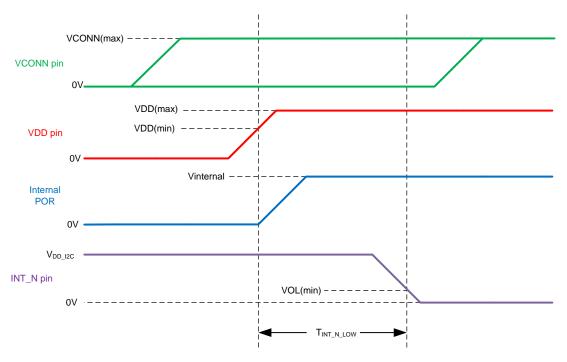

| Power-Up Re          | quirements                                                                                                      |                                                              |              |       |     |      |

| INT_N_LOW            | Time from VDD (min) to TUSB422 asserts INT_N low.                                                               | Measured from VDD(min) to INT_N pin at VOL(min).             |              |       | 4   | ms   |

| VDD_RISE             | VDD rise time                                                                                                   | Measured from 0V to VDD(min)                                 |              |       | 40  | ms   |

| Sampling tim         | ings                                                                                                            |                                                              | <del>.</del> |       |     |      |

| CC_SAMPLE_R          | Delay from Vconn fault detected to Vconn fault status flag set                                                  | CC_SAMPLE_RATE = 2'b01                                       |              | 2     |     | ms   |

| VBUSINRATE           | The sampling interval of VBUS Voltage                                                                           | CC_SAMPLE_RATE = 2'b01                                       |              |       | 2.2 | ms   |

图 1. Power-Up Timing

# 6.7 Typical Characteristics

## 7 Detailed Description

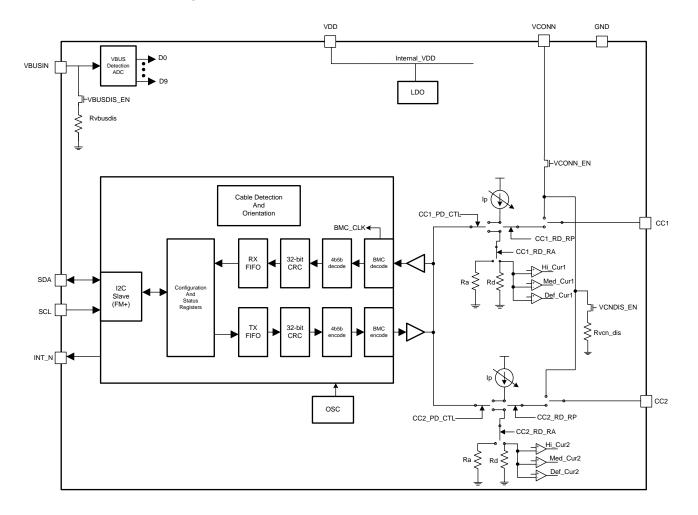

#### 7.1 Overview

The USB Type-C ecosystem operates around a small form factor connector and cable that is flippable and reversible. Due to the nature of the connector, a scheme is needed to determine the connector orientation. Additional schemes are needed to determine when a USB port is attached, determine the acting role of the USB port (Source, Sink, active cable, audio accessory, debug accessory), and communicate Type-C current capabilities. These schemes are implemented over the CC pins according to the *USB Type-C Specification 1.2*. The TUSB422 provides Configuration Channel (CC) logic for determining USB port attach and detach, role detection, cable orientation, and Type-C Current detection/advertisement. The TUSB422 also contains several features such as VCONN sourcing, VBUS enable, VBUS discharge enable, detection of vSafe0V, and low standby current.

The TUSB422 provides a USB Type-C Port Controller Interface (TCPCi) allowing the USB Type-C Port Manager (TCPM) residing in an external microprocessor the ability to determine when a port partner is attached or removed, cable orientation, enable or remove power to the Type-C port. The TUSB422 implements a USB PD BMC physical layer and protocol layer for communication over the Type-C port for purposes like power negotiations, alternate mode enablement (ie DisplayPort over Type-C), and data role negotiations just to mention a few. The TUSB422 takes a message provided by external processor, calculate and append a 32-bit CRC, encode, and transmit the encoded message over the CC wire in the cable. The TUSB422 also receives data from the CC wire and determined if packet is valid or not, respond with GoodCRC, and notify external processor of its arrival by asserting the interrupt (INT\_N).

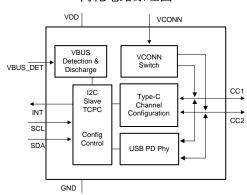

#### 7.2 Functional Block Diagram

## Functional Block Diagram (接下页)

#### 7.2.1 Cables, Adapters, and Direct Connect Devices

*Type-C Specification 1.2* defines several cables, plugs and receptacles to be used to attach ports. TUSB422 supports all cables, receptacles, and plugs.

#### 7.2.1.1 USB Type-C receptacles and Plugs

- USB Type-C receptacle for USB2.0 and USB3.1 and full-featured platforms and devices

- USB Full-Featured Type-C plug

- USB2.0 Type-C Plug

#### 7.2.1.2 USB Type-C Cables

- USB Full-featured Type-C cable with USB3.1 full featured plug

- USB2.0 Type-C cable with USB2.0 plug

- Captive cable with either a USB Full featured plug or USB2.0 plug

#### 7.2.1.3 Direct Connect Devices

TUSB422 supports the attaching and detaching of a direct connect device such as a cradle dock or captive cable.

## 7.3 Feature Description

### 7.3.1 USB PD I2C Type-C Port Controller Interface (TCPC)

The TUSB422 provides up to 1Mbps I2C USB Type-C Port Controller Interface (TCPC) interface and register set allowing for control by external processor. The TUSB422 implements the following optional TCPC features.

- Up to 24 V VBUS Measurement and Alarms

- Default, 1.5 A, and 3 A Source Resistor (Rp) advertisement

- Source VCONN

- VCONN overcurrent fault detection

#### 7.3.2 USB PD BMC PHY

The TUSB422 contains a USB Power Delivery BMC (Bi-phase Mark coded) Baseband phy. The TCPM can enable the TUSB422's USB PD BMC phy for any of the following conditions when the TUSB422 is in Attached.SNK, Attach.SRC, DebugAccessory, or PoweredAccessory state:

Receiver Detect Register is non-zero

The USB PD phy will always be disabled when the TUSB422 is in the unattached mode.

The TUSB422 PD BMC phy receiver threshold will be set based on the value of the POWER\_ROLE field in the Message Header Info register. The default receiver threshold can be changed by setting the VIX\_PD and VIX\_PD\_OVERRIDE fields in the PHY BMC RX Control register.

注

The TUSB422 supports all PD2.0 and PD 3.0 messages except for the PD 3.0 Get Source Capabilities Extended Message. Upon receipt of this message, GoodCRC is not returned, and no Rx alert flag is set. The side effect is that the port partner will retry the message. After the retries are exhausted, the port partner will send a soft reset message.

#### 表 1. Power Role

| POWER-ROLE | V <sub>IH</sub>   | V <sub>IL</sub>   |

|------------|-------------------|-------------------|

| 0          | $V_{IH(PD\_SRC)}$ | $V_{IL(PD\_SRC)}$ |

| 1          | $V_{IH(PD\_SNK)}$ | $V_{IL(PD\_SNK)}$ |

#### 7.3.3 DFP (Downstream Facing Port)

The TUSB422 can be used in applications in which USB devices are connected too. For example, in a desktop application the Type-C port(s) must be able to determine when a device is attached and enable both power (in the form of VBUS) and datapath (either USB data and/or Alternate Mode data like DisplayPort) to attached device. The TUSB422 can be used in a DFP application by programming the *Role Control* register to 0x05. This presents Rp on both of TUSB422 CC pins. When configured as a DFP, the TUSB422 can be used to control the sourcing of VCONN. Control of VBUS source path must be handled outside of the TUSB422.

Upon enabling TUSB422 for DFP, the TUSB422 will continuously monitor both CC1 and CC2 for a connection. After a connection has been determined, the TUSB422 will notify system of event by asserting the INT\_N pin low. Upon detecting assertion of INT\_N, the external microprocessor should read and clear the appropriate *Alert* registers.

The following steps are for initialization of the TUSB422 for DFP operation.

- 1. Upon TUSB422 power-up, the Power Status flag in *Alert* Register should get set indicating TUSB422 is initialized. When set, this flag will cause the INT\_N pin to be assert low.

- 2. SW read the Alert Registers to determine reason for INT\_N assertion. The expectation is Power Status bit (Reg10h bit 1) is set.

- 3. SW read Power Status register and notice that TCPC\_INIT\_STATUS flag is cleared. This indicates TUSB422 is ready.

- 4. SW clear Power Status bit in Alert register by writing a 1'b1 to the bit.

- 5. Program the TUSB422 to present Rp on both CC pins. This is done by writing 0x05 to the *Role Control* register. If advertising greater than default Type-C current is desired, then write 0x15 for 1.5 A current or 0x25 for 3 A current advertisement

- 6. Write Look4Connection command to the Command register.

- 7. The TUSB422 now presents Rp on both CC pins and look for a connection.

Because TUSB422 supports Dead Battery Mode, a dedicated DFP application (like a Car Charger) which uses the TUSB422 should incorporate a diode in the source power path circuitry to block VBUS from being received by another attached DFP/DRP that is providing VBUS.

#### 7.3.4 UFP (Upstream Facing Port)

A UFP is a port that will present Rd on its CC pins and sink VBUS. The TUSB422 functions as a UFP by programming the *Role Control* register to 0x0A. This will cause TUSB422 to present a Rd on both CC pins.

The following steps are for initialization of the TUSB422 for DFP operation.

- 1. Upon TUSB422 power-up, the Power Status flag in *Alert* Register should get set indicating TUSB422 is initialized. When set, this flag will cause the INT\_N pin to be assert low.

- 2. SW read the Alert Registers to determine reason for INT\_N assertion. The expectation is Power Status bit (Reg10h bit 1) is set.

- 3. SW read Power Status register and notice that TCPC\_INIT\_STATUS flag is cleared. This indicates TUSB422 is readv.

- 4. SW clear Power Status bit in Alert register by writing a 1'b1 to the bit.

- 5. Program the TUSB422 to present Rd on both CC pins. This is done by writing 0x0A to the *Role Control* register

- 6. Write Look4Connection command to the Command register.

- 7. The TUSB422 now presents Rd on both CC pins and look for a connection.

#### 7.3.5 DRP (Dual-Role Port)

A Dual-Role port functions as both a DFP and a UFP. The TUSB422 supports DRP either autonomously or manually. In autonomous DRP mode, the TUSB422 state machine toggles between UFP (Rd) and DFP (Rp) on both its CC pins. Autonomous DRP is enabled by programming *Role Control* register to 0x4A and writing Looking4Connection command to the *Command* register. Manual mode is under complete control of external processor. External processor must toggle between writing 0x0A and 0x05 to *Role Control* register at interval defined by Type-C specification summarized in 表 2.

### 表 2. USB Type-C DRP Toggle Requirements

| PARAMETER        | MIN   | MAX    | DESCRIPTION                                                                        |

|------------------|-------|--------|------------------------------------------------------------------------------------|

| t <sub>DRP</sub> | 50 ms | 100 ms | The period a DRP shall complete a Source (Rp) to Sink (Rd) and back advertisement  |

| dcSRC.DRP        | 30%   | 70%    | The percent of time that DRP shall advertise Source (Rp) during $t_{\text{DRP}}$ . |

The following steps are for initialization of the TUSB422 for DRP operation.

- 1. Upon TUSB422 power-up, the Power Status flag in *Alert* Register should get set indicating TUSB422 is initialized. When set, this flag will cause the INT\_N pin to be assert low.

- 2. SW read the *Alert* Registers to determine reason for INT\_N assertion. The expectation is Power Status bit (Reg10h bit 1) is set.

- 3. SW read Power Status register and notice that TCPC\_INIT\_STATUS flag is cleared. This indicates TUSB422 is ready.

- 4. SW clear Power Status bit in *Alert* register by writing a 1'b1 to the bit.

- Program the TUSB422 to present Rd on both CC pins. This is done by writing 0x4A to the Role Control register

- 6. Write Look4Connection command to the Command register.

- 7. The TUSB422 now presents Rd on both Rp pins and look for a connection.

The TUSB422 autonomously toggles between Rd and Rp according to the setting of the *CC General Control* register. If a value other than default value is desired, then CC General control should be programmed to desired value before performing Step 6.

#### 7.3.6 Type-C Current Mode Advertising

Once a valid cable detection and attach have been completed, the TUSB422 has the option to advertise thru CC1/CC2 pins the level of Type-C current a UFP can sink. The TUSB422 supports all three possible Type-C current options: Default (500 mA / 900 mA), Medium(1.5 A), and High (3 A). The current advertisement used by TUSB422 is determined by the value programmed in the *Role Control* register.

注 V<sub>DD</sub> must be greater than 3.0 V to advertise 3 A current.

#### 7.3.7 VBUS Source Enable/Disable Control

The TUSB422 is unable to directly control VBUS enable due to no GPIO support. For this reason, external microprocessor must directly control the Vbus enable. If it wishes, the external microprocessor may notify the TUSB422 when Vbus has been enable/disabled, or raised above vSafe5V value. Notification to TUSB422 comes in the form of writing to the *Command* register any of the following commands: SourceVbusDefaultVoltage (that is, vSafe5V enable), SourceVbusHighVoltage (that is, greater than vSafe5V), or DisableSourceVbus. If these commands are issued to the TUSB422, the TUSB422 ignores these commands.

#### 7.3.8 VBUS Sink Enable/Disable Control

The TUSB422 cannot directly control VBUS Sink path, and therefore; VBUS sink path control is handled externally. Software may write the SinkVbus command to TUSB422 Command register, but the TUSB422 ignores this command.

### 7.3.9 VBUS Monitoring

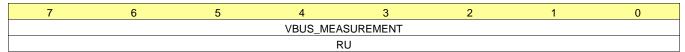

One of the features of USB PD is the ability to raise VBUS above the default vSafe5V level. The ability to monitor the VBUS voltage level is critical to determining when VBUS is at desired level as well as when VBUS is no longer present. The TUSB422 implements measuring of VBUS and the results are stored in the VBUS voltage register. The VBUS voltage measurement is enabled by setting the VBUS\_VOLTAGE\_MONITOR bit in the Power Control register.

#### 7.3.10 VBUS Discharge

The TUSB422 implements internal VBUS discharge. The TUSB422 can be setup to discharge VBUS automatically based on Type-C conditions or software can force a VBUS discharge by setting the FORCE DISCHARGE bit in the *Power Control* register.

The TUSB422 cannot directly control the enable of external VBUS switch. Therefore, software must disable VBUS switch before or immediately after discharge of VBUS is required.

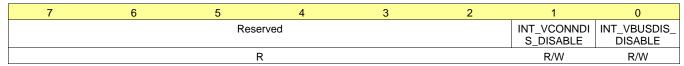

The TUSB422 meets the USB PD standard with a bulk capacitance defined by  $C_{(BULK\_SRC)}$ . If bulk capacitance greater than  $C_{(BULK\_SRC)}$  is required, then external VBUS discharge must be used. If an external VBUS discharge is desired, the TUSB422 internal VBUS discharge circuit can be disabled by setting the INT\_VBUSDIS\_DISABLE bit in the *VBUS and VCONN Control* register.

#### 7.3.11 VBUS to CC Short Detection from Legacy Charger

A legacy Type-A charger will always have VBUS active. When customer plugs a Type-A to Type-C cable into both charger and TUSB422, the TUSB422 immediately detects Rp and then detects VBUS. If for some reason, there is a short between VBUS and CC, the TUSB422 the CC pin is exposed to VBUS voltage. The TUSB422 implements a detection of VBUS to CC short by monitoring voltage level on each the CC pin. If the initial voltage is above 3.5 V and TUSB422 is presenting Rd, then the TUSB422 will set the CC\_FAULT status flag. The TUSB422 keeps the CC1\_STATE and CC2\_STATE flags in the open state. This indicates a invalid connection exist and user should be notified. The TUSB422 continues to look for a valid connection. Once user removes the fault condition (for example, selects a new cable), the TUSB422 indicates a valid connection by updating CC1\_STATE and CC2\_STATE to appropriate value.

#### 7.3.12 VBUS Power Source Requirements

The TUSB422 is a Source if MESSAGE\_HEADER\_INFO POWER\_ROLE = 1. As outlined in the USB TCPCi specification, the TUSB422 when operating as a source discharges VBUS under any of the following conditions when Auto Discharge (AUTO\_DISCHARGE\_DISCONNECT = 1) is enabled.

- Disconnect (Removal of Rd by port partner) is detected. The TUSB422 discharges VBUS to vSafe0V.

- Upon setting Force Discharge bit, the TUSB422 discharges VBUS to either vSafe0V or to the voltage specified by VBUS Stop Discharge register.

The TUSB422 does not automatically discharge VBUS upon reception of a Hard Reset.

#### 7.3.13 VBUS Power Sink Requirements.

The TUSB422 is a Sink if MESSAGE\_HEADER\_INFO POWER\_ROLE = 0. As outlined in the TCPC specification, the TUSB422 when operating as a sink must discharge VBUS to vSafe0V under any of the following conditions when Auto Discharge (AUTO DISCHARGE DISCONNECT = 1) is enabled.

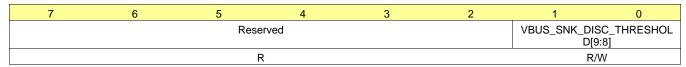

- If VBUS present detection is enabled and VBUS Sink Disconnect Threshold register is zero and VBUS present bit in the Power Status register transitions from a 1 to 0.

- VBUS crosses the threshold programmed in the VBUS Sink Disconnect Threshold register.

#### 7.3.14 VCONN

VCONN is required by active cables, emarker, and VCONN powered accessories like Alt Mode adapters. These types of devices or cables present Ra on one CC pin and Rd on the other CC pin. VCONN must be enabled when any of device or cable requiring VCONN is connected to a Type-C port and the TUSB422 is operating as a DFP or DFP in DRP mode. Software can also enable the VCONN switch when the TUSB422 is a UFP during a VCONN\_SWAP sequence. The TUSB422 implements a VCONN switch which is controlled by software. The default state of this switch is open. By setting the ENABLE\_VCONN bit in *Power Control* register, the TUSB422 removes closes the switch resulting in VCONN power to be connected to the CC pin indicated by value of PLUG\_ORIENTATION bit in *TCPC Control* register.

Once the VCONN switch is closed, the switch can be opened by any of the following conditions.

- Software clear ENABLE\_VCONN bit in Power Control register.

- VCONN overcurrent fault condition occurs resulting in TUSB422 opening VCONN switch and setting the VCONN\_OCP\_FAULT\_STATUS bit in Fault Status register.

- Over temperature condition detected by TUSB422. Must be enabled in OTSD Control register.

- · Hard Reset ordered set is received.

- Cable is removed (Rd no longer present) results in TUSB422 opening VCONN switch and discharging VCONN to vSafe0V

The TUSB422 discharges VCONN to vSafe0V by enabling Rd at designated CC pin anytime the VCONN switch transitions from closed to open state. Once at vSafe0V, the TUSB422 disables the discharge circuit by removing Rd and then re-enable Rp (assuming it is still enabled in *Role Control* register).

If an external VCONN discharge is desired, the TUSB422 internal VCONN discharge circuit can be disabled by setting the INT\_VCONNDIS\_DISABLE bit in the *VBUS and VCONN Control* register.

Before closing the VCONN switch, the TCPM must make sure the voltage on VCONN pin is at a valid level. When opening the VCONN switch by clearing the ENABLE\_VCONN bit, the TCPM software must make sure voltage on VCONN pin is at valid level until after VCONN switch is opened and then, if desired, can remove the voltage from the VCONN pin. Removing the voltage on VCONN pin before Vconn switch is opened will result in a false VCONN fault condition.

#### 7.3.15 Interrupts

The TUSB422 asserts the INT\_N pin low anytime an unmasked event occurs. Upon assertion of the interrupt, the TCPM should read the *Alert* Registers to determine the reason for interrupt. Upon reading the *Alert* register, the TCPM should clear the interrupt by writing a 1'b1 to the appropriate field in the Alert register.

If the FAULT flag is set in the *Alert* register, the TCPM must first read the *Fault Status* register to determine reason for fault. Then clear the appropriate field in the *Fault Status* register by writing a 1'b1. Once all fields in *Fault Status* register are cleared, the TCPM can then clear the flag in the *Alert* Register by writing a 1'b1.

The TUSB422 also has Vendor Defined Interrupt registers which is not part of the USB TCPC specification. These vendor defined interrupts are masked by default. Software can enable vendor interrupts by setting the appropriate bit in the Vendor Interrupts Mask Register and setting the VENDOR\_IRQ\_MASK field in the Alert Mask register.

#### 7.3.16 Fast Role Swap

The TUSB422 supports Fast Role Swap TX as defined in the USB Power Delivery 3.0 specification. The TUSB422 does not support Fast Role Swap RX function.

The TUSB422 can also transmit a FastRole swap pulse. This is done by writing a 1'b1 to the TX\_FAST\_ROLE\_SWAP bit in the PHY BMC TX Control register. Upon setting this bit, the TUSB422 generates a FastRole swap pulse as defined by  $T_{\text{FRSWAPTX}}$  parameter. The TUSB422 clears the TX\_FAST\_ROLE\_SWAP bit after it has completed the transmission.

#### 7.4 Device Functional Modes

#### 7.4.1 Unattached Mode

Unattached mode is the primary mode of operation for the TUSB422 since a USB port can be unattached for a lengthy period of time. In this mode, the TUSB422 may be configured as UFP (present Rd on both CC pins), DFP (present Rp on both CC pins), or DRP (alternate between Rp and Rd on both CC pins) operation and waiting for a connection. The TUSB422 remains in this mode until a connection is detected. Upon detection of a connection, the INT\_N pin will be asserted low.

In Unattached mode, VDD is available, and all IOs are operational. VCONN is disabled. USB PD BMC phy is disabled.

#### 7.4.2 Active Mode

The TUSB422 is in the Active mode when either CC1\_STATE field or CC2\_STATE field in the *CC Status* register are non-zero, the TCPM has completed the required Type-C debounce of CC pins, and the TCPM has set the AUTO\_DISCHARGE\_DISCONNECT in the *Power Control* register. In active mode, all IOs are operational, and VCONN is available for an active cable. The USB PD phy can be enabled in this mode by setting the *Receiver Detect Register* to a non-zero value. The USB PD BMC PHY functionality can only be used if the TUSB422 is in any of the following active states: Attached.SRC, Attached.SNK, DebugAccessory, or PoweredAccessory. Use of TUSB422 USB PD BMC PHY in any other active state is not permitted.

#### 7.4.3 Power Role Swap

Upon entering the active mode, the power provider and consumer is determined by whether or not TUSB422 is presenting a Rp or a Rd on CC pins. If TUSB422 is presenting a Rp, then TUSB422 is a power provider. If TUSB422 is presenting a Rd, then TUSB422 is a power consumer. Once in the active mode, it may become necessary change power role through performing a power role swap. Key requirements for performing a power role swap by the software are listed below. For additional details on power role swap, consult the USB PD specification.

Transition from power provider to power consumer:

- 1. TCPM state machine needs to transition from Attached.SRC to Attached.SNK.

- 2. Disable VBUS source. TCPM should send DisableSourceVbus command to TUSB422 Command register.

- 3. Once VBUS is at vSafe0V, disable AUTO\_DISCHARGE\_DISCONNECT in Power Control register and change *Role Control* register to present a Rd.

- 4. Upon reception of PS\_RDY message from port partner, update message header information and send PS\_RDY back to port partner.

- 5. Enable Sink VBUS and VBUS presence detection. TCPM should send SinkVbus and EnableVbusDetect commands to TUSB422 *Command* register.

Transition from power consumer to power provider:

- 1. Disable AUTO DISCHARGE DISCONNECT in the *Power Control* register

- 2. Disable VBUS presence detection. TCPM should send DisableVbusDetect command to TUSB422 *Command* register.

- Disable system sink VBUS. TCPM should also send DisableSinkVbus command to TUSB422 Command register.

- 4. TCPM state machine needs to transition from Attached.SNK to Attached.SRC.

- 5. Upon reception of PS\_RDY message from port partner, change *Role Control* register to present a Rp.

- 6. Enable system source VBUS. TCPM should send SourceVbusDefaultVoltage command to TUSB422 Command register.

- 7. Once VBUS is at vSafe5V, the TCPM should update message header information and then send PS\_RDY to its port partner.

- Upon successful completion of power-role swap, enable AUTO\_DISCHARGE\_DISCONNECT in the Power Control register

## Device Functional Modes (接下页)

注

During Power-role swap, the TUSB422 will disable its VCONN. Software workaround is to re-enable VCONN and issue error recovery for VCONN powered accessories. This may result in momentary loss of video/data.

#### 7.4.4 Debug Accessory

A Debug accessory is a device which presents Rd on both of TUSB422 CC pins or Rp on both of TUSB422 CC pins. The TUSB422 upon detecting either of these two conditions on its CC pins performs the required Type-C debounce. If either condition is still present at end of the debounce, the TUSB422 sets the DEBUG\_ACC\_CONNECTED bit in the Power Status Register.

The TCPM is required to determine cable orientation by reading the CC1\_STATE and CC2\_STATE in the CC Status register and writing the orientation to the PLUG\_ORIENTATION bit in the TCPC Control register.

#### 表 3. DebugAccessory Attached as a Sink

| CC1_STATE  | CC2_STATE  | TCPM Writes to PLUG_ORIENTATION bit |  |  |

|------------|------------|-------------------------------------|--|--|

| 2'b10 (Rd) | 2'b01 (Ra) | 1'b0. PD communication over CC1     |  |  |

| 2'b01 (Ra) | 2'b10 (Rd) | 1'b1. PD communication over CC2     |  |  |

#### 表 4. DebugAccessory Attached as a Source

| CC1_STATE                          | CC2_STATE                          | TCPM Writes to PLUG_ORIENTATION bit |

|------------------------------------|------------------------------------|-------------------------------------|

| Voltage is greater than CC2_STATE. | Voltage is less than CC1_STATE.    | 1'b0. PD communication over CC1     |

| Voltage is less than CC2_STATE     | Voltage is greater than CC1_STATE. | 1'b1. PD communication over CC2     |

#### 7.4.5 Dead Battery Mode

Low battery power could cause conditions in which communication over USB Type-C can no longer be maintained. When this situation occurs, it is critical to transition to attached. SNK state so that power from VBUS can be used to charge the battery back to an operational level. This condition is known as Dead Battery Mode. The TUSB422 supports dead-battery mode by presenting Rd to both CC pins when VDD is no longer active.

In the dead-battery mode access to TUSB422 registers is not available. Upon exiting dead-battery mode, the TUSB422 enters mode dictated by the value of *Role Control* register.

注

When exiting dead battery mode, the TUSB422's Rd is momentarily removed for about 100 µs during power up. This should not cause an issue in system since USB-C standard requires 100 ms debounce on CC pins.

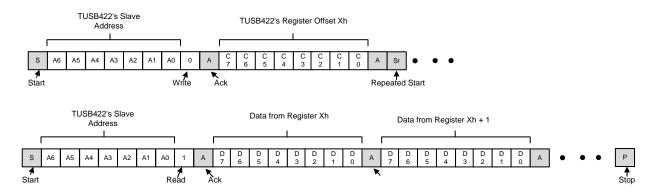

### 7.5 Programming

The TUSB422 is controlled using I2C. The TUSB422 local I2C interface is available for reading/writing after  $T_{INT\_N\_LOW}$  after the device is powered up. The SCL and SDA terminals are used for I2C clock and I2C data respectively.

图 5. TUSB422 I2C Addresses

| 7 (MSB) | 6 | 5 | 4 | 3 | 2 | 1 | 0 (W/R) |

|---------|---|---|---|---|---|---|---------|

| 0       | 1 | 0 | 0 | 0 | 0 | 0 | 0/1     |

图 6. I2C Write With Data

The following procedure should be followed to write data to TUSB422 I<sup>2</sup>C registers (refer to 图 6):

- 1. The master initiates a write operation by generating a start condition (S), followed by the TUSB422 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The TUSB422 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within TUSB422) to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB422 acknowledges the sub-address cycle.

- 5. The master presents the first byte of data to be written to the I<sup>2</sup>C register.

- 6. The TUSB422 acknowledges the byte transfer

- 7. The master may continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the TUSB422.

- 8. The master terminates the write operation by generating a stop condition (P).

图 7. I2C Read Without Repeated Start

The following procedure should be followed to read the TUSB422 I<sup>2</sup>C registers without a repeated Start (refer **2** 7).

- 1. The master initiates a read operation by generating a start condition (S), followed by the TUSB422 7-bit address and a zero-value "W/R" bit to indicate a read cycle.

- 2. The TUSB422 acknowledges the 7-bit address cycle.

- 3. Following the acknowledge the master continues sending clock.

- 4. The TUSB422 transmit the contents of the memory registers MSB-first starting at register 00h or last read sub-address+1. If a write to the I<sup>2</sup>C register occurred prior to the read, then the TUSB422 shall start at the sub-address specified in the write.

- 5. The TUSB422 waits for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I<sup>2</sup>C master acknowledges reception of each data byte transfer.

- 6. If an ACK is received, the TUSB422 transmits the next byte of data as long as master provides the clock. If a NAK is received, the TUSB422 stops providing data and waits for a stop condition (P).

- 7. The master terminates the write operation by generating a stop condition (P).

图 8. I2C Read With Repeated Start

The following procedure should be followed to read the TUSB422 I<sup>2</sup>C registers with a repeated Start (refer 88).

- 1. The master initiates a read operation by generating a start condition (S), followed by the TUSB422 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The TUSB422 acknowledges the 7-bit address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within TUSB422) to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB422 acknowledges the sub-address cycle.

- 5. The master presents a repeated start condition (Sr).

- 6. The master initiates a read operation by generating a start condition (S), followed by the TUSB422 7-bit address and a one-value "W/R" bit to indicate a read cycle.

- 7. The TUSB422 acknowledges the 7-bit address cycle.

- 8. The TUSB422 transmit the contents of the memory registers MSB-first starting at the sub-address.

- 9. The TUSB422 shall wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I<sup>2</sup>C master acknowledges reception of each data byte transfer.

- 10. If an ACK is received, the TUSB422 transmits the next byte of data as long as master provides the clock. If a NAK is received, the TUSB422 stops providing data and waits for a stop condition (P).

- 11. The master terminates the read operation by generating a stop condition (P).

图 9. I2C Write Without Data

The following procedure should be followed for setting a starting sub-address for I<sup>2</sup>C reads (refer to 图 8).

- 1. The master initiates a write operation by generating a start condition (S), followed by the TUSB422 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The TUSB422 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within TUSB422) to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB422 acknowledges the sub-address cycle.

- 5. The master terminates the write operation by generating a stop condition (P).

After initial power-up, if no sub-addressing is included for the read procedure (refer to 🛭 8), then reads start at register offset 00h and continue byte by byte through the registers until the I<sup>2</sup>C master terminates the read operation. During a read operation, the TUSB422 auto-increments the I<sup>2</sup>C internal register address of the last byte transferred independent of whether or not an ACK was received from the I2C master.

# 7.6 Register Maps

# 表 5. Register Maps

|           |                              | 5. Kegister Wi | •                                                                          |

|-----------|------------------------------|----------------|----------------------------------------------------------------------------|

| ADDRESS   | REGISTER NAME                | RESET          | DEFINITION                                                                 |

| 0x00      | VENDOR_ID_BYTE_0             | 0x51           |                                                                            |

| 0x01      | VENDOR_ID_BYTE_1             | 0x04           |                                                                            |

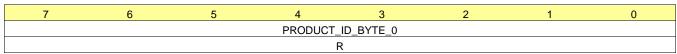

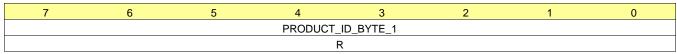

| 0x02      | PRODUCT_ID_BYTE_0            | 0x22           |                                                                            |

| 0x03      | PRODUCT_ID_BYTE_1            | 0x04           |                                                                            |

| 0x04      | DEVICE_ID_BYTE_0             | 0x00           |                                                                            |

| 0x05      | DEVICE_ID_BYTE_1             | 0x01           |                                                                            |

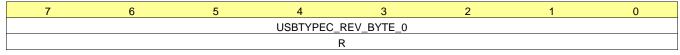

| 0x06      | USBTYPEC_REV_BYTE_0          | 0x11           |                                                                            |

| 0x07      | USBTYPEC_REV_BYTE_1          | 0x00           |                                                                            |

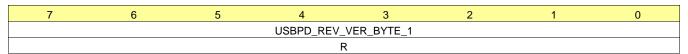

| 80x0      | USBPD_REV_VER_BYTE_0         | 0x11           |                                                                            |

| 0x09      | USBPD_REV_VER_BYTE_1         | 0x20           |                                                                            |

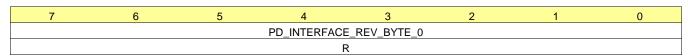

| 0x0A      | PD_INTERFACE_REV_BYTE_0      | 0x10           |                                                                            |

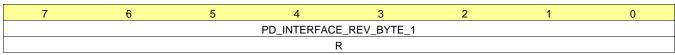

| 0x0B      | PD_INTERFACE_REV_BYTE_1      | 0x10           |                                                                            |

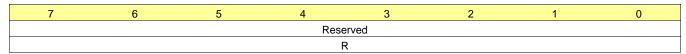

| 0x0C 0x0F | Reserved                     | 0x00           | Reserved                                                                   |

| 0x10      | ALERT_BYTE_0                 | 0x00           |                                                                            |

| 0x11      | ALERT_BYTE_1                 | 0x00           |                                                                            |

| 0x12      | ALERT_MASK_BYTE_0            | 0xFFh          |                                                                            |

| 0x13      | ALERT_MASK_BYTE_1            | 0x0F           |                                                                            |

| 0x14      | POWER_STATUS_MASK            | 0xFF           |                                                                            |

| 0x15      | FAULT_STATUS_MASK            | 0x7F           |                                                                            |

| 0x16 0x17 | Reserved                     | 0x00           | Reserved                                                                   |

| 0x18      | CONFIG_STARDARD_OUTPUT       | 0x60           |                                                                            |

| 0x19      | TCPC_CONTROL                 | 0x00           |                                                                            |

| 0x1A      | ROLE_CONTROL                 | 0x0A           |                                                                            |

| 0x1B      | FAULT_CONTROL                | 0x06           |                                                                            |

| 0x1C      | POWER_CONTROL                | 0x60           |                                                                            |

| 0x1D      | CC_STATUS                    | 0x00           |                                                                            |

| 0x1E      | POWER_STATUS                 | 0x00           |                                                                            |

| 0x1F      | FAULT_STATUS                 | 0x00           |                                                                            |

| 0x20 0x22 | Reserved                     | 0x00           | Reserved                                                                   |

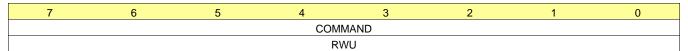

| 0x23      | COMMAND                      | 0x00           |                                                                            |

| 0x24      | DEVICE_CAPABILITIES_1_BYTE_0 | 0x98           |                                                                            |

| 0x25      | DEVICE_CAPABILITIES_1_BYTE_1 | 0x1E           |                                                                            |

| 0x26      | DEVICE_CAPABILITIES_2_BYTE_0 | 0xC5           |                                                                            |

| 0x27      | DEVICE_CAPABILITIES_2_BYTE_1 | 0x00           |                                                                            |

| 0x28      | STANDARD_INPUT_CAPABILITIES  | 0x00           |                                                                            |

| 0x29      | STANDARD_OUTPUT_CAPABILITIES | 0x00           |                                                                            |

| 0x2A 0x2D | Reserved                     | 0x00           | Reserved                                                                   |

| 0x2E      | MESSAGE_HEADER_INFO          | 0x02           |                                                                            |

| 0x2F      | RECEIVE_DETECT               | 0x00           |                                                                            |

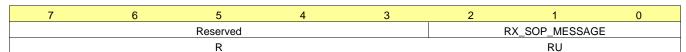

| 0x30      | RECEIVE_BYTE_COUNT           | 0x00           | Number of Bytes in the RECEIVE_BUFFER that are not stale.                  |

| 0x31      | RX_BUF_FRAME_TYPE            | 0x00           | Type of received frame (with a reference to a description of the register) |

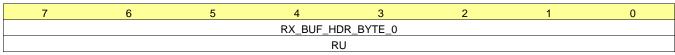

| 0x32      | RX_BUF_HEADER_BYTE_0         | 0x00           | Byte 0 (bits 70) of RX message header                                      |

| 0x33      | RX_BUF_HEADER_BYTE_1         | 0x00           | Byte 1 (bits 158) of RX message header                                     |

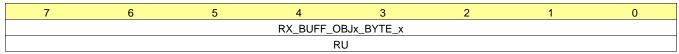

| 0x34      | RX_BUF_OBJ1_BYTE_0           | 0x00           | RX Byte 0 (bits 70) of 1st data object                                     |

# Register Maps (接下页)

表 5. Register Maps (接下页)

| ADDRESS | REGISTER NAME        | RESET | DEFINITION                               |

|---------|----------------------|-------|------------------------------------------|

| 0x35    | RX_BUF_OBJ1_BYTE_1   | 0x00  | RX Byte 1 (bits 158) of 1st data object  |

| 0x36    | RX_BUF_OBJ1_BYTE_2   | 0x00  | RX Byte 2 (bits 2316) of 1st data object |

| 0x37    | RX_BUF_OBJ1_BYTE_3   | 0x00  | RX Byte 3 (bits 3124) of 1st data object |

| 0x38    | RX_BUF_OBJ2_BYTE_0   | 0x00  | RX Byte 0 (bits 70) of 2nd data object   |

| 0x39    | RX_BUF_OBJ2_BYTE_1   | 0x00  | RX Byte 1 (bits 158) of 2nd data object  |

| 0x3A    | RX_BUF_OBJ2_BYTE_2   | 0x00  | RX Byte 2 (bits 2316) of 2nd data object |

| 0x3B    | RX_BUF_OBJ2_BYTE_3   | 0x00  | RX Byte 3 (bits 3124) of 2nd data object |

| 0x3C    | RX_BUF_OBJ3_BYTE_0   | 0x00  | RX Byte 0 (bits 70) of 3rd data object   |

| 0x3D    | RX_BUF_OBJ3_BYTE_1   | 0x00  | RX Byte 1 (bits 158) of 3rd data object  |