TPSM831D31

ZHCSIO9A - AUGUST 2018 - REVISED JUNE 2021

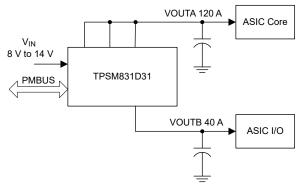

# TPSM831D31 8V 至 14V 输入、0.25V 至 1.52V 双路输出、 120A + 40A PMBus™ 电源模块

# 1 特性

输入电压范围: 8V 至 14V

• 双路输出:120A(三相)+40A(一相)

• 输出电压范围: 0.25 V 至 1.52 V

- 可编程 (阶跃为 5mV)

- 差分遥感

- ±0.5% Vref 精度, 具有遥感功能

• PMBus 接口

- 可编程 VouT、UVLO、故障限制

- VIN、VOUT、IOUT、温度遥测

支持高达 1MHz 的总线速度

- 片上非易失性配置存储器

超快瞬态响应

开关频率范围: 350 kHz 至 700 kHz

• 15mm × 48mm 封装尺寸和 12mm 高度

效率高达 95%

• 双电源正常状态指示输出

过流、过压、过热保护

IC 工作结温范围: - 40°C 至 125°C

工作环境温度范围: - 40°C 至 105°C

#### 2 应用

具有双电源轨的高性能处理器/ASIC

网络处理器电源(Broadcom<sup>®</sup>、Cavium<sup>®</sup>、 Marvell®、NXP®)

- 高电流 FPGA 电源 (Intel®、Xilinx®)

- 高性能 ARM 处理器电源

# 3 说明

TPSM831D31 是一款 PMBus™ 控制型双输出四相电 源模块,该电源模块将一个具有四个高效智能功率级的 高性能 D-CAP+™ 控制器组合在一个坚固耐用的热增强 型表面贴装封装中。用户提供输入和输出电容器以及一 些无源组件即可完成系统。第一个输出是能够提供高达 120A 连续输出电流的三相功率级。第二个输出是能够 提供高达 40A 输出电流的单相功率级。

PMBus 接口提供每个输出电压、UVLO、软启动、过 流和热关断参数的转换器配置。该接口具有遥测支持功 能,可报告实际输入电压、输出电压、输出电流和器件 温度。该器件可报告输入和输出功率。该器件支持标准 PMBus 警告 和故障 功能。该器件支持高达 1MHz 的 PMBus 通信速度, 具有 1.8V 或 3.3V 逻辑电平, 详见 SMBus 规范 V3.0 第 4.3 节。该模块器件支持 PMBus 1.3 规范中的一部分命令。

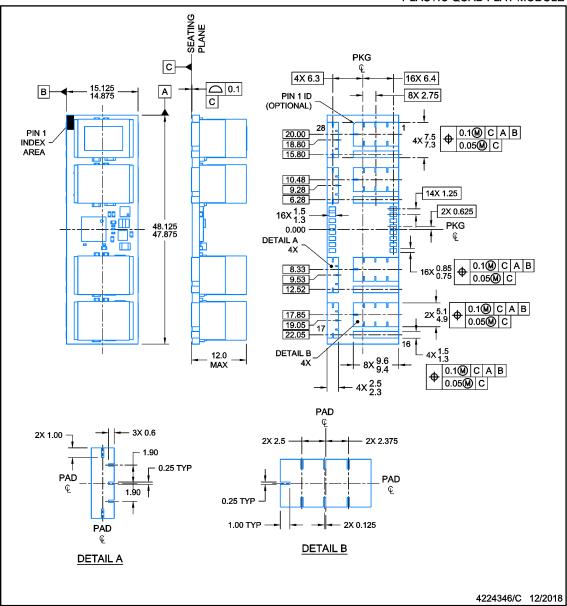

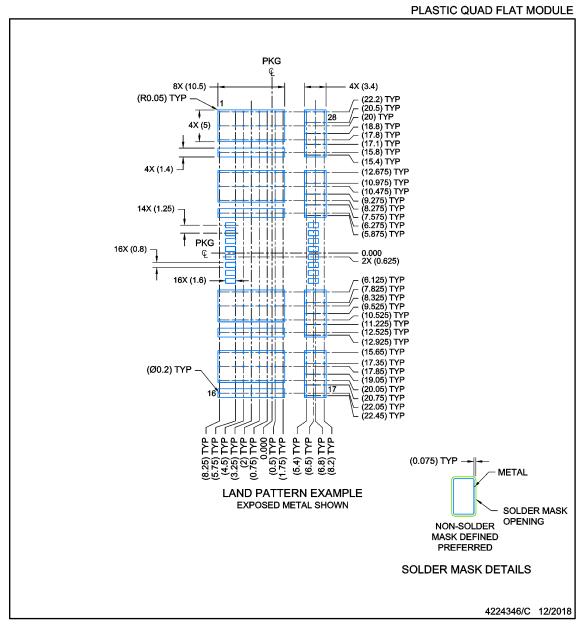

# 器件信息

| 器件型号       | 封装 <sup>(1)</sup> | 封装尺寸 ( 标称值 )      |

|------------|-------------------|-------------------|

| TPSM831D31 | QFM (28)          | 48.00mm × 15.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

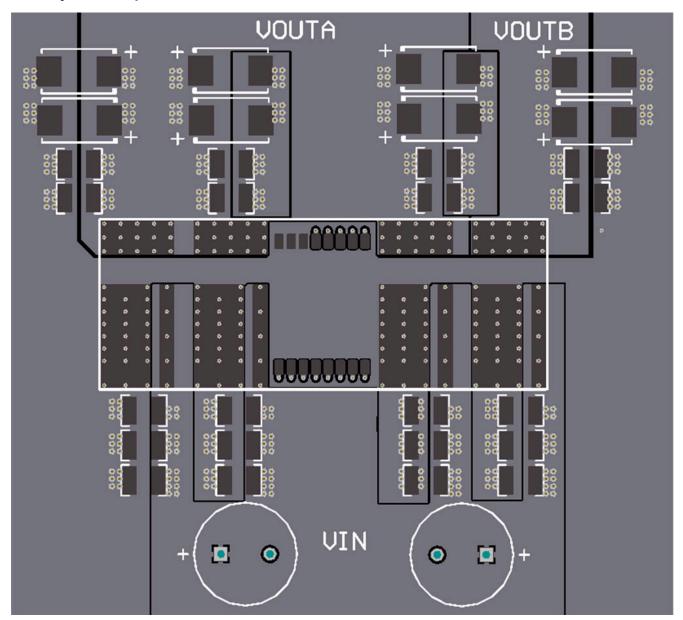

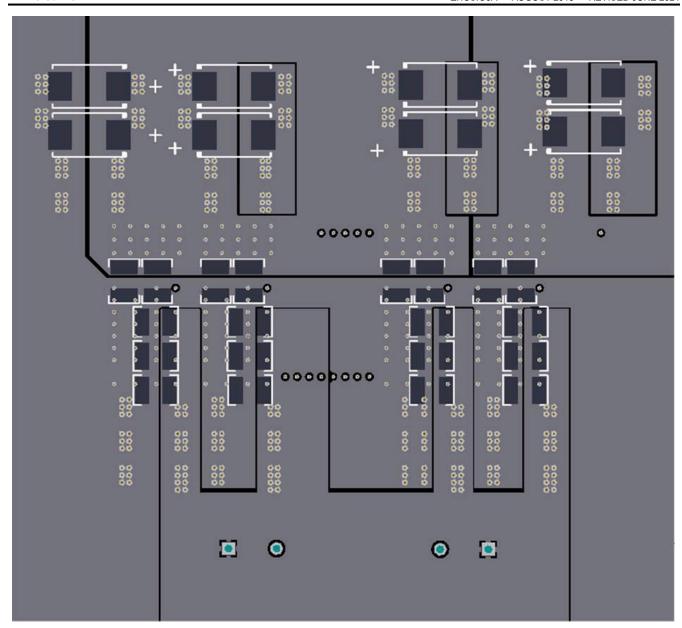

简化版应用

# **Table of Contents**

| 1 特性1                                                   | 7.2 Functional Block Diagram            | 12 |

|---------------------------------------------------------|-----------------------------------------|----|

| 2 应用                                                    | 7.3 Feature Description                 | 13 |

|                                                         | 7.4 Device Functional Modes             | 17 |

| 4 Revision History2                                     | 7.5 Programming                         | 17 |

| 5 Pin Configuration and Functions3                      | 8 Application and Implementation        | 72 |

| 6 Specifications5                                       | 8.1 Application Information             | 72 |

| 6.1 Absolute Maximum Ratings5                           | 8.2 Typical Application                 | 72 |

| 6.2 ESD Ratings5                                        | 9 Power Supply Recommendations          | 78 |

| 6.3 Recommended Operating Conditions5                   | 10 Layout                               | 78 |

| 6.4 Thermal Information6                                | 10.1 Layout Guidelines                  | 78 |

| 6.5 Electrical Characteristics6                         | 10.2 Layout Examples                    |    |

| 6.6 References: DAC8                                    | 11 Device and Documentation Support     | 80 |

| 6.7 Telemetry 8                                         | 11.1 接收文档更新通知                           | 80 |

| 6.8 Current Sense and Calibration8                      | 11.2 支持资源                               |    |

| 6.9 Logic Interface Pins: A_EN, A_PGOOD, B_EN,          | 11.3 Trademarks                         | 80 |

| B PGOOD,RESET9                                          | 11.4 静电放电警告                             | 80 |

| 6.10 Protections: OVP and UVP9                          | 11.5 术语表                                |    |

| 6.11 Typical Characteristics (V <sub>IN</sub> = 12 V)10 | 12 Mechanical, Packaging, and Orderable |    |

| 7 Detailed Description12                                | Information                             | 81 |

| 7.1 Overview12                                          |                                         |    |

|                                                         |                                         |    |

# **4 Revision History**

| CI | hanges from Revision * (August 2018) to Revision A (June 2021) | Page |

|----|----------------------------------------------------------------|------|

| •  | 将数据表状态从 <i>预告信息</i> 更改为 <i>量产数据</i>                            | 1    |

| •  | 更新了整个文档中的表格、图和交叉参考的编号格式                                        | 1    |

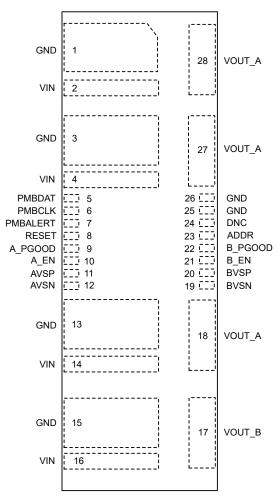

# **5 Pin Configuration and Functions**

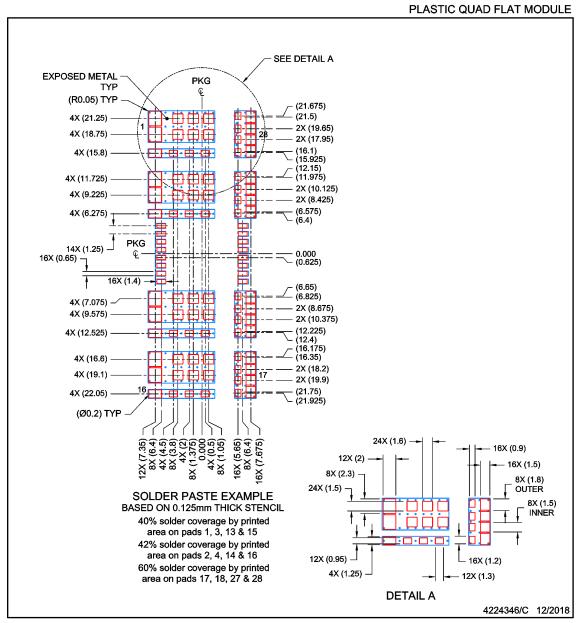

图 5-1. MOA Package, 28-Pin QFM (Top View)

表 5-1. Pin Functions

| PIN       | PIN I/O <sup>(1)</sup> |                                                                                                                                                                | DESCRIPTION                                                                                                                                                    |

|-----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO   |                        | 1/0(-/                                                                                                                                                         | DESCRIPTION                                                                                                                                                    |

| ADDR      | 23                     | I                                                                                                                                                              | Connect a resistor from this pin to GND to set the desired PMBus address. Do not leave this pin floating. See PMBus ADDRESS section.                           |

| A_EN 10   |                        | I                                                                                                                                                              | Active high enable input for VOUT_A. Asserting this pin high enables power conversion on the VOUT_A channel.                                                   |

| A_PGOOD 9 |                        | 0                                                                                                                                                              | Open drain Power Good signal of the VOUT_A channel. This pin requires a pullup resistor. This pin is pulled low when a shutdown fault occurs.                  |

| AVSN      | 12                     | Negative input of the remote voltage sense of channel A. Connect this pin to ground at the VOUT_A load for best voltage regulation. Do not let this pin float. |                                                                                                                                                                |

| AVSP      | 11                     | I                                                                                                                                                              | Positive input of the remote voltage sense of channel A. Connect this pin to VOUT_A at the load for best voltage regulation. Do not let this pin float.        |

| B_EN      | 21                     | I                                                                                                                                                              | Active high enable input for VOUT_B. Asserting this pin high enables power conversion on the VOUT_B channel.                                                   |

| B_PGOOD   | 22                     | 0                                                                                                                                                              | Open drain Power Good signal of the VOUT_B channel. This pin requires a pullup resistor. This pin is pulled low when a shutdown fault occurs.                  |

| BVSN      | 19                     | I                                                                                                                                                              | Negative input of the remote voltage sense of channel B. Connect this pin to ground at the VOUT_B load for best voltage regulation. Do not let this pin float. |

# 表 5-1. Pin Functions (continued)

| PIN      |     | uo(1)              | DECORPTION                                                                                                                                                                                   |  |  |

|----------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                  |  |  |

| BVSP     | 20  | I                  | Positive input of the remote voltage sense of channel B. Connect this pin to VOUT_A at the load for best voltage regulation. Do not let this pin float.                                      |  |  |

| DNC      | 24  | _                  | Do not connect. This pin is connected to internal circuitry. Do not connect this pin to other signal or voltage source. Connecting the pin to GND is recommended.                            |  |  |

|          | 1   |                    |                                                                                                                                                                                              |  |  |

|          | 3   |                    |                                                                                                                                                                                              |  |  |

| GND      | 13  | G                  | Power ground of the device. Connect pins 1, 3, 13, and 15 to the bypass caps associated with VIN. Connect pads 1, 3, 13, 15 to the PCB ground planes using multiple vias for optimal thermal |  |  |

| GND      | 15  | G                  | performance.                                                                                                                                                                                 |  |  |

|          | 25  |                    |                                                                                                                                                                                              |  |  |

|          | 26  |                    |                                                                                                                                                                                              |  |  |

| PMBCLK   | 6   | I                  | PMBus serial clock interface. (Open Drain)                                                                                                                                                   |  |  |

| PMBDAT   | 5   | I/O                | PMBus bi-directional serial data interface. (Open Drain)                                                                                                                                     |  |  |

| PMBALERT | 7   | I/O                | PMBus bi-directional ALERT pin interface. (Open Drain)                                                                                                                                       |  |  |

| RESET    | 8   | I                  | Active low RESET input that resets the output voltage to its programmed BOOT voltage. This pin requires a pullup resistor.                                                                   |  |  |

|          | 2   |                    |                                                                                                                                                                                              |  |  |

| \ /\h.   | 4   |                    | Input voltage. These pins provide voltage to the power conversion stages of the module.                                                                                                      |  |  |

| VIN      | 14  | ı                  | Connect these pins to the PCB VIN planes using multiple vias for optimal thermal performance.                                                                                                |  |  |

|          | 16  |                    |                                                                                                                                                                                              |  |  |

|          | 18  |                    |                                                                                                                                                                                              |  |  |

| VOUT_A   | 27  | 0                  | Output voltage of channel A. Connect these pins to the output A load. Connect external bypass capacitors between these pins and GND pins 1, 3, and 13.                                       |  |  |

|          | 28  |                    | oupasitors between those pine and OND pine 1, 0, and 10.                                                                                                                                     |  |  |

| VOUT_B   | 17  | 0                  | Output voltage of channel B. Connect this pin to the output B load. Connect external bypass capacitors between this pin and GND pin 15.                                                      |  |  |

<sup>(1)</sup> G = ground, I = input, O = output

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                        | MIN   | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------|-------|-----|------|

|                                       | VIN                                                    | - 0.3 | 19  | V    |

| Input voltage <sup>(2)</sup>          | ADDR, AVSP, BVSP, RESET, PMBCLK, PMBDAT                | - 0.3 | 3.6 | V    |

|                                       | AGND, AVSN, BVSN                                       | - 0.3 | 0.3 | V    |

| Output voltage <sup>(1)</sup> (2)     | VOUT_A, VOUT_B, A_PGOOD, B_PGOOD, PMBALERT             | - 0.3 | 3.6 | V    |

| Mechanical shock                      | Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted |       | 500 | G    |

| Mechanical vibration                  | Mil-STD-883D, Method 2007.2, 20 to 2000 Hz             |       | 10  | G    |

| Operating junction temperatu          | ire, T <sub>J</sub>                                    | - 40  | 150 | °C   |

| Storage temperature, T <sub>STG</sub> |                                                        | - 55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                          |                                                                                | VALUE | UNIT |

|--------------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2500 | V    |

| V <sub>(ESD)</sub> | Liectiostatic discriarge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                 |                                 | MIN  | NOM  | MAX                                                 | UNIT |

|-------------------------------------------------|---------------------------------|------|------|-----------------------------------------------------|------|

| VIN                                             |                                 | 8    | 12   | 14                                                  | V    |

| VOUT_A, VOUT_B, AVSP, BVSP                      |                                 | 0.25 |      | 1.52                                                | V    |

| IOUTA                                           |                                 | 0    |      | 120                                                 | Α    |

| IOUTB                                           |                                 | 0    |      | 40                                                  | Α    |

| PMBCLK, PMBDAT, RESET pullup, A_PGOOD pullup, I | B_PGOOD pullup, PMBALERT pullup |      | 3.3  | 3.5                                                 | V    |

| Switching frequency                             |                                 | 350  | 400  | 700                                                 | kHz  |

| Operating junction temperature, T <sub>J</sub>  |                                 | - 40 |      | 125                                                 | °C   |

| Operating ambient temperature, T <sub>A</sub>   |                                 | - 40 |      | 105                                                 | °C   |

| External input capacitance, C <sub>IN</sub>     | Ceramic                         |      | 500  |                                                     | μF   |

| External input capacitance, C <sub>IN</sub>     | Non-ceramic                     |      | 1000 |                                                     | μF   |

| External output conscitance C                   | Ceramic                         | 600  | 1200 |                                                     | μF   |

| External output capacitance, C <sub>OUT_A</sub> | Non-ceramic                     | 2750 | 5500 |                                                     | μF   |

| External output conscitance C                   | Ceramic                         | 200  | 400  | 14<br>1.52<br>120<br>40<br>3.5<br>700<br>125<br>105 | μF   |

| External output capacitance, C <sub>OUT_B</sub> | Non-ceramic                     | 900  | 1800 |                                                     | μF   |

<sup>(2)</sup> All voltage values are with respect to the network ground terminal GND unless otherwise noted.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **6.4 Thermal Information**

|                   |                                                                                                                                                                |                    | TPSM831D31 |      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|------|

|                   | THERMAL METRIC <sup>(4)</sup>                                                                                                                                  |                    | MOA (QFN)  | UNIT |

|                   |                                                                                                                                                                |                    | 28 PINS    |      |

|                   |                                                                                                                                                                | Natural Convection | 5.5        | °C/W |

| R <sub>0</sub> JA | Junction-to-ambient thermal resistance (1)                                                                                                                     | 200 LFM            | 3.4        | °C/W |

|                   |                                                                                                                                                                | 400 LFM            | 2.8        | °C/W |

| ψJT               | Junction-to-top characterization parameter (2)                                                                                                                 |                    | 0.3        | °C/W |

| ψ ЈВ              | Junction-to-ambient thermal resistance (1)  200 LFM  400 LFM  Junction-to-top characterization parameter (2)  Junction-to-board characterization parameter (3) |                    | 1.6        | °C/W |

| T <sub>SD</sub>   | Thermal shutdown temperature (default setting)                                                                                                                 |                    | 135        | °C   |

- (1) The junction-to-ambient thermal resistance applies to devices soldered directly to a 100 mm x 150 mm, 8-layer PCB with 2 oz. copper.

- (2) The junction-to-top board characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (section 6 and 7). T<sub>J</sub> = ψ<sub>JT</sub> × Pdis + T<sub>T</sub>; where Pdis is the power dissipated in the device and T<sub>T</sub> is the temperature of the top of the inductor.

- (3) The junction-to-board characterization parameter, Ψ<sub>JB</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7). T<sub>J</sub> = Ψ<sub>JB</sub> × Pdis + T<sub>B</sub>; where Pdis is the power dissipated in the device and T<sub>B</sub> is the temperature of the board 1 mm from the device.

- (4) For more information about thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report .

#### **6.5 Electrical Characteristics**

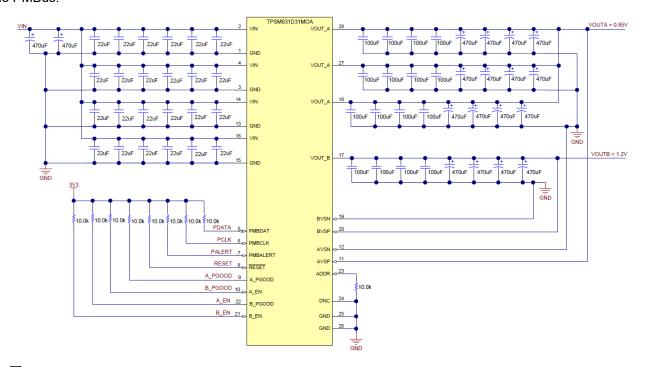

$T_A = -40^{\circ}\text{C}$  to +105°C,  $V_{IN} = 12 \text{ V}$ ,  $V_{OUTA} = V_{AVSP} = 1 \text{ V}$ ,  $V_{OUTB} = V_{BVSP} = 1 \text{ V}$ ,  $V_{AVSN} = V_{BVSN} = 00$ ,  $I_{OUTA} = I_{OUTB} = 0 \text{ A}$ ,  $F_{SW} = 400 \text{ kHz}$ ,  $C_{IN1} = 24 \times 22 \text{-}\mu\text{F}$ , 25-V, 1210 ceramic,  $C_{IN2} = 2 \times 470 \mu\text{F}$ , electrolytic bulk,  $C_{OUTA1} = 12 \times 100 \mu\text{F}$ , 6.3-V, 1210 ceramic,  $C_{OUTB2} = 12 \times 470 \mu\text{F}$ , 6.3-V polymer bulk. Minimum and maximum limits are specified through production test or design of the module/internal controller. Typical values represent the most likely parametric norm and are provided for reference only (unless otherwise noted).

|                       | PARAMETER                            | TEST CONDITIONS                                                                                          | MIN      | TYP  | MAX   | UNIT |

|-----------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|----------|------|-------|------|

| INPUT VOLTA           | AGE                                  |                                                                                                          | <u>'</u> |      |       |      |

| V <sub>IN</sub>       | Input voltage range                  |                                                                                                          | 8        |      | 14    | V    |

| UVLO                  | V <sub>IN</sub> undervoltage lockout | V <sub>IN</sub> increasing (default setting)                                                             |          | 7.25 |       | V    |

| UVLO                  | VIN undervoltage lockout             | V <sub>IN</sub> decreasing (default setting)                                                             |          | 6.5  |       | V    |

| I <sub>IN(STBY)</sub> | Input standby current                | A_EN = B_EN = GND                                                                                        |          | 8    |       | mA   |

| OUTPUT VOI            | TAGE                                 |                                                                                                          |          |      |       |      |

|                       | Boot voltage                         | 5-mV DAC (default setting)                                                                               | 0.492    | 0.5  | 0.508 | V    |

|                       | Programmable range                   | 5-mV DAC                                                                                                 | 0.25     |      | 1.52  | V    |

|                       | Programmable step size               | 5-mV DAC                                                                                                 |          | 5    |       | mV   |

| $V_{OUT\_A}$          | Set-point voltage tolerance          | 5-mV DAC, 0.8 V $\leq$ V <sub>OUT</sub> $\leq$ 1 V                                                       | - 0.5%   |      | 0.5%  |      |

|                       | Line regulation                      | 8 V $\leq$ V <sub>IN</sub> $\leq$ 14 V, I <sub>OUT</sub> = 0 A                                           |          | 0.1% |       |      |

|                       | Load regulation                      | 0 A ≤ I <sub>OUT</sub> ≤ 120 A                                                                           |          | 0.1% |       |      |

|                       | Output voltage ripple                | 20-MHz bandwidth, I <sub>OUT</sub> = 90 A                                                                |          | 10   |       | mV   |

|                       | Boot voltage                         | 5-mV DAC (default setting)                                                                               | 0.492    | 0.5  | 0.508 | V    |

|                       | Programmable range                   | 5-mV DAC                                                                                                 | 0.25     |      | 1.52  | V    |

|                       | Programmable step size               | 5-mV DAC                                                                                                 |          | 5    |       | mV   |

| V <sub>OUT_</sub> A   | Set-point voltage tolerance          | 5-mV DAC, 0.8 V $\leq$ V <sub>OUT</sub> $\leq$ 1 V                                                       | - 0.5%   |      | 0.5%  |      |

|                       | Line regulation                      | $8 \text{ V} \leqslant \text{V}_{\text{IN}} \leqslant 14 \text{ V}, \text{I}_{\text{OUT}} = 0 \text{ A}$ |          | 0.1% |       |      |

|                       | Load regulation                      | 0 A ≤ I <sub>OUT</sub> ≤ 120 A                                                                           |          | 0.1% |       |      |

|                       | Output voltage ripple                | 20-MHz bandwidth, I <sub>OUT</sub> = 30 A                                                                |          | 20   |       | mV   |

www.ti.com.cn

$T_A = -40^{\circ}\text{C to } + 105^{\circ}\text{C}, \ V_{\text{IN}} = 12 \ \text{V}, \ V_{\text{OUTA}} = V_{\text{AVSP}} = 1 \ \text{V}, \ V_{\text{OUTB}} = V_{\text{BVSP}} = 1 \ \text{V}, \ V_{\text{AVSN}} = V_{\text{BVSN}} = 0 \ \text{V}, \ I_{\text{OUTA}} = I_{\text{OUTB}} = 0 \ \text{A}, \ F_{\text{SW}} = 400 \ \text{kHz}, \ C_{\text{IN}1} = 24 \times 22 \text{-}\mu\text{F}, \ 25 \text{-V}, \ 1210 \ \text{ceramic}, \ C_{\text{IN}2} = 2 \times 470 \ \mu\text{F}, \ \text{electrolytic bulk}, \ C_{\text{OUTA}1} = 12 \times 100 \ \mu\text{F}, \ \text{6.3 \text{-V}}, \ 1210 \ \text{ceramic}, \ C_{\text{OUTB}2} = 4 \times 470 \ \mu\text{F}, \ \text{6.3 \text{-V}}, \ 1210 \ \text{ceramic}, \ C_{\text{OUTB}2} = 4 \times 470 \ \mu\text{F}, \ \text{6.3 \text{-V}}, \ \text{polymer bulk}.$  Minimum and maximum limits are specified through production test or design of the module/internal controller. Typical values represent the most likely parametric norm and are provided for reference only (unless otherwise noted).

|                                                  | PARAMETER                                             | TEST CONDITIONS                                                                    | MIN  | TYP                  | MAX  | UNIT  |

|--------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|------|----------------------|------|-------|

| OUTPUT CUR                                       | RENT                                                  |                                                                                    |      |                      |      |       |

|                                                  | Output current                                        | Natural convection <sup>(2)</sup>                                                  | 0    |                      | 120  | Α     |

|                                                  | Overcurrent fault threshold                           | Factory default setting (150% of I <sub>OUT</sub> max)                             |      | 180                  |      | Α     |

| I <sub>OUT_A</sub>                               | Per phase OCL level                                   | (default setting)                                                                  |      | 54                   |      | Α     |

|                                                  | Overcurrent warning threshold                         | Factory default setting (100% of I <sub>OUT</sub> max)                             |      | 120                  |      | Α     |

|                                                  | Output current                                        | Natural convection <sup>(2)</sup>                                                  | 0    |                      | 40   | Α     |

| I <sub>OUT_B</sub>                               | Overcurrent fault threshold                           | Factory default setting (150% of I <sub>OUT</sub> max)                             |      | 60                   |      | Α     |

| OUT_B                                            | Per Phase OCL level                                   | (default setting)                                                                  |      | 54                   |      | Α     |

| PERFORMANO TIMING  tstartupa  tstartupb  tvccvid | Overcurrent warning threshold                         | Factory default setting (100% of I <sub>OUT</sub> max)                             |      | 40                   |      | Α     |

| PERFORMAN                                        | CE                                                    |                                                                                    |      |                      |      |       |

|                                                  | Efficiency <sup>(1)</sup>                             | I <sub>OUT_A</sub> = 90 A, V <sub>OUT_B</sub> disabled                             |      | 92%                  |      |       |

|                                                  | Efficiency                                            | I <sub>OUT_B</sub> = 30 A, V <sub>OUT_A</sub> = disabled                           |      | 92%                  |      |       |

| TIMING                                           | ·                                                     |                                                                                    |      |                      |      |       |

| t <sub>STARTUPA</sub>                            | VOUTA start-up time                                   | V <sub>VBOOT</sub> > 0 V, no faults, TON_DELAY = 0xB1EC (PAGE 0) (default setting) | 0.38 | 0.48                 | 0.58 | ms    |

| t <sub>STARTUPB</sub>                            | VOUTB start-up time                                   | V <sub>VBOOT</sub> > 0 V, no faults, TON_DELAY = 0xB396 (PAGE 1) (default setting) | 0.8  | 0.9                  | 1    | ms    |

| t <sub>VCCVID</sub>                              | VID change to VSP change                              | ACK of SetVID_x command to start of voltage ramp                                   |      |                      | 500  | ns    |

| t <sub>ON_BLANK</sub>                            | Rising-edge blanking time <sup>(3)</sup>              | MFR_SPEC_09<8:6> = 110b<br>(default setting)                                       | 53   | 72                   | 92   | ns    |

| SL <sub>SET</sub>                                | Slew rate setting <sup>(3)</sup>                      | VOUT_TRANSITION_RATE = 0xE028 (default setting)                                    |      | 2.5                  |      | mV/μs |

| SL <sub>SS</sub>                                 | AVSP and BVSP slew rate soft-<br>start <sup>(3)</sup> | MFR_SPEC_13<8> = 0b (default setting)                                              |      | SL <sub>SET</sub> /4 |      | mV/μs |

| SWITCHING F                                      | REQUENCY                                              |                                                                                    |      |                      | '    |       |

|                                                  | Switching frequency                                   | FREQUENCY_SWITCH = 0x0190 (VOUTA default setting)                                  | 360  | 400                  | 440  | kHz   |

| f <sub>SW</sub>                                  | Switching frequency                                   | FREQUENCY_SWITCH = 0x01C2 (VOUTB default setting)                                  | 405  | 450                  | 495  | kHz   |

|                                                  | Range <sup>(3)</sup>                                  |                                                                                    | 350  |                      | 700  | kHz   |

- (1) Phase shedding disabled.

- (2) See SOA graph for derating over temperature.

- (3) Applies to both VOUTA and VOUTB.

### 6.6 References: DAC

Over recommended operating conditions. Minimum, typical and maximum values are specified through production test or design of the internal controller (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITIONS                                          | MIN     | TYP   | MAX     | UNIT |

|------------------------|--------------------------------------------|----------------------------------------------------------|---------|-------|---------|------|

| V <sub>VIDSTP</sub>    | VID step size <sup>(1)</sup>               | 5 mV DAC: Change VID0 HI to LO to HI                     |         | 5     |         | mV   |

| K <sub>RATIO</sub>     | Voltage divider ratio <sup>(1)</sup>       | VOUT_SCALE_LOOP = 0xe808,<br>VOUT_SCALE_MONITOR = 0xe808 |         | 1.000 |         |      |

| V <sub>OUT_TRIML</sub> | V <sub>OUT</sub> offset LSB <sup>(1)</sup> | MFR_SPECIFIC_05 = 0x01                                   | 0       | 1.25  | 2.5     | mV   |

|                        | V <sub>OUT</sub> offset range              | MFR_SPECIFIC_05 = 0x1F                                   | 37.5    | 38.75 | 40      |      |

| V                      |                                            | MFR_SPECIFIC_05 = 0xA0                                   | - 43.25 | - 40  | - 37.75 |      |

| V <sub>OUT_TRIMR</sub> |                                            | MFR_SPECIFIC_05 = 0x5F                                   | 56.25   | 58.75 | 61.25   | mV   |

|                        |                                            | MFR_SPECIFIC_05 = 0xE0                                   | - 63    | - 60  | - 57    |      |

<sup>(1)</sup> Applies to both VOUTA and VOUTB.

# 6.7 Telemetry

Over recommended operating conditions. Minimum, typical and maximum values are specified through production test or by design of the module/internal controller (unless otherwise noted)

|                        | PARAMETER TEST CONDITIONS                            |                                                                                      | MIN  | TYP    | MAX | UNIT |

|------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------|--------|-----|------|

| V <sub>READ_VOUT</sub> | MFR_READ_VOUT accuracy                               | 5-mV DAC : $0.25 \text{ V} \leqslant \text{V}_{\text{VSP}} \leqslant 1.52 \text{ V}$ | - 12 |        | 12  | mV   |

| V <sub>READ_VIN</sub>  | READ_VIN accuracy                                    | $8 \text{ V} \leqslant \text{V}_{\text{IN}} \leqslant 14 \text{ V}$                  |      | ±2.25% |     |      |

| I <sub>MON_ACC_A</sub> | Digital current monitor accuracy, Rail A (READ_IOUT) | I <sub>OUT</sub> = 120 A                                                             |      | ±3%    |     |      |

| I <sub>MON_ACC_B</sub> | Digital current monitor accuracy, Rail B (READ_IOUT) | I <sub>OUT</sub> = 40 A                                                              | ±3%  |        |     |      |

| Temp                   | READ_TEMP1                                           | - 40°C ≤ TSEN ≤ 150°C                                                                | - 2  | 0      | 2   | °C   |

#### 6.8 Current Sense and Calibration

Over recommended operating conditions. Typical values are specified through production test or design of the internal controller (unless otherwise noted)

|                          | PARAMETER                                          | TEST CONDITIONS                        | MIN TYP | MAX | UNIT               |

|--------------------------|----------------------------------------------------|----------------------------------------|---------|-----|--------------------|

| I <sub>MON_CAL_OF1</sub> | Current monitor calibration offset LSB (per-phase) | IOUT_CAL_OFFSET resolution (per-phase) | 0.125   |     | Α                  |

|                          | Current monitor calibration offset                 | IOUT_CAL_OFFSET = 0xE808 (per-phase)   | 1       |     | Α                  |

| MON_CAL_OF2              | range (per-phase)                                  | IOUT_CAL_OFFSET = 0xEFF9 (per-phase)   | - 0.875 |     | Α                  |

| I <sub>MON_CAL_OF3</sub> | Current monitor calibration offset LSB (total)     | IOUT_CAL_OFFSET resolution (total)     | 0.25    |     | Α                  |

|                          | Current monitor calibration offset                 | IOUT_CAL_OFFSET = 0xE820 (total)       | 4       |     | Α                  |

| MON_CAL_OF4              | range (total)                                      | IOUT_CAL_OFFSET = 0xEFE2 (total)       | - 3.75  |     | Α                  |

| I <sub>MON_CAL_LSB</sub> | Current monitor calibration gain LSB               | IOUT_CAL_GAIN resolution               | 0.3125% |     |                    |

| 1                        | Current monitor calibration gain                   | IOUT_CAL_GAIN = 0xD131                 | 4.7656  |     | $\mathbf{m}\Omega$ |

| IMON_CAL_GAIN            | range                                              | IOUT_CAL_GAIN = 0xD150                 | 5.25    |     | mΩ                 |

# 6.9 Logic Interface Pins: A\_EN, A\_PGOOD, B\_EN, B\_PGOOD, RESET

Over recommended operating conditions. Minimum, typical and maximum values are specified through production test or design of the internal controller (unless otherwise noted)

|                        | PARAMETER                                | TEST CONDITIONS                                                  | MIN   | TYP  | MAX  | UNIT |

|------------------------|------------------------------------------|------------------------------------------------------------------|-------|------|------|------|

| R <sub>RPGDL</sub>     | Open-drain pulldown resistance           | $V_{A\_PGOOD} = V_{B\_PGOOD} = 0.45 \text{ V}$                   |       | 36   | 50   | Ω    |

| I <sub>VRTTLK</sub>    | Open-drain leakage current               | SDIO, A_PGOOD, B_PGOOD, Hi Z Leakage, 3.3-V applied in off state | - 2   | 0.2  | 2    | μA   |

| V <sub>AENL</sub>      | Channel A ENABLE logic low               |                                                                  |       |      | 0.7  | V    |

| V <sub>AENH</sub>      | Channel A ENABLE logic high              |                                                                  | 0.8   |      |      | V    |

| V <sub>AENHYS</sub>    | Channel A ENABLE hysteresis              |                                                                  | 0.028 | 0.05 | 0.07 | V    |

| t <sub>AENDIG</sub>    | Channel A ENABLE deglitch <sup>(1)</sup> |                                                                  | 0.2   |      |      | μs   |

| I <sub>AENH</sub>      | Channel A I/O 1.1-V leakage              | V <sub>A_EN</sub> = 1.1 V                                        |       |      | 25   | μA   |

| V <sub>BENL</sub>      | Channel B ENABLE logic low               |                                                                  |       |      | 0.7  | V    |

| V <sub>BENH</sub>      | Channel B ENABLE logic high              |                                                                  | 0.8   |      |      | V    |

| V <sub>BENHYS</sub>    | Channel B ENABLE hysteresis              |                                                                  | 0.028 | 0.05 | 0.07 | V    |

| t <sub>BENDIG</sub>    | Channel B ENABLE deglitch <sup>(1)</sup> |                                                                  | 0.2   |      |      | μs   |

| t <sub>AENVRRDYF</sub> | Channel A ENABLE low to A_PGOOD low      | From A_EN low to A_PGOOD low                                     |       |      | 1.5  | μs   |

| I <sub>BENH</sub>      | Channel B I/O 1.1-V leakage              | V <sub>BENH</sub> = 1.1 V                                        |       |      | 25   | μA   |

| V <sub>RSTL</sub>      | RESET logic low                          |                                                                  |       |      | 0.8  | V    |

| V <sub>RSTH</sub>      | RESET logic high <sup>(1)</sup>          |                                                                  | 1.09  |      |      | V    |

| t <sub>RSTTDLY</sub>   | RESET delay time                         |                                                                  |       | 1    |      | μs   |

<sup>(1)</sup> Specified by design. Not production tested.

#### 6.10 Protections: OVP and UVP

Over recommended operating conditions. Minimum, typical and maximum values are specified through production test or design of the internal controller (unless otherwise noted)

|                       | PARAMETER                                              | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| V <sub>RDYH5</sub>    | Tracking OVP                                           | Measured at the VSP pin wrt VID code. Device latches OFF.        | 330  |      | 400  | mV   |

| V <sub>RDYH0</sub>    | Tracking OVF                                           | Measured at the VSP pin wrt VID code. Device latches OFF.        | 140  |      | 200  | mV   |

| t <sub>RDYDGLTO</sub> | VR_RDY deglitch time                                   | See <sup>(1)</sup>                                               |      |      | 2.5  | μs   |

| t <sub>RDYDGLTU</sub> | VR_RDY deglitch time                                   | f <sub>SW</sub> = 500 kHz                                        |      | 4    |      | μs   |

| V <sub>RDYL</sub>     | Undervoltage protection <sup>(2)</sup>                 | (V <sub>VSP</sub> + V <sub>DROOP</sub> ) with respect to VID     | 370  | 400  | 430  | mV   |

| V <sub>OVPA</sub>     | Fixed overvoltage protection, channel A <sup>(2)</sup> | $V_{AVSP} > V_{OVP}$ for 1 $\mu$ s, ENABLE = HI or LO, PWM to LO | 2.75 | 2.75 | 2.86 | V    |

| V <sub>OVPB</sub>     | Fixed overvoltage protection, channel B <sup>(2)</sup> | $V_{BVSP} > V_{OVP}$ for 1 $\mu$ s, ENABLE = HI or LO, PWM to LO | 1.85 | 1.9  | 1.95 | V    |

<sup>(1)</sup> Time from VSP out of 200-mV or 400-mV VDAC boundary to VR\_RDY low.

<sup>(2)</sup> Can be programmed with different configurations.

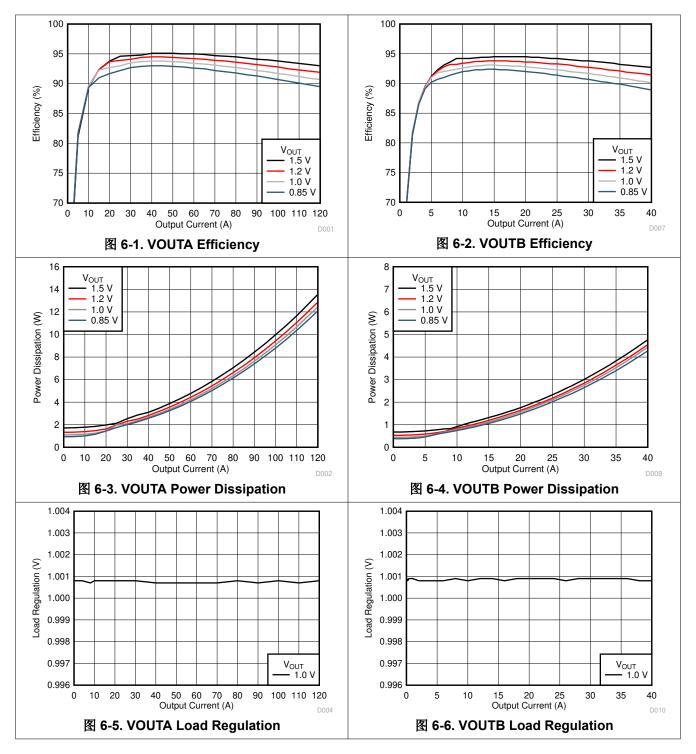

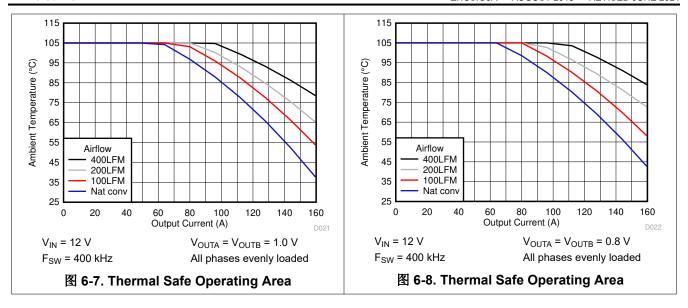

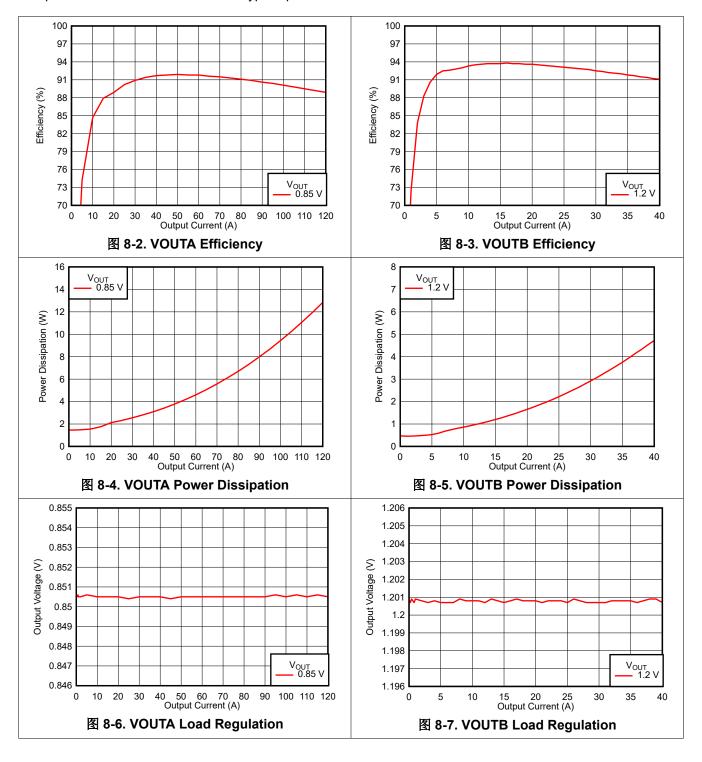

# 6.11 Typical Characteristics (V<sub>IN</sub> = 12 V)

www.ti.com.cn

# 7 Detailed Description

# 7.1 Overview

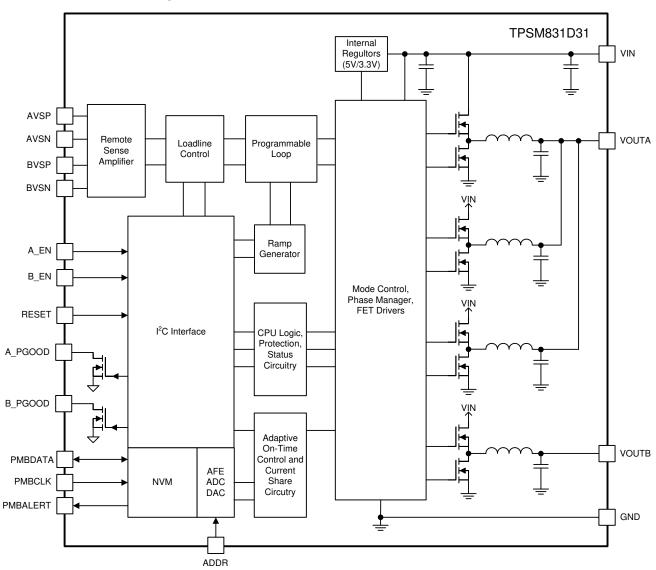

The TPSM831D31 is a PMBus-controlled, dual output 4-phase power module. Both outputs have a programmable output voltage range of 0.25 V to 1.52 V. The first output is configured as a 3-phase power stage that can deliver up to 120 A of output current. The second output is a single phase power stage that can deliver up to 40 A of output current

# 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

# 7.3 Feature Description

#### 7.3.1 DCAP+ Control

For high current applications, D-CAP+ control architecture, combines the benefits of D-CAP constant on-time control with those of multiphase converters. D-CAP+ control ensures that inductor currents of individual phases are fed back so the system has accurate droop control and good current-sharing performance as well an error amplifier is utilized to improve DC accuracy over load and line.

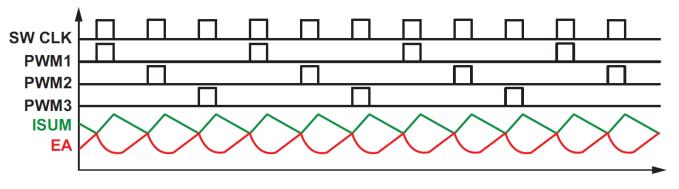

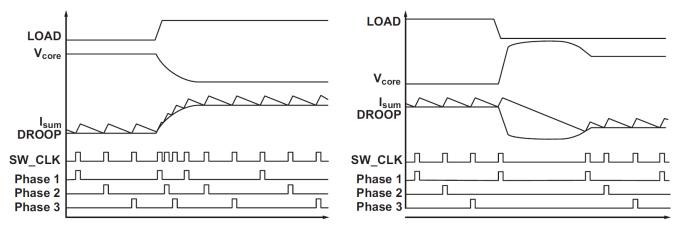

ા 7-1 illustrates the operational waveforms of D-CAP+ control architecture with 3 phases in steady state. By using the adaptive on-time control concept, a pseudo fixed switching frequency of SW\_CLK is generated by comparing the summed inductor currents, ISUM, and the error amplifier output, EA, signal. By distributing the switching signal to different phases, all phases can be perfectly interleaved in steady state. During load transients, the switching frequency is varied to improve the transient performance as shown in ₹ 7-2. Variable switching frequencies of different phases can be observed.

One important feature of a multiphase converter is the capability to dynamically add or drop the number of operational phases based on load conditions. The goal is to optimize efficiency while maintaining good load transient performance.

图 7-1. 3-Phase Steady State Switching

图 7-2. 3-Phase Transient Operation

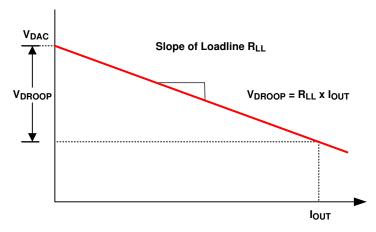

#### 7.3.2 Setting the Load-Line (DROOP)

图 7-3. Load Line

The loadline can be set with VOUT\_DROOP register via PMBus. The programmable range for channel A is between 0 m $\Omega$  and 3.125 m $\Omega$  with 64 options, and the range for channel B is between 0 m $\Omega$  and 0.875 m $\Omega$  with 16 options to fulfill the requirements for different applications. See  $\frac{1}{8}$  7-27 for the DC load line settings.

#### 7.3.3 Start-Up Timing

The start-up time is the time from when a start condition is received (as programmed by the ON\_OFF\_CONFIG command) until the output voltage starts to rise. The start-up time for both outputs can be programmed using the TON DELAY command as shown in 表 7-1.

| 7 Hotalt op Hillo     |                      |                                                                                                                                  |  |  |  |  |  |

|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| START-UP TIME (ms)(1) |                      |                                                                                                                                  |  |  |  |  |  |

| MIN TYP MAX           |                      |                                                                                                                                  |  |  |  |  |  |

| 0.38                  | 0.48                 | 0.58                                                                                                                             |  |  |  |  |  |

| 0.8                   | 0.9                  | 1                                                                                                                                |  |  |  |  |  |

| 1.308                 | 1.408                | 1.508                                                                                                                            |  |  |  |  |  |

| 2.28                  | 2.432                | 2.584                                                                                                                            |  |  |  |  |  |

|                       | Invalid              |                                                                                                                                  |  |  |  |  |  |

|                       | 0.38<br>0.8<br>1.308 | MIN         TYP           0.38         0.48           0.8         0.9           1.308         1.408           2.28         2.432 |  |  |  |  |  |

表 7-1. Start-Up Time

(1) Channel A (PAGE 0); Channel B (PAGE 1)

#### 7.3.4 Load Transitions

The TPSM831D31 achieves fast load transient performance using the inherent variable switching frequency characteristics. When there is a sudden load increase, the output voltage rapidly drops, which forces the PWM pulses to switch sooner and more frequently which causes the inductor current to rapidly increase. As the inductor current reaches the new load current, the device reaches a steady-state operating condition and the PWM switching resumes the steady-state frequency.

When there is a sudden load release, the output voltage rapidly rises, which forces the PWM pulses to be delayed until the inductor current reaches the new load current. At that point, the switching resumes and steady-state switching continues.

# 7.3.5 Switching Frequency

The TPSM831D31 switching frequency can be selected from several values between 350 kHz to 700 kHz as shown in 表 7-2. The FREQUENCY\_SWITCH command is used to select the desired switching frequency.

表 7-2. Switching Frequency Select

|                           | = Omitoring Froquency Coloct                              |

|---------------------------|-----------------------------------------------------------|

| FREQUENCY<br>SELECT (kHz) | COMMAND                                                   |

| 350                       | FREQUENCY_SWITCH = 0x015E                                 |

| 400                       | FREQUENCY_SWITCH = 0x0190 (VOUTA factory default setting) |

| 450                       | FREQUENCY_SWITCH = 0x01C2 (VOUTB factory default setting) |

| 500                       | FREQUENCY_SWITCH = 0x01F4                                 |

| 550                       | FREQUENCY_SWITCH = 0x0226                                 |

| 600                       | FREQUENCY_SWITCH = 0x0258                                 |

| 650                       | FREQUENCY_SWITCH = 0x028A                                 |

| 700                       | FREQUENCY_SWITCH = 0x02BC                                 |

#### 7.3.6 RESET Function

During adaptive voltage scaling (AVS) operation, the voltage may become falsely adjusted to be out of ASIC operating range. The RESET function returns the voltage to the VBOOT voltage. When the voltage is out of ASIC operating range, the ASIC issues a RESET signal to the TPSM831D31 device. The device senses this signal and after a delay of greater than 1  $\mu$ s, it sets an internal RESET\_FAULT signal and sets VOUT\_COMMAND to VBOOT. The device pulls the output voltage to the VBOOT level with the slew rate set by VOUT\_TRANSITION\_RATE command.

When the RESET pin signal goes high, the internal RESET\_FAULT signal goes low.

表 7-3. VBOOT

| BOOT VOLTAGE SETTING (5-mV DAC) | BOOT VOLTAGE (V) |

|---------------------------------|------------------|

| MFR_SPEC_11<7:0> = 00h          | 0.000            |

| MFR_SPEC_11<7:0> = 33h          | 0.500            |

| MFR_SPEC_11<7:0> = 83h          | 0.900            |

| MFR_SPEC_11<7:0> = 97h          | 1.000            |

| MFR_SPEC_11<7:0> = BFh          | 1.200            |

# 7.3.7 VID Table

The DAC voltage VDAC can be changed via PMBus according to 表 7-4.

# 表 7-4. VID Table (5 mV DAC)

|                  | 表 7-4. VID Table (5 MV DAC) |                  |             |                  |             |                  |             |                  |             |                  |             |

|------------------|-----------------------------|------------------|-------------|------------------|-------------|------------------|-------------|------------------|-------------|------------------|-------------|

| VID Hex<br>VALUE | DAC<br>STEP                 | VID Hex<br>VALUE | DAC<br>STEP | VID Hex<br>VALUE | DAC<br>STEP | VID Hex<br>VALUE | DAC<br>STEP | VID Hex<br>VALUE | DAC<br>STEP | VID Hex<br>VALUE | DAC<br>STEP |

| 00               | 0.000                       | 2B               | 0.460       | 56               | 0.675       | 81               | 0.890       | AC               | 1.105       | D7               | 1.320       |

| 01               | 0.250                       | 2C               | 0.465       | 57               | 0.680       | 82               | 0.895       | AD               | 1.110       | D8               | 1.325       |

| 02               | 0.255                       | 2D               | 0.470       | 58               | 0.685       | 83               | 0.900       | AE               | 1.115       | D9               | 1.330       |

| 03               | 0.260                       | 2E               | 0.475       | 59               | 0.690       | 84               | 0.905       | AF               | 1.120       | DA               | 1.335       |

| 04               | 0.265                       | 2F               | 0.480       | 5A               | 0.695       | 85               | 0.910       | В0               | 1.125       | DB               | 1.340       |

| 05               | 0.270                       | 30               | 0.485       | 5B               | 0.700       | 86               | 0.915       | B1               | 1.130       | DC               | 1.345       |

| 06               | 0.275                       | 31               | 0.490       | 5C               | 0.705       | 87               | 0.920       | B2               | 1.135       | DD               | 1.350       |

| 07               | 0.280                       | 32               | 0.495       | 5D               | 0.710       | 88               | 0.925       | В3               | 1.140       | DE               | 1.355       |

| 08               | 0.285                       | 33               | 0.500       | 5E               | 0.715       | 89               | 0.930       | B4               | 1.145       | DF               | 1.360       |

| 09               | 0.290                       | 34               | 0.505       | 5F               | 0.720       | 8A               | 0.935       | B5               | 1.150       | E0               | 1.365       |

| 0A               | 0.295                       | 35               | 0.510       | 60               | 0.725       | 8B               | 0.940       | В6               | 1.155       | E1               | 1.370       |

| 0B               | 0.300                       | 36               | 0.515       | 61               | 0.730       | 8C               | 0.945       | В7               | 1.160       | E2               | 1.375       |

| 0C               | 0.305                       | 37               | 0.520       | 62               | 0.735       | 8D               | 0.950       | В8               | 1.165       | E3               | 1.380       |

| 0D               | 0.310                       | 38               | 0.525       | 63               | 0.740       | 8E               | 0.955       | В9               | 1.170       | E4               | 1.385       |

| 0E               | 0.315                       | 39               | 0.530       | 64               | 0.745       | 8F               | 0.960       | BA               | 1.175       | E5               | 1.390       |

| 0F               | 0.320                       | 3A               | 0.535       | 65               | 0.750       | 90               | 0.965       | BB               | 1.180       | E6               | 1.395       |

| 10               | 0.325                       | 3B               | 0.540       | 66               | 0.755       | 91               | 0.970       | BC               | 1.185       | E7               | 1.400       |

| 11               | 0.330                       | 3C               | 0.545       | 67               | 0.760       | 92               | 0.975       | BD               | 1.190       | E8               | 1.405       |

| 12               | 0.335                       | 3D               | 0.550       | 68               | 0.765       | 93               | 0.980       | BE               | 1.195       | E9               | 1.410       |

| 13               | 0.340                       | 3E               | 0.555       | 69               | 0.770       | 94               | 0.985       | BF               | 1.200       | EA               | 1.415       |

| 14               | 0.345                       | 3F               | 0.560       | 6A               | 0.775       | 95               | 0.990       | C0               | 1.205       | EB               | 1.420       |

| 15               | 0.350                       | 40               | 0.565       | 6B               | 0.780       | 96               | 0.995       | C1               | 1.210       | EC               | 1.425       |

| 16               | 0.355                       | 41               | 0.570       | 6C               | 0.785       | 97               | 1.000       | C2               | 1.215       | ED               | 1.430       |

| 17               | 0.360                       | 42               | 0.575       | 6D               | 0.790       | 98               | 1.005       | C3               | 1.220       | EE               | 1.435       |

| 18               | 0.365                       | 43               | 0.580       | 6E               | 0.795       | 99               | 1.010       | C4               | 1.225       | EF               | 1.440       |

| 19               | 0.370                       | 44               | 0.585       | 6F               | 0.800       | 9A               | 1.015       | C5               | 1.230       | F0               | 1.445       |

| 1A               | 0.375                       | 45               | 0.590       | 70               | 0.805       | 9B               | 1.020       | C6               | 1.235       | F1               | 1.450       |

| 1B               | 0.380                       | 46               | 0.595       | 71               | 0.810       | 9C               | 1.025       | C7               | 1.240       | F2               | 1.455       |

| 1C               | 0.385                       | 47               | 0.600       | 72               | 0.815       | 9D               | 1.030       | C8               | 1.245       | F3               | 1.460       |

| 1D               | 0.390                       | 48               | 0.605       | 73               | 0.820       | 9E               | 1.035       | C9               | 1.250       | F4               | 1.465       |

| 1E               | 0.395                       | 49               | 0.610       | 74               | 0.825       | 9F               | 1.040       | CA               | 1.255       | F5               | 1.470       |

| 1F               | 0.400                       | 4A               | 0.615       | 75               | 0.830       | A0               | 1.045       | СВ               | 1.260       | F6               | 1.475       |

| 20               | 0.405                       | 4B               | 0.620       | 76               | 0.835       | A1               | 1.050       | CC               | 1.265       | F7               | 1.480       |

| 21               | 0.410                       | 4C               | 0.625       | 77               | 0.840       | A2               | 1.055       | CD               | 1.270       | F8               | 1.485       |

| 22               | 0.415                       | 4D               | 0.630       | 78               | 0.845       | A3               | 1.060       | CE               | 1.275       | F9               | 1.490       |

| 23               | 0.420                       | 4E               | 0.635       | 79               | 0.850       | A4               | 1.065       | CF               | 1.280       | FA               | 1.495       |

| 24               | 0.425                       | 4F               | 0.640       | 7A               | 0.855       | A5               | 1.070       | D0               | 1.285       | FB               | 1.500       |

| 25               | 0.430                       | 50               | 0.645       | 7B               | 0.860       | A6               | 1.075       | D1               | 1.290       | FC               | 1.505       |

| 26               | 0.435                       | 51               | 0.650       | 7C               | 0.865       | A7               | 1.080       | D2               | 1.295       | FD               | 1.510       |

| 27               | 0.440                       | 52               | 0.655       | 7D               | 0.870       | A8               | 1.085       | D3               | 1.300       | FE               | 1.515       |

| 28               | 0.445                       | 53               | 0.660       | 7E               | 0.875       | A9               | 1.090       | D4               | 1.305       | FF               | 1.520       |

| 29               | 0.450                       | 54               | 0.665       | 7F               | 0.880       | AA               | 1.095       | D5               | 1.310       |                  |             |

|                  |                             |                  |             |                  |             |                  |             |                  |             |                  |             |

Instruments

# 表 7-4. VID Table (5 mV DAC) (continued)

| VID Hex | DAC   | VID Hex | DAC  |

|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|------|

| VALUE   | STEP  | VALUE   | STEP |

| 2A      | 0.455 | 55      | 0.670 | 80      | 0.885 | AB      | 1.100 | D6      | 1.315 |         |      |

#### 7.4 Device Functional Modes

#### 7.4.1 Continuous Conduction Mode

The TPSM831D31 device operates in continuous conduction mode (CCM) at a fixed frequency. As programmed from the factory, phase shedding is disabled and can be enabled with a PMBus command. To begin power conversion, the EN signal and/or OPERATION command must be asserted high. Following a fault that stops power conversion, the enable contol must be pulled low and then re-asserted high to resume power conversion.

# 7.4.2 Operation With EN Signal Control

According to a bit value in the ON OFF CONFIG register, the TPSM831D31 device can be commanded to use the EN pin to enable or disable power conversion, regardless of the state of the OPERATION command. The TPSM831D31 is factory programmed to use the EN pin only. When the EN pin is pulled low, power conversion stops immediately without first waiting for a turn-off delay or actively ramping down the output voltage.

#### 7.4.3 Operation With OPERATION Control

According to a bit value in the ON OFF CONFIG register, the TPSM831D31 device can be commanded to use the OPERATION command to enable or disable conversion, regardless of the state of the EN signal.

### 7.4.4 Operation With EN and OPERATION Control

According to a bit value in the ON OFF CONFIG register, the TPSM831D31 device can be commanded to require both the assertion of the EN pin, and the OPERATION command to enable or disable conversion.

#### 7.5 Programming

#### 7.5.1 PMBus Connections

The TPSM831D31 device can support either 100-kHz class, 400-kHz class or 1-MHz class operation, with 1.8-V or 3.3-V logic levels. Connection for the PMBus interface should follow the DC specifications given in Section 4.3 of the System Management Bus (SMBus) Specification V3.0 . The complete SMBus specification is available from the SMBus website, smbus.org.

#### 7.5.2 PMBus Address Selection

The PMBus slave address is set by the voltage on the ADDR pin and is selected with a resistor from the ADDR pin to GND. Refer to 表 7-5.

Note that TPSM831D31 uses 7 bit addressing, per the SMBus specification. Users communicating to the device using generic I<sup>2</sup>C drivers should be aware that these 7 bits occupy the most significant bits of the first byte in each transaction, with the least significant bit being the data direction bit (0 for write operations, 1 for read operations). That is, for read transactions, the address byte is  $A_6A_5A_4A_3A_2A_1A_01$  and for write operations the address byte is  $A_6A_5A_4A_3A_2A_1A_00$ . Refer to the SMBus specification for more information.

表 7-5. PMBus Slave Address Selection

| V <sub>ADDR</sub> (V) | PMBus Address<br>(7 bit binary)<br>A <sub>6</sub> A <sub>5</sub> A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | PMBus Address<br>(7 bit decimal) | R <sub>ADDRL</sub> (kΩ) | I <sup>2</sup> C Address Byte<br>(Write Operation) | I <sup>2</sup> C Address Byte<br>(Read Operation) |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|----------------------------------------------------|---------------------------------------------------|

| ≤ 0.039 V             | 1011000b                                                                                                                                    | 88d                              | 0                       | B0h                                                | B1h                                               |

| 0.073 V ± 15 mV       | 1011001b                                                                                                                                    | 89d                              | 0.453                   | B2h                                                | B3h                                               |

| 0.122 V ± 15 mV       | 1011010b                                                                                                                                    | 90d                              | 0.768                   | B4h                                                | B5h                                               |

| 0.171 V ± 15 mV       | 1011011b                                                                                                                                    | 91d                              | 1.13                    | B6h                                                | B7h                                               |

| 0.219 V ± 15 mV       | 1011100b                                                                                                                                    | 92d                              | 1.47                    | B8h                                                | B9h                                               |

| 0.268 V ± 15 mV       | 1011101b                                                                                                                                    | 93d                              | 1.87                    | BAh                                                | BBh                                               |

# 表 7-5. PMBus Slave Address Selection (continued)

| V <sub>ADDR</sub> (V) | PMBus Address<br>(7 bit binary)<br>A <sub>6</sub> A <sub>5</sub> A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | PMBus Address<br>(7 bit decimal) | R <sub>ADDRL</sub> (kΩ) | I <sup>2</sup> C Address Byte<br>(Write Operation) | I <sup>2</sup> C Address Byte<br>(Read Operation) |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|----------------------------------------------------|---------------------------------------------------|

| 0.317 V ± 15 mV       | 1011110b                                                                                                                                    | 94d                              | 2.32                    | BCh                                                | BDh                                               |

| 0.366 V ± 15 mV       | 1011111b                                                                                                                                    | 95d                              | 2.74                    | BEh                                                | BFh                                               |

| 0.415 V ± 15 mV       | 1100000b                                                                                                                                    | 96d                              | 3.24                    | C0h                                                | C1h                                               |

| 0.464 V ± 15 mV       | 1100001b                                                                                                                                    | 97d                              | 3.74                    | C2h                                                | C3h                                               |

| 0.513 V ± 15 mV       | 1100010b                                                                                                                                    | 98d                              | 4.32                    | C4h                                                | C5h                                               |

| 0.562 V ± 15 mV       | 1100011b                                                                                                                                    | 99d                              | 4.99                    | C6h                                                | C7h                                               |

| 0.610 V ± 15 mV       | 1100100b                                                                                                                                    | 100d                             | 5.62                    | C8h                                                | C9h                                               |

| 0.660 V ± 15 mV       | 1100101b                                                                                                                                    | 101d                             | 6.34                    | CAh                                                | CBh                                               |

| 0.708 V ± 15 mV       | 1100110b                                                                                                                                    | 102d                             | 7.15                    | CCh                                                | CDh                                               |

| 0.757 V ± 15 mV       | 1100111b                                                                                                                                    | 103d                             | 8.06                    | CEh                                                | CFh                                               |

| 0.806 V ± 15 mV       | 1101000b                                                                                                                                    | 104d                             | 9.09                    | D0h                                                | D1h                                               |

| 0.854 V ± 15 mV       | 1101001b                                                                                                                                    | 105d                             | 10.0                    | D2h                                                | D3h                                               |

| 0.903 V ± 15 mV       | 1101010b                                                                                                                                    | 106d                             | 11.3                    | D4h                                                | D5h                                               |

| 0.952 V ± 15 mV       | 1101011b                                                                                                                                    | 107d                             | 12.7                    | D6h                                                | D7h                                               |

| 1.000 V ± 15 mV       | 1101100b                                                                                                                                    | 108d                             | 14.3                    | D8h                                                | D9h                                               |

| 1.050 V ± 15 mV       | 1101101b                                                                                                                                    | 109d                             | 16.2                    | DAh                                                | DBh                                               |

| 1.098 V ± 15 mV       | 1101110b                                                                                                                                    | 110d                             | 18.2                    | DCh                                                | DDh                                               |

| 1.147 V ± 15 mV       | 1101111b                                                                                                                                    | 111d                             | 20.5                    | DEh                                                | DFh                                               |

| 1.196 V ± 15 mV       | 1110000b                                                                                                                                    | 112d                             | 23.7                    | E0h                                                | E1h                                               |

| 1.245 V ± 15 mV       | 1110001b                                                                                                                                    | 113d                             | 27.4                    | E2h                                                | E3h                                               |

| 1.294 V ± 15 mV       | 1110010b                                                                                                                                    | 114d                             | 31.6                    | E4h                                                | E5h                                               |

| 1.343 V ± 15 mV       | 1110011b                                                                                                                                    | 115d                             | 37.4                    | E6h                                                | E7h                                               |

| 1.392 V ± 15 mV       | 1110100b                                                                                                                                    | 116d                             | 45.3                    | E8h                                                | E9h                                               |

| 1.440 V ± 15 mV       | 1110101b                                                                                                                                    | 117d                             | 54.9                    | EAh                                                | EBh                                               |