**TPSM82816**

# TPSM8281x 具有集成电感器和频率同步功能、采用 MicroSIP™ 和 MagPack™ 封 装的 2.7V 至 6V 输入、4A/6A 降压电源模块

# 1 特性

可调和可同步开关频率为 1.8MHz 至 4MHz

• 展频时钟(可选)

• 可选强制 PWM 或 PFM/PWM 运行

• 输出电压精度为 ±1% ( PWM 操作 )

• 输入电压范围: 2.7V 至 6V

输出电压范围: 0.6V 至 5.5V

• 可调软启动或跟踪

具有窗口比较器的电源正常输出

精密使能输入可实现

- 用户定义的欠压锁定

- 准确时序控制

• 针对低 EMI 要求进行了优化

- 无键合线封装

- 采用 MagPack 技术屏蔽电感器和 IC

- 通过优化的引脚排列简化了布局

• 100% 占空比

输出放电

典型静态电流:18µA

• 工作温度范围: -40°C 至 125°C

• 最大封装高度: 1.6mm (SIE)/2.0mm (VCA)

• 优异的热性能

与以下器件引脚对引脚兼容:

- SIE: TPSM82813 (3A) 和 TPSM82810 (4A)

- VCA (MagPack): TPSM82811 (1A). TPSM82812 (2A)、TPSM82813 (3A)

# 3 说明

TPSM8281x 是具有集成电感器和引脚对引脚兼容性且 高效易用的 1A、2A、3A、4A 和 6A 同步降压直流/直 流电源模块系列。这些器件基于固定频率峰值电流模式 控制拓扑,用于具有高功率密度和易用性要求的电信、 测试和测量以及医疗应用领域。低阻开关可在高温环境 下支持高达 6A 的持续输出电流。用户可通过外部方式 在 1.8MHz 至 4MHz 范围内调节开关频率,亦可在该 频率范围内将其同步至外部时钟。在省电模式下, TPSM8281x 会在轻负载时自动进入 PFM,从而可在 整个负载范围内保持高效率。TPSM8281x 可在 PWM 模式下提供 1% 的输出电压精度,这有助于实现具有高 输出电压精度的电源设计。SS/TR 引脚可设置启动时 间或跟踪向外部源提供的输出电压。此行为可实现不同 电源轨的外部时序控制并限制启动期间的浪涌电流。

#### 器件信息

| 器件型号(3)                  | 输出电流 | <b>封装</b> <sup>(1)</sup> | 本体尺寸(标<br>称值)    |

|--------------------------|------|--------------------------|------------------|

| TPSM82814 <sup>(2)</sup> | 4A   | VCA ( QFN-               | 2.5mm ×          |

| TPSM82816                | 6A   | FCMOD, 13)               | 3.0mm            |

| TPSM82816                | 6A   | SIE ( uSiP ,<br>14 )     | 3.0mm ×<br>4.0mm |

- 有关更多信息,请参阅节11。

- 预发布信息(非量产数据)。 (2)

- 请参阅器件比较表。

### 2 应用

- 光学模块、数据中心互连

- 测试和测量

- 患者监护和诊断

- 无线基础设施

- 航天和国防

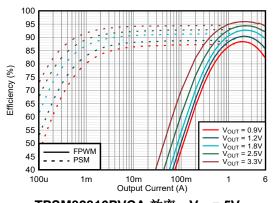

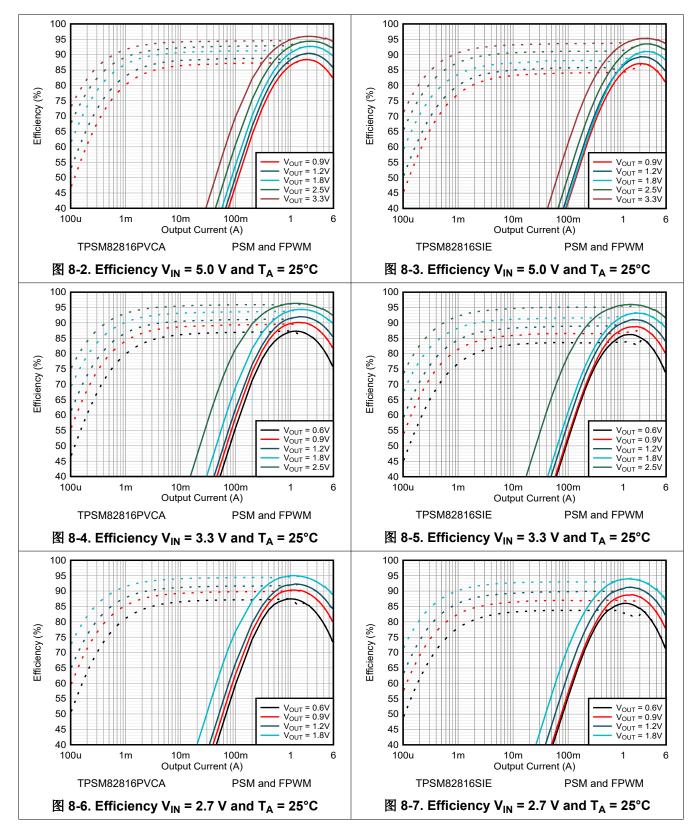

TPSM82816PVCA 效率; V<sub>IN</sub> = 5V

# **Table of Contents**

| 1 特性                                 | 1              | 8 Application and Implementation        | 17              |

|--------------------------------------|----------------|-----------------------------------------|-----------------|

| 2 应用                                 | 1              | 8.1 Application Information             | 17              |

| 3 说明                                 |                | 8.2 Typical Application                 | 17              |

| 4 Device Comparison Table            |                | 8.3 System Examples                     | 25              |

| 5 Pin Configuration and Functions    |                | 8.4 Power Supply Recommendations        | <mark>26</mark> |

| 6 Specifications                     |                | 8.5 Layout                              | <mark>27</mark> |

| 6.1 Absolute Maximum Ratings         |                | 9 Device and Documentation Support      | <mark>29</mark> |

| 6.2 ESD Ratings                      |                | 9.1 Device Support                      | 29              |

| 6.3 Recommended Operating Conditions |                | 9.2 Documentation Support               | 29              |

| 6.4 Thermal Information              |                | 9.3 接收文档更新通知                            | 29              |

| 6.5 Electrical Characteristics       | <mark>7</mark> | 9.4 支持资源                                | 29              |

| 6.6 Typical Characteristics          |                | 9.5 Trademarks                          | 29              |

| 7 Detailed Description               |                | 9.6 静电放电警告                              | 29              |

| 7.1 Overview                         |                | 9.7 术语表                                 |                 |

| 7.2 Functional Block Diagram         | 10             | 10 Revision History                     |                 |

| 7.3 Feature Description              |                | 11 Mechanical, Packaging, and Orderable |                 |

| 7.4 Device Functional Modes          |                | Information                             | 30              |

# **4 Device Comparison Table**

| DEVICE NUMBER <sup>(1)</sup>  | OUTPUT CURRENT | SPREAD SPECTRUM CLOCKING | BODY SIZE (NOM)                    |

|-------------------------------|----------------|--------------------------|------------------------------------|

| TPSM82814PVCAR <sup>(2)</sup> | 4 A            |                          | 2.5 mm × 3.0 mm × 1.95 mm          |

| TPSM82816PVCAR                | 6 A            | Set by COMP / FSET pin   | 2.5 11111 × 5.5 11111 × 1.55 11111 |

| TPSM82816SIER                 | 6 A            |                          | 3.0 mm × 4.0 mm × 1.6 mm           |

For all available packages, see 节 11.

提交文档反馈

3

English Data Sheet: SLUSEY7

Preview information (not Production Data). (2)

# 5 Pin Configuration and Functions

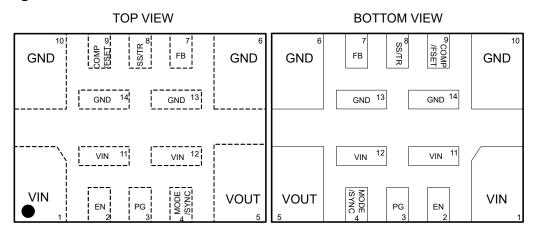

图 5-1. uSiP 14-Pin SIE Package

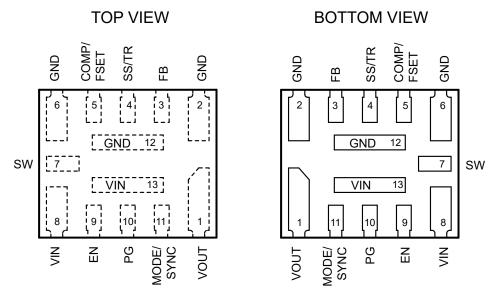

图 5-2. QFN-FCMOD 13-Pin VCA Package

# 表 5-1. Pin Functions

|               | PIN TYPE <sup>(1)</sup> |          | TVDE(1)  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-------------------------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | SIE                     | VCA      | I TPE("/ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

| EN            | 2                       | 9        | I        | This pin is the enable pin of the device. Connect to logic low to disable the device. Pull high to enable the device. Do not leave this pin unconnected.                                                                                                                                                                                                                              |

| FB            | 7                       | 3        | I        | Voltage feedback input. Connect the output voltage resistor divider to this pin.                                                                                                                                                                                                                                                                                                      |

| GND           | 6, 10, 13, 14           | 2, 6, 12 |          | Ground pin                                                                                                                                                                                                                                                                                                                                                                            |

| MODE/<br>SYNC | 4                       | 11       | ı        | The device runs in PSM (auto PFM/PWM transition) mode when this pin is pulled low. When the pin is pulled high, the device runs in forced PWM mode. Do not leave this pin unconnected. The MODE/SYNC pin can also be used to synchronize the device to an external frequency. See <i>Synchronizing to an External Clock</i> .                                                         |

| COMP/<br>FSET | 9                       | 5        | I        | Device compensation and frequency set input. A resistor from this pin to GND defines the compensation of the control loop as well as the switching frequency if not externally synchronized. The switching frequency is set to 2.25 MHz if the pin is tied to GND or VIN. Spread spectrum is also enabled and disabled by this pin. See COMP/FSET. Do not leave this pin unconnected. |

| PG            | 3                       | 10       | 0        | Open-drain power-good output with window comparator. This pin is pulled to GND while VOUT is outside the power-good threshold. This pin can be left open or tied to GND if not used. A pullup resistor can be connected to any voltage not larger than VIN.                                                                                                                           |

| SS/TR         | 8                       | 4        | I        | Soft-start, tracking pin. A capacitor connected from this pin to GND defines the output voltage rise time. The pin can also be used as an input for tracking and sequencing - see <i>Voltage Tracking</i> .                                                                                                                                                                           |

| VOUT          | 5                       | 1        |          | Output voltage pin. This pin is internally connected to the integrated inductor.                                                                                                                                                                                                                                                                                                      |

| VIN           | 1, 11, 12               | 8, 13    |          | Power supply input. Connect the input capacitor as close as possible between the VIN and GND pins.                                                                                                                                                                                                                                                                                    |

| SW            | _                       | 7        | 0        | Switch pin of the power stage. This pin can be left floating.                                                                                                                                                                                                                                                                                                                         |

<sup>(1)</sup> I = input, O = output

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)(1)

|                            |                                                   | MIN   | MAX                   | UNIT |

|----------------------------|---------------------------------------------------|-------|-----------------------|------|

|                            | VIN, EN, MODE/SYNC                                | - 0.3 | 6.5                   | V    |

|                            | SW                                                | - 0.3 | V <sub>IN</sub> +0.3  | V    |

| Pin voltage <sup>(2)</sup> | SW (transient for less than 10 ns) <sup>(3)</sup> | -3    | 10                    | V    |

|                            | FB                                                | - 0.3 | 4                     | V    |

|                            | COMP/FSET, PG, SS/TR, VOUT                        | - 0.3 | V <sub>IN</sub> + 0.3 | V    |

| I <sub>SINK_PG</sub>       | Sink Current at PG pin                            |       | 10                    | mA   |

| T <sub>J</sub>             | Operating junction temperature                    | - 40  | 125                   | °C   |

| T <sub>stg</sub>           | Storage temperature                               | - 40  | 125                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values are with respect to the network ground terminal

- (3) While switching

# 6.2 ESD Ratings

|                              |               |                                                                                 | VALUE | UNIT |

|------------------------------|---------------|---------------------------------------------------------------------------------|-------|------|

| V                            | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | \/   |

| V <sub>(ESD)</sub> discharge | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±750  | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

|                      |                                             | MIN                          | NOM | MAX | UNIT       |

|----------------------|---------------------------------------------|------------------------------|-----|-----|------------|

| V <sub>IN</sub>      | Input voltage range                         | 2.7                          |     | 6   | V          |

| V <sub>OUT</sub>     | Output voltage range                        | 0.6                          |     | 5.5 | V          |

| I <sub>OUT</sub>     | Output current                              | 0                            |     | 6   | Α          |

| C <sub>OUT</sub>     | Effective output capacitance <sup>(1)</sup> | 32 ×<br>V / V <sub>OUT</sub> |     | 470 | μF         |

| C <sub>IN</sub>      | Effective input capacitance <sup>(1)</sup>  | 5                            | 10  |     | μF         |

| R <sub>CF</sub>      |                                             | 4.5                          |     | 100 | <b>k</b> Ω |

| I <sub>SINK_PG</sub> | Sink current at PG pin                      | 0                            |     | 2   | mA         |

| TJ                   | Junction temperature                        | - 40                         |     | 125 | °C         |

(1) The values given for all the capacitors in the table are effective capacitance, which includes the DC bias effect. Due to the DC bias effect of ceramic capacitors, the effective capacitance is lower than the nominal value when a voltage is applied. Please check the manufacturer's DC bias curves for the effective capacitance vs DC voltage applied. Please see the feature description for COMP/FSET about the output capacitance vs compensation setting and output voltage.

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TPSM82816

English Data Sheet: SLUSEY7

# **6.4 Thermal Information**

|                        |                                              | TPSM8281x     |                    |                       |                       |      |

|------------------------|----------------------------------------------|---------------|--------------------|-----------------------|-----------------------|------|

| THERMAL METRIC(1)      |                                              | SIE (14 PINS) |                    | VCA (13 PINS)         |                       | UNIT |

|                        |                                              | JEDEC 51-5    | EVM                | JEDEC 51-7            | EVM                   |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 45.3          | 32.2               | 72.1                  | 26.6                  | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29            | n/a <sup>(2)</sup> | 37.2                  | n/a <sup>(2)</sup>    | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 27.4          | n/a <sup>(2)</sup> | 21.2                  | n/a <sup>(2)</sup>    | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 5.7           | 7.2                | (-0.4) <sup>(3)</sup> | (-1.9) <sup>(3)</sup> | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.2          | 12.7               | 20.8                  | 10.1                  | °C/W |

- (1) For more information about thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

- (2) Not applicable to an EVM.

- (3) The junction temperature is lower than the inductor temperature leading to a temperature increase towards the top of the package

#### **6.5 Electrical Characteristics**

Over operating junction remperature range ( $T_J = -40$ °C to +125°C) and  $V_{IN} = 2.7$  V to 6 V. Typical values at  $V_{IN} = 5$  V and  $T_J = 25$ °C. (unless otherwise noted)

|                        | PARAMETER                                            | TEST CONDITIONS                                                                                       | MIN   | TYP  | MAX  | UNIT |

|------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|------|------|------|

| SUPPLY                 |                                                      |                                                                                                       |       |      |      |      |

| IQ                     | Quiescent current                                    | EN = High, no load, device not switching, MODE/SYNC = GND, V <sub>OUT</sub> = 0.6 V                   |       | 18   | 36   | μА   |

| I <sub>SD</sub>        | Shutdown current                                     | EN = GND                                                                                              |       | 0.15 | 90   | μА   |

| V                      | Lindon (alto go lo alco ut throughold                | V <sub>IN</sub> rising                                                                                | 2.45  | 2.6  | 2.7  | V    |

| $V_{UVLO}$             | Undervoltage lockout threshold                       | V <sub>IN</sub> falling                                                                               | 2.1   | 2.5  | 2.6  | V    |

| т                      | Thermal shutdown threshold                           | T <sub>J</sub> rising                                                                                 |       | 180  |      | °C   |

| $T_{JSD}$              | Thermal shutdown hysteresis                          | T <sub>J</sub> falling                                                                                |       | 15   |      | °C   |

| CONTRO                 | OL and INTERFACE                                     |                                                                                                       |       |      |      |      |

| $V_{\text{IH,EN}}$     | Input threshold voltage                              | EN rising                                                                                             | 1.05  | 1.1  | 1.15 | V    |

| V <sub>IL,EN</sub>     | Input threshold voltage                              | EN falling                                                                                            | 0.96  | 1.0  | 1.05 | V    |

| I <sub>IH,EN</sub>     | Input leakage current into EN                        | EN = VIN or GND                                                                                       |       |      | 125  | nA   |

| V <sub>IH</sub>        | Input-threshold voltage at MODE/SYNC                 |                                                                                                       | 1.1   |      |      | V    |

| V <sub>IL</sub>        | Input-threshold voltage at MODE/SYNC                 |                                                                                                       |       |      | 0.3  | V    |

| I <sub>IH</sub>        | Input leakage current into MODE/SYNC                 |                                                                                                       |       | -    | 250  | nA   |

| f <sub>SW</sub>        | PWM switching frequency range                        | MODE/SYNC = high                                                                                      | 1.8   | 2.25 | 4    | MHz  |

| f <sub>SW</sub>        | PWM switching frequency                              | COMP/FSET = GND or V <sub>IN</sub>                                                                    | 2.08  | 2.25 | 2.4  | MHz  |

| f <sub>SW</sub>        | PWM switching frequency tolerance                    | using a resistor from COMP/FSET to GND                                                                | - 12% |      | 12%  |      |

| f <sub>SYNC</sub>      | Frequency range on MODE/SYNC pin for synchronization |                                                                                                       | 1.8   |      | 4    | MHz  |

| t <sub>Sync_lock</sub> | Time to lock to external frequency                   |                                                                                                       |       | 50   |      | μs   |

|                        | Duty cycle of synchronization signal at MODE/SYNC    |                                                                                                       | 20%   |      | 80%  |      |

| t <sub>Delay</sub>     | Enable delay time                                    | Time from EN high to device starts switching; V <sub>IN</sub> applied already                         | 135   | 270  | 520  | μs   |

| t <sub>Ramp</sub>      | Output voltage ramp time, SS/TR pin open             | I <sub>OUT</sub> = 0 mA, time from device starts switching to power good; device not in current limit | 90    | 150  | 220  | μs   |

| I <sub>SS/TR</sub>     | SS/TR source current                                 |                                                                                                       | 8     | 10   | 12   | μA   |

| R <sub>DIS,SS/T</sub>  | Internal discharge resistance on SS/TR               | EN = low                                                                                              | 0.7   | 1.1  | 1.5  | kΩ   |

|                        | Tracking gain                                        | V <sub>FB</sub> / V <sub>SS/TR</sub>                                                                  |       | 1    |      |      |

提交文档反馈

1

English Data Sheet: SLUSEY7

# 6.5 Electrical Characteristics (续)

Over operating junction remperature range ( $T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C) and  $V_{IN}$  = 2.7 V to 6 V. Typical values at  $V_{IN}$  = 5 V and  $T_J$  = 25 $^{\circ}$ C. (unless otherwise noted)

|                     | PARAMETER                                       | TEST CONDITIONS                                                                                                  | MIN  | TYP  | MAX  | UNIT |

|---------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                     | Tracking offset                                 | V <sub>FB</sub> when V <sub>SS/TR</sub> = 0 V                                                                    |      | ±1   |      | mV   |

| \/                  | UVP Power-good threshold voltage; dc            | V <sub>OUT</sub> rising (%V <sub>FB</sub> )                                                                      | 92%  | 95%  | 98%  |      |

| V <sub>TH_PG</sub>  | level                                           | V <sub>OUT</sub> falling (%V <sub>FB</sub> )                                                                     | 87%  | 90%  | 93%  |      |

| \/                  | OVP Power-good threshold voltage; dc            | V <sub>OUT</sub> rising (%V <sub>FB</sub> )                                                                      | 107% | 110% | 113% |      |

| $V_{TH\_PG}$        | level                                           | V <sub>OUT</sub> falling (%V <sub>FB</sub> )                                                                     | 104% | 107% | 111% |      |

| $V_{OL,PG}$         | Low-level output voltage at PG                  | I <sub>SINK_PG</sub> = 2 mA                                                                                      |      | 0.01 | 0.3  | V    |

| I <sub>IH,PG</sub>  | Input leakage current into PG                   | V <sub>PG</sub> = 5 V                                                                                            |      |      | 100  | nA   |

| t <sub>PG,DLY</sub> | PG deglitch time                                | for a high level to low level transition on the Power-good output                                                |      | 40   |      | μs   |

| OUTPUT              | -                                               |                                                                                                                  |      |      | '    |      |

|                     | Feedback voltage                                |                                                                                                                  |      | 0.6  |      | V    |

| $V_{FB}$            | Feedback voltage accuracy                       | PWM mode, V <sub>IN</sub> ≥ V <sub>OUT</sub> + 1 V                                                               | - 1% |      | 1%   |      |

|                     |                                                 | PFM mode, $V_{IN} \geqslant V_{OUT} + 1 \text{ V}, V_{OUT} \geqslant$ 1.5 V, Co,eff $\geqslant$ 47 $\mu\text{F}$ | - 1% |      | 2%   |      |

|                     |                                                 | PFM mode, $V_{IN} \geqslant V_{OUT}$ + 1 V, $V_{OUT}$ < 1.5 V, Co,eff $\geqslant$ 68 $\mu F$                     | - 1% |      | 2.5% |      |

|                     | Feedback voltage accuracy with voltage tracking | $V_{IN} \geqslant V_{OUT}$ + 1 V, $V_{SS/TR}$ = 0.3 V, PWM mode                                                  | - 5% |      | 5%   |      |

| I <sub>IH,FB</sub>  | Input leakage current into FB                   | V <sub>FB</sub> = 0.6 V                                                                                          |      | 1    | 70   | nA   |

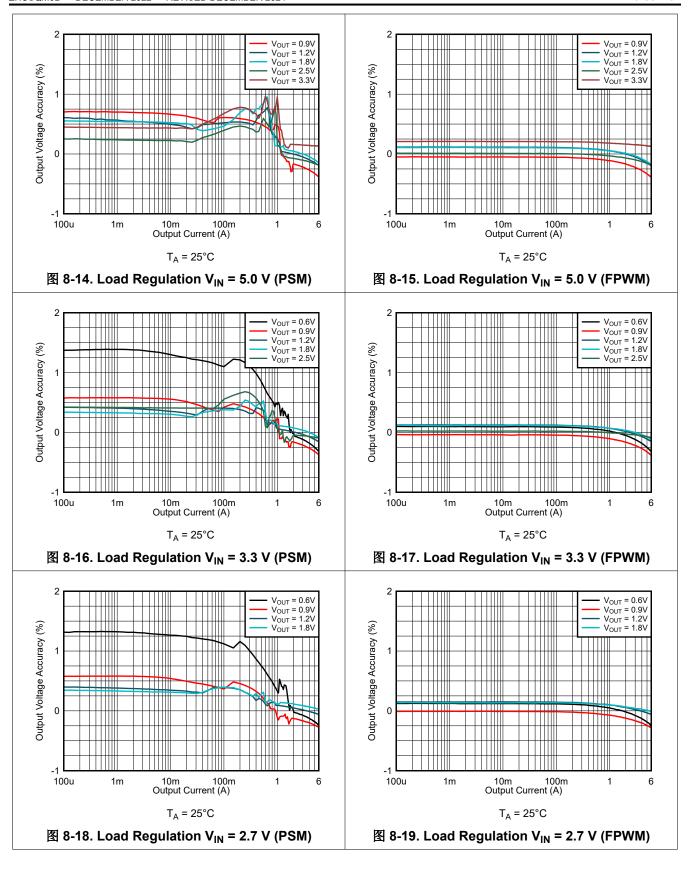

|                     | Load regulation                                 | PWM mode                                                                                                         |      | 0.05 |      | %/A  |

| R <sub>DIS</sub>    | Output discharge resistance                     |                                                                                                                  |      | 30   | 50   | Ω    |

| t <sub>on,min</sub> | Minimum on-time of high-side FET                | $V_{IN}\geqslant 3.3 \text{ V}$                                                                                  |      | 45   | 67   | ns   |

| R <sub>DP</sub>     | Dropout resistance TPSM82816SIE                 | 100% mode                                                                                                        |      | 27   |      | mΩ   |

| R <sub>DP</sub>     | Dropout resistance TPSM82814PVCA, TPSM82816PVCA | 100% mode                                                                                                        |      | 23   |      | mΩ   |

| I <sub>LIMH</sub>   | High-side FET switch current limit TPSM82814    | DC value, V <sub>IN</sub> = 3 V to 6 V                                                                           | 5.3  | 7.2  | 8.4  | Α    |

| I <sub>LIMH</sub>   | High-side FET switch current limit TPSM82816    | DC value, V <sub>IN</sub> = 3 V to 6 V                                                                           | 7.3  | 9.2  | 10.4 | Α    |

| I <sub>LIMNEG</sub> | Low-side FET negative current limit             | DC value, MODE/SYNC = high                                                                                       |      | - 3  |      | Α    |

*提交文档反馈* Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TPSM82816

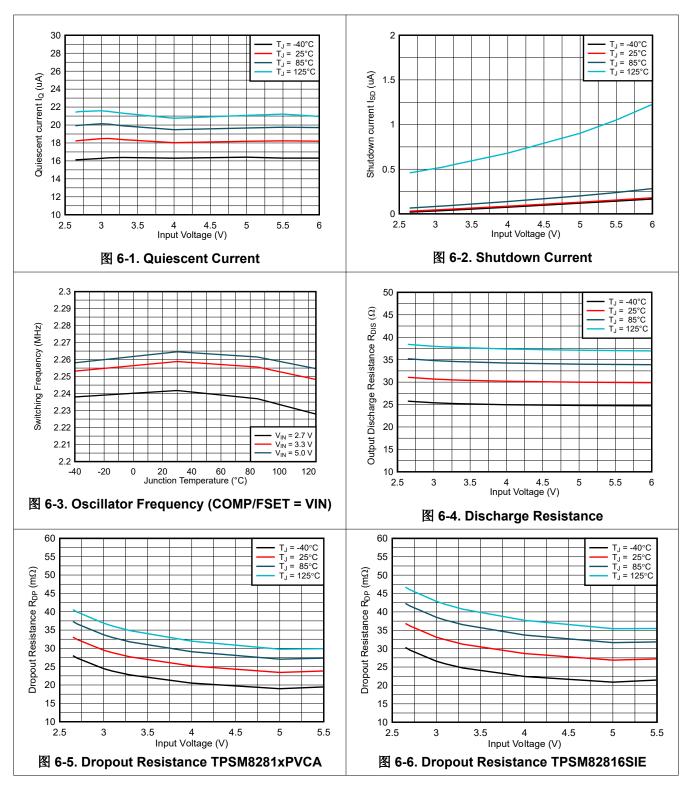

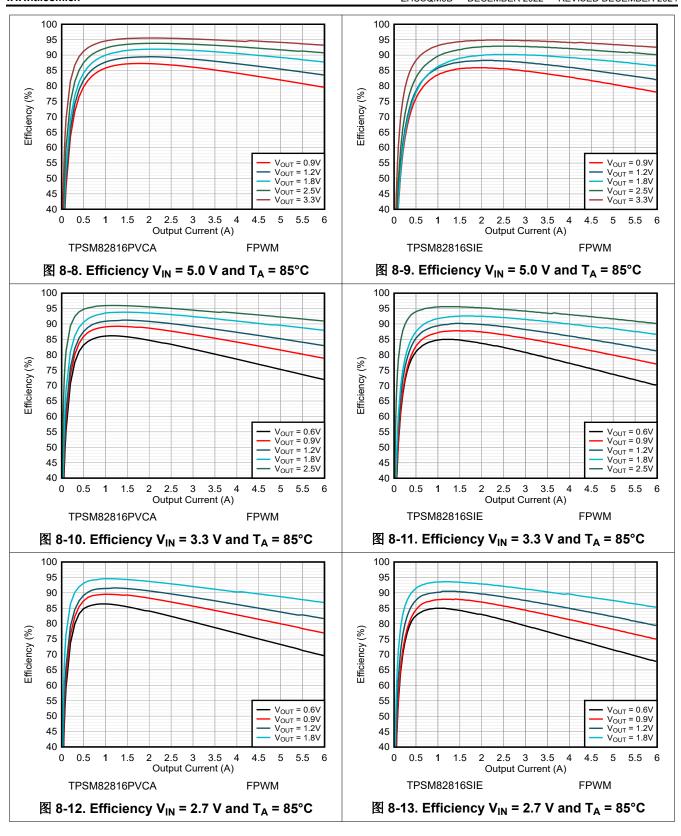

# **6.6 Typical Characteristics**

English Data Sheet: SLUSEY7

# 7 Detailed Description

#### 7.1 Overview

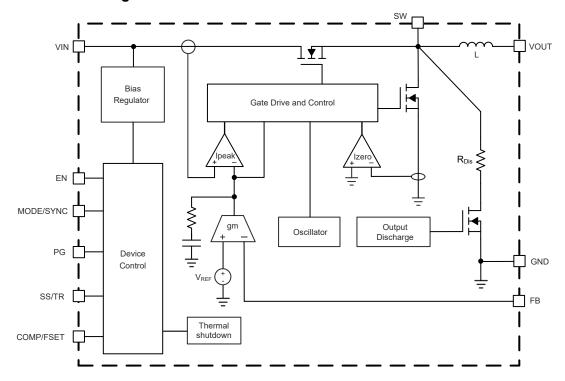

The TPSM8281x synchronous switch mode DC/DC converter power modules are based on a fixed-frequency peak current-mode control topology. The control loop is internally compensated. To optimize the bandwidth of the control loop to the wide range of output capacitance that can be used with the TPSM8281x, one of two internal compensation settings can be selected. See *COMP/FSET*. The compensation setting is selected either by a resistor from COMP/FSET to GND or by the logic state of this pin. The regulation network achieves fast and stable operation with small external components and low-ESR ceramic output capacitors.

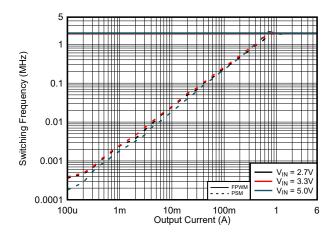

The device supports forced fixed frequency operation (FPWM) with the MODE/SYNC pin tied to a logic high level. The frequency is defined as either 2.25 MHz (internally fixed when COMP/FSET is tied to GND or VIN) or in a range of 1.8 MHz to 4 MHz (defined by a resistor from COMP/FSET to GND). Alternatively, the device can be synchronized to an external clock signal in a range from 1.8 MHz to 4 MHz, applied to the MODE/SYNC pin with no need for additional passive components. An internal PLL allows the device to change from internal clock to external clock during operation. The synchronization to the external clock is done on the falling edge of the clock applied at MODE/SYNC to the rising edge on the internal SW node. When the MODE/SYNC pin is set to a logic low level, the device operates in power save mode (PSM). At low output current, the device operates in PFM mode and automatically transitions to fixed-frequency PWM mode at higher output current. In PFM operation, the switching frequency decreases linearly based on the load to sustain high efficiency down to very low output current (see *Power Save Mode Operation (PSM)* for more details).

The TPSM8281xP versions in the VCA package use MagPack technology to deliver the highest-performance power module design. Leveraging our proprietary integrated-magnetics MagPack packaging technology, these power modules deliver industry-leading power density, high efficiency and good thermal performance, ease of use, and reduced EMI emissions.

#### 7.2 Functional Block Diagram

Product Folder Links: TPSM82816

#### 7.3 Feature Description

#### 7.3.1 Precise Enable (EN)

The TPSM8281x starts operation when the rising EN threshold is exceeded. For proper operation, the EN pin must be terminated and must not be left floating. Pulling the EN pin low forces the device into shutdown. In this mode, the internal high-side and low-side MOSFETs are turned off and the entire internal control circuitry is switched off. The voltage applied at the EN pin of the TPSM8281x is compared to a fixed threshold of 1.1 V for a rising voltage.

The enable input threshold for a falling edge is typically 100 mV lower than the rising edge threshold. The Precise Enable input provides a user-programmable undervoltage lockout by adding a resistor divider to the input of the EN pin. The Precise Enable input also allows you to drive the pin by a slowly changing voltage and enables the use of an external RC network to achieve a precise power-up delay. See the *Achieving a Clean Start-up by Using a DC/DC Converter with a Precise Enable-pin Threshold* analog design journal for more details.

#### 7.3.2 Output Discharge

The purpose of the discharge function is to make sure of a defined down-ramp of the output voltage when the device is being disabled, but also to keep the output voltage close to 0 V when the device is off. The output discharge feature is only active after the TPSM8281x has been enabled at least once since the supply voltage was applied. The discharge function is enabled as soon as the device is disabled, in thermal shutdown, or in undervoltage lockout. The minimum supply voltage required for the discharge function to remain active is typically 2 V. Output discharge is not activated during a current limit event.

#### 7.3.3 COMP/FSET

This pin allows the user to set three different parameters independently:

- Internal compensation settings for the control loop (two settings available)

- The switching frequency in PWM mode from 1.8 MHz to 4 MHz

- Enable / disable spread spectrum clocking (SSC)

A resistor from COMP/FSET to GND changes the compensation as well as the switching frequency. The change in compensation allows the user to adopt the device to different values of output capacitance. The resistor must be placed close to the pin to keep the parasitic capacitance on the pin to a minimum. The compensation setting is sampled at the start-up of the converter, so a change in the resistor during operation only has an effect on the switching frequency, but not on the compensation.

To save external components, the pin can also be directly tied to VIN or GND to set a pre-defined switching frequency or compensation. Do not leave the pin floating.

The switching frequency has to be selected based on the maximum input voltage in the application and the output voltage to meet the specifications for the minimum on time.

Example:  $V_{IN} = 5.5 \text{ V}$ ,  $V_{OUT} = 1 \text{ V}$

$$f_{Sw,max} = \frac{V_{OUT}}{V_{IN} \times t_{ON,min}} = \frac{1 V}{5.5 V \times 67 \, ns} = 2.71 \, MHz$$

(1)

The compensation range has to be chosen based on the effective minimum capacitance used. The capacitance can be increased from the minimum value as given in  $\frac{1}{8}$  7-1, up to the maximum of 470  $\mu F$  in both compensation ranges. If the capacitance of an output changes during operation, for example when load switches are used to connect or disconnect parts of the circuitry, the compensation has to be chosen for the minimum capacitance on the output. If the output capacitance exceeds 72  $\mu F \times V / VOUT[V]$ , use the second compensation setting to get the best load transient response. If the output capacitance only exceeds 32  $\mu F \times V / VOUT[V]$ , use the first compensation setting. Compensating for large output capacitance but having too little effective capacitance on the output can lead to instability.

Product Folder Links: TPSM82816

The switching frequency for the different compensation setting is determined by the following equations.

提交文档反馈

For compensation (comp) setting 1 with spread spectrum clocking (SSC) disabled:

$$R_{CF}\left[k\Omega\right] = \frac{18\,MHz \times k\Omega}{f_S[MHz]}\tag{2}$$

For compensation (comp) setting 1 with spread spectrum clocking (SSC) enabled:

$$R_{CF}\left[k\Omega\right] = \frac{60 \,MHz \times k\Omega}{f_S[MHz]} \tag{3}$$

For compensation (comp) setting 2 with spread spectrum clocking (SSC) disabled:

$$R_{CF}\left[k\Omega\right] = \frac{180 \ MHz \times k\Omega}{f_S[MHz]} \tag{4}$$

表 7-1. Switching Frequency and Compensation

| COMPENSATION                                                                                   | R <sub>CF</sub>         | SWITCHING FREQUENCY                                     | MINIMUM OUTPUT<br>CAPACITANCE    |

|------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------|----------------------------------|

|                                                                                                |                         |                                                         | CAPACITANCE                      |

| For smallest output capacitance (comp setting 1) SSC disabled                                  | 10 kΩ 4.5 kΩ            | 1.8 MHz (10 kΩ) 4 MHz (4.5 kΩ)<br>according to 方程式 2    | 32 μF × V / V <sub>OUT</sub> [V] |

| For smallest output capacitance (comp setting 1) SSC enabled                                   | 33 kΩ 15 kΩ             | 1.8 MHz (33 k Ω ) 4 MHz (15 k Ω )<br>according to 方程式 3 | 32 μF × V / V <sub>OUT</sub> [V] |

| For best transient response<br>(larger output capacitance)<br>(comp setting 2)<br>SSC disabled | 100 kΩ 45 kΩ            | 1.8 MHz (100 kΩ) 4 MHz (45 kΩ)<br>according to 方程式 4    | 72 µF × V / V <sub>OUT</sub> [V] |

| For smallest output capacitance (comp setting 1) SSC disabled                                  | Tied to GND             | Internally fixed 2.25 MHz                               | 32 μF × V / V <sub>OUT</sub> [V] |

| For best transient response<br>(larger output capacitance)<br>(comp setting 2)<br>SSC enabled  | Tied to V <sub>IN</sub> | Internally fixed 2.25 MHz                               | 72 µF × V / V <sub>OUT</sub> [V] |

The minimum output capacitance required for stability depends on the output voltage as stated in 表 7-1. Refer to *Output Capacitor* for further details on the output capacitance required depending on the output voltage.

A too-high resistor value for  $R_{CF}$  is decoded as "tied to  $V_{IN}$ " and a value below the lowest range is decoded as "tied to GND". The minimum output capacitance in  $\frac{1}{8}$  7-1 is for capacitors close to the output of the device. If the capacitance is distributed, a lower compensation setting can be required.

#### 7.3.4 MODE/SYNC

When MODE/SYNC is set low, the device operates in PWM or PFM mode, depending on the output current. The MODE/SYNC pin forces PWM mode when set high. The pin also allows you to apply an external clock in a frequency range from 1.8 MHz to 4 MHz for external synchronization. When an external clock is applied, the device only operates in PWM mode. As with the switching frequency selection, the specification for the minimum on-time has to be observed when applying the external clock signal. When using external synchronization, TI recommends to set the switching frequency (as set by R<sub>CF</sub>) to a similar value as the externally applied clock. This action makes sure that, if the external clock fails, the switching frequency stays in the same range and the settling time to the internal clock is reduced. When there is no resistor from COMP/FSET to GND, but the pin is pulled high or low, external synchronization is not possible. An internal PLL allows you to change from an internal clock to external clock during operation. The synchronization to the external clock is done on the falling edge of the applied clock to the rising edge of the internal SW pin (see *Synchronizing to an External Clock*). The MODE/SYNC pin can be changed during operation.

#### 7.3.5 Spread Spectrum Clocking (SSC)

The device offers spread spectrum clocking as an option, set by the COMP/FSET pin. When SSC is enabled, the switching frequency is randomly changed in PWM mode when the internal clock is used. The frequency variation is typically between the nominal switching frequency and up to 288 kHz above the nominal switching frequency. When the device is externally synchronized, the TPSM8281x follows the external clock and the internal spread spectrum block is turned off. SSC is also disabled during soft start.

#### 7.3.6 Undervoltage Lockout (UVLO)

If the input voltage drops, the undervoltage lockout prevents mis-operation of the device by switching off both the MOSFETs. The device is fully operational for voltages above the rising UVLO threshold and turns off if the input voltage goes below the falling threshold.

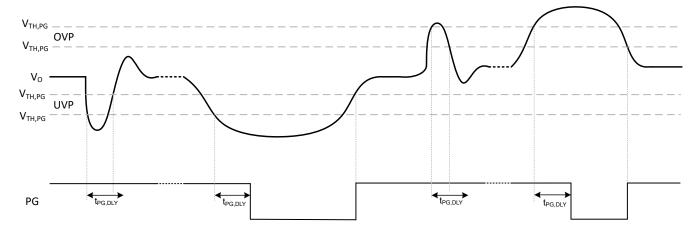

#### 7.3.7 Power-Good Output (PG)

The device has a power-good output with window comparator. The PG pin goes high impedance after the FB pin voltage is above 95% and less than 107% of the nominal voltage, and is driven low after the voltage falls below 90% or rises higher than 110% of the nominal voltage (typical). 表 7-2 shows the typical PG pin logic. The PG pin is an open-drain output and is specified to sink up to 2 mA. The power good output requires a pullup resistor connected to any voltage rail less than VIN. The PG signal can be used for sequencing of multiple rails by connecting to the EN pin of other converters. If not used, the PG pin can be left floating or connected to GND.

| ₹ 7-2.1 Ower-Good I III Logic |                                                                              |                 |     |  |  |

|-------------------------------|------------------------------------------------------------------------------|-----------------|-----|--|--|

| DE                            | VICE STATE                                                                   | PG LOGIC STATUS |     |  |  |

| DEVICE STATE                  |                                                                              | HIGH IMPEDANCE  | LOW |  |  |

|                               | $0.95 \times V_{FB\_NOM} \leqslant V_{FB} \leqslant 1.07 \times V_{FB\_NOM}$ | √               |     |  |  |

| Enabled (EN = High)           | $V_{FB}$ < 0.9 × $V_{FB\_NOM}$ or $V_{FB}$ > 1.1 × $V_{FB\_NOM}$             |                 | √   |  |  |

| Shutdown (EN = Low)           |                                                                              |                 | √   |  |  |

| UVLO                          | $2 \text{ V} \leqslant \text{V}_{\text{IN}} < \text{V}_{\text{UVLO}}$        |                 | √   |  |  |

| Thermal Shutdown              | $T_J > T_{JSD}$                                                              |                 | √   |  |  |

| Power Supply Removal          | V <sub>IN</sub> < 2 V                                                        | undefined       |     |  |  |

表 7-2. Power-Good Pin Logic

The PG pin has a 40-  $\mu$  s deglitch time on the falling edge. See  $\mathbb{Z}$  7-1.

图 7-1. Power-Good Transient and Delay Behavior

#### 7.3.8 Thermal Shutdown

The junction temperature  $(T_J)$  of the device is monitored by an internal temperature sensor. If  $T_J$  exceeds 180°C (typical), the device goes into thermal shutdown. Both the high-side and low-side power FETs are turned off and PG goes low. When  $T_J$  decreases below the hysteresis amount of typically 15°C, the converter resumes normal operation, beginning with soft start. During PFM the thermal shutdown is not active.

Product Folder Links: TPSM82816

#### 7.4 Device Functional Modes

#### 7.4.1 Pulse Width Modulation (PWM) Operation

The TPSM8281x have two operating modes: Forced PWM mode (FPWM) and Power Save Mode (PSM).

With the MODE/SYNC pin set to high, the TPSM8281x operates with pulse width modulation (PWM) in continuous conduction mode (CCM). The switching frequency is either defined by a resistor from the COMP/ FSET pin to GND or by an external clock signal applied to the MODE/SYNC pin.

With the MODE/SYNC pin set to low, the TPSM8281x operates with pulse frequency modulation (PFM) during light load and automatically transitions into PWM as the load current increases.

#### 7.4.2 Power Save Mode Operation (PSM)

When the MODE/SYNC pin is low, power save mode is allowed. The device operates in PWM mode as long as the peak inductor current is above the PFM threshold of about 1.8 A. When the peak inductor current drops below the PFM threshold, the device starts to skip switching pulses. The frequency set with the resistor on COMP/FSET must be in a range of 1.8 MHz to 3.5 MHz.

In power save mode, the switching frequency decreases linearly with the load current to maintain high efficiency. The linear behavior of the switching frequency in power save mode is shown in \ \ 7-2.

图 7-2. Switching Frequency versus Output Current ( $V_{OUT} = 1.8 \text{ V}$ ,  $R_{CF} = 10 \text{ k}\Omega$ )

#### 7.4.3 100% Duty-Cycle Operation

The device offers a low input-to-output voltage differential by entering 100% duty cycle mode. When the minimum off-time of typically 15 ns is reached, the TPSM8281x skips switching cycles while approaching 100% mode. In 100% mode, the high-side MOSFET switch is constantly turned on. The minimum input voltage to maintain a minimum output voltage is given by:

$$V_{IN(min)} = V_{OUT(min)} + I_{OUT} \times R_{DP}$$

(5)

where:

- R<sub>DP</sub> is the resistance from VIN to VOUT, which includes the high-side MOSFET on-resistance and DC resistance of the inductor

- V<sub>OUT(min)</sub> is the minimum output voltage the load can accept

This operation mode is particularly useful in battery-powered applications to achieve longest operation time by taking full advantage of the whole battery voltage range.

Product Folder Links: TPSM82816

#### 7.4.4 Current Limit and Short-Circuit Protection

The TPSM8281x is protected against overload and short circuit events. If the inductor current exceeds the current limit I<sub>LIMH</sub>, the high-side MOSFET is turned off and the low-side MOSFET is turned on to ramp down the inductor current. The high-side MOSFET turns on again only if the current in the low-side MOSFET has decreased below the low-side current limit. Due to internal propagation delays, the actual current can exceed the static current limit. The dynamic current limit is given as:

$$I_{peak (typ)} = I_{LIMH} + \frac{V_L}{L} \times t_{PD}$$

(6)

where

- · I<sub>LIMH</sub> is the static current limit, as specified in the electrical characteristics

- · L is the effective inductance

- SIE: typically 220 nH

- VCA (MagPack): typically 200 nH

- V<sub>L</sub> is the voltage across the inductor (V<sub>IN</sub> V<sub>OUT</sub>)

- t<sub>PD</sub> is the internal propagation delay of typically 50 ns

The dynamic peak current is calculated as follows:

$$I_{peak (typ)} = I_{LIMH} + \frac{V_{IN} - V_{OUT}}{L} \times 50 \text{ ns}$$

(7)

The low-side MOSFET also contains a negative current limit to prevent excessive current from flowing back through the inductor to the input. If the low-side sinking current limit is exceeded, the low-side MOSFET is turned off. In this scenario, both MOSFETs are off until the start of the next cycle. The negative current limit is only active in Forced PWM mode.

#### 7.4.5 Soft Start / Tracking (SS/TR)

The soft-start circuitry controls the output voltage slope during start-up. This action avoids excessive inrush current and makes sure of a controlled output voltage rise time. This action also prevents unwanted voltage drops from high impedance power sources or batteries. When EN is set high, the device starts switching after a delay of about 270  $\,\mu$  s. Then  $V_{OUT}$  rises with a slope controlled by an external capacitor connected to the SS/TR pin.

A capacitor connected from SS/TR to GND is charged with 10  $\mu$ A by an internal current source during soft start until it reaches the reference voltage of 0.6 V. After reaching 0.6 V, the SS/TR pin voltage is clamped internally while the SS/TR pin voltage keeps rising to a maximum of about 3.3 V. The capacitance required to set a certain ramp-time ( $t_{ramp}$ ) is:

$$C_{SS}[nF] = \frac{10\mu A \times t_{ramp}[ms]}{0.6 \, V} \tag{8}$$

Leaving the SS/TR pin disconnected provides the fastest start-up ramp of 150  $\mu$ s typically. If the device is set to shutdown (EN = GND), undervoltage lockout, or thermal shutdown, an internal resistor of about 1.1 k  $\Omega$  pulls the SS/TR pin to GND to make sure of a proper low level. Returning from those states causes a new start-up sequence.

A voltage applied at the SS/TR pin can also be used to track a controller voltage. The output voltage follows this voltage in both directions up and down in forced PWM mode. In PSM mode, the output voltage decreases based on the load current. An external voltage applied on SS/TR is internally clamped to the feedback voltage (0.6 V). TI recommends to set the final value of the external voltage on SS/TR to be slightly above 0.6 V to make sure the device operates with the internal reference voltage when the power-up sequencing is finished. See *Voltage Tracking*.

Product Folder Links: TPSM82816

# 8 Application and Implementation

#### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定 器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

#### 8.1 Application Information

The TPSM8281x are synchronous step-down converter power modules. The power inductor is integrated inside the module. The SIE package variant has a shielded inductor with an inductance of 220 nH ±20%.

The VCA MagPack package not only has a 200nH shielded Inductor but also shields the IC for a better EMI performance. With its smaller package size, it also offers a higher power density compared to the SIE package. The 4A and 6A versions in the VCA package give the same efficiency and performance and are different only in their rated output current. The efficiency of the VCA package is up to 4% higher than the SIE package.

The TPSM82813SIL (3A), TPSM82810SIL (4A), and TPSM82816SIE (6A) are pin-to-pin compatible with each other. The TPSM82811PVCA (1A), TPSM82812PVCA (2A), TPSM82813PVCA (3A), TPSM82814PVCA (4A), and TPSM82816PVCA (6A) are also pin-to-pin compatible with each other.

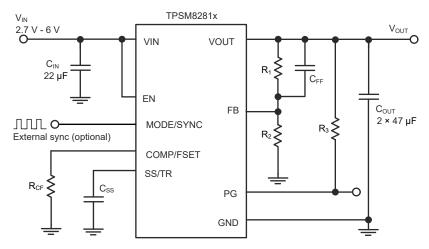

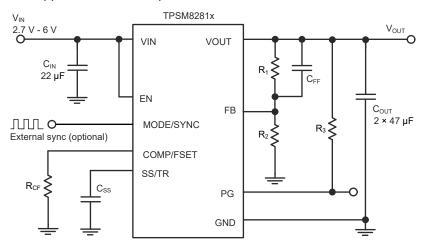

# 8.2 Typical Application

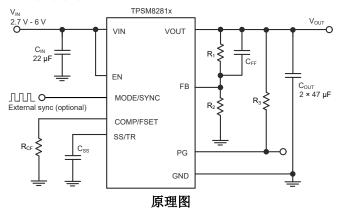

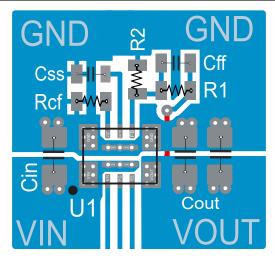

图 8-1. Typical Application Schematic

#### 8.2.1 Design Requirements

The design guidelines provide a component selection to operate the device within the recommended operating conditions.

REFERENCE **DESCRIPTION** MANUFACTURER (1) IC TPSM82816 Texas Instruments  $C_{IN}$  $22 \mu F / X7R / 6.3 V$ ; GRM21BZ1AJ226ME15L Murata  $C_{OUT}$  for  $V_{OUT}$  < 1 V  $3 \times 47 \,\mu\text{F} / X6S / 6.3 \,\text{V}; \, GRM21BC80J476ME01L$ Murata 2 × 47 µF / X6S / 6.3 V; GRM21BC80J476ME01L  $C_{OUT}$  for  $V_{OUT} \geqslant 1 \ V$ Murata  $C_{SS}$ 4.7 nF Any  $R_{CF}$ 10 k $\Omega$ Any  $C_{FF}$ 10 pF Any

Product Folder Links: TPSM82816

表 8-1. List of Components

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

表 8-1. List of Components (续)

| REFERENCE      | DESCRIPTION       | MANUFACTURER (1) |

|----------------|-------------------|------------------|

| R <sub>1</sub> | Depending on VOUT | Any              |

| R <sub>2</sub> | Depending on VOUT | Any              |

| R <sub>3</sub> | 100 kΩ            | Any              |

(1) See the Third-party Products Disclaimer.

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Setting the Output Voltage

The output voltage of the TPSM8281x is adjustable. Choose resistors R1 and R2 to set the output voltage within a range of 0.6 V to 5.5 V according to 方程式 9. To keep the feedback (FB) net robust from noise, set R2 equal to or lower than 100 k  $\Omega$  to have at least 6  $\mu$ A of current in the voltage divider. Lower values of FB resistors achieve better noise immunity, and lower light load efficiency, as explained in the *Design Considerations for a Resistive Feedback Divider in a DC/DC Converter* analog design journal.

$$R_1 = R_2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right) = R_2 \times \left(\frac{V_{OUT}}{0.6 V} - 1\right) \tag{9}$$

表 8-2. Examples for setting the Output Voltage

| A 0 2. Examples for Setting the Sutput Voltage |                 |                |                                                |                |  |  |  |  |  |  |

|------------------------------------------------|-----------------|----------------|------------------------------------------------|----------------|--|--|--|--|--|--|

| NOMINAL OUTPUT VOLTAGE V <sub>OUT</sub>        | R <sub>1</sub>  | R <sub>2</sub> | Max C <sub>FF</sub><br>at min C <sub>out</sub> | OUTPUT VOLTAGE |  |  |  |  |  |  |

| 0.8 V                                          | 16.9 k Ω        | 51 kΩ          | 15 pF                                          | 0.7988 V       |  |  |  |  |  |  |

| 1.0 V                                          | <b>20 k</b> Ω   | <b>30 k</b> Ω  | 13 pF                                          | 1.0 V          |  |  |  |  |  |  |

| 1.1 V                                          | 39.2 k Ω        | <b>47 k</b> Ω  | 6.8 pF                                         | 1.101 V        |  |  |  |  |  |  |

| 1.2 V                                          | <b>68 k</b> Ω   | 68 k Ω         | 3.9 pF                                         | 1.2 V          |  |  |  |  |  |  |

| 1.5 V                                          | <b>76.8 k</b> Ω | 51 kΩ          | 3.3 pF                                         | 1.5 V          |  |  |  |  |  |  |

| 1.8 V                                          | 80.6 k Ω        | 40.2 k Ω       | 3.3 pF                                         | 1.803 V        |  |  |  |  |  |  |

| 2.5 V                                          | 47.5 k Ω        | 15 k Ω         | 5.6 pF                                         | 2.5 V          |  |  |  |  |  |  |

| 3.3 V                                          | 88.7 kΩ         | 19.6 k Ω       | 3 pF                                           | 3.315 V        |  |  |  |  |  |  |

#### 8.2.2.2 Feedforward Capacitor

A feedforward capacitor ( $C_{FF}$ ) is required in parallel with  $R_1$  to improve the transient response. The maximum value for the feedforward capacitor  $C_{FF}$  at the minimum output capacitance is determined by 方程式 10:

$$C_{ff, max}\left[nF\right] = \frac{266.1 \, nF \times \Omega}{R_1} \tag{10}$$

For examples of feedforward capacitor values for common output voltages when using the minimum required output capacitance, refer to  $\frac{1}{8}$  8-2.

To improve the load transient performance, more output capacitance can be added. Increasing the  $C_{FF}$  above values given by 方程式 10 can also improve the response with larger  $C_{OUT}$ . The converter's loop response must be evaluated either through a simple load step or by a phase margin measurement. For details, please refer to: *AN-1733 Load Transient Testing Simplified application note*.

#### 8.2.2.3 Input Capacitor

For most applications, TI recommends a 22-µF nominal ceramic capacitor. The input capacitor buffers the input voltage for transient events and also decouples the converter from the supply. A X7R or X7T multilayer ceramic capacitor (MLCC) is recommended for best filtering and must be placed between VIN and GND as close as possible to those pins. For applications with ambient temperatures below 85°C, a capacitor with X5R dielectric

Product Folder Links: TPSM82816

can be used. Ceramic capacitors have a DC-Bias effect, which has a strong influence on the final effective capacitance. Choose the right capacitor carefully in combination with considering the package size and voltage rating. The minimum required input capacitance is 5 µF.

#### 8.2.2.4 Output Capacitor

The architecture of the TPSM8281x allows the use of ceramic output capacitors which have low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended. To keep the low resistance up to high frequencies and to get a narrow capacitance variation with temperature, TI recommends to use an X7R or X7T dielectric. At temperatures below 85°C, an X5R dielectric can be used.

Using a higher capacitance value has advantages like smaller voltage ripple and a tighter DC output accuracy in power save mode. By changing the device compensation with a resistor from COMP/FSET to GND, the device can be compensated in two steps based on the minimum capacitance used on the output. The maximum capacitance is 470 µF in any of the compensation settings. The minimum capacitance required on the output depends on the compensation setting and output voltage as shown in 表 7-1. For output voltages below 1 V, the minimum required capacitance increases linearly from 32 µF at 1 V to 53 µF at 0.6 V with the compensation setting for smallest output capacitance. The other compensation setting scales the same. Ceramic capacitors have a DC-Bias effect, which has a strong influence on the final effective capacitance. Choose the right capacitor carefully in combination with considering the package size and voltage rating.

提交文档反馈

19

English Data Sheet: SLUSEY7

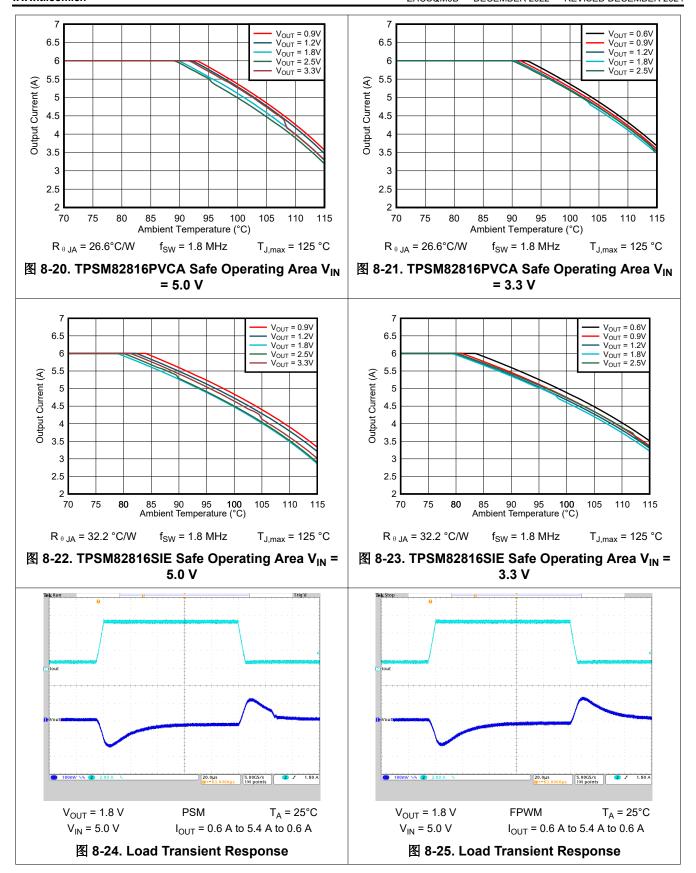

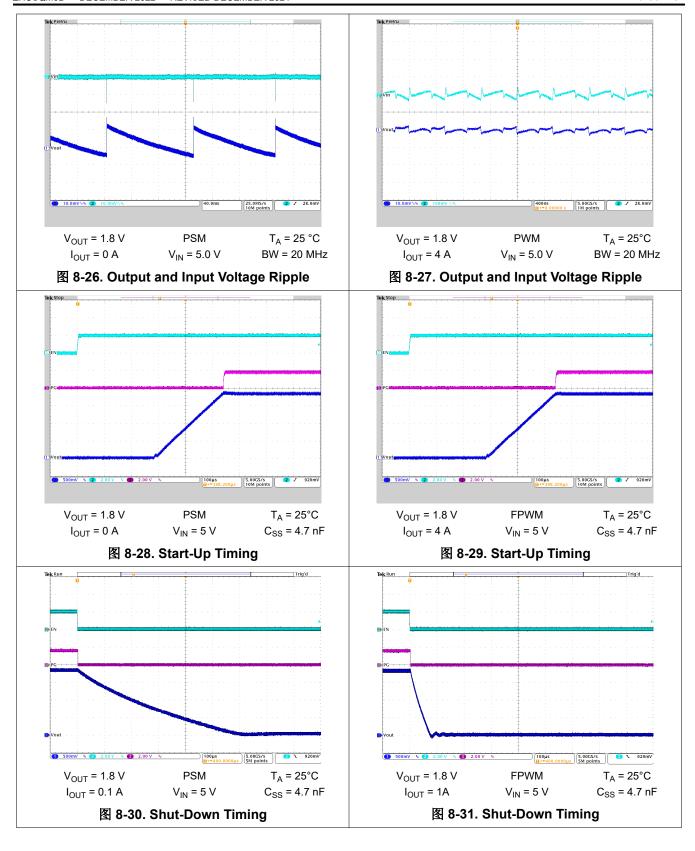

#### 8.2.3 Application Curves

$T_A = 25$ °C,  $V_{IN} = 5$  V,  $V_{OUT} = 1.8$  V, 1.8 MHz, PWM mode, BOM =  $\frac{1}{8}$  8-1 unless otherwise noted.

Product Folder Links: TPSM82816

20 提交文档反馈

# www.ti.com.cn

Product Folder Links: TPSM82816

Product Folder Links: TPSM82816

#### 8.3 System Examples

#### 8.3.1 Voltage Tracking

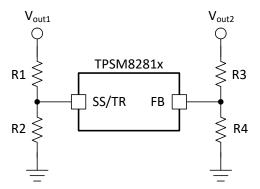

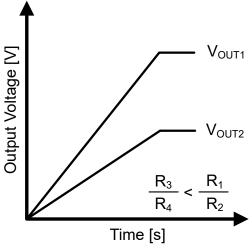

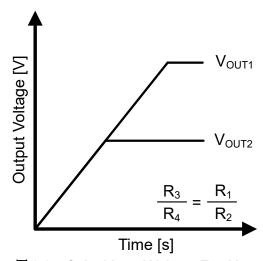

The SS/TR pin is externally driven by another voltage source to achieve output voltage tracking. The application circuit is shown in 8-32. From 0 V to 0.6 V, the internal reference voltage to the internal error amplifier follows the SS/TR pin voltage. When the SS/TR pin voltage is above 0.6 V, the voltage tracking is disabled and the FB pin voltage is regulated at 0.6 V. The device achieves ratiometric, as shown in 8-33 or coincidental (simultaneous) output tracking, as shown in 8-33.

The  $R_2$  value must be set properly to achieve accurate voltage tracking by taking the 10-  $\mu$  A charging current into account. 1 k $\Omega$  or smaller is a sufficient value for  $R_2$ . For decreasing SS/TR pin voltage, the device does not sink current from the output when the device is in PSM. The resulting decrease of the output voltage can be slower than the SS/TR pin voltage if the load is light.

In case both devices need to run in forced PWM mode after start-up, TI recommends to tie the MODE/SYNC pin of the secondary device to the output voltage or the power-good signal of the primary device. The TPSM8281x has a duty cycle limitation defined by the minimum on time, which can cause the secondary device to not track when the output voltage is very low. Delaying FPWM mode until the output voltage is higher operates the device in PSM mode, with improved tracking at very low output voltages

When driving the SS/TR pin with an external voltage, do not exceed the voltage rating of the SS/TR pin.

图 8-32. Schematic for Output Voltage Tracking

图 8-34. Coincidental Voltage Tracking

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

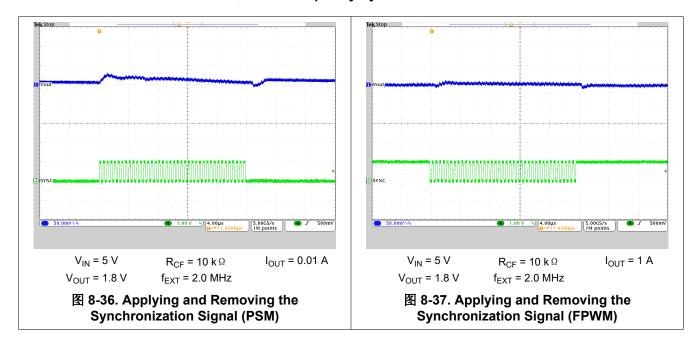

#### 8.3.2 Synchronizing to an External Clock

The TPSM8281x can be synchronized by applying a clock on the MODE/SYNC pin. There is no need for any additional circuitry as long as the input signal meets the requirements given in the electrical specifications. See 8-35. The clock can be applied, changed, and removed during operation. TI recommends the value of the R<sub>CF</sub> resistor be chosen such that the internally defined frequency and the externally-applied frequency are close to each other to have a fast settling time to the external clock. Synchronizing to a clock is not possible if the COMP/FSET pin is connected to Vin or GND. 8-36 and 8-37 show the external clock being applied and removed. When an external clock is applied, the device operates in PWM mode.

图 8-35. Frequency Synchronization

#### 8.4 Power Supply Recommendations

The TPSM8281x device family has no special requirements for the input power supply. The output current of the input power supply must be rated according to the supply voltage, output voltage, and output current of the TPSM8281x.

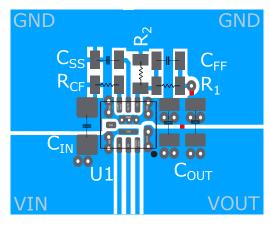

#### 8.5 Layout

#### 8.5.1 Layout Guidelines

A proper layout is critical for the operation of any switched mode power supply, especially at high switching frequencies. Therefore, the PCB layout of the TPSM8281x demands careful attention to make sure of best performance. A poor layout can lead to issues like bad line and load regulation, instability, increased EMI radiation, and noise sensitivity. Refer to the *Five Steps to a Great PCB Layout for a Step-Down Converter* analog design journal for a detailed discussion of general best practices. Specific recommendations for the device are listed below.

- Place the input capacitor as close as possible to the VIN and GND pins of the device. This placement is the most critical component placement. Route the input capacitor directly to the VIN and GND pins avoiding vias.

- Place the output capacitor ground close to the VOUT and GND pins and route directly avoiding vias.

- Place the FB resistors, R1 and R2, and the feedforward capacitor C<sub>FF</sub> close to the FB pin and place C<sub>SS</sub> close to the SS/TR pin to minimize noise pickup.

- Place the R<sub>CF</sub> resistor close to the COMP/FSET pin to minimize the parasitic capacitance.

- Note that the recommended layout is implemented on the EVM and shown in the *TPSM8281xEVM-089*Evaluation Module EVM user's guide, MagPack™ Technology 3A/6A Power Module with Frequency Sync

Evaluation Module EVM user's guide, and in Layout Example.

- Note that the recommended land pattern for the TPSM8281x is shown at the end of this data sheet. For best

manufacturing results, create the pads as solder mask defined (SMD), when some pins (such as VIN, VOUT,

and GND) are connected to large copper planes. Using SMD pads keeps each pad the same size and avoids

solder pulling the device during reflow.

#### 8.5.2 Layout Example

图 8-38. Example Layout VCA

图 8-39. Example Layout SIE

#### 8.5.2.1 Thermal Consideration

The TPSM8281x module temperature must be kept less than the maximum rating of 125°C. The following are three basic approaches for enhancing thermal performance:

- Improve the power dissipation capability of the PCB design

- Improve the thermal coupling of the component to the PCB

- · Introduce airflow into the system

To estimate the approximate module temperature of the TPSM8281x, apply the typical efficiency stated in this data sheet to the desired application condition to compute the power dissipation of the module. Then, calculate the module temperature rise by multiplying the power dissipation by the thermal resistance. For more details on how to use the thermal parameters in real applications, see the application notes: *Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs* and *Semiconductor and IC Package Thermal Metrics*.

The thermal values in *Thermal Information* used the recommended land pattern, shown at the end of this data sheet, including the vias as shown. The TPSM8281x was simulated on a PCB defined by JEDEC 51-7. For the SIE package, the vias on the GND pins were connected to copper on other PCB layers, while the remaining vias were not connected to other layers.

# 9 Device and Documentation Support

# 9.1 Device Support

#### 9.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

#### 9.2 Documentation Support

#### 9.2.1 Related Documentation

For related documentation see the following:

- Texas Instruments, TPSM8281xEVM-089 Evaluation Module EVM user's guide

- Texas Instruments, MagPack™ Technology 3A/6A Power Module with Frequency Sync Evaluation Module EVM user's guide

- Texas Instruments, Achieving a Clean Start-up by Using a DC/DC Converter with a Precise Enable-pin analog design journal

- Texas Instruments, Design Considerations for a Resistive Feedback Divider in a DC/DC Converter analog design journal

- Texas Instruments, AN-1733 Load Transient Testing Simplified application report

- Texas Instruments, Five Steps to a Great PCB Layout for a Step-Down Converter analog design journal

- Texas Instruments, Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs application note

# 9.3 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*通知* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 9.4 支持资源

TI E2E<sup>™</sup> 中文支持论坛是工程师的重要参考资料,可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题,获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的使用条款。

#### 9.5 Trademarks

MicroSIP<sup>™</sup>, and MagPack<sup>™</sup>, and TI E2E<sup>™</sup> are trademarks of Texas Instruments. 所有商标均为其各自所有者的财产。

#### 9.6 静电放电警告

Copyright © 2024 Texas Instruments Incorporated

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 9.7 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

Product Folder Links: TPSM82816

# 10 Revision History

注:以前版本的页码可能与当前版本的页码不同

| Changes from Revision A (June 2024) to Revision B (December 2024) | Page |

|-------------------------------------------------------------------|------|

| • 将 TPSM82816PVCAR 从"预告信息"更改为"量产数据"                               | 1    |

|                                                                   |      |

| Changes from Revision * (December 2022) to Revision A (June 2024) | Page |

| • 向数据表添加了 TPSM82814PVCAR (产品预发布)和 TPSM82816PVCAR (预告信息)           | 1    |

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

> Copyright © 2024 Texas Instruments Incorporated Product Folder Links: TPSM82816

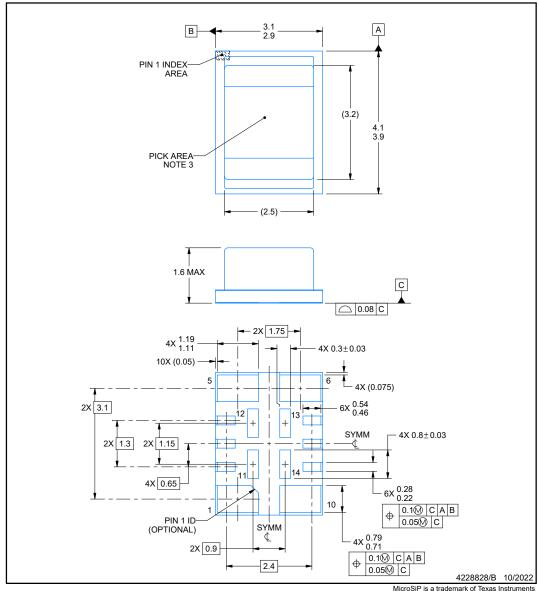

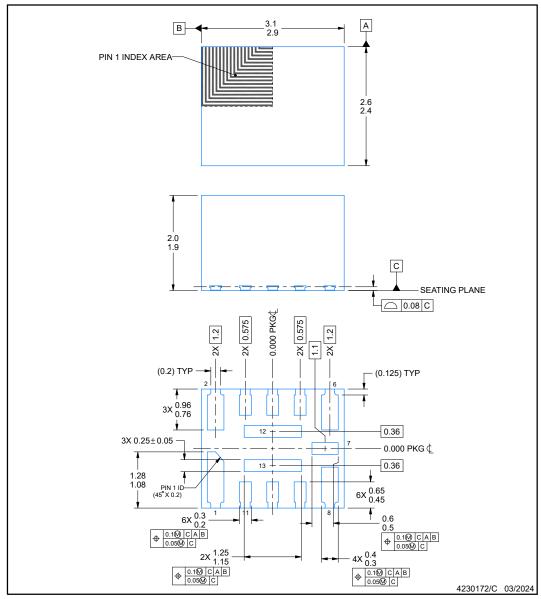

# SIE0014A-C01

# **PACKAGE OUTLINE**

uSIP™ - 1.6 mm max height

MICRO SYSTEM IN PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Pick and place nozzle Ø 1.3 mm or smaller recommended.

4. The package thermal pads must be soldered to the printed circuit board for thermal and mechanical performance.

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

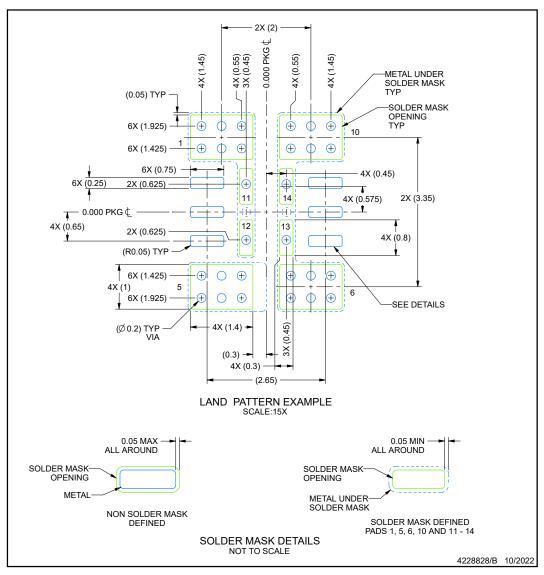

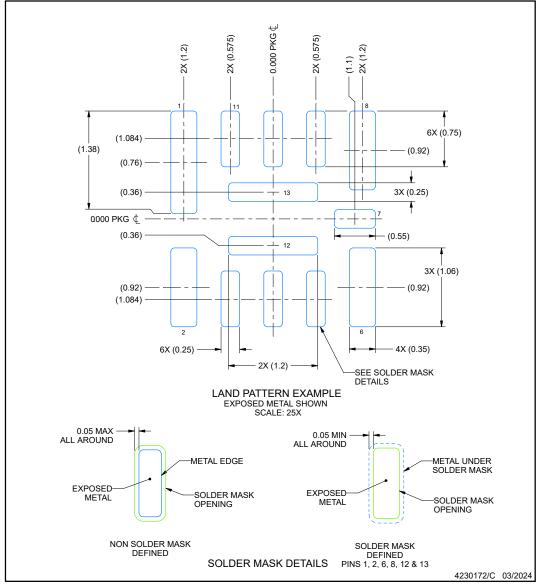

#### **EXAMPLE BOARD LAYOUT**

# SIE0014A-C01

#### uSIP™ - 1.6 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

- 5. This package is designed to be soldered to thermal pads on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 6. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

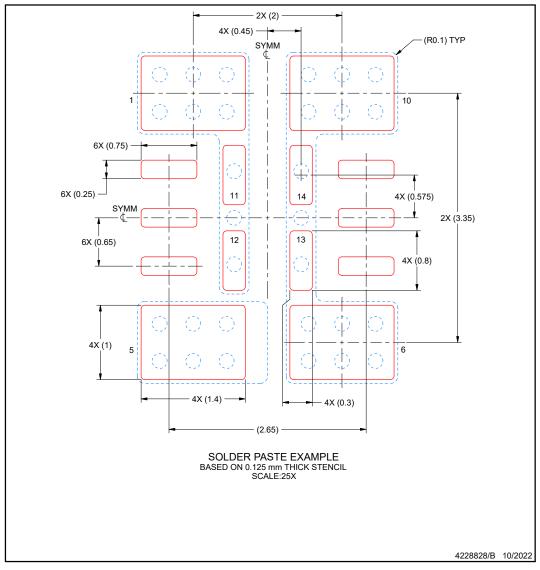

# **EXAMPLE STENCIL DESIGN**

# SIE0014A-C01

### uSIP™ - 1.6 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate

Product Folder Links: TPSM82816

# **PACKAGE OUTLINE**

# **VCA0013A**

# QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

#### **EXAMPLE BOARD LAYOUT**

# **VCA0013A**

#### QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271)

Product Folder Links: TPSM82816

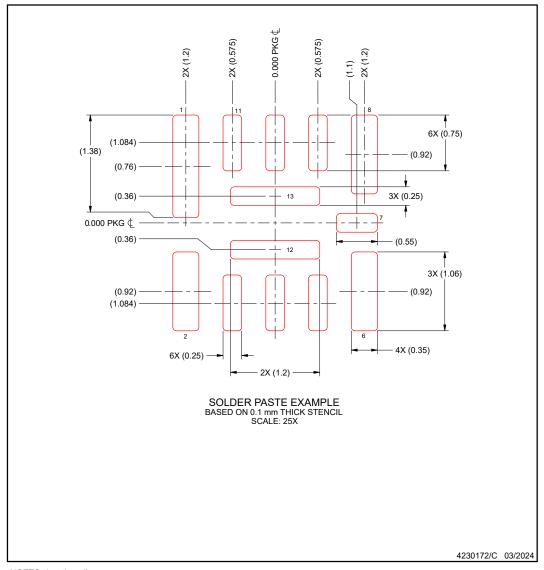

# **EXAMPLE STENCIL DESIGN**

# **VCA0013A**

#### QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

www.ti.com 8-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins          | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                         |                       |      | (4)                           | (5)                        |              |                  |

| TPSM82816PVCAR        | Active | Production    | QFN-FCMOD<br>(VCA)   13 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | ЗНСІ             |

| TPSM82816PVCAR.A      | Active | Production    | QFN-FCMOD<br>(VCA)   13 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | ЗНСІ             |

| TPSM82816SIER         | Active | Production    | uSiP (SIE)   14         | 3000   LARGE T&R      | Yes  | NIAU                          | Level-2-260C-1 YEAR        | -40 to 125   |                  |

| TPSM82816SIER.A       | Active | Production    | uSiP (SIE)   14         | 3000   LARGE T&R      | Yes  | NIAU                          | Level-2-260C-1 YEAR        | -40 to 125   |                  |

| XPSM82816PVCAR        | Active | Preproduction | QFN-FCMOD<br>(VCA)   13 | 2500   LARGE T&R      | -    | Call TI                       | Call TI                    | -40 to 125   |                  |

| XPSM82816PVCAR.A      | Active | Preproduction | QFN-FCMOD<br>(VCA)   13 | 2500   LARGE T&R      | -    | Call TI                       | Call TI                    | -40 to 125   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 8-Nov-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

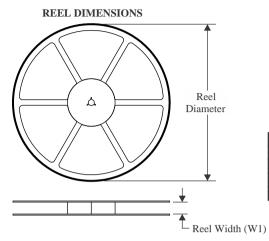

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jun-2025

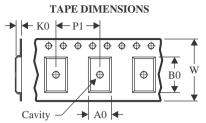

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

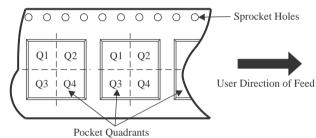

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPSM82816PVCAR | QFN-<br>FCMOD   | VCA                | 13 | 2500 | 330.0                    | 12.4                     | 3.3        | 2.8        | 2.2        | 8.0        | 12.0      | Q1               |

| TPSM82816SIER  | uSiP            | SIE                | 14 | 3000 | 178.0                    | 13.2                     | 3.27       | 4.07       | 1.78       | 8.0        | 12.0      | Q1               |

www.ti.com 24-Jun-2025

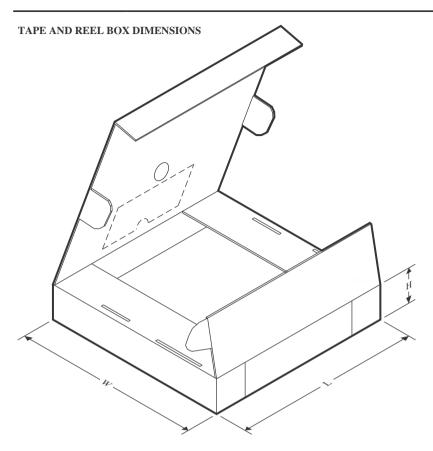

# \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPSM82816PVCAR | QFN-FCMOD    | VCA             | 13   | 2500 | 367.0       | 367.0      | 35.0        |

| TPSM82816SIER  | uSiP         | SIE             | 14   | 3000 | 383.0       | 353.0      | 58.0        |

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月