TPSM5D1806E

ZHCSP41 - JANUARY 2022

# TPSM5D1806E 工作温度范围为 -55°C 至 +125°C 的 4.5V 至 15V 输入、双路 6A/ 单路 12A 输出电源模块

# 1 特性

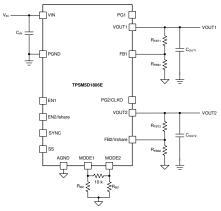

- 独立双路 6A 输出

- 并行单路 12A 输出

- 输出电压范围: 0.5V 至 5.5V

- 0.5V,温度范围内的电压基准精度为 ±1.25%

- 具有相位延迟的频率同步

- 针对每个输出的独立使能和电源正常指示功能

- 启动至预偏置输出

- UV 和 OV 电源正常输出

- 可选开关频率选项:

500kHz、1.0MHz、1.5MHz 和 2.0MHz

- 符合 EN55011 辐射 EMI 限值

- 工作结温范围: -55°C 至 +125°C

- 工作环境温度范围:-55°C 至 +105°C

- 8mm × 5.5mm × 1.8mm 标准 QFN 封装

- 使用 TPSM5D1806E 并借助 WEBENCH® Power Designer 创建定制设计方案

# 2 应用

- 支持航天和国防

- 医疗成像

- 加固型通信

- 航电设备和飞机控制

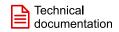

双路输出简化版原理图

# 3 说明

TPSM5D1806E 双路 6A 输出电源模块是一款灵活的高 度集成直流/直流电源,采用紧凑型 8mm × 5.5mm × 1.8mm QFN 封装。输入电压范围为 4.5 V 至 15 V, 因 此可对宽电压范围的中间总线以及标准 5V 和 12V 电 压轨进行电压转换。两个 6A 输出可以针对两个单独的 电源轨分别配置,也可以合并为一个两相 12A 输出。

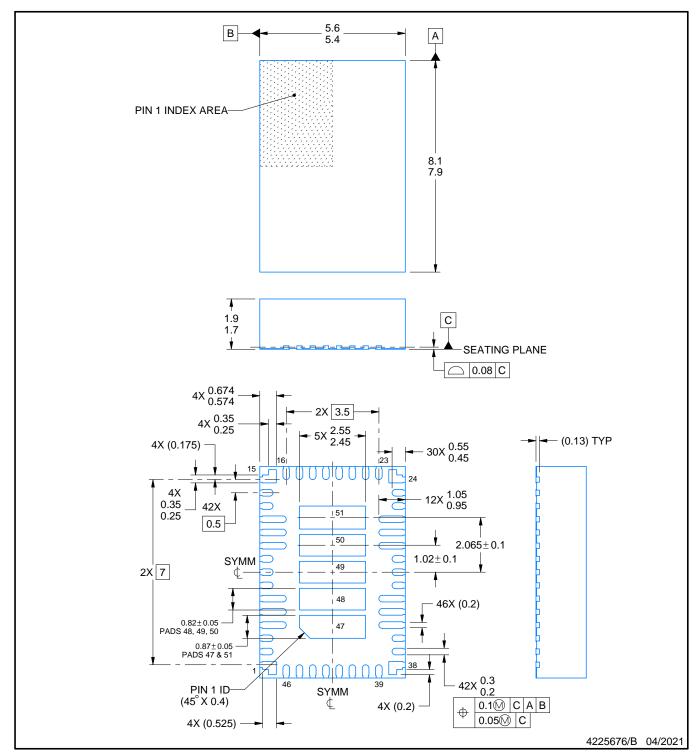

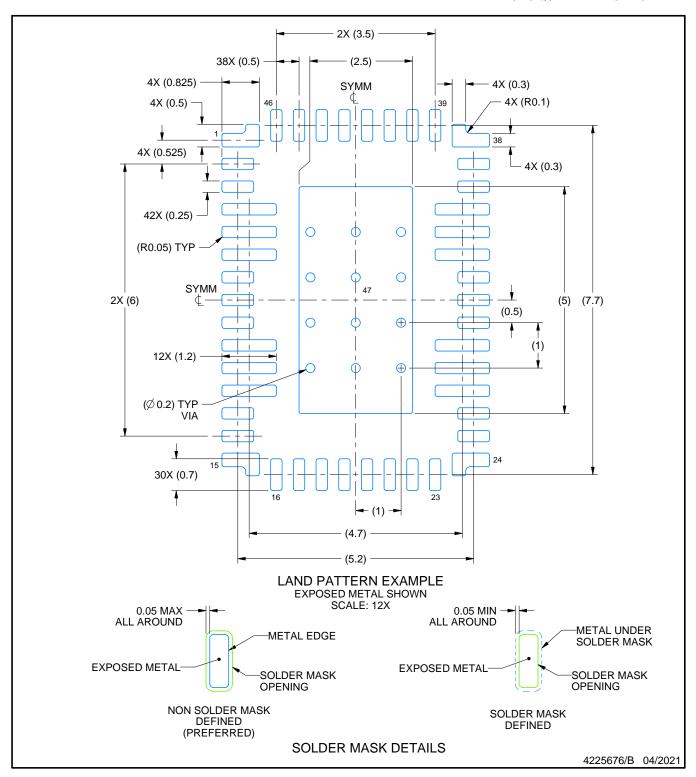

具有出色封装布局的低厚度 51 引脚 QFN 封装可提高 热性能。-55°C 的增强温度性能可实现外部机舱安装 模块或飞行控制单元等环境中的航天应用。该封装的所 有信号引脚均分布在外围,器件下方有一些大型散热焊 盘,可在制造过程中实现简单布局和轻松处理。

集成的电源设计省去了设计流程中的环路补偿和磁性元 件选型。该器件可为每路输出提供独立的使能控制和电 源正常信号。开关频率和相位偏移可以使用引脚束带进 行配置。该器件还提供了过流和热关断保护。

#### 器件信息

| 器件型号        | 封装 <sup>(1)</sup> | 封装尺寸(标称值)           |

|-------------|-------------------|---------------------|

| TPSM5D1806E | QFN               | 8mm × 5.5mm × 1.8mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

# **Table of Contents**

| 1 特性                                                 | 1 | 7.4 Device Functional Modes             | <mark>2</mark> 1 |

|------------------------------------------------------|---|-----------------------------------------|------------------|

| 2 应用                                                 |   | 8 Application and Implementation        | <mark>22</mark>  |

|                                                      |   | 8.1 Application Information             | <u>22</u>        |

| 4 Revision History                                   |   | 8.2 Typical Application (Dual Outputs)  | <mark>22</mark>  |

| 5 Pin Configuration and Functions                    |   | 9 Power Supply Recommendations          | <mark>27</mark>  |

| 6 Specifications                                     |   | 10 Layout                               | 28               |

| 6.1 Absolute Maximum Ratings                         |   | 10.1 Layout Guidelines                  | 28               |

| 6.2 ESD Ratings                                      |   | 10.2 Layout Examples                    | 28               |

| 6.3 Recommended Operating Conditions                 |   | 11 Device and Documentation Support     | <mark>31</mark>  |

| 6.4 Thermal Information                              |   | 11.1 Device Support                     | <mark>31</mark>  |

| 6.5 Electrical Characteristics                       |   | 11.2 接收文档更新通知                           | 31               |

| 6.6 Typical Characteristics (V <sub>IN</sub> = 12 V) | 8 | 11.3 支持资源                               | 31               |

| 6.7 Typical Characteristics (V <sub>IN</sub> = 5 V)  |   | 11.4 Trademarks                         | 31               |

| 7 Detailed Description                               |   | 11.5 Electrostatic Discharge Caution    | 31               |

| 7.1 Overview                                         |   | 11.6 术语表                                | 31               |

| 7.2 Functional Block Diagram                         |   | 12 Mechanical, Packaging, and Orderable |                  |

| 7.3 Feature Description                              |   | Information                             | 32               |

| •                                                    |   |                                         |                  |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| January 2022 | *        | Initial release |

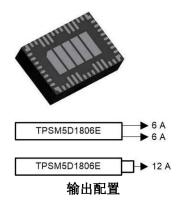

# **5 Pin Configuration and Functions**

图 5-1. 51-Pin RDB QFN Package (Top View)

表 5-1. Pin Functions

| Pin        | Pin          |                     | Decariation                                                                                                                                                                                                                                                                                                 |  |

|------------|--------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name       | No.          | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                 |  |

| AGND       | 42, 43       | G                   | Analog ground for the internal analog control circuit. Connect to PGND at one single point, away from noisy circuitry.                                                                                                                                                                                      |  |

| BP5        | 44           | 0                   | Output of the internal 5-V regulator. Bypass this pin with a minimum of 1.5 µF of effective capacitance to AGND. Can be used as a pullup voltage for PGOOD signals.                                                                                                                                         |  |

| DNC        | 7, 8, 31, 32 | _                   | Do not connect. Do not connect these pins to AGND, PGND, to another DNC pin, or to any other voltage. These pins are connected to internal circuitry. Each pin must be soldered to an isolated pad.                                                                                                         |  |

| EN1        | 1            | I                   | Channel 1 enable input. Float or pull high to enable. Can also be used to externally adjust EN UVLO by connecting a resistor divider between VIN and AGND.                                                                                                                                                  |  |

| EN2/ISHARE | 46           | I/O                 | Multi-function pin Dual output configuration: Channel 2 enable input. Float or pull high to enable. Can also be used to externally adjust EN UVLO by connecting resistor divider between VIN and AGND. Parallel output configuration: Current balance node of the internal regulators. Leave this pin open. |  |

| FB1        | 40           | I                   | Channel 1 feedback input. Connect to the output voltage of channel 1 with a resistor divider.                                                                                                                                                                                                               |  |

# 表 5-1. Pin Functions (continued)

| Pin         |                                 | <b>T</b> (1)        | B                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------|---------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name No.    |                                 | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                      |  |

| FB2/VSHARE  | 45                              | I/O                 | Multi-function pin Dual output configuration: Channel 2 Feedback input. Connect to the output voltage of channel 2 with a resistor divider. Parallel output configuration: The COMP voltage of the internal regulators. Leave this pin open.                                                                                                                                                     |  |

| MODE1       | 37                              | I                   | Mode setting pin. Programs channel configuration as either dual or parallel outputs and programs channel interleaving using a resistor between the MODE1 pin and AGND. A 10-k $\Omega$ resistor is required between the MODE1 pin and MODE2 pin.                                                                                                                                                 |  |

| MODE2       | 38                              | 1                   | Mode setting pin. Select from four pre-set switching frequencies using a resistor between the MODE2 pin and AGND. A 10-k $\Omega$ resistor is required between MODE1 pin and MODE2 pin.                                                                                                                                                                                                          |  |

| PGND        | 10 - 12,<br>27 - 29,<br>47 - 51 | G                   | Power ground of the device. This is the return current path for the power stage of the device. Connect these pins to the bypass capacitors associated with VIN and VOUT. Connect pads 47, 48, 49, 50, and 51 to the PCB ground planes using multiple vias for optimal thermal performance. All pins must be connected together externally with a copper plane or pour directly under the device. |  |

| PGOOD1      | 3                               | 0                   | Channel 1 power-good indicator output. This pin is an open-drain output, which asserts low during any fault condition. When used, a pullup resistor to BP5 or other external supply is required. Leave this pin open if unused.                                                                                                                                                                  |  |

| PGOOD2/CLKO | 2                               | 0                   | Multi-function pin  Dual output configuration: Channel 2 power-good indicator output. This pin is an open-drain output, which asserts low during any fault condition. When used, a pullup resistor to BP5 or another external supply is required. Leave this pin open if unused.  Parallel output configuration: 180° clock output. Leave this pin open if unused.                               |  |

| RS -        | 41                              | G                   | For parallel output applications, this pin functions as remote sense negative input to the differential amplifier. Connect this pin to the point of ground regulation using a kelvin trace. For dual output configurations, this pin must be tied to AGND.                                                                                                                                       |  |

| SS          | 39                              | I                   | External soft start when configured for parallel output operation. Place a capacitor from SS to AGND to set output voltage rise time. For independent dual channel configurations, leave this pin open.                                                                                                                                                                                          |  |

| SW1         | 30                              | 0                   | Channel 1 power stage switch node. Can be used to monitor the switch node.                                                                                                                                                                                                                                                                                                                       |  |

| SW2         | 9                               | 0                   | Channel 2 power stage switch node. Can be used to monitor the switch node.                                                                                                                                                                                                                                                                                                                       |  |

| SYNC        | 36                              | ı                   | This pin synchronizes to external clock or the CLKO pin of another device.                                                                                                                                                                                                                                                                                                                       |  |

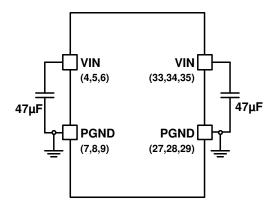

| VIN         | 4 - 6, 33 -<br>35               | I                   | Power conversion input pins. Pins 4, 5, and 6 are not internally connected to pins 33, 34, and 35. Connection must be made using the PCB VIN plane. Bypass VIN pins with ceramic capacitance to PGND, close to the device.                                                                                                                                                                       |  |

| VOUT1       | 20 - 26                         | 0                   | Channel 1 output voltage. These pins are connected to the internal output inductor. Connect to the output load. Place external bypass capacitors between these pins and PGND.                                                                                                                                                                                                                    |  |

| VOUT2       | 13 - 19                         | 0                   | Channel 2 output voltage. These pins are connected to the internal output inductor. Connect to the output load. Place external bypass capacitors between these pins and PGND.                                                                                                                                                                                                                    |  |

(1) G = Ground, I = Input, O = Output

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                      |                                                                                    | MIN   | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------|-------|-----|------|

|                      | VIN                                                                                | - 0.3 | 16  |      |

| Input voltage        | BP5, EN1, EN2/ISHARE, FB1, FB2/VSHARE, MODE1, MODE2, PGOOD1, PGOOD2/CLKO, SS, SYNC | - 0.3 | 6   | V    |

|                      | RS - , PGND to AGND                                                                | - 0.3 | 0.3 |      |

|                      | VOUT1, VOUT2                                                                       | - 0.3 | 6   |      |

| Output voltage       | SW1, SW2                                                                           | - 0.3 | 16  | V    |

|                      | SW1, SW2 transient (10ns)                                                          | - 3   | 18  |      |

| T <sub>J</sub>       | Operating IC junction temperature                                                  | - 55  | 125 | °C   |

| T <sub>stg</sub>     | Storage temperature                                                                | - 55  | 125 | °C   |

|                      | Peak reflow case temperature                                                       |       | 260 | °C   |

|                      | Maximum number or reflows allowed                                                  |       | 3   |      |

| Mechanical shock     | Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted                             |       | 500 | G    |

| Mechanical vibration | Mil-STD-883D, Method 2007.2, 20 to 2000 Hz                                         |       | 20  | G    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |               |                                                                             | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2500 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup>       | ±1000 | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                        | MIN                | NOM MAX | UNIT |

|------------------|----------------------------------------|--------------------|---------|------|

| V <sub>IN</sub>  | Input voltage                          | 4.5 <sup>(2)</sup> | 15      | V    |

| V <sub>OUT</sub> | Output voltage                         | 0.5                | 5.5     | V    |

| I <sub>OUT</sub> | Output current per channel, continuous |                    | 6       | Α    |

| V <sub>EN</sub>  | EN voltage                             | 0                  | 5.5     | V    |

| $V_{PGOOD}$      | PGOOD pull-up voltage                  |                    | 5.5     | V    |

| T <sub>A</sub>   | Operating ambient temperature          | - 55               | 125     | °C   |

<sup>(1)</sup> Recommended operating conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications, see the *Electrical Characteristics* table.

<sup>(2)</sup> See the Minimum Input Voltage section for the recommended minimum input voltage at higher output voltages.

#### 6.4 Thermal Information

|                   |                                                  | TPSM5D1806 |      |

|-------------------|--------------------------------------------------|------------|------|

|                   | THERMAL METRIC <sup>(1)</sup>                    | RDB (QFN)  | UNIT |

|                   |                                                  | 51 PINS    |      |

| R <sub>0</sub> JA | Junction-to-ambient thermal resistance (2)       | 13.9       | °C/W |

| $\Psi_{JT}$       | Junction-to-top characterization parameter (3)   | 1.8        | °C/W |

| Ψ ЈВ              | Junction-to-board characterization parameter (4) | 9.4        | °C/W |

| T <sub>SHDN</sub> | Thermal Shutdown Temperature                     | 165        | °C   |

| T <sub>SHDN</sub> | Thermal Shutdown Hysteresis                      | 20         | °C   |

- (1) For more information about thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

- (2) The junction-to-ambient thermal resistance, R  $_{\theta$  JA, applies to devices soldered directly to a 100 mm × 100 mm, 6-layer PCB with 2 oz. copper and natural convection cooling. Additional airflow reduces R  $_{\theta}$  JA.

- (3) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (section 6 and 7). T<sub>J</sub> = ψ<sub>JT</sub> × Pdis + T<sub>T</sub>; where Pdis is the power dissipated in the device and T<sub>T</sub> is the temperature of the top of the device.

- (4) The junction-to-board characterization parameter, Ψ<sub>JB</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7). T<sub>J</sub> = Ψ<sub>JB</sub> × Pdis + T<sub>B</sub>; where Pdis is the power dissipated in the device and T<sub>B</sub> is the temperature of the board 1 mm from the device.

#### 6.5 Electrical Characteristics

Limits apply over  $T_A = -55^{\circ}\text{C}$  to +125°C,  $V_{\text{IN}} = 12 \text{ V}$  (unless otherwise noted); Minimum and maximum limits are specified through production test or by design. Typical values represent the most likely parametric norm and are provided for reference only.

|                        | PARAMETER                            | TEST CONDITIONS                                                                                      | MIN                | TYP  | MAX              | UNIT   |

|------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------|--------------------|------|------------------|--------|

| INPUT VOLTA            | AGE (VIN)                            |                                                                                                      |                    |      |                  |        |

| V <sub>IN</sub>        | Operating input voltage range        |                                                                                                      | 4.5 <sup>(1)</sup> |      | 15               | V      |

| UVLO                   | V <sub>IN</sub> turn on              | V <sub>IN</sub> increasing                                                                           | 3.5                | 3.7  | 3.9              | V      |

| UVLO                   | Hysteresis                           |                                                                                                      |                    | 200  |                  | mV     |

| IQ                     | Quiescent current                    | Non-switching, V <sub>FB1</sub> , V <sub>FB2</sub> > 0.5 V, T <sub>A</sub> = 25°C, EN1 = EN2 = 5 V   |                    | 4    |                  | mA     |

| I <sub>SHDN</sub>      | Shutdown supply current              | T <sub>A</sub> = 25°C, EN1 = EN2 = 0 V                                                               |                    | 270  |                  | μΑ     |

| INTERNAL LI            | DO (BP5)                             |                                                                                                      |                    |      |                  |        |

| BP5                    | Regulation voltage                   | $6 \text{ V} \leqslant \text{V}_{\text{IN}} \leqslant 15 \text{ V}, \text{ I}_{\text{LOAD}}$ = 70 mA | 4.8                | 5.0  | 5.2              | V      |

| FEEDBACK               |                                      |                                                                                                      |                    |      |                  |        |

|                        | Feedback voltage                     | T <sub>J</sub> = 25°C                                                                                |                    | 0.5  |                  | V      |

| V V                    | Temperature accuracy                 | T <sub>J</sub> = -55°C to 125°C                                                                      | - 1.25%            |      | +1.25%           |        |

| $V_{(FB1)}, V_{(FB2)}$ | Load regulation                      | T <sub>A</sub> = +25°C, over I <sub>OUT</sub> range                                                  |                    | 0.2% |                  |        |

|                        | Line regulation                      | T <sub>A</sub> = +25°C, I <sub>OUT</sub> = 0 A, over V <sub>IN</sub> range                           |                    | 0.1% |                  |        |

| OUTPUT CU              | RRENT                                |                                                                                                      |                    |      |                  |        |

|                        | Output current                       | Per channel                                                                                          | 0                  |      | 6 <sup>(2)</sup> | Α      |

| I <sub>OUT</sub>       | Overcurrent threshold source current | DC current                                                                                           |                    | 6.6  |                  | Α      |

|                        | Overcurrent threshold sink current   | DC current                                                                                           |                    | -2.8 |                  | Α      |

|                        | 0.4-4                                | I <sub>OUT</sub> ≥ 3 A per channel                                                                   |                    | 15%  |                  |        |

| I <sub>SH(acc)</sub>   | Output current sharing accuracy      | I <sub>OUT</sub> < 3 A per channel                                                                   |                    | 1    |                  | Α      |

|                        | OCP hiccup wait time                 | Wait time to attempt re-start                                                                        |                    | 7    |                  | ms     |

|                        | OCP hiccup entry time                | Cycles before hiccup                                                                                 |                    | 16   |                  | cycles |

Product Folder Links: TPSM5D1806E

# **6.5 Electrical Characteristics (continued)**

Limits apply over  $T_A = -55^{\circ}\text{C}$  to +125°C,  $V_{IN} = 12 \text{ V}$  (unless otherwise noted); Minimum and maximum limits are specified through production test or by design. Typical values represent the most likely parametric norm and are provided for reference only.

| only.                 | PARAMETER                                         | TEST CONDITIONS                                            | MIN    | TYP   | MAX   | UNIT   |

|-----------------------|---------------------------------------------------|------------------------------------------------------------|--------|-------|-------|--------|

| SOFT STAR             |                                                   | TEST CONDITIONS                                            | Milia  |       | WAX   | Olviii |

|                       |                                                   | Time from awitching to DCOOD high without C                |        | 1     |       |        |

| t <sub>SS</sub>       | Default soft-start time                           | Time from switching to PGOOD high without C <sub>SS</sub>  |        |       |       | ms     |

| I <sub>SS</sub>       | Soft-start charge current                         | $T_{SS} \leqslant 50 \text{ ms}, C_{SS} < 0.3 \mu\text{F}$ |        | 2     |       | μA     |

| Rss                   | Soft-start discharge resistance                   |                                                            |        | 600   |       | Ω      |

| ENABLE (E             | N)                                                |                                                            |        |       |       |        |

|                       | Enable threshold voltage                          | EN rising                                                  |        | 1.2   | 1.3   | V      |

| $V_{EN}$              |                                                   | EN falling                                                 | 1      | 1.1   |       | V      |

|                       | Hysteresis on Enable                              |                                                            |        | 100   |       | mV     |

|                       | Enable pullup current                             | EN floating                                                |        | 1.4   |       | μA     |

|                       | Enable to start switching time                    | VIN ≥ 4.5 V, toggle EN                                     |        | 0.3   |       | ms     |

| SWITCH NO             | DDE (SW)                                          |                                                            |        |       |       |        |

|                       | SW1, SW2 Discharge FET                            |                                                            |        | 32    |       | Ω      |

|                       | SW1, SW2 minimum on time                          |                                                            |        | 40    | 50    | ns     |

|                       | SW1, SW2 minimum off time                         |                                                            |        | 150   | 200   | ns     |

| SWITCHING             | FREQUENCY                                         |                                                            |        |       | '     |        |

|                       | Fsw1                                              | MODE2 resistor = 10.7 k Ω                                  | 450    | 500   | 550   | kHz    |

|                       | Fsw2                                              | MODE2 resistor = 17.4 k Ω                                  | 900    | 1000  | 1100  | kHz    |

|                       | Fsw3                                              | MODE2 resistor = 28.7 k Ω                                  | 1350   | 1500  | 1650  | kHz    |

|                       | Fsw4                                              | MODE2 resistor = 53.6 k $\Omega$                           | 1800   | 2000  | 2200  | kHz    |

| SYNCHRON              | IIZATION (SYNC)                                   | MODEL TOOLSON CO.O K                                       |        |       |       |        |

|                       | High-level input                                  |                                                            | 2      |       |       | V      |

| V <sub>IH(SYNC)</sub> | Low-level input                                   |                                                            |        |       | 0.6   | V      |

| V <sub>IL(sync)</sub> | · · · · · · · · · · · · · · · · · · ·             |                                                            | 20%    |       | 80%   | v      |

|                       | Input duty cycle                                  |                                                            | 2076   |       | 60%   |        |

|                       | Sync frequency versus internal oscillator setting |                                                            | -20%   |       | +20%  |        |

| CLOCK OU              | TPUT (CLKO)                                       |                                                            |        |       |       |        |

| V <sub>OH(CLKO)</sub> | High-level output                                 | Ι <sub>Ο</sub> = 20 μΑ                                     | 2.2    |       |       | V      |

| V <sub>OL(CLKO)</sub> | Low-level output                                  | Ι <sub>0</sub> = 20 μΑ                                     |        |       | 0.4   | V      |

| 02(02:10)             | Pulse width output                                |                                                            |        | 80    |       | ns     |

| POWER GO              | OOD WARNING (PGOOD1, PGOOD2)                      |                                                            |        |       |       |        |

|                       |                                                   | V <sub>FB1</sub> , V <sub>FB2</sub> falling (warning)      | 87%    | 90%   | 93%   |        |

|                       |                                                   | V <sub>FB1</sub> , V <sub>FB2</sub> rising (good)          | 90%    | 93%   | 96%   |        |

|                       | PGOOD thresholds                                  | V <sub>FB1</sub> , V <sub>FB2</sub> falling (good)         | 104%   | 107%  | 110%  |        |

| PGOOD                 |                                                   | V <sub>FB1</sub> , V <sub>FB2</sub> rising (warning)       | 107%   | 110%  | 113%  |        |

| . 0000                | PGOOD leakage current                             | V <sub>PGOOD</sub> = 5.5 V                                 | 107 70 | 11070 | 11370 | μA     |

|                       | PGOOD leakage current                             | BP5 = 5 V, I <sub>PGOOD</sub> = 6mA                        |        |       | 0.5   | V      |

|                       | ·                                                 |                                                            |        |       |       |        |

| OUTDUT                | Minimum VIN for asserted output                   | $V_{PGOOD} \le 0.5 \text{ V}, I_{PGOOD} = 1 \text{ mA}$    |        |       | 1.5   | V      |

| OUIPUI UI             | NDERVOLTAGE AND OVERVOLTAGE                       |                                                            |        | 4000/ | Г     |        |

|                       | OV fault threshold                                | V <sub>FB1</sub> , V <sub>FB2</sub> rising (fault)         |        | 120%  |       |        |

|                       | UV fault threshold                                | V <sub>FB1</sub> , V <sub>FB2</sub> falling (fault)        |        | 80%   |       |        |

<sup>(1)</sup> See the Minimum and Maximum Input Voltage section for the recommended minimum input voltage at higher output voltages.

<sup>(2)</sup> See Safe Operating Area plots in the *Typical Characteristics* sections of the data sheet.

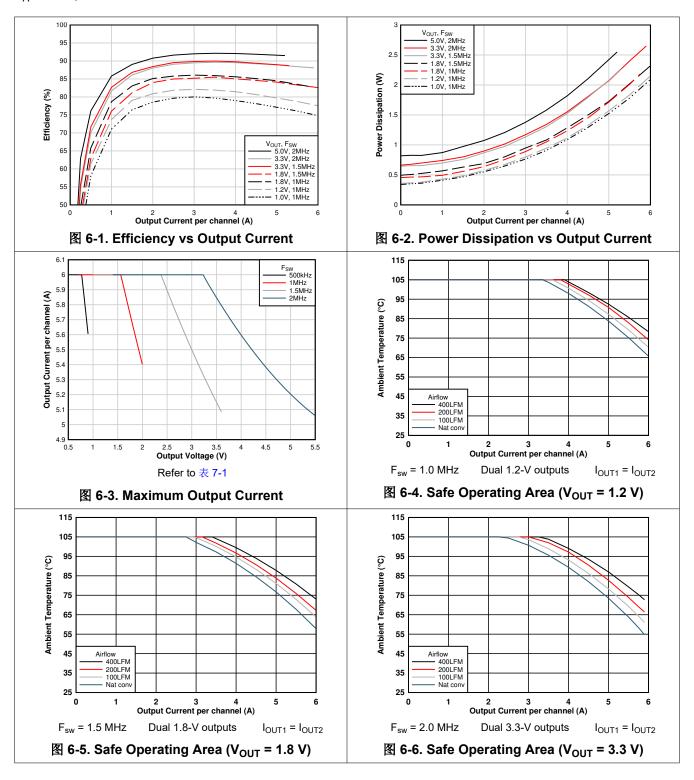

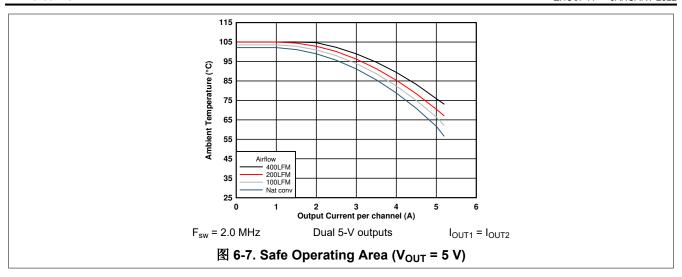

# 6.6 Typical Characteristics ( $V_{IN} = 12 \text{ V}$ )

$T_A = 25$ °C, unless otherwise noted

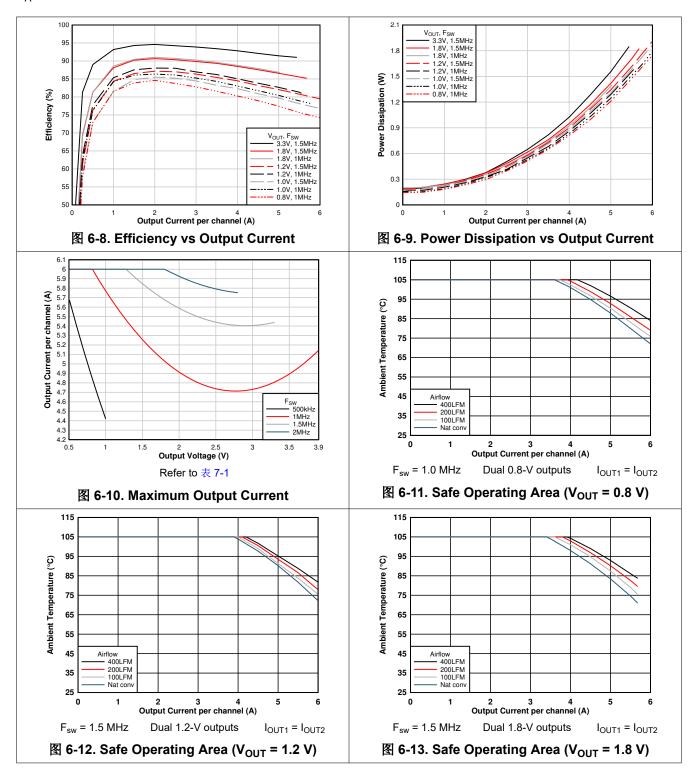

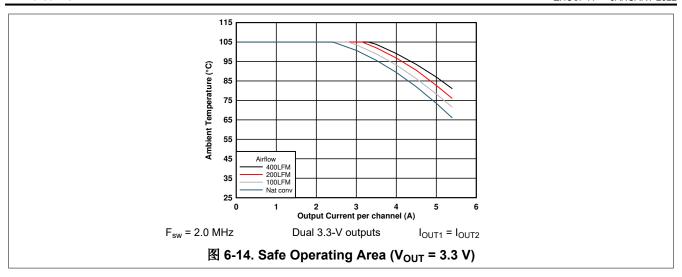

# 6.7 Typical Characteristics (V<sub>IN</sub> = 5 V)

T<sub>A</sub> = 25°C unless otherwise noted

# 7 Detailed Description

## 7.1 Overview

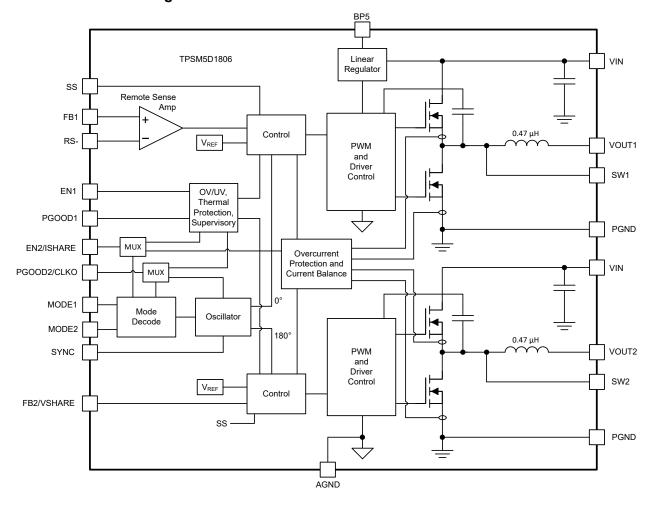

The TPSM5D1806E device is a dual output, step-down DC-DC power module with 4.5-V to 15-V input voltage range. Each device has two output channels and is capable of delivering up to 6-A of load current per channel. The device features exceptional efficiency and thermal performance in a very small solution size. The device is configurable as two independent 6-A outputs or a single 2-phase output to deliver up to 12 A. The TPSM5D1806E uses a fixed frequency, proprietary advanced current mode control architecture. The device operates in forced PWM (FPWM) operation to maintain constant switching frequency over the load range. The device is internally compensated, which reduces design time and requires fewer external components. The switching frequency and the phase operation are configured using pin strapping. The MODE1 pin sets the phase operation. 表 7-4 shows the resistor values that are required to set the phase operation and the correct phase offset. The switching frequency can be selected from pre-set values of 500 kHz, 1.0 MHz, 1.5 MHz, and 2.0 MHz through pin-strapping on the MODE2 pin. The TPSM5D1806E is also capable of synchronization to an external clock. The four switching frequency options allow the device to meet a wide range of design requirements. The module also features the following:

- · Power-good (PGOOD) flag for each channel

- · Precision enable for each channel

- · Internal or adjustable soft-start rate

- Start-up into pre-bias voltage

The device has a pinout designed for simple, optimum PCB layout, low EMI, and excellent thermal performance.

# 7.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 7.3 Feature Description

#### 7.3.1 Adjustable Output Voltage

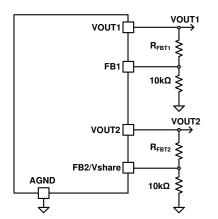

When operating the TPSM5D1806E as a dual output device, the two output voltages (VOUT1 and VOUT2) are set using resistor dividers between the output voltages and AGND with the mid-point of the resistor divider connecting to the corresponding feedback pin (FB1 and FB2). See 8 7-4.

Select a bottom feedback resistor of 10 k $\Omega$  and calculate the value for the top feedback resistor (R<sub>FBT</sub>) using the following equation. Use divider resistors with 1% tolerance or better and with a temperature coefficient of 100 ppm or lower.

$$R_{FBT} = 20 \times (V_{OUT} - 0.5)(k\Omega)$$

(1)

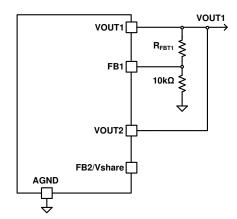

When connecting the two outputs of the TPSM5D1806E for current sharing, the output voltage is set using only a single feedback divider connected to FB1. The FB pin of the second channel, FB2, must be left floating as shown in  $\[ \]$  7-2. Use  $\[ \]$   $\[ \]$  1 to calculate the  $\[ \]$   $\[ \]$   $\[ \]$  1.

图 7-2. Single Device, Current Sharing

#### 7.3.2 Frequency Selection

The TPSM5D1806E can be set to one of four switching frequencies:

- 500 kHz

- 1.0 MHz

- 1.5 MHz

- 2.0 MHz

The switching frequency is set using the MODE2 pin on the device. When setting the switching frequency, both channels of the device are set to the same frequency. Not all input voltage and output voltage combinations can operate at all switching frequencies. Check  $\frac{1}{8}$  7-1 for allowable switching frequencies. Select the appropriate resistor from  $\frac{1}{8}$  7-5 to set the switching frequency.

#### 7.3.2.1 Synchronization

The TPSM5D1806E can also be synchronized to an external clock that is within ±20% of the switching frequency set by the MODE2 pin. The external clock signal can be applied to the SYNC pin before or after powering up. When the device is synchronized to an external clock signal, if the clock signal is removed, the device transitions to an intermediate frequency, which is 75% of the programmed frequency for approximately eight clock cycles. After eight clock cycles, the device transitions to the switching frequency set by the MODE2 pin.

# 7.3.2.2 Allowable Switching Frequency

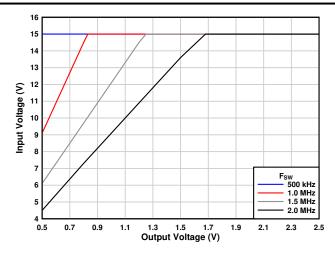

The TPSM5D1806E can be operated over a wide input voltage range with a wide output voltage setting range and at four selectable switching frequencies. However, not all input voltage, output voltage, and switching frequency combinations can be achieved due to timing and current limitations.

When setting the switching frequency, both channels of the device are set to the same frequency. When operating in dual output configuration, make sure that both channels can be operated at the desired switching frequency by referencing 表 7-1.

| 表 7-1. Allowable | Switching | Frequency |

|------------------|-----------|-----------|

|------------------|-----------|-----------|

| 2 1 17 mondate differently |           |                   |       |                        |      |  |  |  |

|----------------------------|-----------|-------------------|-------|------------------------|------|--|--|--|

|                            | Switching | V <sub>IN</sub> : | = 5 V | V <sub>IN</sub> =      | 12 V |  |  |  |

| Output Current per Channel | Frequency | V <sub>OUT</sub>  | Range | V <sub>OUT</sub> Range |      |  |  |  |

|                            | (kHz)     | Min               | Max   | Min                    | Max  |  |  |  |

|                            | 500       | _                 | _     | 0.5                    | 0.8  |  |  |  |

| 6 A                        | 1000      | 0.5               | 0.8   | 0.7                    | 1.6  |  |  |  |

| 0 A                        | 1500      | 0.5               | 1.3   | 1.0                    | 2.4  |  |  |  |

|                            | 2000      | 0.6               | 1.8   | 1.4                    | 3.2  |  |  |  |

|                            | 500       | 0.5               | 0.8   | 0.5                    | 0.9  |  |  |  |

| 5 A                        | 1000      | 0.5               | 1.8   | 0.7                    | 2.0  |  |  |  |

| JA                         | 1500      | 0.5               | 3.3   | 1.0                    | 3.6  |  |  |  |

|                            | 2000      | 0.6               | 2.8   | 1.4                    | 5.5  |  |  |  |

|                            | 500       | 0.5               | 0.9   | 0.5                    | 0.9  |  |  |  |

| ≤ 4 A                      | 1000      | 0.5               | 3.9   | 0.7                    | 2.0  |  |  |  |

|                            | 1500      | 0.5               | 3.5   | 1.0                    | 3.6  |  |  |  |

|                            | 2000      | 0.6               | 2.8   | 1.4                    | 5.5  |  |  |  |

## 7.3.3 Minimum and Maximum Input Voltage

The minimum input voltage of the TPSM5D1806E is 4.5 V, however, the minimum recommended input voltage increases at higher output voltages. Refer to  $\frac{1}{8}$  7-2 to determine the minimum recommended input voltage for each switching frequency. Also reference  $\frac{1}{8}$  7-1 to ensure that the output voltage can be operated at the selected switching frequency. Control the turn ON and turn OFF of the device at an input voltage greater than the minimum using a resistor divider on the EN1 (EN2) pin between VIN and AGND (see  $\frac{1}{1}$  7.3.10).

表 7-2. Minimum Input Voltage

| •                         | •                                           |

|---------------------------|---------------------------------------------|

| Switching Frequency (kHz) | Minimum Input Voltage                       |

| 500                       | 4.5 V                                       |

| 1000                      | 4.5 V or VOUT × 1.3 (whichever is greater)  |

| 1500                      | 4.5 V or VOUT × 1.6 (whichever is greater)  |

| 2000                      | 4.5 V or VOUT × 1.75 (whichever is greater) |

Additionally, the maximum input voltage of the TPSM5D1806E is 15 V, however, the maximum recommended input voltage decreases at lower output voltages and higher switching frequencies. See  $\boxed{8}$  7-3 for the maximum recommended input voltage for each of the allowable switching frequencies across the output voltage range.

Product Folder Links: TPSM5D1806E

图 7-3. Maximum Input Voltage

# 7.3.4 Recommended Settings

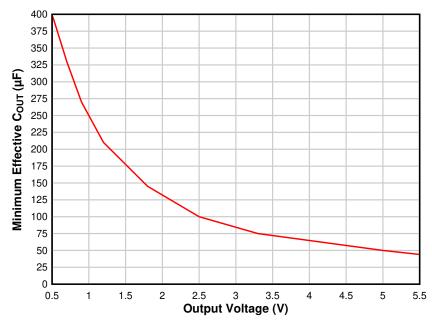

表 7-3 lists the recommended operating settings for several common output voltages. The table takes into account the minimum and maximum input voltage limits along with timing and current limitations. The table also lists the minimum required effective output capacitance for each output voltage. Also included in this table is the minimum required input voltage and required enable divider resistors to ensure safe turn ON at the minimum input voltage.

Refer to  $\frac{1}{8}$  7-1 for the allowable switching frequency. The recommended switching frequency typically results in the highest efficiency. When operating at a switching frequency other than the recommended, consult  $\frac{1}{10}$  7.3.3 for the minimum and maximum allowable input voltage.

When setting the switching frequency, both channels of the device are set to the same frequency. When operating in dual output configuration, make sure that both channels can be operated at the desired switching frequency by referencing.

表 7-3. Recommended Settings

| Output<br>Voltage<br>(V) | Top<br>Feedback<br>Resistor<br>R <sub>FBT</sub> <sup>(1)</sup><br>(k Ω) | F <sub>SW</sub><br>(kHz) | MODE2<br>Resistor<br>(kΩ) | Minimum<br>C <sub>OUT</sub> <sup>(2)</sup><br>(μF) | Minimum<br>Input<br>Voltage<br>(V) | Bottom<br>Enable<br>Resistor<br>R <sub>ENB</sub> <sup>(3)</sup><br>(k Ω) |

|--------------------------|-------------------------------------------------------------------------|--------------------------|---------------------------|----------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|

| 0.5                      | open                                                                    | 500                      | 10.7                      | 400                                                | 4.5                                | (4)                                                                      |

| 0.8                      | 6.04                                                                    | 500                      | 10.7                      | 280                                                | 4.5                                | _                                                                        |

| 0.9                      | 8.06                                                                    | 1000                     | 17.4                      | 265                                                | 4.5                                | _                                                                        |

| 1.0                      | 10.0                                                                    | 1000                     | 17.4                      | 250                                                | 4.5                                | _                                                                        |

| 1.1                      | 12.1                                                                    | 1000                     | 17.4                      | 235                                                | 4.5                                | _                                                                        |

| 1.2                      | 14.0                                                                    | 1000                     | 17.4                      | 220                                                | 4.5                                | _                                                                        |

| 1.5                      | 20.0                                                                    | 1000                     | 17.4                      | 180                                                | 4.5                                | _                                                                        |

| 1.8                      | 26.1                                                                    | 1000 17.4 140            |                           | 140                                                | 4.5                                | _                                                                        |

| 2.5                      | 40.2                                                                    | 1500                     | 28.7                      | 100                                                | 4.5                                | _                                                                        |

| 3.0                      | 49.9                                                                    | 1500                     | 28.7                      | 85                                                 | 4.8                                | 29.4                                                                     |

| 3.3                      | 56.2                                                                    | 1500                     | 28.7                      | 75                                                 | 5.3                                | 26.1                                                                     |

| 4.0                      | 69.8                                                                    | 2000                     | 53.6                      | 65                                                 | 7.1                                | 18.2                                                                     |

| 4.5                      | 80.6                                                                    | 2000                     | 53.6                      | 60                                                 | 7.9                                | 16.2                                                                     |

| 5.0                      | 90.9                                                                    | 2000                     | 53.6                      | 50                                                 | 8.8                                | 14.3                                                                     |

| 表 7-3. Recommended Settings (continued) |

|-----------------------------------------|

|-----------------------------------------|

| Output<br>Voltage<br>(V) | Top<br>Feedback<br>Resistor<br>R <sub>FBT</sub> <sup>(1)</sup><br>(k Ω) | F <sub>SW</sub><br>(kHz) | MODE2<br>Resistor<br>(kΩ) | Minimum<br>C <sub>OUT</sub> <sup>(2)</sup><br>(μF) | Minimum<br>Input<br>Voltage<br>(V) | Bottom<br>Enable<br>Resistor<br>R <sub>ENB</sub> <sup>(3)</sup><br>(k Ω) |

|--------------------------|-------------------------------------------------------------------------|--------------------------|---------------------------|----------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|

| 5.5                      | 100                                                                     | 2000                     | 53.6                      | 45                                                 | 9.6                                | 13.0                                                                     |

- (1)  $R_{FBB} = 10 \text{ k} \Omega$

- (2) Minimum C<sub>OUT</sub> listed is the effective value, taking into account the effects of DC bias and temperature variation.

- (3)  $R_{ENT} = 100 \text{ k} \Omega$

- (4) "—" means not required.

#### 7.3.5 Device Mode Configuration

The TPSM5D1806E provides a wide range of configurations through pin strapping of two pins: MODE1 and MODE2. These pins are used to configure the device outputs, set the phase offset, and set the switching frequency. The operating mode of the device can be either two independent 6-A outputs or both outputs connected together in parallel for increased current up to 12 A. In either application, a  $10-k\Omega$  resistor is required from MODE1 to MODE2.

# 7.3.5.1 MODE1 (Operating Mode and Phase Position)

Place a 10-k  $\Omega$  resistor from MODE1 to MODE2.

Place a resistor from MODE1 to AGND to set the device in the desired operating mode. The MODE1 resistor also selects the phase position for each channel. See 表 7-4 for MODE1 resistor values and the corresponding settings.

表 7-4. Operating Mode and Phase Position Settings

|                                 |                                             |                    | •                   |                                                                         |

|---------------------------------|---------------------------------------------|--------------------|---------------------|-------------------------------------------------------------------------|

| Operating Mode                  | Operating Mode Channel 1 Phase Position (°) |                    | Mode1 Resistor (kω) | Comments                                                                |

|                                 | 0                                           | 180                | 15.4                | Sets phase position for both channels to 0° and 180°.                   |

| Dual outputs                    | 90 <sup>(1)</sup>                           | 270 <sup>(1)</sup> | 24.9                | Sets phase position for both channels to 90° and 270° from SYNC signal. |

| Paralleled outputs<br>(2 phase) | 0                                           | 180                | 10.7                | Sets phase positions for both channels of the device.                   |

<sup>(1)</sup> Requires synchronization to an external clock signal.

#### 7.3.5.2 MODE2 (Setting the Switching Frequency)

Place a resistor from MODE2 to AGND to set the switching frequency of the device. See  $\frac{1}{8}$  7-5 for MODE2 resistor values and the corresponding settings. For dual-output applications, check  $\frac{1}{8}$  7-1 to make sure both outputs can operate at the selected switching frequency.

If synchronizing to an external clock, the TPSM5D1806E can only be synchronized to a frequency that is within ±20% of the switching frequency set by the MODE2 pin.

表 7-5. Switching Frequency Settings

| • • • • • • • • • • • • • • • • • • • • | . , ,               |

|-----------------------------------------|---------------------|

| Switching Frequency<br>(kHz)            | MODE2 Resistor (kΩ) |

| · · · · ·                               | ` '                 |

| 500                                     | 10.7                |

| 1000                                    | 17.4                |

|                                         |                     |

| 1500                                    | 28.7                |

| 2000                                    | 53.6                |

|                                         |                     |

Product Folder Links: TPSM5D1806E

Submit Document Feedback

#### 7.3.6 Input Capacitors

The TPSM5D1806E requires a minimum input capacitance of 88  $\mu$  F (4 × 22  $\mu$  F or 2 × 47  $\mu$  F) of ceramic type. High-quality, ceramic-type X5R or X7R capacitors with sufficient voltage rating are required. Place input capacitors, as close as possible to both VIN sides of the device, between VIN and PGND as shown in  $\Xi$  7-4. Applications with transient load requirements can benefit from adding additional bulk capacitance to the input as well.

图 7-4. Input Capacitors Pin Connections

## 7.3.7 Minimum Required Output Capacitance

The TPSM5D1806E requires a minimum amount of ceramic output capacitance (per phase) depending on the output voltage setting. The amount of required output capacitance is shown in 27-5 and is the amount of effective capacitance. The effects of DC bias and temperature variation must be considered when using ceramic capacitance. For ceramic capacitors, the package size, voltage rating, and dielectric material contributes to differences between the standard rated value and the actual effective value of the capacitance. When adding additional capacitance above the minimum, the capacitance can be ceramic type, low-ESR polymer type, or a combination of the two.

图 7-5. Minimum Required Output Capacitance (per Phase)

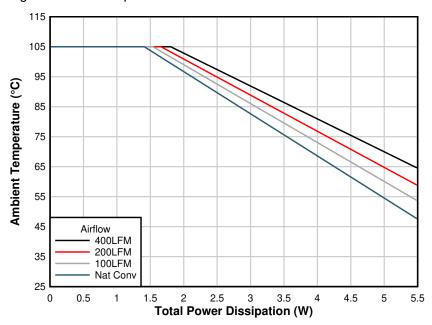

## 7.3.8 Ambient Temperature Versus Total Power Dissipation

When operating the TPSM5D1806E in dual channel configuration with different output voltages, the maximum operating ambient temperature can be determined using the total power dissipation of both channels. Refer to the power dissipation curves, 图 6-2 and 图 6-9, to determine the power dissipation for each output. Sum the power dissipation of both outputs to calculate the total power dissipation. Refer to 图 7-6 to determine the maximum allowable operating ambient temperature for a given total power dissipation. Increasing the airflow allows operation at a higher ambient temperature.

图 7-6. Ambient Temperature Versus Total Power Dissipation

## 7.3.9 Remote Sense

The TPSM5D1806E supports differential remote sense for accurate output regulation when operated in multiphase configuration. In multi-phase configuration, FB1 and RS - pins are used for remote sensing. The FB1 pin must be connected to the mid-point of the resistor divider. Additionally, the RS - pin must be connected to the negative sensing point. The FB1 and RS - pins are extremely high-impedance input terminals of the true differential remote sense amplifier. The feedback resistor divider must use resistor values much less than 100 k $\Omega$  to reduce susceptibility to noise. A simple rule of thumb is to use a 10-k $\Omega$  lower divider resistor and then size the upper resistor to achieve the desired ratio.

When configured as a dual-output device, connect the RS - pin to AGND.

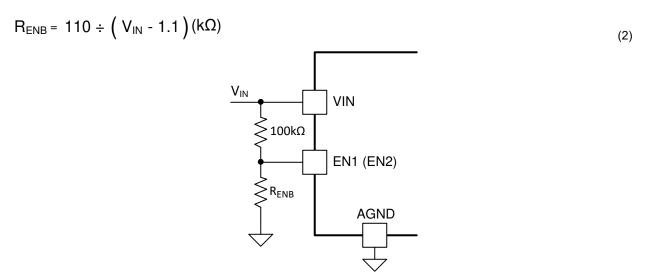

#### 7.3.10 Enable (EN) and Undervoltage Lockout (UVLO)

The precision enable feature of the TPSM6D1806E allows the voltage on the EN pin ( $V_{EN}$ ) to control the ON/OFF functionality of the device. The EN pin has an internal pullup. Floating the EN pin allows the device to start up when a valid input voltage is applied. The TPSM5D1806 switching action and output regulation are enabled when  $V_{EN}$  is greater than 1.2 V (typical). While the device is switching, if the EN voltage falls below 1.1 V (typical), the device stops switching.

It is recommended to control the turn-on and turn-off of the device at a voltage greater than the minimum input voltage as shown in 表 7-2. An external UVLO control can be added using a resistor divider on the EN1 (EN2) pin, between VIN and AGND (see 图 7-7). Select a top enable resistor of 100 k $\Omega$  and calculate the value for the bottom enable resistor (R<sub>ENB</sub>) using 方程式 2. It is recommended to use divider resistors with 1% tolerance or better and with temperature coefficient of 100 ppm or lower.

图 7-7. Adjustable UVLO Control

#### 7.3.11 Soft Start

The TPSM5D1806E soft-start feature limits the inrush current from the input supply when the device is powered up. For dual-output configuration, the soft-start time is internally programmed to 1 ms. The soft-start pin must be left floating in dual-output configuration.

The external soft start is enabled when the device is configured in parallel-output operation. In parallel-output applications, if the SS pin is left open, the default soft-start time is also 1 ms. Applications that deliver high load current can have a large amount of capacitance at the output and can require longer soft-start time. The soft-start time for such applications can be extended by connecting an external capacitor,  $C_{SS}$ , from the soft-start pin to AGND. With external  $C_{SS}$ , the soft-start time is the longer of 1 ms or the programmed external soft-start time. An internal current source ( $I_{SS}$  = 2  $\mu$  A) charges  $C_{SS}$  and generates a ramp from 0 V to  $V_{FB}$  (0.5 V) to control the ramp-up rate of the output voltage. The external soft-start time can be selected from  $\frac{1}{8}$  7-6 or calculated using  $\frac{1}{2}$   $\frac{1}{2}$

$$t_{SS} = \frac{0.5 \times C_{SS}}{2 \,\mu\text{A}} \tag{3}$$

表 7-6. C<sub>SS</sub> Values and Soft-Start Times

| C <sub>SS</sub> (nF) | C <sub>SS</sub> (nF) Open |     | 6.2 8.2 |     | 12 | 20 |  |

|----------------------|---------------------------|-----|---------|-----|----|----|--|

| t <sub>SS</sub> (ms) | 1                         | 1.5 | 2       | 2.5 | 3  | 5  |  |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

# TPSM5D1806E

ZHCSP41 - JANUARY 2022

The soft-start capacitor is discharged when VOUT is shut down by either fault protection or when  $V_{\text{EN}}$  is below the enable threshold.

#### 7.3.12 Power Good

The Power Good pins (PGOOD1, PGOOD2) are open-drain outputs that require a pullup resistor of 1 k $\Omega$  to 100 k $\Omega$  to a voltage source of 5.5 V or less to indicate the output voltage is within the PGOOD range. The BP5 output can be used as the pullup voltage source. The PGOOD detection is activated after soft start is completed. When the output voltage is within a range of  $\pm 10\%$  of the target, the PGOOD goes high after a 50- $\mu$ s internal delay. During operation, if the output voltage falls outside of  $\pm 10\%$  of target voltage, PGOOD is pulled low after a 10- $\mu$ s delay. The PGOOD feature is active while the voltage at the VIN pin is either equal to or greater than 1.5 V.

#### 7.3.13 Safe Start-Up into Pre-Biased Outputs

The device has been designed to prevent the low-side MOSFET from discharging a pre-biased output.

#### 7.3.14 BP5

The BP5 pin is the output of an internal 5-V regulator. Bypass this pin with a minimum of 1.5  $\mu$ F of effective capacitance to AGND. Place the capacitor as close as possible to the BP5 pin. This pin can be used as a pullup voltage for power-good signals.

#### 7.3.15 Overcurrent Protection

For protection against load faults, the TPSM5D1806E implements a cycle-by-cycle peak current protection. When the inductor current hits the peak current limit threshold, the high-side FET turns off and the low-side FET turns on. The device monitors the valley current threshold during the high-side FET off time. If the inductor current clears the valley current threshold, the high-side FET will turn on at the next clock edge. However, if the inductor current remains higher than the valley current threshold, the next high-side FET cycle is skipped, the low-side FET remains on, and an internal counter is incremented. This counter increments every clock edge as long as the inductor current remains higher than the valley current threshold. If the current falls below the valley current threshold at the next clock edge, the counter is reset. If the counter increments 16 consecutive clock cycles, a current limit fault is identified and the device enters hiccup mode to reduce power dissipation. In hiccup mode, the module continues in a cycle of successive shutdown and power up until the load fault is removed. During this period, the average current flowing into the fault is significantly reduced, which reduces power dissipation. Once the fault is removed, the module automatically recovers and returns to normal operation.

#### 7.3.16 Thermal Shutdown

The internal thermal shutdown circuitry forces the device to stop switching if the junction temperature exceeds 165°C typically. The device re-initiates the power-up sequence when the junction temperature drops below 145°C typically.

## 7.4 Device Functional Modes

#### 7.4.1 Active Mode

The TPSM5D1806E is in active mode when  $V_{IN}$  is above the turn-on threshold and the EN pin voltage is above the EN high threshold. Floating the EN pin allows the device to start-up when a valid input voltage is applied. This allows self start-up of the TPSM5D1806E when the input voltage is in the operation range of 4.5 V to 15 V. Connecting a resistor divider between VIN, EN, and AGND increases the UVLO threshold.

#### 7.4.2 Shutdown Mode

The EN pin provides electrical ON and OFF control for the TPSM5D1806E. When the EN pin voltage is below the EN low threshold, the device is in shutdown mode. In shutdown mode, the standby current is 250 μ A typical.

# 8 Application and Implementation

## 备注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## **8.1 Application Information**

The TPSM5D1806E is a dual 6-A output, step-down, DC/DC power module. It is used to convert a higher DC voltage to two separate 6-A power rails or one combined 12-A power rail. The following design procedure can be used to select components for the TPSM5D1806. Alternately, the WEBENCH® software can be used to generate complete designs. When generating a design, the WEBENCH® software uses an iterative design procedure and accesses comprehensive databases of components. See <a href="https://www.ti.com">www.ti.com</a> for more details.

# **8.2 Typical Application (Dual Outputs)**

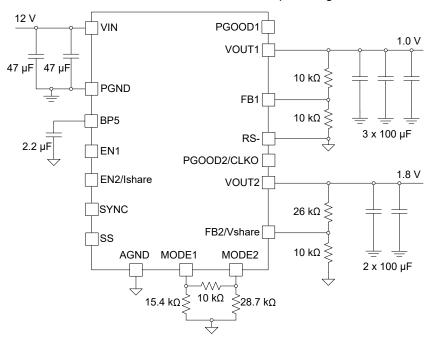

8-1 shows a typical TPSM5D1806M-ET schematic for a dual-output design.

图 8-1. TPSM5D1806E Dual Output Typical Schematic

#### 8.2.1 Design Requirements

For this design example, use the parameters listed in  $\frac{1}{8}$  8-1 as the input parameters and follow the design procedures in  $\frac{1}{8}$  8.2.2.

| Design Parameter                 | Value              |

|----------------------------------|--------------------|

| Input voltage V <sub>IN</sub>    | 12 V typical       |

| Output voltage V <sub>OUT1</sub> | 1.0 V              |

| Output voltage V <sub>OUT2</sub> | 1.8 V              |

| Switching frequency              | 1.5 MHz            |

| Output current rating            | Up to 6 A / output |

表 8-1. Design Example Parameters

# 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPSM5D1806E device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , and output current  $(I_{OUT})$  requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

# 8.2.2.2 Output Voltage Setpoint

The output voltage of the TPSM5D1806E device is externally adjustable using a resistor divider. The recommended value of  $R_{EBB}$  is 10 k  $\Omega$ . The value for  $R_{EBT}$  can be calculated using 方程式 4:

$$R_{FBT} = 20 \times (V_{OUT} - 0.5)(k\Omega)$$

(4)

For the desired output voltage of 1.0 V, the formula yields a value of 10 k  $\Omega$  . Choose the closest available value of 10.0 k  $\Omega$  for R<sub>FRT</sub>.

For the desired output voltage of 1.8 V, the formula yields a value of 26 k  $\Omega$ . Choose the closest available value of 26.1 k  $\Omega$  for R<sub>FBT</sub>.

#### 8.2.2.3 Input Capacitors

The TPSM5D1806E requires a minimum input capacitance of 88  $\mu$ F of ceramic type. High-quality ceramic type X5R or X7R capacitors with sufficient voltage rating are recommended. An additional 100  $\mu$ F of non-ceramic capacitance is recommended for applications with transient load requirements. The voltage rating of the input capacitors must be greater than the maximum input voltage.

For this design example, two 47-µF, 25-V ceramic capacitors are used.

#### 8.2.2.4 Output Capacitor Selection

The TPSM5D1806E requires a minimum amount of output capacitance for proper operation. The minimum amount of required output varies depending on the output voltage. See 🗵 7-5 for the required output capacitance.

For this design example, three  $100-\mu F$ , 6.3-V ceramic capacitors are selected for the 1.0-V output. For the 1.8-V output, two  $100-\mu F$ , 6.3-V ceramic capacitors are selected. Additional output capacitance can be needed to meet transient requirements.

Copyright © 2022 Texas Instruments Incorporated

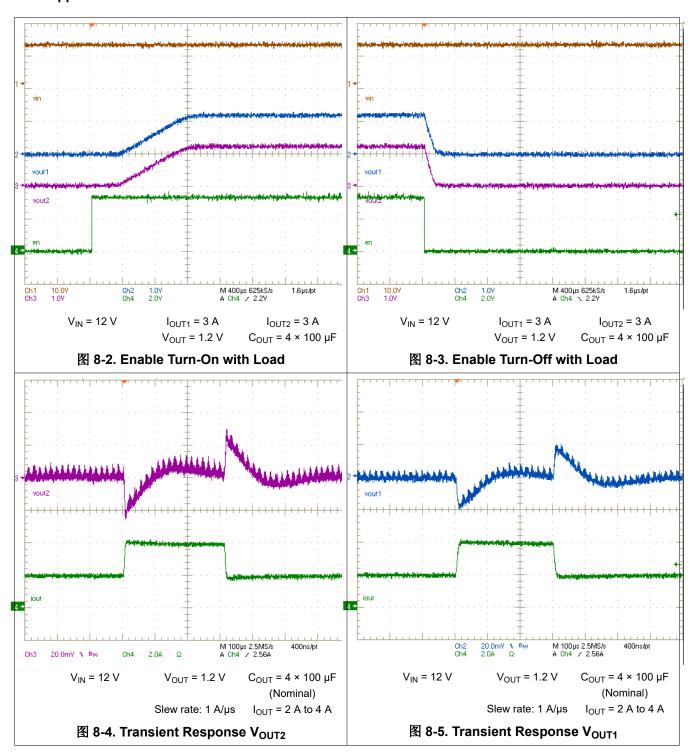

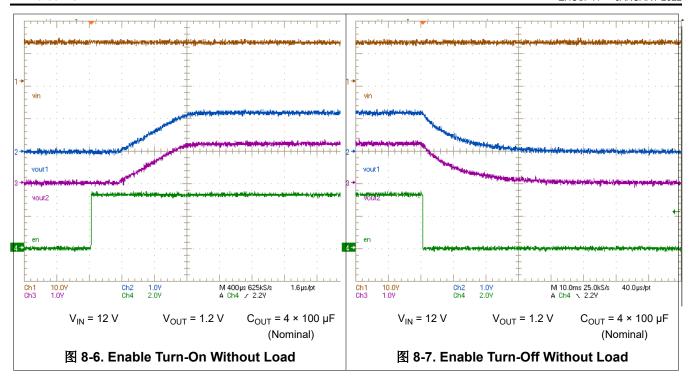

## 8.2.3 Application Curves

#### 8.2.4 Typical Application (Paralleled Outputs)

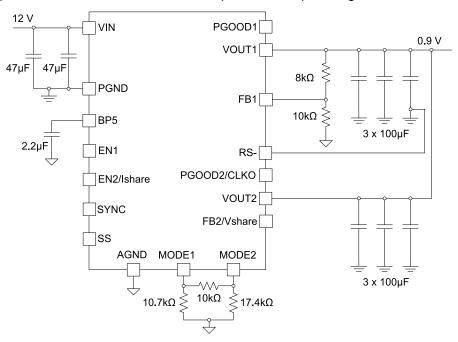

The dual outputs of the TPSM5D1806E can be combined to create a higher current (up to 12 A), single output. 8 8-8 shows a typical TPSM5D1806E schematic for a paralleled output design.

图 8-8. TPSM5D1806E Parallel Outputs Typical Schematic

#### 8.2.4.1 Design Requirements

For this design example, use the parameters listed in  $\frac{1}{8}$  8-2 as the input parameters and follow the design procedures in  $\frac{1}{8}$  8.2.4.2.

表 8-2. Design Example Parameters

| Design Parameter              | Value        |

|-------------------------------|--------------|

| Input voltage V <sub>IN</sub> | 12 V typical |

| Output voltage                | 0.9 V        |

| Switching frequency           | 1.0 MHz      |

| Output current rating         | Up to 12 A   |

#### 8.2.4.2 Detailed Design Procedure

#### 8.2.4.2.1 Output Voltage Setpoint

The output voltage of the TPSM5D1806E device is externally adjustable using a resistor divider. The recommended value of  $R_{FBB}$  is 10 k  $\Omega$ . The value for  $R_{FBT}$  can be calculated using 方程式 5:

$$R_{FBT} = 20 x \left( V_{OUT} - 0.5 \right) (k\Omega)$$

(5)

For the desired output voltage of 0.9 V, the formula yields a value of 8 k  $\Omega$ . Choose the closest available value of 8.06 k  $\Omega$  for R<sub>FBT</sub> or place two resistors in series to come closer to the exact value.

## 8.2.4.2.2 Input Capacitors

The TPSM5D1806E requires a minimum input capacitance of 88  $\,\mu$ F of ceramic type. High-quality ceramic type X5R or X7R capacitors with sufficient voltage rating are recommended. An additional 100  $\,\mu$ F of non-ceramic

capacitance is recommended for applications with transient load requirements. The voltage rating of the input capacitors must be greater than the maximum input voltage.

For this design example, two 47-µF, 25-V ceramic capacitors are used.

# 8.2.4.2.3 Output Capacitor Selection

The TPSM5D1806E requires a minimum amount of output capacitance for proper operation. The minimum amount of required output varies depending on the output voltage. See 🖺 7-5 for the required output capacitance.

For this design example, six 100-µF, 6.3-V ceramic capacitors are selected for the 0.9-V output. Additional output capacitance can be needed to meet transient requirements.

# 9 Power Supply Recommendations

The TPSM5D1806E is designed to operate from an input voltage supply range between 4.5 V and 15 V. This input supply must be well-regulated and able to withstand maximum input current and maintain a stable voltage. The resistance of the input supply rail must be low enough that an input current transient does not cause a high enough drop at the TPSM5D1806E supply voltage that can cause a false UVLO fault triggering and system reset.

If the input supply is located more than a few centimeters from the TPSM5D1806E, additional bulk capacitance can be required in addition to the ceramic bypass capacitors. The typical amount of bulk capacitance is a  $47-\mu F$  electrolytic type capacitor.

Copyright © 2022 Texas Instruments Incorporated

## 10 Layout

The performance of any switching power supply depends as much on the layout of the PCB as the component selection. The following guidelines help users design a PCB with the best power conversion performance, optimal thermal performance, and minimized generation of unwanted EMI.

# 10.1 Layout Guidelines

To achieve optimal electrical and thermal performance, an optimized PCB layout is required.

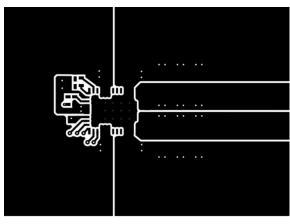

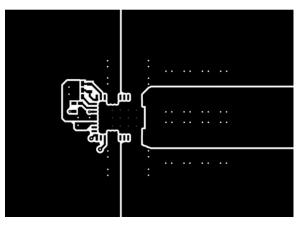

⊠ 10-1 and ⊠ 10-2 show typical PCB layouts. The following are some considerations for an optimized layout.

- Use large copper areas for power planes (VIN, VOUT, and PGND) to minimize conduction loss and thermal stress

- Place ceramic input and output capacitors close to the device pins to minimize high frequency noise.

- · Locate additional output capacitors between the ceramic capacitor and the load.

- · Connect AGND to PGND at a single point.

- Place R<sub>FBT</sub> and R<sub>FBB</sub> as close as possible to the FB pin.

- Use multiple vias to connect the power planes to internal layers.

## 10.2 Layout Examples

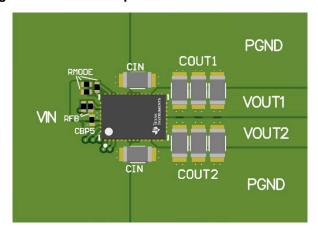

## **Single Device Dual Output**

图 10-1. Typical Dual-Output Layout

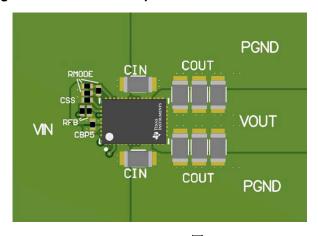

## **Single Device Parallel Output**

图 10-2. Typical Parallel-Output Layout

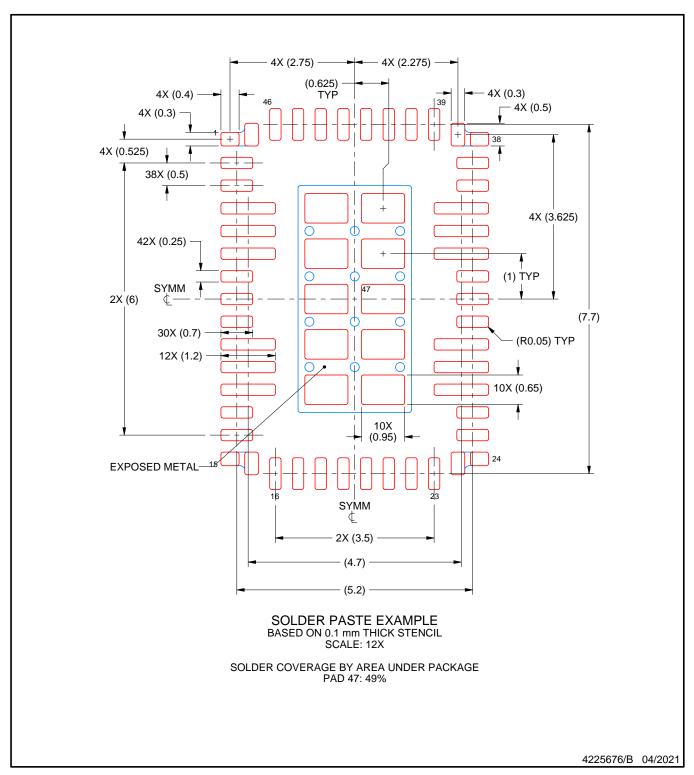

# 10.2.1 Package Specifications

|                             | TPSM5D1806  Meets UL 94 V-O  iability  Per Bellcore TR-332, 50% stress, T <sub>A</sub> = 40°C, ground benign |      | Unit |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|------|------|

| Flammability                | Meets UL 94 V-O                                                                                              |      |      |

| MTBF Calculated Reliability | Per Bellcore TR-332, 50% stress, T <sub>A</sub> = 40°C, ground benign                                        | 89.3 | MHrs |

#### 10.2.2 EMI

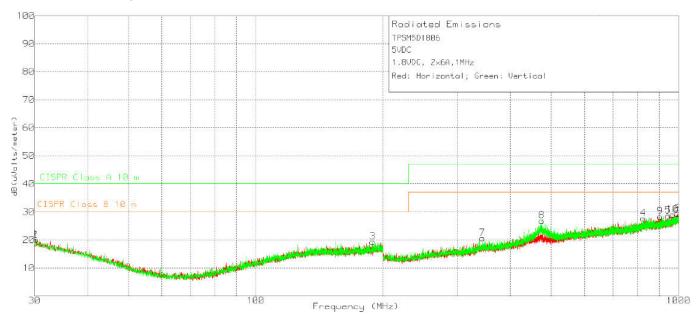

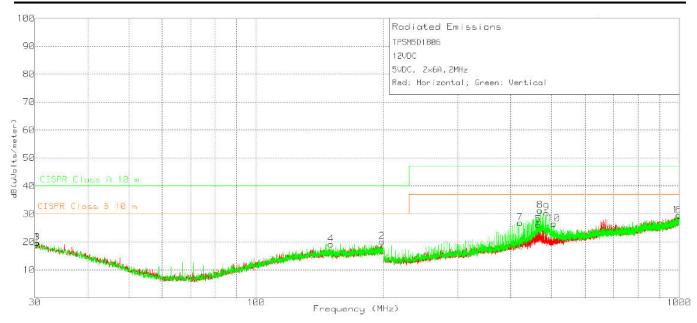

The TPSM5D1806E is compliant with EN55011 Class-B radiated emissions.

☑ 10-3 and ☑ 10-4 show typical examples of radiated emissions plots for the TPSM5D1806E. The graphs include the plots of the antenna in the horizontal and vertical positions.

EMI plots were measured using the standard TPSM5D1806EVM with ferrite beads (Murata, BLM18SG330SN1) in series with the input wires.

图 10-3. Radiated Emissions 5-V Input, 1.8-V Outputs, 6-A/Output Load

图 10-4. Radiated Emissions 12-V Input, 5-V Output, 6-A/Output Load

# 11 Device and Documentation Support

## 11.1 Device Support

# 11.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

#### 11.1.2 Development Support

#### 11.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPSM5D1806E device with the WEBENCH® Power Designer.

- Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

# 11.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击 订阅更新 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 11.3 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 11.4 Trademarks

TI E2E™ is a trademark of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

# 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 11.6 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS   | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)  |

|-----------------------|--------|---------------|------------------|-----------------------|--------|-------------------------------|----------------------------|--------------|-------------------|

| 2UM5D1806MRDBRETG4    | Active | Production    | B0QFN (RDB)   51 | 2000   LARGE T&R      | Yes    | NIPDAU                        | Level-3-260C-168 HR        | -55 to 125   | TPSM5D1806M<br>ET |

| 2UM5D1806MRDBRETG4.A  | Active | Production    | B0QFN (RDB)   51 | 2000   LARGE T&R      | Yes    | NIPDAU                        | Level-3-260C-168 HR        | -55 to 125   | TPSM5D1806M<br>ET |