TPS92661-Q1

ZHCSCS9-SEPTEMBER 2014

# 适用于汽车前灯系统的高亮度 LED 矩阵管理器

## 1 特性

- 12 个串联 LED 旁路开关

- 多点 UART 通信接口

- 可编程 10 位脉宽调制 (PWM) 亮度调节

- 独立的打开和关闭时间

- 内置相移功能

- 器件间同步

- LED 开路/短路检测和保护

- 故障报告

- AEC-Q100 等级 1

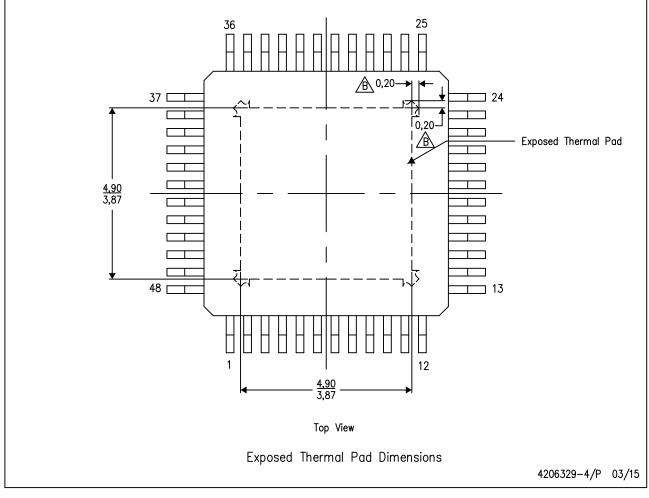

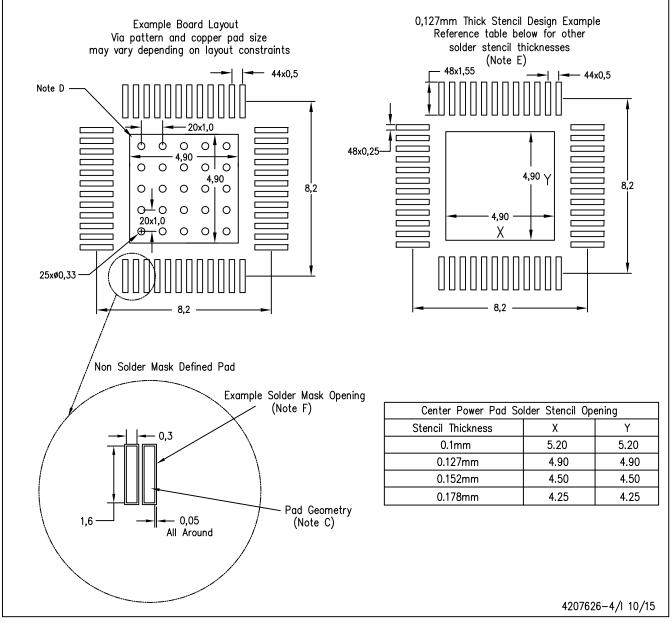

- 散热增强型封装

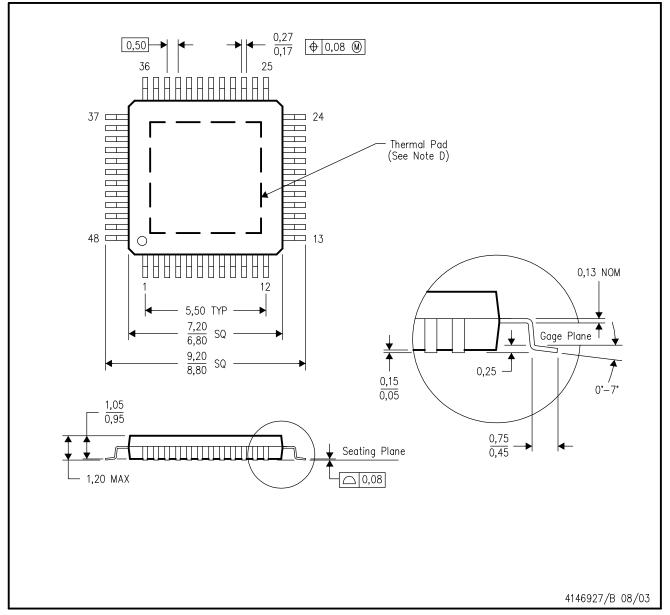

- 48 引脚薄型四方扁平 (TQFP) 外露垫封装

#### 2 应用

- 汽车前灯系统

- 高亮度 LED 矩阵系统

## 3 说明

TPS92661 器件是一款紧凑型高集成解决方案,适用于对应用中的大阵列高亮度 LED (如,汽车前灯)进行分流 FET 亮度调节。

TPS92661 器件包括一个 12 开关串联阵列(用于绕过 串联电路中的单个 LED)以及一个串行通信接口(通 过主微控制器进行控制和管理)。

板载充电泵电源轨可升至接地端以上 67 V,能够提供 LED 旁路开关栅极驱动。旁路开关的低导通电阻 (R<sub>DS(on)</sub>) 最大限度降低了传导损耗和功耗。

TPS92661 器件包含一个多点通用异步收发器 (UART),适用于串行通信。 串联电路中各 LED 的打 开和关闭时间可单独编程。 PWM 频率可通过内部寄存器调整,多个器件可同步为相同的频率和相位。

TPS92661 器件具有 LED 开路保护以及通过串行接口 实现的 LED 开路和短路故障报告功能。

TQFP 封装采用连通拓扑,能够在单层金属核 LED 载 板上轻松传递信号。

## 器件信息(1)

| 部件号         | 封装       | 封装尺寸 (标称值)      |

|-------------|----------|-----------------|

| TPS92661-Q1 | PHP (48) | 7.00mm x 7.00mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

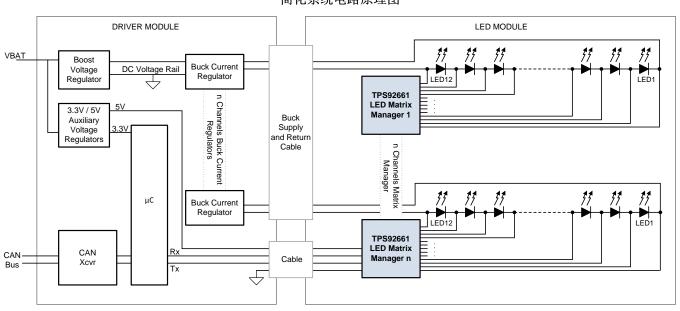

## 简化系统电路原理图

# 目录

| 1 | 特性1                                  | 8 A  | pplication and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

|---|--------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | 应用 1                                 | 8    | 3.1 Applications Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38 |

| 3 | 说明 1                                 | 8    | 3.2 Design Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38 |

| 4 | 修订历史记录 2                             | 9 P  | ower Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

| 5 | Pin Configuration and Functions3     | 9    | 0.1 General Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

| 6 | Specifications4                      | 9    | 0.2 Internal Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 |

| • | 6.1 Absolute Maximum Ratings         | 9    | 0.3 Power Up and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

|   | 6.2 Handling Ratings                 | 9    | 0.4 VIN Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41 |

|   | 6.3 Recommended Operating Conditions | 9    | 0.5 Initialization Set-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41 |

|   | 6.4 Thermal Information              | 10 L | .ayout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |

|   | 6.5 Electrical Characteristics 6     |      | 0.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | 6.6 Typical Characteristics          | 1    | 0.2 Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43 |

| 7 | Detailed Description 9               | 11 - | 器件和文档支持                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| • | 7.1 Overview                         |      | 1.1 商标                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | 7.2 Functional Block Diagram         | 1    | 1.2 静电放电警告                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44 |

|   | 7.3 Feature Description              | 1    | 1.3 Export Control Notice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

|   | 7.4 Device Functional Modes          | 1    | 1.4 术语表                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

|   | 7.5 Programming                      |      | 机械封装和可订购信息                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   | 5                                    | '    | A 14 MAN 11 A 14 MA 11 MAN 11 |    |

|   | 7.6 Register Map                     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

# 4 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2014 年 9 月 | *    | 最初发布。 |

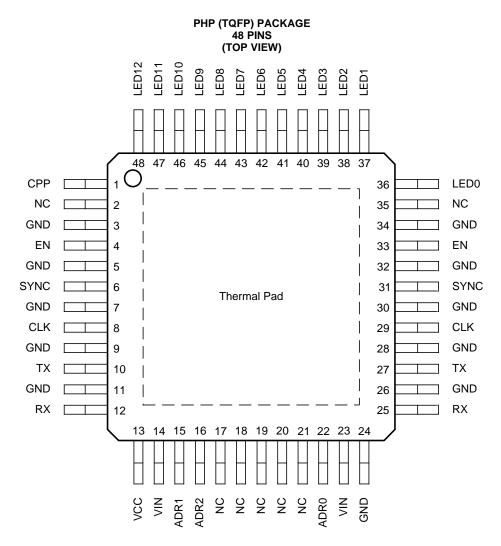

## 5 Pin Configuration and Functions

**Pin Functions**

| PIN  |                                                      | 1/0 | DESCRIPTION                                                                                             |

|------|------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------|

| NAME | NO.                                                  | 1/0 | DESCRIPTION                                                                                             |

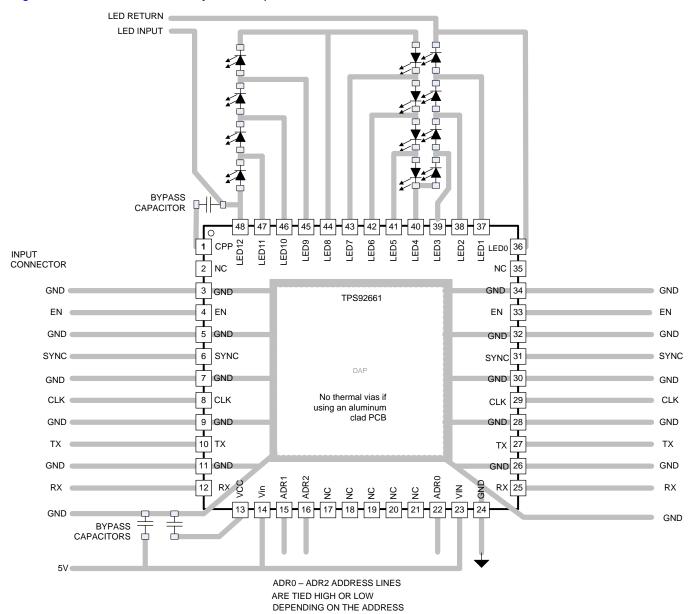

| ADR0 | 22                                                   | 1   | Least significant bit (LSB) of device address. Connect to VIN or GND.                                   |

| ADR1 | 15                                                   | 1   | Second bit of device address. Connect to VIN or GND.                                                    |

| ADR2 | 16                                                   | I   | Most significant bit (MSB) of device address. Connect to VIN or GND.                                    |

| CLK  | 8                                                    | 1   | System clock. This clock is provided externally (by the microcontroller unit or an external             |

| CLK  | oscillator) and is the primary clock for the device. |     | oscillator) and is the primary clock for the device.                                                    |

| СРР  | 1                                                    | 1   | Charge pump output. Bypass with a ceramic capacitor with a minimum value of 0.1 $\mu\text{F}$ to LED12. |

| EN   | 4                                                    | _   | Enable pins. The device is active when EN is high or in reset when EN is low. Connect to                |

| EIN  | 33                                                   | '   | microcontroller unit output or tie to VCC or VIN for enable at power-up.                                |

| GND  | 3, 5, 7, 9, 11,<br>24, 26, 28,<br>30, 32, 34         | ı   | Device system ground. All pins MUST be connected for proper operation.                                  |

| LED0 | 36                                                   | 0   | Connect to cathode of LED1.                                                                             |

| LED1 | 37                                                   | 0   | Connect to anode of LED1 and cathode of LED2.                                                           |

| LED2 | 38                                                   | 0   | Connect to anode of LED2 and cathode of LED3.                                                           |

## Pin Functions (continued)

| F           | PIN                          | 1/0 | DECODIDETION                                                                                                                                                                                                                |  |  |

|-------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.                          | I/O | DESCRIPTION                                                                                                                                                                                                                 |  |  |

| LED3        | 39                           | 0   | Connect to anode of LED3 and cathode of LED4.                                                                                                                                                                               |  |  |

| LED4        | 40                           | 0   | Connect to anode of LED4 and cathode of LED5.                                                                                                                                                                               |  |  |

| LED5        | 41                           | 0   | Connect to anode of LED5 and cathode of LED6.                                                                                                                                                                               |  |  |

| LED6        | 42                           | 0   | Connect to anode of LED6 and cathode of LED7.                                                                                                                                                                               |  |  |

| LED7        | 43                           | 0   | Connect to anode of LED7 and cathode of LED8.                                                                                                                                                                               |  |  |

| LED8        | 44                           | 0   | Connect to anode of LED8 and cathode of LED9.                                                                                                                                                                               |  |  |

| LED9        | 45                           | 0   | Connect to anode of LED9 and cathode of LED10.                                                                                                                                                                              |  |  |

| LED10       | 46                           | 0   | Connect to anode of LED10 and cathode of LED11.                                                                                                                                                                             |  |  |

| LED11       | 47                           | 0   | Connect to anode of LED11 and cathode of LED12.                                                                                                                                                                             |  |  |

| LED12       | 48                           | 0   | Connect to anode of LED12.                                                                                                                                                                                                  |  |  |

| NC          | 2, 17, 18, 19,<br>20, 21, 35 | _   | No connection.                                                                                                                                                                                                              |  |  |

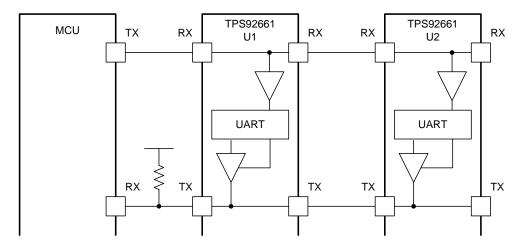

|             | 12                           |     | Received data pins. Connect one RX pin of first device to microcontroller unit TX output and                                                                                                                                |  |  |

| RX          | 25                           | I/O | use second pin to connect to a RX pin of the second device. All other devices use both pins to route the RX line through each device.                                                                                       |  |  |

|             | 6                            |     | Synchronization pins. Allows synchronization of multiple TPS92661 devices on the same                                                                                                                                       |  |  |

| SYNC        | 31                           | I/O | network. May be driven by the microcontroller unit, or one TPS92661 device may be programmed via the serial interface to provide this pulse. Only one device should drive this signal. May be left unconnected if not used. |  |  |

|             | 10                           |     | Transmitted data pins. Connect one TX pin of first device to microcontroller unit RX input and                                                                                                                              |  |  |

| TX          | 27                           | I/O | use second pin to connect to a TX pin of the second device. All other devices use both pins to route the TX line through each device. This pin requires a $100k\Omega$ pull-up resistor.                                    |  |  |

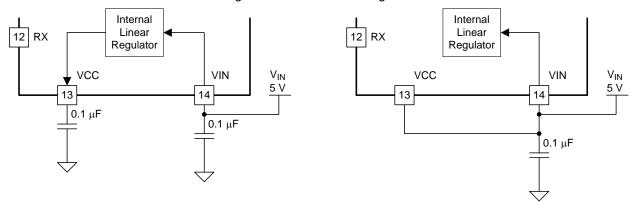

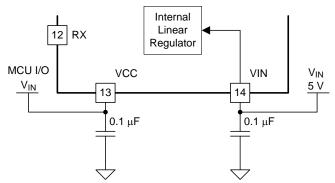

| VCC         | 13                           | 0   | Output of the on-board 3.3-V LDO. This pin requires a ceramic output capacitor with a value of 0.1 $\mu$ F or greater. Tie to the VIN pin for 5-V microcontroller unit systems.                                             |  |  |

| VIN         | 14                           |     | 5-V power supply input for device. Bypass with a ceramic capacitor with a minimum value of                                                                                                                                  |  |  |

| VIIN        | 23                           |     | 0.1 μF.                                                                                                                                                                                                                     |  |  |

| Thermal Pad |                              | -   | Connect to system GND.                                                                                                                                                                                                      |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings (1)(2)

Over operating free-air temperature range (unless otherwise noted)

|               |                                      | MIN  | MAX | UNIT |

|---------------|--------------------------------------|------|-----|------|

|               | VIN, VCC to GND                      | -0.3 | 7   |      |

|               | CPP to GND                           | -0.3 | 67  |      |

| Input voltage | CPP to LED12                         | -0.3 | 7   | V    |

| Input voltage | LEDx to GND                          | -0.3 | 60  | V    |

|               | LEDx to LED(x-1)                     | -0.3 | 7   |      |

|               | SYNC, EN, CLK, TX, RX, ADR0-2 to GND | -0.3 | 7   |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales/Office/Distributors for availability and specifications.

www.ti.com.cn

## 6.2 Handling Ratings

|                    |                           |                                              |                         | MIN   | MAX  | UNIT |

|--------------------|---------------------------|----------------------------------------------|-------------------------|-------|------|------|

| T <sub>stg</sub>   | Storage temperature range |                                              |                         | -40   | 150  | °C   |

|                    |                           | Human body model (HBM), per AEC (            | Q100-002 <sup>(1)</sup> | -2000 | 2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Charged device model (CDM), per AEC Q100-011 | ALL Pins                | -750  | 750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                 |                  | MIN                 | NOM         | MAX                      | UNIT |

|------------------|---------------------------------|------------------|---------------------|-------------|--------------------------|------|

| V <sub>IN</sub>  | Supply input voltage range      |                  | 4.5                 |             | 5.5                      | V    |

| VI               | Input voltage range per channel | LEDx to LED(x-1) |                     |             | 5.0                      | V    |

| Io               | Output current range            |                  | Thermal             | lly Limited |                          | Α    |

| f <sub>CLK</sub> | CLK frequency <sup>(1)</sup>    |                  | 0.1                 |             | 16                       | MHz  |

| D <sub>CLK</sub> | CLK duty cycle                  |                  | 40%                 |             | 60%                      |      |

| t <sub>EW</sub>  | EN input pulse width low        |                  | 50                  |             |                          | ns   |

| t <sub>ESS</sub> | EN setup to serial start        |                  | 24/f <sub>CLK</sub> |             |                          | S    |

| t <sub>SW</sub>  | SYNC input pulse width          |                  | 1/f <sub>CLK</sub>  |             |                          | S    |

| V <sub>IH</sub>  | High-level input voltage        |                  | 1.9                 |             | V <sub>VCC</sub> + 0.3 V | V    |

| V <sub>IL</sub>  | Low-level input voltage         |                  | GND –<br>0.3 V      |             | 8.0                      | V    |

| T <sub>A</sub>   | Ambient temperature             |                  | -40                 |             | 125                      | °C   |

| TJ               | Junction temperature            |                  | -40                 |             | 150                      | °C   |

<sup>(1)</sup> Minimum  $f_{clk}$  is applicable only when CKWEN bit is set.  $f_{clk}$  down to 0Hz is possible when bit is not set.

## 6.4 Thermal Information

|                        |                                              | TPS92661 |       |

|------------------------|----------------------------------------------|----------|-------|

|                        | THERMAL METRIC <sup>(1)</sup>                | TQFP     | UNITS |

|                        |                                              | 48 pins  |       |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 25.7     |       |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 10.5     |       |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.1      | 20044 |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2      | °C/W  |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.0      |       |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.3      |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# TEXAS INSTRUMENTS

## 6.5 Electrical Characteristics

Limits apply over operating junction temperature range  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +150^{\circ}\text{C}$ . Typical values represent the most likely parametric norm at  $\text{T}_{\text{J}} = 25^{\circ}\text{C}$ . Unless otherwise noted,  $\text{V}_{\text{IN}} = 5 \text{ V}$ . For digital outputs,  $\text{C}_{\text{LOAD}} = 20 \text{ pF}$ .

|                         | PARAMETER                                      | CONDITIONS                                           | MIN  | TYP                 | MAX  | UNIT<br>S |

|-------------------------|------------------------------------------------|------------------------------------------------------|------|---------------------|------|-----------|

| GENERAL                 |                                                |                                                      |      |                     |      |           |

| I <sub>VIN-OP</sub>     | Input operating bias current                   | No switching                                         |      | 1                   |      | mA        |

| V <sub>IN-UVT</sub>     | VIN internal POR threshold                     | VIN rising                                           |      |                     | 4.5  | V         |

| V <sub>CC-REG</sub>     | Regulated VCC voltage                          | 0 mA ≤ I <sub>VCC</sub> ≤ 5 mA                       | 3.1  | 3.3                 | 3.5  | V         |

| I <sub>VCC-LIM</sub>    | VCC current limit                              |                                                      |      | 10                  |      | mA        |

| V <sub>CPP</sub>        | Charge pump operating voltage                  | V <sub>VIN</sub> = 5 V, V <sub>SW</sub> = 0 V - 60 V |      | 6.2                 |      | V         |

| f <sub>CPP</sub>        | Charge pump oscillator frequency               |                                                      | 1.3  | 2.3                 | 3.3  | MHz       |

| LED MATR                | IX SWITCHES                                    |                                                      |      |                     |      |           |

| R <sub>DS(on)</sub>     | LED switch on-resistance (1)                   |                                                      |      | 225                 |      | mΩ        |

| R <sub>ALL(on)</sub>    | All switches on-resistance                     | Measured LED12 - LED0                                |      | 1800                | 3400 | mΩ        |

| I <sub>DS(off)</sub>    | OFF state switch leakage current               |                                                      |      |                     | 50   | μΑ        |

| V <sub>TH-S</sub>       | LED short threshold voltage                    | V <sub>SW</sub> = 0 V - 60 V                         | 0.52 |                     | 1.4  | V         |

| V <sub>TH-O</sub>       | LED OPEN threshold voltage                     | V <sub>SW</sub> = 0 V - 60 V                         | 5    | 6                   | 6.9  | V         |

| t <sub>TO-O</sub>       | LED OPEN detection and correction delay        |                                                      |      | 50                  | 150  | ns        |

| t <sub>REP</sub>        | LED fault reporting delay                      |                                                      |      |                     | 5    | μs        |

| t <sub>RISE(LEDx)</sub> | LEDx drain voltage rise time <sup>(2)</sup>    | I <sub>LED</sub> = 800 mA                            |      | 2                   |      | μs        |

| t <sub>FALL(LEDx)</sub> | LEDx drain voltage fall time <sup>(2)</sup>    | I <sub>LED</sub> = 800 mA                            |      | 2                   |      | μs        |

| DIGITAL SE              | PECIFICATIONS                                  |                                                      |      |                     |      |           |

| V <sub>IH-TH</sub>      | High-level input voltage threshold             |                                                      |      |                     | 1.9  | V         |

| V <sub>IL-TH</sub>      | Low-level input voltage threshold              |                                                      | 0.8  |                     |      | V         |

| V <sub>OH</sub>         | High-level output voltage                      | I <sub>SOURCE</sub> = 2 mA, V <sub>VCC</sub> = 4.0 V | 4.27 |                     |      | V         |

| V <sub>OL</sub>         | Low-level output voltage                       | I <sub>SINK</sub> = 2 mA, V <sub>VCC</sub> = 4.5 V   |      |                     | 0.23 | V         |

| I <sub>OS</sub>         | Output short circuit current (source or sink)  | V <sub>VCC</sub> = 4.5 V                             |      | 42                  |      | mA        |

| R <sub>SP</sub>         | Internal SYNC pull-down                        |                                                      |      | 100                 |      | kΩ        |

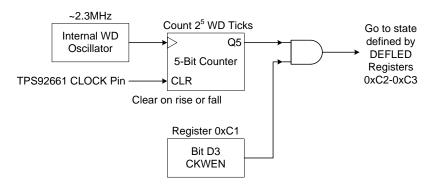

| t <sub>WD-TO</sub>      | CLK watchdog timeout                           |                                                      |      | 32/f <sub>CPP</sub> |      | μs        |

| t <sub>TO</sub>         | CLK rise to TX output valid <sup>(2)</sup>     |                                                      |      | 80                  |      | ns        |

| t <sub>TZ</sub>         | CLK rise to TX output tri-state <sup>(2)</sup> |                                                      |      | 80                  |      | ns        |

<sup>(1)</sup> Single channel on-resitance (R<sub>DS(on)</sub>) measurement includes internal bond wires. All switches on-resistance (R<sub>ALL(on)</sub>) should be used for all power calculations. See Internal Switch Resistance for details.

<sup>(2)</sup> Specified by design. Not production tested.

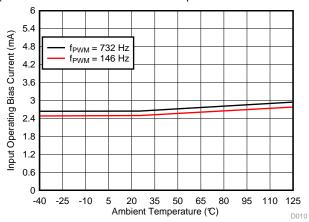

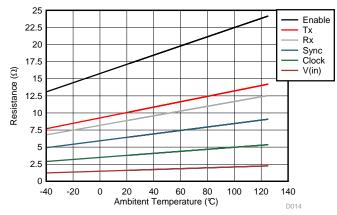

## 6.6 Typical Characteristics

$T_A = 25$ °C free air unless otherwise specified

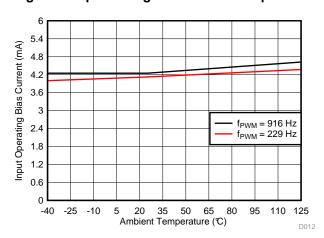

Figure 1. Input Voltage Current vs Temperature

$V_{VIN} = 5.5 \text{ V}$   $f_{CLK} = 15 \text{ MHz}$  Figure 3. Input Voltage Current Draw vs

Temperature

3.35

3.34

\$\int\_{\text{vcc}} = \text{No Load} \\ \text{lvcc} = 5 \text{ mA} \\

\$\int\_{\text{vcc}} = 5 \text{ mA} \\

\$\int\_{\text{vcc}} = 5 \text{ mA} \\

\$\int\_{\text{vcc}} = 3.31

\$\int\_{\text{vcc}} = 3.31

\$\int\_{\text{vcc}} = 3.31

\$\int\_{\text{vcc}} = 3.32

\$\int\_{\text{vcc}} = 3.29

\$\int\_{\text{vcc}} = 3.27

\$\int\_{\text{vcc}} = 3.27

Figure 5. Regulated VCC Voltage vs Junction Temperature

Junction Temperature (°C)

150

36 55 74 93 112 131

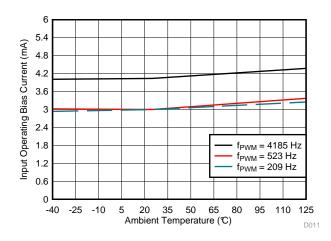

$V_{VIN} = 5.5 \text{ V}$   $f_{CLK} = 8.57 \text{ MHz}$ Figure 2. Input Voltage Current Draw vs

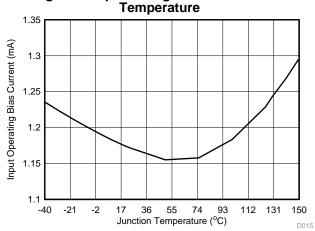

Figure 4. Input Operating Bias Current, Non-Switching vs. Junction Temperature

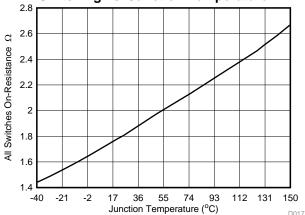

Figure 6. All Switches On-Resistance vs Junction Temperature

3.26 3.25

-40

-21 -2

www.ti.com.cn

## **Typical Characteristics (continued)**

$T_A = 25$ °C free air unless otherwise specified

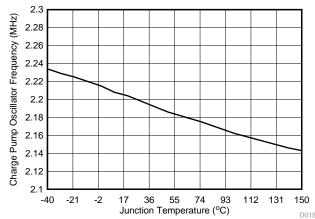

Figure 7. Charge Pump Oscillator Frequency vs Junction Temperature

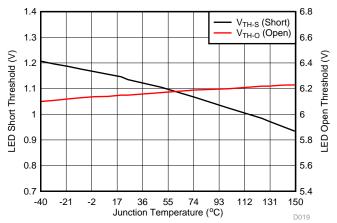

Figure 8. Channel Open and Short Protection Thresholds vs Junction Temperature

www.ti.com.cn ZHCSCS9 – SEPTEMBER 2014

## 7 Detailed Description

#### 7.1 Overview

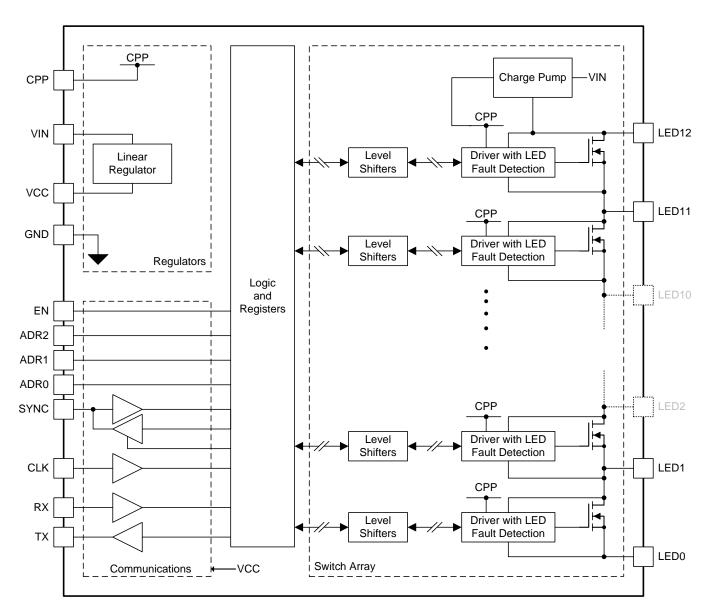

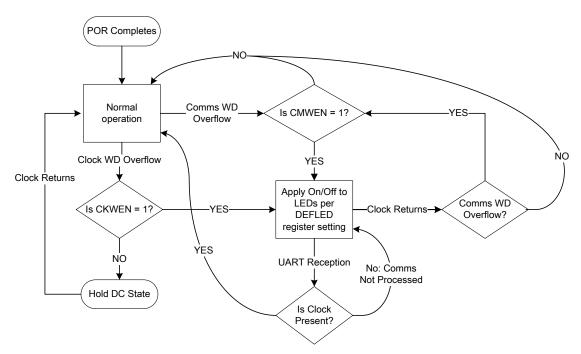

The TPS92661 lighting matrix manager (LMM) device, in conjunction with a buck switching current regulator, enables a fully dynamic matrix beam solution where each LED can be individually controlled. This type of control of an LED array is ideally suited for dynamic headlight applications where adaptive beam forming requires pixel level control of the array.

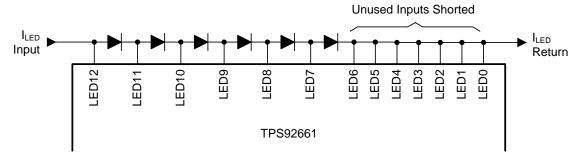

The TPS92661 device configures 12 series connected low voltage switches (MOSFETs) that can float up to 67 V above ground potential. Each switch connects in parallel to one LED, thereby creating individual shunt paths across each LED of a series string of 12 LEDs. LED strings with fewer LEDs can be used, however the unused channels should be physically shorted externally to reduce unnecessary internal power consumption.

Each switch has an individual driver, overvoltage protection circuit and diagnostics circuit referenced to the source of that switch. This configuration allows for fully dynamic operation with the switches above it and below it. The device monitors overvoltage conditions on each switch and automatically protects them in the event of an open LED connection. The device detects open LED conditions as well as shorted LED conditions and reports them through the fault reporting network.

All twelve internal bypass switches can be individually pulse width modulated (PWM) at a programmed frequency and duty cycle. This PWM dimming topology provides Inherent phase shifting capability. In addition, the switch transitions during PWM dimming are slew rate limited to mitigate any EMI concerns due to the di/dt and dv/dt of the switching action.

The TPS92661 device also provides multi-drop UART communications capability between a host MCU and up to 8 slave TPS92661 devices. The UART receives data corresponding to the desired PWM information for all 12 internal switches. In addition, it can send back fault and other diagnostic data to the host MCU. Hardware connections on the three address pins allows addressing of the eight devices.

An internal regulator accepts the 5-V power supply input for the TPS92661 device and generates a 3.3-V regulated output for the I/O buffers used in the internal UART. The internal regulator can be bypassed by shorting VIN to VCC if 5-V communication is desired.

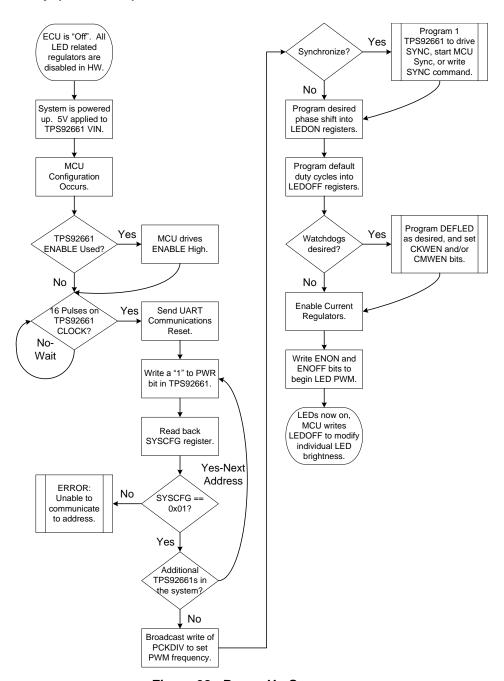

The combination of features in the TPS92661 device provides the ideal interface for individual control of high current LED arrays. The Figure 27 shows a dynamic headlight application using multiple TPS92661 devices. The electronic control unit (ECU), usually attached to the outside of the headlight, contains the master MCU, a boost pre-regulator stage that takes the variable battery voltage and steps it up to a stable DC voltage rail. The application includes multiple channels of buck current regulators to provide a stable current through each series string of 12 high brightness LEDs. The TPS92661 device should reside on the LED load board where it is as close as possible to the LEDs to which it directly connects.

This location has two major benefits.

- The close proximity minimizes distributed inductance and parasitic capacitance associated with the cable connection between ECU board and LED load board. When PWM dimming with a parallel shunt FET, locating the switch close to the LED prevents large ringing during each transition.

- The close proximity offers better thermal connection

Ultimately, the TPS92661 device enables an optimal partition for a flexible, high performing dynamic headlight system.

# TEXAS INSTRUMENTS

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Controlling the Internal LED Bypass Switches

The TPS92661 device (LED Matrix Manager) consists of 12 series connected bypass switches between terminals LED12 and LED0. Each bypass switch, when driven to an off state, allows the string current to flow through the corresponding parallel-connected LED, turning the LED on. Conversely, driving the bypass switch to an on state shunts the current through the bypass switch and turns the LED off.

ZHCSCS9-SEPTEMBER 2014 www.ti.com.cn

## **Feature Description (continued)**

#### 7.3.2 Internal Switch Resistance

Each single switch (connected between  $LED_n$  and  $LED_{n-1}$ ) has a measurable typical  $R_{DS(on)}$  value of 225 m $\Omega$ . This measurement includes the actual on-resistance ( $R_{DS(on)}$ ) of the switch and the resistance of the two internally connected bond wires. When multiple series switches are on, the effective resistance is not simply the number of channels multiplied by 225 mΩ because there are not two conducting bond wires for every seriesconnected switch. For this reason the all-switches on-resistance (RALL(on)) is specified in the Electrical Characteristics table. This value includes the twelve R<sub>DS(on)</sub> on-resistances and the resistance of the bond wires at each end of the series connected switches.

The dominant power loss mechanism In the TPS92661 device, is I<sup>2</sup>R loss through the switches. Other power loss sources are always less than 50 mW. When calculating the power dissipation of the TPS92661 device switches, use Equation 1 for the best estimation of this power loss.

$$R_{DS(on)(x\_channels)} = R_{ALL(on)(max)} \times \left(\frac{n}{12}\right) = 238 \text{ m}\Omega \times n$$

where

See the 6 LED, 1.5-A Application section for a sample calculation.

#### 7.3.3 PWM Dimming

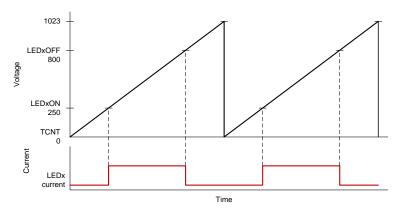

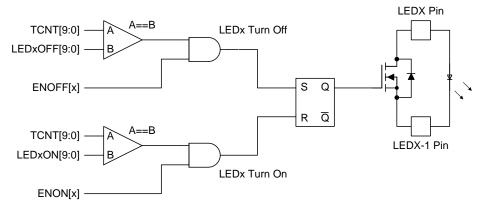

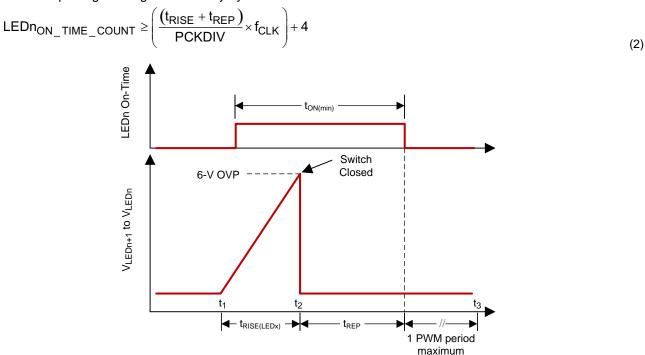

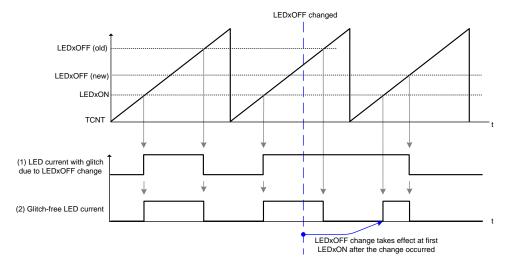

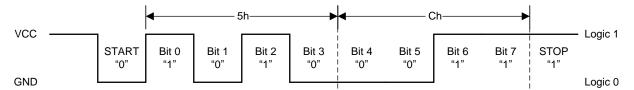

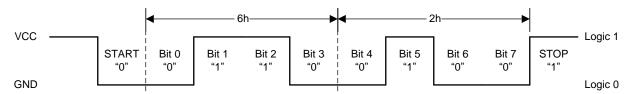

The TPS92661 device provides 10-bit PWM dimming of each individual LED. The LED turn-on and turn-off times are separately programmed for each LED. The LEDxON registers and LEDxOFF registers (where x = 1 to 12) determine the LED turn-on and turn-off times, respectively, within the PWM dimming period. Phase shifting can be accomplished by staggering the LEDxON times or LEDxOFF times. The 10-bit internal PWM Period Counter (TCNT) is compared against the LEDxON and LEDxOFF values.

When TCNT reaches the programmed LEDxON value for a given LED, the corresponding bypass switch is turned off to force current through the LED. Similarly, when TCNT reaches the programmed LEDxOFF value, the bypass switch is turned on to turn off the LED. TCNT counts continuously from 0 to 1023 and returns to 0 again. The LED PWM dimming period equals 1024 times the internally divided, programmable PWM clock period. Figure 9 shows an example of LED PWM using values of LEDxON = 250 and LEDxOFF = 800.

Figure 9. LED PWM Example

Because the LEDxON and LEDxOFF times are completely programmable, this allows the system flexibility to phase shift the leading edge (LED On), the trailing edge (LED Off), or double-edge PWM.

The comparison circuitry consists of a digital comparator, along with an AND gate to allow that particular comparison to propagate to the LED switch. The TCNT counter value is continuously compared against the value programmed into the LED On/Off registers. The ENON bit that corresponds to that particular LED determines whether or not that comparison has any effect at the LED. The logic is represented in Figure 10.

Figure 10. PWM Dimming Control Logic

#### 7.3.4 PWM Clock

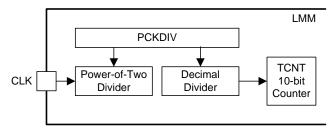

The PWM clock that drives TCNT is a divided-down version of the CLK input. The divider is programmed by writing to the PWM clock divider register (PCKDIV). The divider comprises two dividers in series: a power-of-2 clock divider followed by a decimal count divider (see Figure 11 and *PWM Clock Divider Register (PCKDIV)* for PCKDIV bitmap). Upon power-up, the PWM clock divider is programmed to a divisor value of 16.

Figure 11. PWM Clock Divider

#### 7.3.5 PWM Synchronization

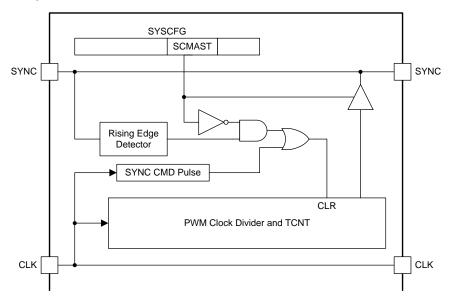

Upon power-up, the TCNT counter is reset to 0. The TCNT counter is clocked by the internal PWM clock. In order to correctly synchronize multiple TPS92661 devices on the same network, two conditions must be met:

- All TPS92661 devices must be clocked by the same clock on the CLK terminal.

- All TPS92661 devices must be programmed with the same PWM clock dividers (PCKDIV).

Assuming that these conditions are met, the TPS92661 devices may be synchronized by either of two methods:

1. As shown in Figure 12, the TPS92661 device includes a synchronization input/output (SYNC) and a synchronization master bit (SCMAST) in the system configuration register (SYSCFG). If SCMAST is set to 1, the TPS92661 device drives the SYNC terminal. The TPS92661 device generates a high pulse that is one-half of a PWM period on SYNC when TCNT and the PWM clock divider are about to roll over to 0. This SYNC signal can be fed to other TPS92661 devices. In other words, either the MCU can drive SYNC, or only one TPS92661 device should have SCMAST set to 1. The rest of the TPS92661 devices on the network must have SCMAST set to 0. If SCMAST is set to 0 (the default value), a low-to-high transition on SYNC at least one CLK cycle resets both TCNT and the PWM clock divider to 0 after internally synchronizing to the rising edge of CLK. SYNC is a feed-through signal that may be tied to the next TPS92661 device in order to synchronize multiple TPS92661 devices with respect to each other.

## NOTE

In order to prevent bus contention, ensure that the network design includes only one synchronization master.

2. The TCNT counter and PWM clock divider can both be reset to 0 at any time by issuing a broadcast write synchronization command. Due to UART bit sampling variability, the synchronization is guaranteed to be within only 16 CLK cycles between TPS92661 devices.

Figure 12. PWM Synchronization

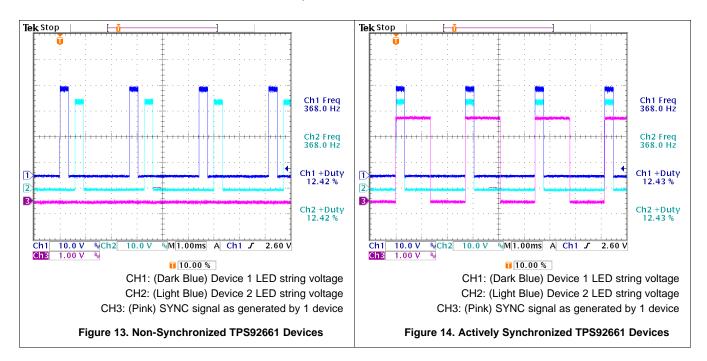

Figure 13 and Figure 14 show an example of two non-synchronized TPS92661 devices and two synchronized devices respectively. In this example all twelve channels on each device are programmed with  $LED_{ON} = 0$  and  $LED_{OFF} = 128$ . In the non-synchronized example TCNT = 0 occurs at two different places in time. By using the SYNC function, TCNT = 0 occurs simultaneously for both devices.

#### 7.3.6 Switch Slew Control

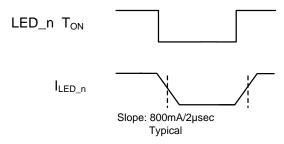

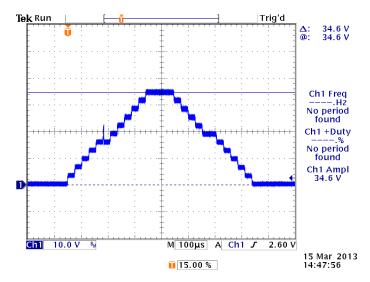

The gate drive control of each series switch slows the rate of change of current through the device. This control eases EMI requirements and aids in the system operation. The switching transition controls the current through the switch at each edge to approximately 800 mA/2 µs. The internal circuitry of the device controls the slew rate. The user cannot change the slew rate. The rise and fall slew rates are matched to ensure accurate representation of the PWM duty cycle. These slew rates assume no LED string capacitance.

Figure 15. TPS92661 Slew Rate Control

## 7.3.7 Effect of Phase Shifting LED Duty Cycles

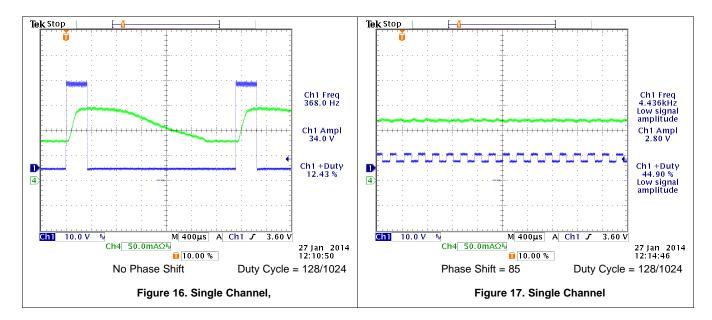

Figure 16 and Figure 17 show the effective system input current (CH4, green trace) and  $V_{(LED12-LED0)}$  string voltage (CH1, blue trace) for various phase shift settings. The results illustrate the advantages of adjusting the phase shift value to minimize the variation in input current. Figure 16 illustrates a zero phase shift condition by setting all twelve LEDxON values to zero and all twelve LEDxOFF values to 128. Figure 17 illustrates optimal phase shifting where all twelve LEDxON values are spaced by a count of 85 (0, 85, 170, 235, ...). The input current variation is greatly reduced with optimal phase shifting as all twelve channels do not draw current from the input simultaneously. This reduces demands on the energy storage capacitance at the system input.

#### 7.3.8 LED Fault Detection and Protection

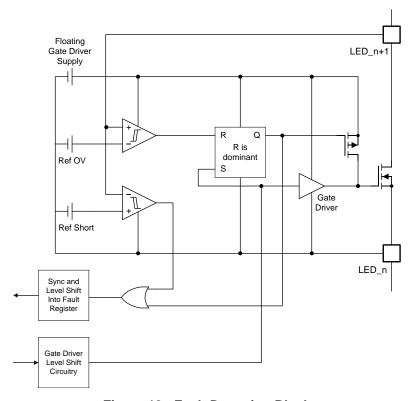

Each individual bypass switch is driven by a floating driver which is powered by the charge pump (see *Functional Block Diagram*). The steady floating driver supply also enables continuous protection and monitoring of LED open and short events.

In the event of an OPEN LED failure, an internal comparator monitors the drain-to-source voltage of the internal switch. If the voltage exceeds  $V_{TH-O}$  (typical 6 V) the device overrides the switch-off signal and turns on the switch. This action maintains current flow in the rest of the LED string in the presence of a faulty or damaged LED and protects the internal switch. The internal latch holds this state until a subsequent on and off cycle at which time the switch attempts to turn off again, and the condition is re-evaluated. The protection circuit also sets the corresponding bit in the FAULT register described in the *Diagnostic Registers* section . The controller can poll this register to determine whether a fault has occurred.

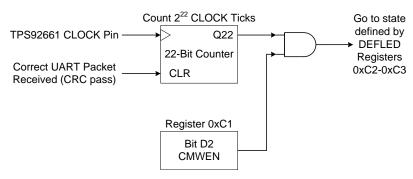

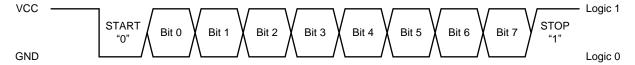

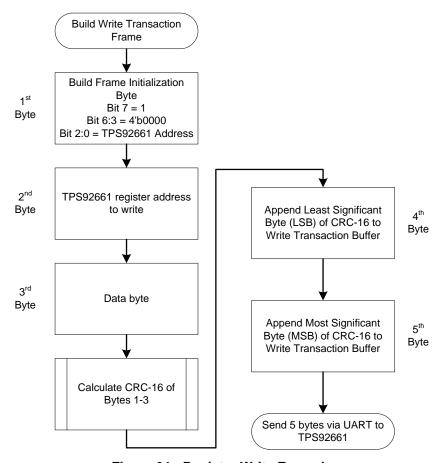

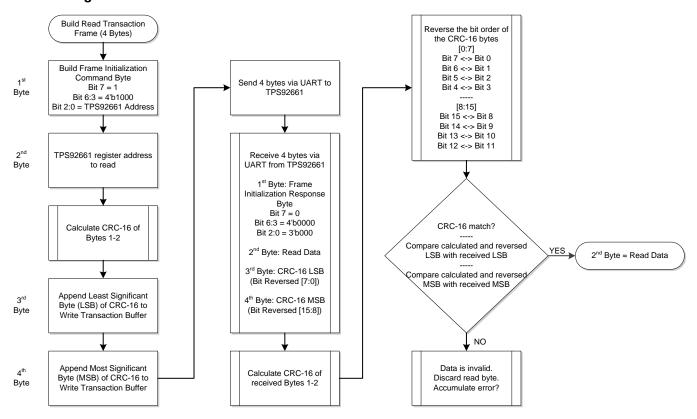

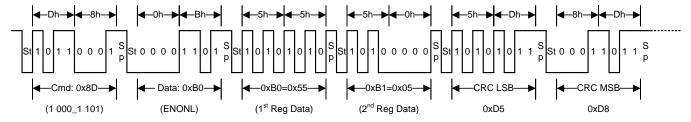

When the device resets a FAULT bit in the register array by writing the bit back to zero, it then clears the latch and re-enables the OPEN switching transition of the corresponding LED. This feature allows the controller to perform multiple checks of the LED fault so that false LED faults can be filtered via software.