**TPS65994AD**

ZHCSLY5A - AUGUST 2020 - REVISED JULY 2021

### 具有集成电源开关、支持 USB4 和交替模式的 USB Type-TPS65994AD 双端口、 C®和 USB PD 控制器

### 1 特性

- 该器件由 USB-IF 进行了 PD3.0 认证

- 认证新的 USB PD 设计时需使用 PD3.0 器件

- TID#: 3495

- 有关 PD2.0 与 PD3.0 的文章

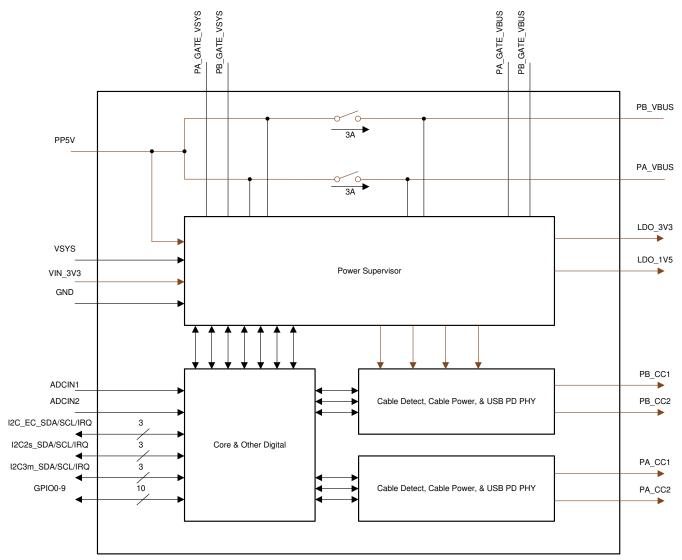

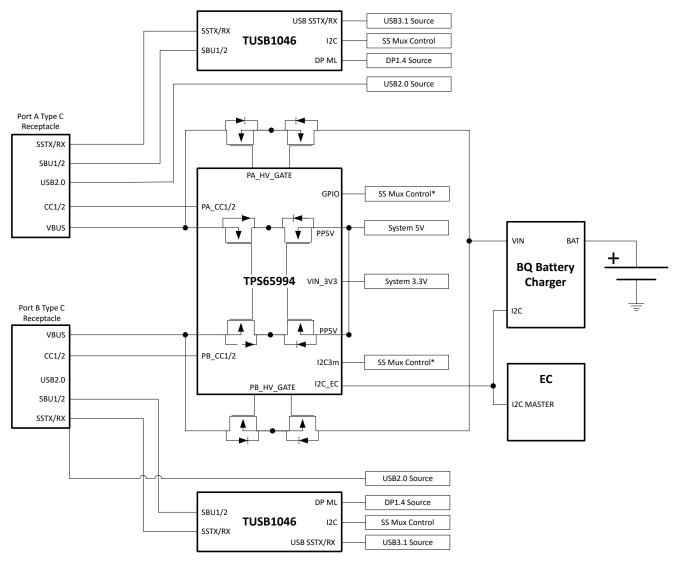

- TPS65994AD 是完全可配置的双端口 USB4 和 Thunderbolt 4 (TBT4) PD3.0 控制器

- 此器件可用于 USB4 主机和器件设计

- 支持工业工作温度范围

- 用于为各种应用轻松配置 TPS65994AD 的 GUI

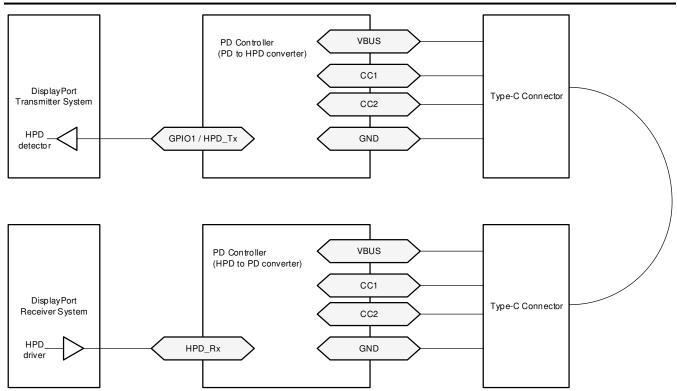

- 支持 DisplayPort 拉电流、Thunderbolt 和用户 可配置交替模式

- 有关更详尽的选择指南和入门信息,请参阅 www.ti.com/usb-c 和 E2E 指南

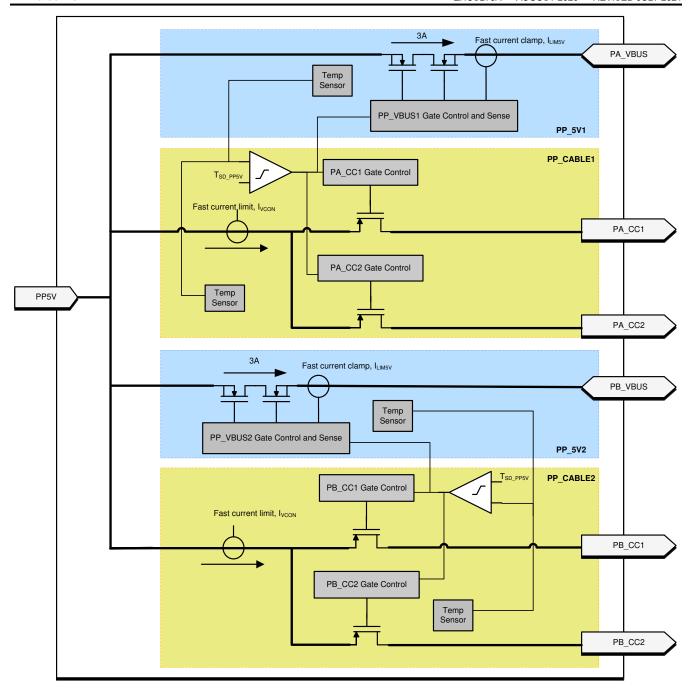

- 完全管理的集成电源路径:

- 集成两个 5V、3A、38m Ω 电源开关

- UL2367 认证编号: E169910

- IEC62368-1 认证编号: US-34737-M3-UL

- 集成强大的电源路径保护

- 为拉电流路径集成了过压保护、欠压保护、反向 电流保护和可调节限流功能

- 为灌电流路径集成了过压保护、欠压保护和反向 电流保护

- USB Type-C® 功率传输 (PD) 控制器

- 10 个可配置 GPIO

- 符合 USB PD 3.0 标准

- 符合 USB Type-C 规范

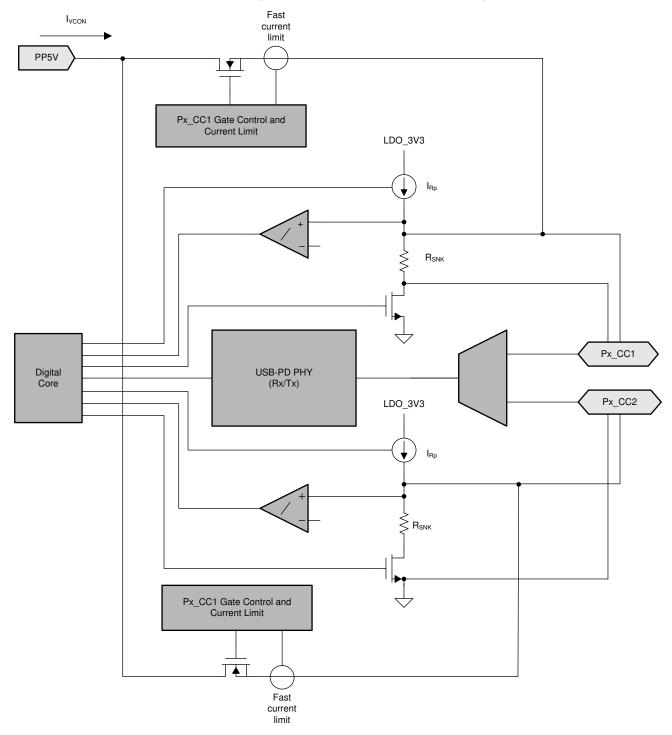

- 线缆连接和方向检测

- 集成式 VCONN 开关

- 集成式无电电池 Rd

- 物理层和策略引擎

- 3.3V LDO 输出,在电池电量耗尽时提供支持

- 通过 3.3V 或 VBUS 源供电

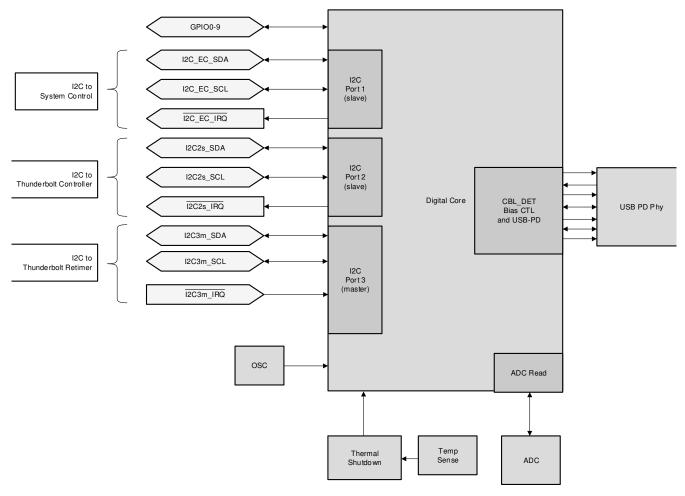

- 1 个 I2C 主端口

- 2 个 I2C 次级端口

# 2 应用

- PC 和笔记本电脑

- 耐用 PC 和笔记本电脑

- 单板计算机

- 集线站

- 平板监视器

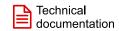

# 3 说明

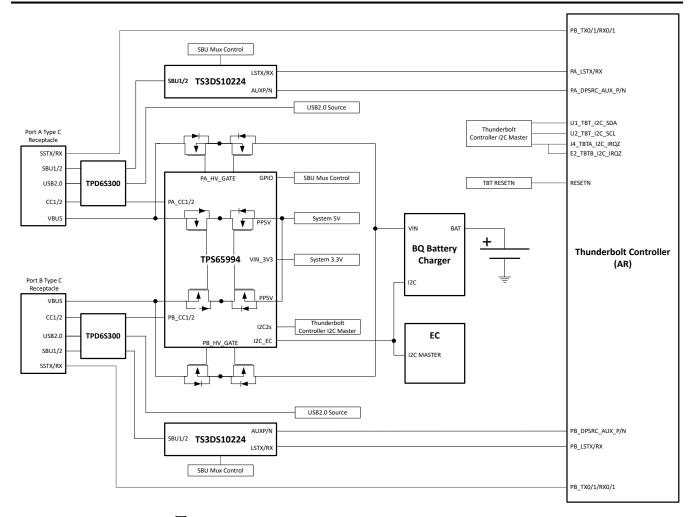

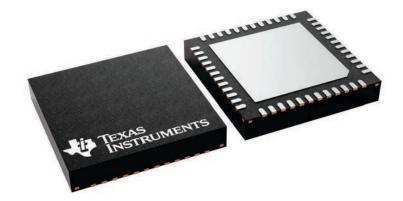

TPS65994AD 是一款高度集成的独立式双端口 USB Type-C 和电力输送 (PD) 控制器,针对 PC 和笔记本 电脑应用进行了优化。TPS65994AD 集成了完全管理 的电源路径与强大的保护功能,可提供完整的 USB-C PD 解决方案。 TPS65994AD Intel 和 AMD 的 PC 和 笔记本电脑终端设备参考设计使用了此器件,确保 PD 控制器在这类设计中提供适当的系统级交互。此功能显 著降低系统设计的复杂性,并缩短上市时间。

### 器件信息

| 器件型号 <sup>(1)</sup> | 封装        | 封装尺寸 ( 标称值 )  |

|---------------------|-----------|---------------|

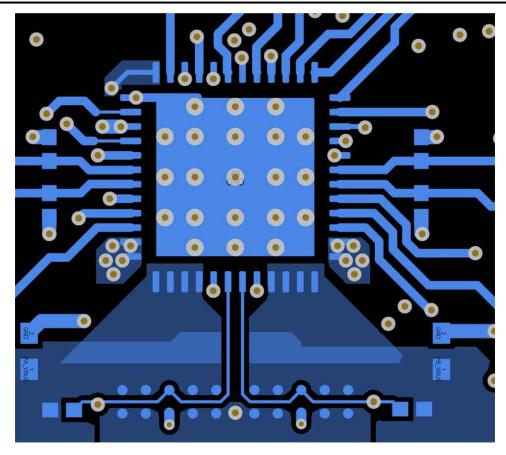

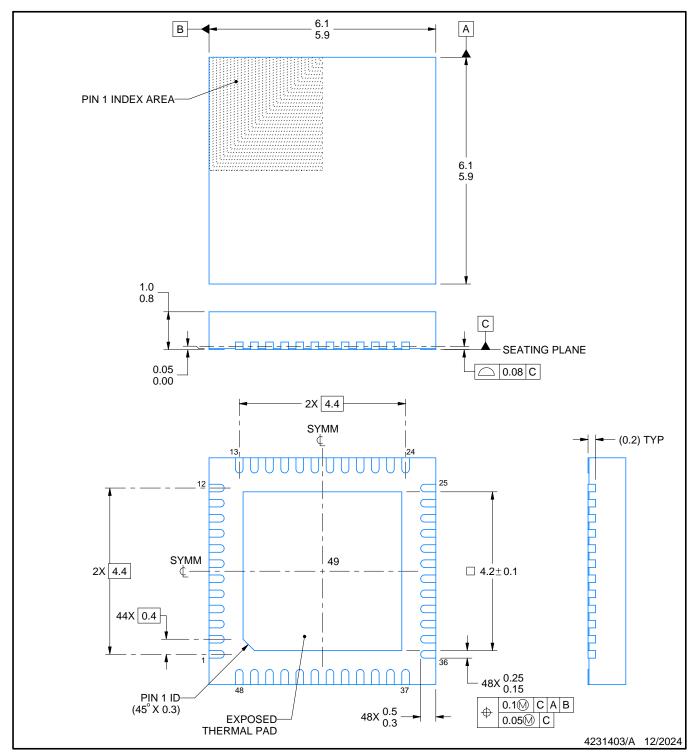

| TPS65994AD          | QFN (RSL) | 6.0mm × 6.0mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

# **Table of Contents**

| 1 特性                                           | 1 | 8.2 Functional Block Diagram                | 19 |

|------------------------------------------------|---|---------------------------------------------|----|

| 2 应用                                           |   | 8.3 Feature Description                     | 20 |

| , <del>, , , , , , , , , , , , , , , , ,</del> |   | 8.4 Device Functional Modes                 | 40 |

| 4 Revision History                             |   | 9 Application and Implementation            | 42 |

| 5 Pin Configuration and Functions              |   | 9.1 Application Information                 | 42 |

| Specifications                                 |   | 9.2 Typical Application                     |    |

| 6.1 Absolute Maximum Ratings                   |   | 10 Power Supply Recommendations             |    |

| 6.2 ESD Ratings                                |   | 10.1 3.3-V Power                            |    |

| 6.3 Recommended Operating Conditions           |   | 10.2 1.5-V Power                            | 49 |

| 6.4 Recommended Capacitance                    |   | 10.3 Recommended Supply Load Capacitance    | 49 |

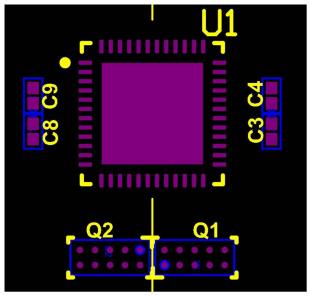

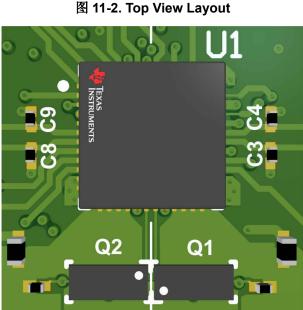

| 6.5 Thermal Information                        |   | 11 Layout                                   | 50 |

| 6.6 Power Supply Characteristics               |   | 11.1 Layout Guidelines                      | 50 |

| 6.7 Power Consumption                          |   | 11.2 Layout Example                         | 50 |

| 6.8 PP_5V Power Switch Characteristics         |   | 11.3 Component Placement                    | 50 |

| 6.9 PP_EXT Power Switch Characteristics        |   | 11.4 Routing PP_5V, VBUS, VIN_3V3, LDO_3V3, |    |

| 6.10 Power Path Supervisory                    |   | LDO_1V5                                     | 52 |

| 6.11 CC Cable Detection Parameters             |   | 11.5 Routing CC and GPIO                    | 54 |

| 6.12 CC VCONN Parameters                       |   | 12 Device and Documentation Support         | 56 |

| 6.13 CC PHY Parameters                         |   | 12.1 Device Support                         |    |

| 6.14 Thermal Shutdown Characteristics          |   | 12.2 Documentation Support                  | 56 |

| 6.15 ADC Characteristics                       |   | 12.3 支持资源                                   | 56 |

| 6.16 Input/Output (I/O) Characteristics        |   | 12.4 Trademarks                             | 56 |

| 6.17 I2C Requirements and Characteristics      |   | 12.5 Electrostatic Discharge Caution        | 56 |

| 6.18 Typical Characteristics                   |   | 12.6 术语表                                    |    |

| 7 Parameter Measurement Information            |   | 13 Mechanical, Packaging, and Orderable     |    |

| B Detailed Description                         |   | Information                                 | 56 |

| 8.1 Overview                                   |   | 13.1 Package Option Addendum                | 57 |

|                                                |   |                                             |    |

# **4 Revision History**

| С | Changes from Revision * (August 2020) to Revision A (July 2021) | Page |

|---|-----------------------------------------------------------------|------|

| • | 更改了 <i>特性</i> 列表                                                | 1    |

| • | 更新了 <i>应用</i> 部分                                                | 1    |

|   | 更新了 <i>说明</i> 部分                                                |      |

# **5 Pin Configuration and Functions**

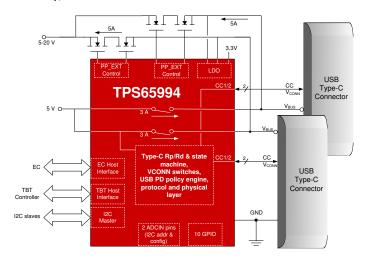

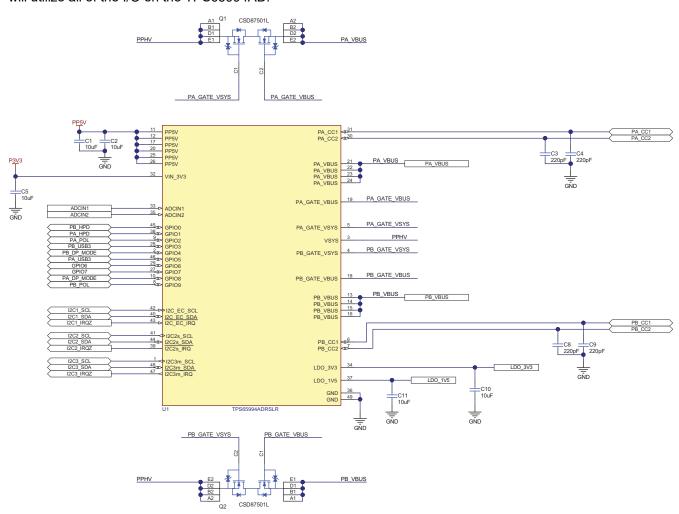

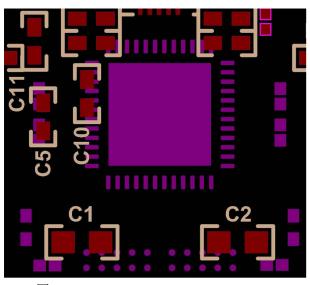

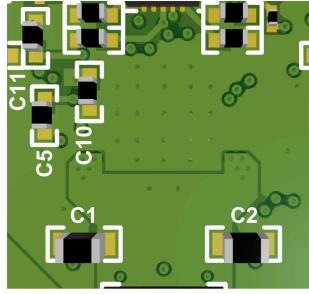

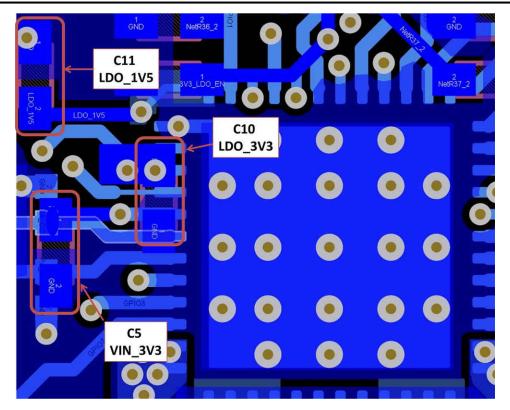

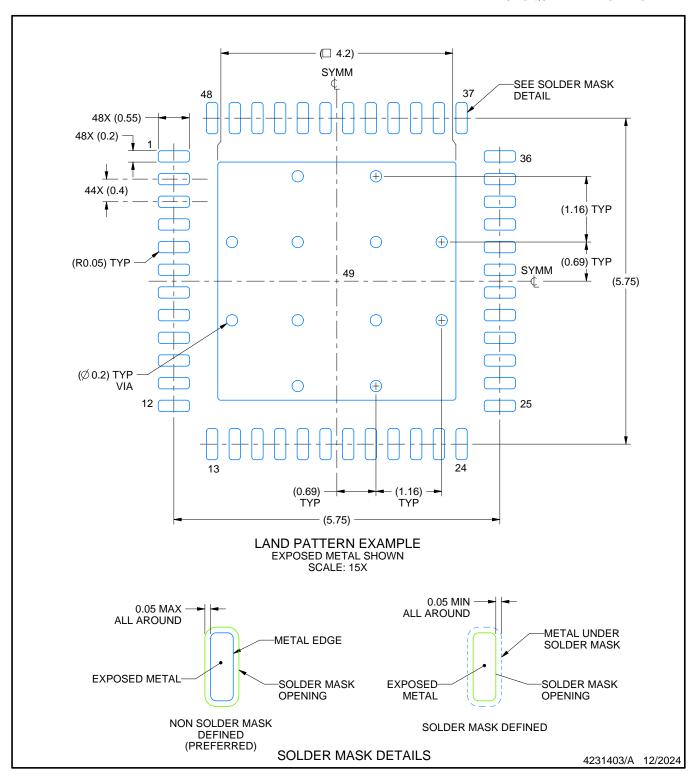

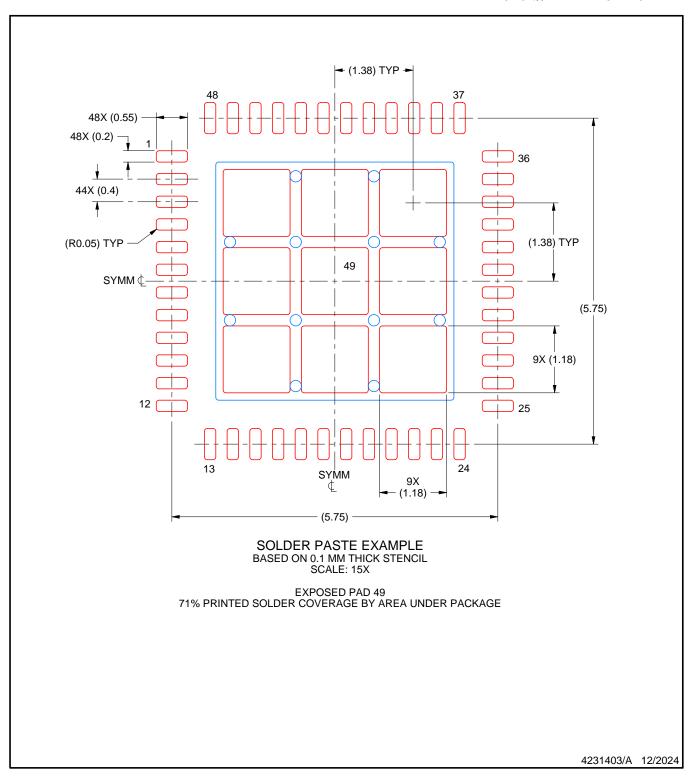

图 5-1. RSL Package 48-pin QFN Top View

表 5-1. Pin Functions

| PIN    |     | TYPE | RESET | Description                                                                                                       |

|--------|-----|------|-------|-------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | ITPE | KESEI | Description                                                                                                       |

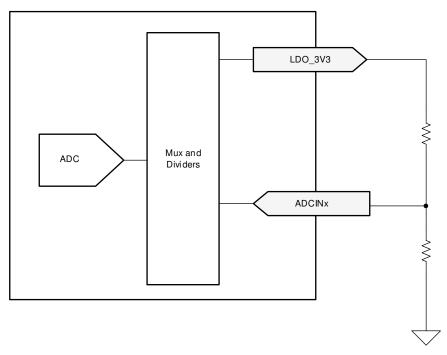

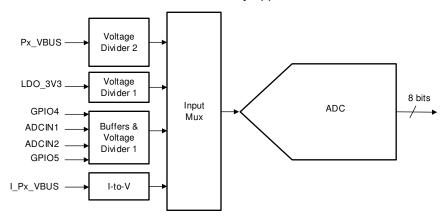

| ADCIN1 | 33  | I    | Hi-Z  | Configuration input. Connect to a resistor divider to LDO_3V3.                                                    |

| ADCIN2 | 35  | I    | Hi-Z  | Configuration input. Connect to a resistor divider to LDO_3V3.                                                    |

| GND    | 36  | _    | _     | Ground. Connect to ground plane.                                                                                  |

| GPIO0  | 45  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused. May be used as DisplayPort HPD signal for Port B. |

| GPIO1  | 38  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused. May be used as DisplayPort HPD signal for Port A. |

| GPIO2  | 9   | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                   |

| GPIO3  | 28  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                   |

| GPIO4  | 2   | I/O  | Hi-Z  | General purpose digital I/O. May be used as an ADC input. Tie to PP5V or ground when unused.                      |

| GPIO5  | 46  | I/O  | Hi-Z  | General purpose digital I/O. May be used as an ADC input. Tie to PP5V or ground when unused.                      |

| GPIO6  | 29  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                   |

| GPIO7  | 27  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                   |

| GPIO8  | 10  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                   |

# 表 5-1. Pin Functions (continued)

| PIN          | l                     |      |       | P                                                                                                                                                                                             |

|--------------|-----------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.                   | TYPE | RESET | Description                                                                                                                                                                                   |

| GPIO9        | 8                     | 0    | Hi-Z  | General purpose digital output. Tie to PP5V or ground when unused.                                                                                                                            |

| I2C_EC_SCL   | 42                    | I    | Hi-Z  | I2C slave serial clock input. Tie to pullup voltage through a resistor. May be grounded if unused. Connect to Embedded Controller (EC).                                                       |

| I2C_EC_SDA   | 40                    | I/O  | Hi-Z  | I2C slave serial data. Open-drain input/output. Tie to pullup voltage through a resistor. May be grounded if unused. Connect to Embedded Controller (EC).                                     |

| I2C_EC_IRQ   | 43                    | 0    | Hi-Z  | I2C slave interrupt. Active low. Connect to external voltage through a pull-up resistor. Connect to Embedded Controller (EC). This can be re-configured to GPIO10. May be grounded if unused. |

| I2C2s_SCL    | 41                    | I    | Hi-Z  | I2C slave serial clock input. Tie to pull-up voltage through a resistor. May be grounded if unused.                                                                                           |

| I2C2s_SDA    | 44                    | I/O  | Hi-Z  | I2C slave serial data. Open-drain input/output. Tie to pullup voltage through a resistor. May be grounded if unused.                                                                          |

| I2C2s_IRQ    | 39                    | 0    | Hi-Z  | I2C slave interrupt. Active low. Connect to external voltage through a pull-up resistor. Tie to PP5V or ground when unused. This can be re-configured to GPIO11.                              |

| I2C3m_SCL    | 1                     | 0    | Hi-Z  | I2C master serial clock. Open-drain output. Tie to pullup voltage through a resistor when used or unused.                                                                                     |

| I2C3m_SDA    | 48                    | I/O  | Hi-Z  | I2C master serial data. Open-drain input/output. Tie to pullup voltage through a resistor when used or unused.                                                                                |

| I2C3m_IRQ    | 47                    | I    | Hi-Z  | I2C master interrupt. Active low. Connect to external voltage through a pull-up resistor. Tie to PP5V or ground when unused. This can be re-configured to GPIO12.                             |

| LDO_1V5      | 37                    | 0    | _     | Output of the CORE LDO. Bypass with capacitance $C_{\text{LDO}\_1V5}$ to GND. This pin cannot source current to external circuits.                                                            |

| LDO_3V3      | 34                    | 0    | _     | Output of supply switched from VIN_3V3 or VBUS LDO. Bypass with capacitance C <sub>LDO_3V3</sub> to GND.                                                                                      |

| PA_CC1       | 31                    | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PA_CC2       | 30                    | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

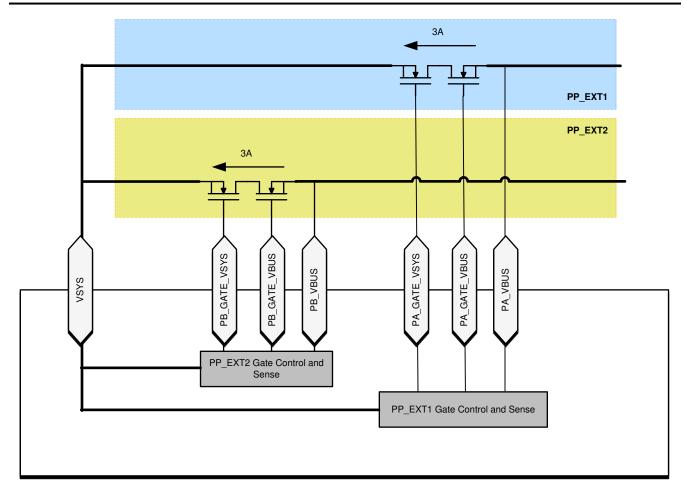

| PA_GATE_VSYS | 5                     | 0    | Hi-Z  | Connect to the PortA N-ch MOSFET that has source tied to VSYS.                                                                                                                                |

| PA_GATE_VBUS | 19                    | 0    | Hi-Z  | Connect to the N-ch MOSFET that has source tied to PA_VBUS.                                                                                                                                   |

| PA_VBUS      | 21,22,23,24           | I/O  | _     | 5-V to 20-V input or 5-V output from PP5V. Bypass with capacitance $C_{\text{VBUS}}$ to GND.                                                                                                  |

| PB_CC1       | 6                     | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PB_CC2       | 7                     | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PB_GATE_VSYS | 4                     | 0    | Hi-Z  | Connect to the Port B N-ch MOSFET that has source tied to VSYS.                                                                                                                               |

| PB_GATE_VBUS | 18                    | 0    | Hi-Z  | Connect to the N-ch MOSFET that has source tied to PB_VBUS.                                                                                                                                   |

| PB_VBUS      | 13,14,15,16           | I/O  | _     | 5-V to 20-V input or 5-V output from PP5V. Bypass with capacitance $C_{\text{VBUS}}$ to GND.                                                                                                  |

| PP5V         | 11,12,17,20,25,<br>26 | I    | _     | 5-V System Supply to VBUS, supply for Px_CCy pins as VCONN.                                                                                                                                   |

| VSYS         | 3                     | I    | _     | High-voltage sinking node in the system. It is used to implement reverse-<br>current-protection (RCP) for the external sinking paths controlled by<br>PA_GATE_VSYS and PB_GATE_VSYS.          |

| VIN_3V3      | 32                    | I    | _     | Supply for core circuitry and I/O. Bypass with capacitance C <sub>VIN_3V3</sub> to GND.                                                                                                       |

# **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                         |                                                                                                     | MIN                                           | MAX | UNIT |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|--|

|                                         | PP5V                                                                                                | - 0.3                                         | 6   |      |  |

|                                         | VIN_3V3                                                                                             | - 0.3                                         | 4   | V    |  |

|                                         | ADCIN1, ADCIN2                                                                                      | - 0.3                                         | 4   |      |  |

|                                         | VSYS, PA_VBUS, PB_VBUS (4)                                                                          | - 0.3                                         | 28  |      |  |

| Input voltage range <sup>(2)</sup>      | PA_CC1, PA_CC2, PB_CC1, PB_CC2                                                                      | - 0.5                                         | 6   |      |  |

|                                         | GPIO0-GPIO9, I2C_EC_IRQ, I2C2s_IRQ, I2C3m_IRQ                                                       | -0.3                                          | 6   | V    |  |

|                                         | I2C_EC_SDA, I2C_EC_SCL,I2C2s_SDA,<br>I2C2s_SCL, I2C3m_SDA, I2C3m_SCL                                | - 0.3                                         | 4   |      |  |

| 2                                       | LDO_1V5 <sup>(3)</sup>                                                                              | - 0.3                                         | 2   |      |  |

| Output voltage range <sup>(2)</sup>     | LDO_3V3 <sup>(3)</sup>                                                                              | - 0.3                                         | 4   | V    |  |

| Output voltage range <sup>(2)</sup>     | PA_GATE_VBUS, PA_GATE_VSYS, PB_GATE_VBUS, PB_GATE_VSYS (3)                                          | - 0.3                                         | 40  | V    |  |

| $V_{GS}$                                | V <sub>Px_GATE_VBUS</sub> - V <sub>Px_VBUS</sub> , V <sub>Px_GATE_SYS</sub> - V <sub>VSYS</sub>     | - 0.5                                         | 12  | V    |  |

|                                         | Source or sink current PA_VBUS, PB_VBUS                                                             | internally limited                            |     |      |  |

|                                         | Positive source current on PA_CC1, PA_CC2, PB_CC1, PB_CC2                                           |                                               | 1   |      |  |

| Source current                          | Positive sink current on PA_CC1, PA_CC2, PB_CC1, PB_CC2 while VCONN switch is enabled               | 0.005  internally limited  internally limited |     | A    |  |

|                                         | GPIO0-GPIO9                                                                                         |                                               |     |      |  |

|                                         | positive sink current for I2C_EC_SDA,<br>I2C_EC_SCL, I2C2s_SDA, I2C2s_SCL,<br>I2C3m_SDA, I2C3m_SCL, |                                               |     |      |  |

|                                         | positive source current for LDO_3V3, LDO_1V5                                                        |                                               |     |      |  |

| Γ <sub>J</sub> Operating junction tempe | erature                                                                                             | - 40                                          | 175 | °C   |  |

| Γ <sub>STG</sub> Storage temperature    |                                                                                                     | - 55                                          | 150 | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

- (2) All voltage values are with respect to network GND. Connect the GND pin directly to the GND plane of the board.

- (3) Do not apply voltage to these pins.

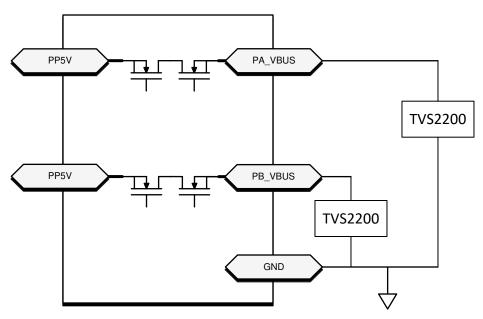

- (4) For Px\_VBUS a TVS with a break down voltage falling between the Recommended max and the Abs max value is recommended such as TVS2200. For Px\_VBUS a Schottky diode is recommended to ensure the MIN voltage is not violated.

# 6.2 ESD Ratings

|                    | PARAMETER               | TEST CONDITIONS                                                                         | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>         | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                  |                                                                                                                                                   | MIN  | MAX | UNIT |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                 |                                  | VIN_3V3                                                                                                                                           | 3.0  | 3.6 |      |

| VI              | Input voltage range (1)          | PP5V <sup>(2)</sup>                                                                                                                               | 4.9  | 5.5 | V    |

|                 |                                  | PA_VBUS, PB_VBUS (3)                                                                                                                              | 4    | 22  |      |

| VI              | Input voltage range (1)          | VSYS                                                                                                                                              | 0    | 22  | V    |

|                 |                                  | I2Cx_SDA, I2Cx_SCL, ADCIN1,<br>ADCIN2                                                                                                             | 0    | 3.6 |      |

| V <sub>IO</sub> | I/O voltage range <sup>(1)</sup> | GPIOx, IZC_EC_IRQ, IZC2s_IRQ, IZC3m_IRQ                                                                                                           | 0    | 5.5 | V    |

|                 |                                  | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2                                                                                                                 | 0    | 5.5 |      |

|                 |                                  | PA_VBUS, PB_VBUS                                                                                                                                  |      | 3   | Α    |

| l <sub>o</sub>  | Output current (from PP5V)       | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2                                                                                                                 |      | 315 | mA   |

| Io              | Output current (from LDO_3V3)    | GPIOx                                                                                                                                             |      | 1   | mA   |

| Io              | Output current (from VBUS LDO)   | sum of current from LDO_3V3 and GPIO0-9.                                                                                                          |      | 5   | mA   |

| T <sub>A</sub>  | Ambient operating temperature    | $\begin{split} I_{PP\_5Vx} \leqslant 1.5 \text{ A, } I_{PP\_5Vy} \leqslant 3.0 \text{ A,} \\ I_{PP\_CABLEx} \leqslant 315 \text{ mA} \end{split}$ | - 40 | 105 | °C   |

| 'A              | Ambient operating temperature    | $I_{PP\_5Vx} \leqslant 3.0 \text{ A, } I_{PP\_CABLEx} \leqslant 315 \text{ mA}$                                                                   | - 40 | 85  | Ü    |

| TJ              | Operating junction temperature   |                                                                                                                                                   | - 40 | 125 | °C   |

- (1) All voltage values are with respect to network GND. All GND pins must be connected directly to the GND plane of the board.

- (2) Maximum current sourced from PP5V to PA\_VBUS or PB\_VBUS. Resistance from Px\_VBUS to Type-C connector less than or equal 30 mΩ. Short all PP5V bumps together.

- (3) All PA\_VBUS bumps should be shorted together. All PB\_VBUS bumps should be shorted together.

### 6.4 Recommended Capacitance

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER <sup>(1)</sup>                  | VOLTAGE RATING | MIN                | NOM | MAX | UNIT |

|----------------------|-------------------------------------------|----------------|--------------------|-----|-----|------|

| C <sub>VIN_3V3</sub> | Capacitance on VIN_3V3                    | 6.3 V          | 5                  | 10  |     | μF   |

| C <sub>LDO_3V3</sub> | Capacitance on LDO_3V3                    | 6.3 V          | 5                  | 10  | 25  | μF   |

| C <sub>LDO_1V5</sub> | Capacitance on LDO_1V5                    | 4 V            | 4.5                |     | 12  | μF   |

| C <sub>Px_VBUS</sub> | Capacitance on VBUS <sup>(4)</sup>        | 25 V           | 1                  | 4.7 | 10  | μF   |

| C <sub>PP5V</sub>    | Capacitance on PP5V                       | 10 V           | 120 <sup>(2)</sup> |     |     | μF   |

| C <sub>VSYS</sub>    | Capacitance on VSYS Sink from VBUS        | 25 V           |                    | 47  | 100 | μF   |

| C <sub>Px_CCy</sub>  | Capacitance on Px_CCy pins <sup>(3)</sup> | 6.3 V          | 200                | 320 | 480 | pF   |

- (1) Capacitance values do not include any derating factors. For example, if 5.0 μF is required and the external capacitor value reduces by 50% at the required operating voltage, then the required external capacitor value would be 10 μF.

- (2) This is a requirement from USB PD (cSrcBulkShared). Keep at least 10 µF tied directly to PP5V.

- (3) This includes all capacitance to the Type-C receptacle.

- (4) The device can be configured to quickly disable PP\_EXT upon certain events. When such a configuration is used, a capacitance on the higher side of this range is recommended.

#### 6.5 Thermal Information

|                         |                                           | DEVICE    |      |

|-------------------------|-------------------------------------------|-----------|------|

| THERM                   | AL METRIC                                 | QFN (RSL) | UNIT |

|                         |                                           | 48 PINS   |      |

| R <sub>0</sub> JA       | Junction-to-ambient thermal resistance    | 26.8      | °C/W |

| R <sub>θ JC</sub> (top) | Junction-to-case (top) thermal resistance | 15.4      | °C/W |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.5 Thermal Information (continued)

|                            |                                                      | DEVICE    |      |

|----------------------------|------------------------------------------------------|-----------|------|

|                            | THERMAL METRIC                                       | QFN (RSL) | UNIT |

|                            |                                                      | 48 PINS   |      |

| R <sub> θ</sub> JB         | Junction-to-board thermal resistance                 | 8.5       | °C/W |

| ψ <sub>JT</sub>            | Junction-to-top characterization parameter           | 0.2       | °C/W |

| ψ ЈВ                       | Junction-to-board characterization parameter         | 8.5       | °C/W |

| R <sub>θ JC</sub> (bottom) | Junction-to-case (bottom GND pad) thermal resistance | 1.8       | °C/W |

# **6.6 Power Supply Characteristics**

Operating under these conditions unless otherwise noted: 3.0 V  $\leqslant$  V<sub>VIN 3V3</sub>  $\leqslant$  3.6 V

| UNIT |  |

|------|--|

|      |  |

| 6    |  |

| ı v  |  |

|      |  |

| 9    |  |

| 3 V  |  |

|      |  |

|      |  |

| S V  |  |

| 5 Ω  |  |

| V    |  |

| 3.6  |  |

# **6.7 Power Consumption**

Operating under these conditions unless otherwise noted: 3.0 V  $\leqslant$  V<sub>VIN\_3V3</sub>  $\leqslant$  3.6 V, no loading on GPIO pins

| PA                          | RAMETER                                                               | TEST CONDITIONS                                                                                                                                          | MIN | TYP | MAX | UNIT |

|-----------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>VIN_3V3,ActSrc</sub> | current into VIN_3V3                                                  | Active Source mode: V <sub>PP5V</sub> =5.0V, V <sub>VIN_3V3</sub> =3.3V                                                                                  |     | 4.5 | 12  | mA   |

| I <sub>VIN_3V3,ActSnk</sub> | current into VIN_3V3                                                  | Active Sink mode: $22V \geqslant V_{PA\_VBUS} \geqslant 4.0V$ , $22V \geqslant V_{PB\_VBUS} \geqslant 4.0V$ , $V_{VIN\_3V3} = 3.3V$                      |     | 4.8 | 12  | mA   |

| I <sub>VSYS</sub>           | current into VSYS                                                     |                                                                                                                                                          |     | 10  |     | μΑ   |

| I <sub>VIN_3V3,IdlSrc</sub> | current into VIN_3V3                                                  | Idle Source mode: V <sub>PA_VBUS</sub> =5.0V, V <sub>PB_VBUS</sub> =5.0V, V <sub>VIN_3V3</sub> =3.3V                                                     |     | 1.1 |     | mA   |

| I <sub>VIN_3V3,IdISnk</sub> | current into VIN_3V3                                                  | Idle Sink mode: 22V $\geqslant$ V <sub>PA_VBUS</sub> $\geqslant$ 4.0V, 22V $\geqslant$ V <sub>PB_VBUS</sub> $\geqslant$ 4.0V, V <sub>VIN_3V3</sub> =3.3V |     | 1.1 |     | mA   |

| P <sub>MstbySnk</sub>       | Power drawn into PP5V<br>and VIN_3V3 in Modern<br>Standby Sink Mode   | Modern Standby Sink Mode: V <sub>PP5V</sub> = 5V, V <sub>VIN_3V3</sub> =3.3V, V <sub>PA_VBUS</sub> =5.0V, V <sub>PB_VBUS</sub> =0V                       |     | 3.7 |     | mW   |

| P <sub>MstbySrc</sub>       | Power drawn into PP5V<br>and VIN_3V3 in Modern<br>Standby Source Mode | Modern Standby Source Mode: V <sub>PP5V</sub> = 5V, V <sub>VIN_3V3</sub> =3.3V, I <sub>Px_VBUS</sub> =0                                                  |     | 4.5 |     | mW   |

| I <sub>VIN_3V3,Sleep</sub>  | current into VIN_3V3                                                  | Sleep mode: $V_{PA\_VBUS}$ =0V, $V_{PB\_VBUS}$ =0V, $V_{VIN\_3V3}$ =3.3V, $T_J$ $\leq 25$ °C                                                             |     | 67  |     | μΑ   |

# 6.8 PP\_5V Power Switch Characteristics

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6V

|                        | PARAMETER                                                                                                                                                                  | TEST CONDITIONS                                                                                                                                                                                                                                                                                                    | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

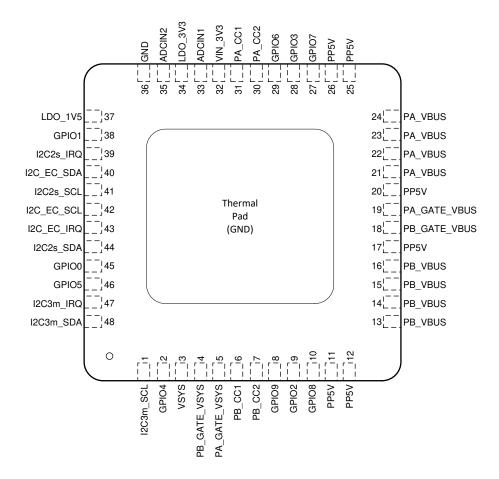

| D.                     | Desistance from DD5V4+ Des VD10                                                                                                                                            | I <sub>LOAD</sub> = 3 A, T <sub>J</sub> ≤25°C                                                                                                                                                                                                                                                                      |      | 37.7 | 41.5 | -    |

| $R_{PP_{.5}V}$         | Resistance from PP5V to Px_VBUS                                                                                                                                            | I <sub>LOAD</sub> = 3 A, T <sub>J</sub> ≤125°C                                                                                                                                                                                                                                                                     |      | 37.7 | 57   | mΩ   |

| IPP5V_REV              | Px_VBUS to PP5V leakage current                                                                                                                                            | $V_{PP5V} = 0V, V_{Px\_VBUS} = 5.5V, PP\_5V disabled, T_J \leq 85^{\circ}C, measure I_{PP5V}$                                                                                                                                                                                                                      |      | 0    | 3    | μА   |

| PP5V_FWD               | PP5V to Px_VBUS leakage current                                                                                                                                            | $V_{PP5V}$ = 5.5V, $V_{Px\_VBUS}$ = 0V, $PP\_5V$ disabled, $T_J \le 85^{\circ}C$ , measure $I_{Px\ VBUS}$                                                                                                                                                                                                          |      | 0    | 15   | μА   |

| LIM5V                  | Current limit setting                                                                                                                                                      | Configure to setting 0                                                                                                                                                                                                                                                                                             | 1.15 |      | 1.36 | Α    |

| LIM5V                  | Current limit setting                                                                                                                                                      | configure to setting 1                                                                                                                                                                                                                                                                                             | 1.61 |      | 1.90 | Α    |

| I <sub>LIM5V</sub>     | Current limit setting                                                                                                                                                      | configure to setting 2                                                                                                                                                                                                                                                                                             | 2.3  |      | 2.70 | Α    |

| I <sub>LIM5V</sub>     | Current limit setting                                                                                                                                                      | configure to setting 3                                                                                                                                                                                                                                                                                             | 3.04 |      | 3.58 | Α    |

| I <sub>LIM5V</sub>     | Current limit setting                                                                                                                                                      | configure to setting 4                                                                                                                                                                                                                                                                                             | 3.22 |      | 3.78 | Α    |

| I <sub>Px_VBUS</sub>   | PP5V to Px_VBUS current sense accuracy                                                                                                                                     | $3.0A \geqslant I_{Px\_VBUS} \geqslant 1A,$ $V_{VIN\_3V3}=3.3V$                                                                                                                                                                                                                                                    | 2.8  | 3.4  | 4.1  | A/V  |

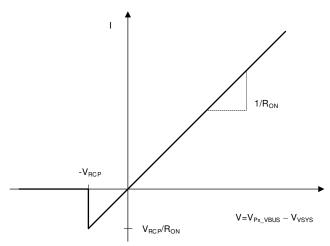

| V <sub>PP_5V_RCP</sub> | RCP clears and PP_5Vx starts<br>turning on when V <sub>Px_VBUS</sub> - V <sub>PP5V</sub> <<br>V <sub>PP_5V_RCP</sub> . Measure V <sub>Px_VBUS</sub> -<br>V <sub>PP5V</sub> |                                                                                                                                                                                                                                                                                                                    | 10   | 15   | 20   | mV   |

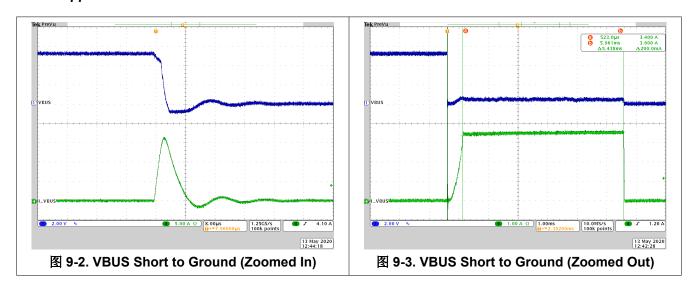

| t <sub>iOS_PP_5V</sub> | response time to VBUS short circuit                                                                                                                                        | Px_VBUS to GND through $10m \Omega$ , $C_{Px_VBUS}=0$                                                                                                                                                                                                                                                              |      | 1.15 |      | μs   |

| tPP_5V_ovp             | response time to V <sub>Px_VBUS</sub> > V <sub>OVP4RCP</sub>                                                                                                               | Enable PP_5Vx, ramp<br>V <sub>Px_VBUS</sub> from 4V to 20V at<br>100 V/ms                                                                                                                                                                                                                                          |      | 4.5  |      | μs   |

| tPP_5V_uvlo            | response time to $V_{PP5V} < V_{PP5V\_UVLO}$ , $PP\_VBUS$ is deemed off when $V_{Px\_VBUS} < 0.8V$                                                                         | R <sub>L</sub> = 100 Ω, no external capacitance on Px_VBUS                                                                                                                                                                                                                                                         |      | 4    |      | μs   |

| PP_5V_rcp              | response time to V <sub>PP5V</sub> < V <sub>Px_VBUS</sub> +V <sub>PP_5V_RCP</sub>                                                                                          | V <sub>PP5V</sub> =5.5V,enable<br>PP_5Vx, ramp V <sub>Px_VBUS</sub><br>from 4V to 21.5V at 10 V/µs                                                                                                                                                                                                                 |      | 0.7  |      | μs   |

| FRS_on                 | Time allowed to enable the pass FET in PP_5Vx with 3A current limit.                                                                                                       | $\begin{split} & \text{Initial V}_{\text{Px\_VBUS}} = \text{0V, 2}\mu\text{F} \\ & \leqslant C_{\text{Px\_VBUS}} \leqslant 20\mu\text{F, 0} \leqslant \\ & \text{I}_{\text{Px\_VBUS}} \leqslant 0.5 \text{ A, FET is} \\ & \text{deemed enabled when} \\ & \text{V}_{\text{Px\_VBUS}} > 4.75\text{V.} \end{split}$ |      | 54   | 150  | μs   |

| t <sub>ILIM</sub>      | Current clamping deglitch time                                                                                                                                             |                                                                                                                                                                                                                                                                                                                    |      | 5    |      | ms   |

| t <sub>on</sub>        | from enable signal to Px_VBUS at 90% of final value                                                                                                                        | $R_L = 100 \Omega$ , $V_{PP5V} = 5V$ , $C_L = 0$                                                                                                                                                                                                                                                                   | 2.6  | 3.5  | 4.4  | ms   |

| OFF                    | from disable signal to Px_VBUS at 10% of final value                                                                                                                       | $R_L = 100 \Omega$ , $V_{PP5V} = 5V$ , $C_L = 0$                                                                                                                                                                                                                                                                   | 0.30 | 0.45 | 0.6  | ms   |

| RISE                   | Px_VBUS from 10% to 90% of final value                                                                                                                                     | $R_L = 100 \Omega$ , $V_{PP5V} = 5V$ , $C_L = 0$                                                                                                                                                                                                                                                                   | 1.2  | 1.7  | 2.2  | ms   |

| FALL                   | Px_VBUS from 90% to 10% of initial value                                                                                                                                   | $R_L = 100 \Omega$ , $V_{PP5V} = 5V$ , $C_L=0$                                                                                                                                                                                                                                                                     | 0.06 | 0.1  | 0.14 | ms   |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.9 PP\_EXT Power Switch Characteristics

Operating under these conditions unless otherwise noted: 3.0 V  $\leqslant$  V<sub>VIN\_3V3</sub>  $\leqslant$  3.6 V

|                                | PARAMETER                                                                                         | TEST CONDITIONS                                                                                                                                                                                               | MIN  | TYP | MAX  | UNIT        |

|--------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------------|

| 1                              | Cate driver coursing current                                                                      | $\begin{array}{l} 0 \leqslant V_{Px\_GATE\_VSYS} - V_{VSYS} \\ \leqslant 6 \text{ V, 0 V} \leqslant V_{VSYS} \leqslant 22 \\ \text{V, V}_{Px\_VBUS} > 4 \text{ V, measure} \\ I_{Px\_GATE\_VSYS} \end{array}$ | 8.5  | 10  | 11.5 | μΑ          |

| Px_gate_on                     | Gate driver sourcing current                                                                      | $\begin{array}{c} 0 \leqslant V_{Px\_GATE\_VBUS^-} \\ V_{Px\_VBUS} \leqslant 6 \text{ V, 4 V} \leqslant \\ V_{Px\_VBUS} \leqslant 22 \text{ V, measure} \\ I_{Px\_GATE\_VBUS} \end{array}$                    | 8.5  | 10  | 11.5 | μΑ          |

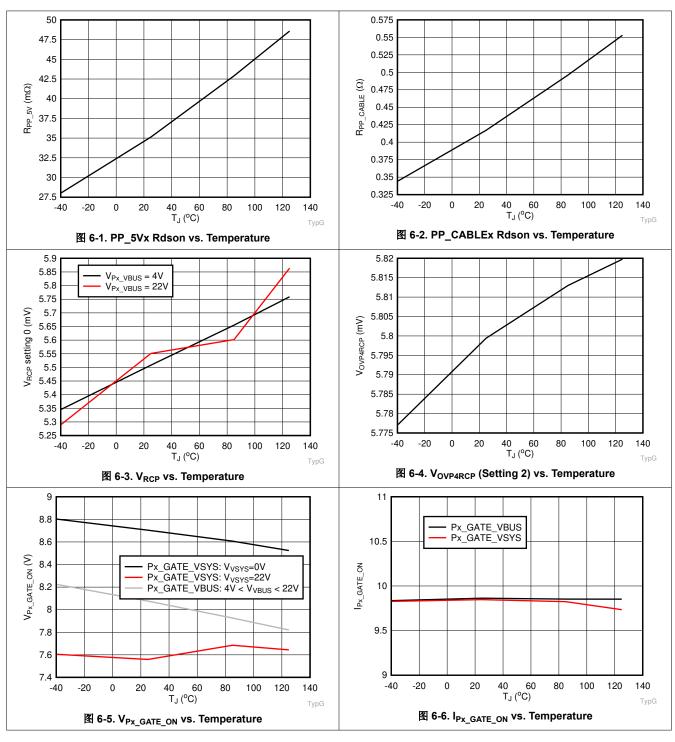

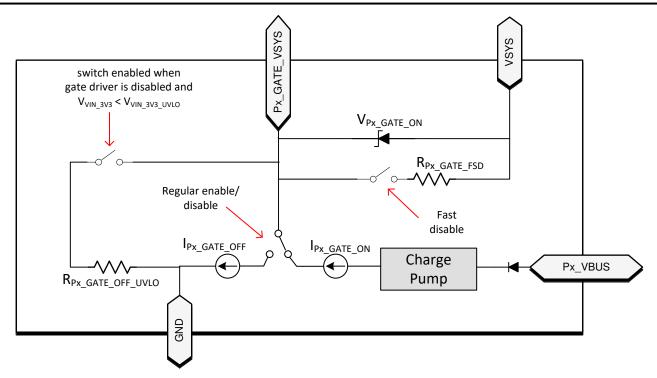

| V <sub>Px_</sub> gate_on       | sourcing voltage (ON)                                                                             | $\begin{array}{l} 0 \leqslant V_{VSYS} \leqslant 22 \text{ V,} \\ I_{Px\_GATE\_VSYS} \leqslant 4  \mu\text{A,} \\ \text{measure } V_{Px\_GATE\_VSYS}  - \\ V_{VSYS}, V_{Px\_VBUS} > 4 \text{ V.} \end{array}$ | 6    |     | 12   | V           |

|                                |                                                                                                   | $ \begin{array}{l} 4~V \leqslant V_{Px\_VBUS} \leqslant 22~V, \\ I_{Px\_GATE\_VBUS} < 4~\mu A, \\ measure~V_{Px\_GATE\_VBUS}~ \\ V_{Px\_VBUS}. \end{array} $                                                  | 6    |     | 12   | V           |

| V <sub>RCP</sub>               |                                                                                                   | setting 0, 4 V $\leqslant$ V <sub>Px_VBUS</sub> $\leqslant$ 22 V, V <sub>VIN_3V3</sub> $\leqslant$ 3.63 V                                                                                                     | 2    | 6   | 10   | mV          |

|                                | comparator mode RCP threshold,                                                                    | setting 1, 4 V $\leqslant$ V <sub>Px_VBUS</sub> $\leqslant$ 22 V, V <sub>VIN_3V3</sub> $\leqslant$ 3.63 V                                                                                                     | 4    | 8   | 12   | mV          |

|                                | V <sub>VSYS</sub> - V <sub>Px_VBUS</sub> .                                                        | $ \begin{array}{l} \text{setting 2, 4 V} \leqslant \\ V_{\text{Px\_VBUS}} \leqslant 22 \text{ V,} \\ V_{\text{VIN\_3V3}} \leqslant 3.63 \text{ V} \end{array} $                                               | 6    | 10  | 14   | mV          |

|                                |                                                                                                   |                                                                                                                                                                                                               | 8    | 12  | 16   | mV          |

|                                |                                                                                                   | normal turnoff: $V_{VSYS} = 5V$ , $V_{Px\_GATE\_VSYS} = 6V$                                                                                                                                                   | 13   |     |      | μΑ          |

| Px_GATE_OFF                    | Sinking strength                                                                                  | normal turnoff: $V_{Px\_VBUS} = 5V$ , $V_{Px\_GATE\_VBUS} = 6V$ , $V_{VSYS} = 5V$                                                                                                                             | 13   |     |      | μΑ          |

|                                |                                                                                                   | fast turnoff: V <sub>VSYS</sub> = 5V,<br>V <sub>Px_GATE_VSYS</sub> =6V,                                                                                                                                       |      |     | 85   | Ω           |

| $R_{Px\_GATE\_FSD}$            | Sinking strength                                                                                  | fast turnoff: V <sub>PX_VBUS</sub> = 5V,<br>V <sub>PX_GATE_VBUS</sub> =6V, V <sub>VSYS</sub> =<br>5 V                                                                                                         |      |     | 85   | Ω           |

| R <sub>Px_GATE_OFF_UVLO</sub>  | Sinking strength in UVLO (safety)                                                                 | V <sub>VIN_3V3</sub> =0V,<br>V <sub>PX_VBUS</sub> =3.0V,<br>V <sub>PX_GATE_VSYS</sub> =0.1V                                                                                                                   |      |     | 1.5  | ΜΩ          |

|                                | soft start slew rate for Px_GATE_VSYS, setting 0                                                  |                                                                                                                                                                                                               | 0.35 |     | 0.47 |             |

| SS                             | soft start slew rate for Px_GATE_VSYS, setting 1                                                  | $4 \text{ V} \leq \text{V}_{\text{Px\_VBUS}} \leq 22 \text{ V},$<br>$500 \text{pF} < \text{C}_{\text{Px\_GATE\_VSYS}} <$                                                                                      | 0.67 |     | 0.91 | <b>N</b> // |

|                                | soft start slew rate for Px_GATE_VSYS, setting 2                                                  | 16 nF, measure slope from<br>10% to 90% of final<br>Px GATE VSYS value,                                                                                                                                       | 1.33 |     | 1.83 | V/ms        |

|                                | soft start slew rate for Px_GATE_VSYS, setting 3                                                  |                                                                                                                                                                                                               | 2.88 |     | 3.90 |             |

| t <sub>Px_GATE_</sub> VBUS_OFF | Time allowed to disable the external FET via Px_GATE_VBUS in normal shutdown mode. <sup>(1)</sup> | V <sub>Px_VBUS</sub> =20V, Gate is off when V <sub>GS</sub> < 1 V                                                                                                                                             |      | 260 |      | μs          |

# **6.9 PP\_EXT Power Switch Characteristics (continued)**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

|                               | PARAMETER                                                                                                                       | TEST CONDITIONS                                                                                                                                    | MIN | TYP  | MAX | UNIT |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>Px_GATE_VBUS_OVP</sub> | Time allowed to disable the external FET via Px_GATE_VBUS in fast shutdown mode (V <sub>OVP4RCP</sub> exceeded). <sup>(1)</sup> | OVP: $V_{OVP4RCP}$ = setting 57, $V_{P_X VBUS}$ =20V initially, then raised to 23V in 50ns, Gate is off when $V_{GS}$ < 1 V                        |     | 3    |     | μs   |

| tpx_gate_vbus_rcp             | Time allowed to disable the external FET via Px_GATE_VBUS in fast shutdown mode (V <sub>RCP</sub> exceeded). <sup>(1)</sup>     | RCP: $V_{RCP}$ = setting 0,<br>$V_{PX\_VBUS}$ =5V, $V_{VSYS}$ =5V<br>initially, then raised to 5.5V<br>in 50ns, Gate is off when<br>$V_{GS}$ < 1 V |     | 1.2  |     | μs   |

| t <sub>Px_GATE_VSYS_OFF</sub> | Time allowed to disable the external FET via Px_GATE_VSYS in normal shutdown mode <sup>(1)</sup>                                | V <sub>VSYS</sub> =20V, Gate is off when V <sub>GS</sub> < 1 V                                                                                     |     | 0.25 |     | ms   |

| t <sub>Px_GATE_VSYS_FSD</sub> | Time allowed to disable the external FET via Px_GATE_VSYS in fast shutdown mode (OVP or FRS) <sup>(1)</sup>                     | $V_{VSYS}$ = $V_{VBUS}$ =20V initially, then $V_{VBUS}$ raised to 23V in 50ns, Gate is off when $V_{GS}$ < 1 V                                     |     | 0.25 |     | μS   |

| t <sub>Px_GATE_VBUS_ON</sub>  | time to enable Px_GATE_VBUS (1)                                                                                                 | measure time from when V <sub>GS</sub> =0V until V <sub>GS</sub> >3V                                                                               |     | 0.25 |     | ms   |

<sup>(1)</sup> These values depend upon the characteristics of the external N-ch MOSFET. The typical values were measured when Px\_GATE\_VSYS and Px\_GATE\_VBUS were used to drive two CSD17571Q2 in common drain back-to-back configuration.

# 6.10 Power Path Supervisory

Operating under these conditions unless otherwise noted: 3.0 V  $\leqslant$  V<sub>VIN 3V3</sub>  $\leqslant$  3.6 V

|                        | PARAMETER                                                                                            | TEST CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|------|

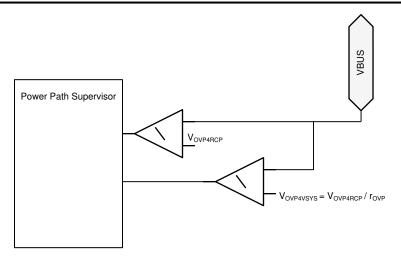

| V <sub>OVP4RCP</sub>   | VBUS over voltage protection typical threshold for RCP programmable range (setting 0 to setting 63). | OVP detected when V <sub>Px_VBUS</sub> > V <sub>OVP4RCP</sub>                   | 5.25  |       | 22.9  | V    |

|                        | Tolernance of V <sub>OVP4RCP</sub> threshold                                                         |                                                                                 | -5    |       | 5     | %    |

| V <sub>OVPLSB</sub>    | VBUS over voltage protection range for RCP                                                           |                                                                                 |       | 280   |       | mV   |

| V <sub>OVP4RCPH</sub>  | hysteresis                                                                                           |                                                                                 | 1.75  | 2     | 2.25  | %    |

|                        |                                                                                                      | setting 0                                                                       | 1     | 1     | 1     | V/V  |

|                        | Configurable ratio of OVP comparator                                                                 | setting 1                                                                       | 0.925 | 0.95  | 0.975 | V/V  |

| r <sub>OVP</sub>       | thresholds. r <sub>OVP</sub> *V <sub>OVP4VSYS</sub> = V <sub>OVP4RCP</sub>                           | setting 2                                                                       | 0.875 | 0.90  | 0.925 | V/V  |

|                        |                                                                                                      | setting 3                                                                       | 0.85  | 0.875 | 0.9   | V/V  |

| V <sub>OVP4VSYS</sub>  | VBUS over voltage protection range for VSYS protection                                               | OVP detected when r <sub>OVP</sub> *V <sub>PX_VBUS</sub> > V <sub>OVP4RCP</sub> | 5     |       | 27.5  | V    |

| V <sub>OVP4VSYS</sub>  | hysteresis                                                                                           | VBUS falling, % of VOVP4VSYS                                                    |       | 2     |       | %    |

|                        |                                                                                                      | rising                                                                          | 3.9   | 4.1   | 4.3   |      |

| V <sub>PP5V_UVLO</sub> | Voltage required on PP5V                                                                             | falling                                                                         | 3.8   | 4.0   | 4.2   | V    |

|                        |                                                                                                      | hysteresis                                                                      |       | 0.1   |       | İ    |

| I <sub>DSCH</sub>      | VBUS discharge current <sup>(1)</sup>                                                                | V <sub>Px_VBUS</sub> = 22V, measure<br>I <sub>Px_VBUS</sub>                     | 4     |       | 13    | mA   |

<sup>(1)</sup> The discharge is enabled automatically when needed to meet USB specifications. It is not always enabled.

### **6.11 CC Cable Detection Parameters**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

| PARAMETER                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------------|-----------------|-----|-----|-----|------|

| Type-C Source (Rp pull-up) |                 |     |     |     |      |

Product Folder Links: TPS65994AD

Submit Document Feedback

# **6.11 CC Cable Detection Parameters (continued)**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

|                        | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                                                                                                                                                      | MIN  | TYP  | MAX  | UNIT                 |

|------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------------------|

| V <sub>OC_3.3</sub>    | Unattached Px_CCy open circuit voltage while Rp enabled, no load       | $V_{LDO_3V3\_UVLO} < V_{LDO_3V3} < 3.6 \text{ V}, \\ R_{CC} = 47 \text{ k}\Omega$                                                                                                                                                                                                    | 1.85 |      |      | V                    |

| V <sub>OC_5</sub>      | Attached Px_CCy open circuit voltage while Rp enabled, no load         | $V_{PP5V\_UVLO} < V_{PP5V} < 5.5 \text{ V}, R_{CC} = 47 \text{ k}\Omega$                                                                                                                                                                                                             | 2.95 |      |      | V                    |

| I_                     |                                                                        | $\begin{array}{c} V_{Px\_CCy} = 5.5 \text{V}, \ V_{Px\_CCx} = 0 \text{V}, \\ V_{LDO\_3V3\_UVLO} < V_{LDO\_3V3} < 3.6 \text{ V}, \\ V_{PP5V} = 3.8 \text{ V}, \ \text{measure current} \\ \text{into Px\_CCy} \end{array}$                                                            |      |      | 10   | μA                   |

| Rev                    | Px_CCy                                                                 | $\begin{array}{l} V_{Px\_CCy} = 5.5 \text{V}, \ V_{Px\_CCx} = 0 \text{V}, \\ V_{LDO\_3V3\_UVLO} < V_{LDO\_3V3} < 3.6 \text{ V}, \\ V_{PP5V} = 0, -10^{\circ} \text{C} \lesssim \text{T}_{\text{J}} \lesssim 85^{\circ} \text{C}, \\ \text{measure current into Px\_CCy} \end{array}$ |      |      | 10   | μΛ                   |

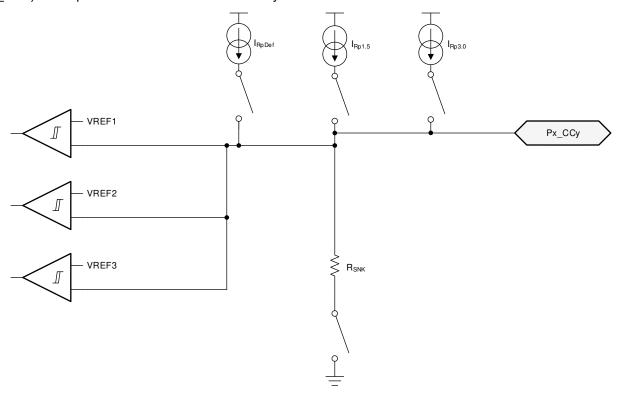

| I <sub>RpDef</sub>     | current source - USB Default                                           | $0 < V_{Px\_CCy} < 1.0 \text{ V}$ , measure $I_{Px\_CCy}$                                                                                                                                                                                                                            | 64   | 80   | 96   | μΑ                   |

| I <sub>Rp1.5</sub>     | current source - 1.5A                                                  | 4.75 V < V <sub>PP5V</sub> < 5.5 V, 0 < V <sub>Px_CCy</sub> < 1.5 V, measure I <sub>Px_CCy</sub>                                                                                                                                                                                     | 166  | 180  | 194  | μA                   |

| I <sub>Rp3.0</sub>     | current source - 3.0A                                                  | 4.75 V < V <sub>PP5V</sub> < 5.5 V, 0 < V <sub>Px_CCy</sub> < 2.45 V, measure I <sub>Px_CCy</sub>                                                                                                                                                                                    | 304  | 330  | 356  | μΑ                   |

| Type-C Sink (Rd p      | ull-down)                                                              |                                                                                                                                                                                                                                                                                      |      |      |      |                      |

|                        | Open/Default detection threshold when Rd applied to Px_CCy             | rising                                                                                                                                                                                                                                                                               | 0.2  |      | 0.24 | ٧                    |

| V <sub>SNK1</sub>      | Open/Default detection threshold when Rd applied to Px_CCy             | falling                                                                                                                                                                                                                                                                              | 0.16 |      | 0.20 | V                    |

|                        | hysteresis                                                             |                                                                                                                                                                                                                                                                                      |      | 0.04 |      | V                    |

| V <sub>SNK2</sub>      | Default/1.5A detection threshold                                       | falling                                                                                                                                                                                                                                                                              | 0.62 |      | 0.68 | V                    |

|                        | Default/1.5A detection threshold                                       | rising                                                                                                                                                                                                                                                                               | 0.63 | 0.66 | 0.69 | V                    |

|                        | hysteresis                                                             |                                                                                                                                                                                                                                                                                      |      | 0.01 |      | V                    |

|                        | 1.5A/3.0A detection threshold when Rd applied to Px_CCy                | falling                                                                                                                                                                                                                                                                              | 1.17 |      | 1.25 | V                    |

| V <sub>SNK3</sub>      | 1.5A/3.0A detection threshold when Rd applied to Px_CCy                | rising                                                                                                                                                                                                                                                                               | 1.22 |      | 1.3  | V                    |

|                        | hysteresis                                                             |                                                                                                                                                                                                                                                                                      |      | 0.05 |      | V                    |

| R <sub>SNK</sub>       | Rd pulldown resistance                                                 | $0.25~V \leqslant V_{Px\_CCy} \leqslant 2.1~V,$ measure resistance on Px_CCy                                                                                                                                                                                                         | 4.1  |      | 6.1  | $\mathbf{k}  \Omega$ |

| R <sub>VCONN_DIS</sub> | VCONN discharge resistance                                             | $0V \leqslant V_{Px\_CCy} \leqslant 5.5 \text{ V, measure}$ resistance on Px_CCy                                                                                                                                                                                                     | 4.1  |      | 6.1  | kΩ                   |

|                        |                                                                        | V <sub>VIN_3V3</sub> =0V, 64 μA < I <sub>Px_CCy</sub> <96<br>μA                                                                                                                                                                                                                      | 0.25 |      | 1.32 |                      |

| $V_{CLAMP}$            | Dead battery Rd clamp                                                  | V <sub>VIN_3V3</sub> =0V, 166 μA <<br>I <sub>Px_CCy</sub> <194 μA                                                                                                                                                                                                                    | 0.65 |      | 1.32 | ٧                    |

|                        |                                                                        | V <sub>VIN_3V3</sub> =0V, 304 μA < I <sub>Px_CCy</sub> <<br>356 μA                                                                                                                                                                                                                   | 1.20 |      | 2.18 |                      |

| $R_Open$               | resistance from Px_CCy to GND                                          | V <sub>Px_VBUS</sub> = 0, V <sub>VIN_3V3</sub> =3.3V,<br>V <sub>Px_CCy</sub> =5 V, measure resistance<br>on Px_CCy                                                                                                                                                                   | 500  |      |      | <b>k</b> Ω           |

| ··Open                 | when configured as open.                                               | V <sub>Px_VBUS</sub> = 5V, V <sub>VIN_3V3</sub> = 0,<br>V <sub>Px_CCy</sub> =5 V, measure resistance<br>on Px_CCy                                                                                                                                                                    | 500  |      |      | <b>k</b> Ω           |

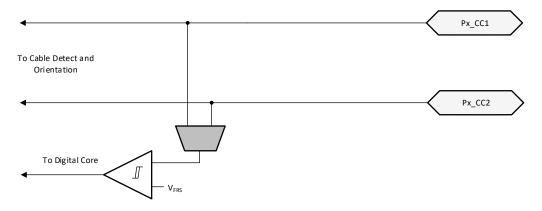

| V <sub>FRS</sub>       | Fast Role swap request voltage detection threshold on Px_CCy (falling) |                                                                                                                                                                                                                                                                                      | 495  | 515  | 535  | mV                   |

| V <sub>FRS</sub>       | hysteresis                                                             |                                                                                                                                                                                                                                                                                      |      | 0.01 |      | V                    |

# **6.11 CC Cable Detection Parameters (continued)**

Operating under these conditions unless otherwise noted: 3.0 V  $\leqslant$  V<sub>VIN 3V3</sub>  $\leqslant$  3.6 V

| PARAMETER             |                                                         | TEST CONDITIONS                                                                                             | MIN | TYP | MAX | UNIT |  |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| t <sub>FRS_DET</sub>  | Fast role swap signal detection time                    | V <sub>Px_CCy</sub> must be below V <sub>FRS</sub> for at least this long before the FRS signal is detected | 30  |     | 35  | μs   |  |

| t <sub>FRS_Resp</sub> | response time of the Fast role swap comparator (rising) | V <sub>Px_CCy</sub> rises from 0.24V to 0.64V                                                               |     |     | 0.6 | μs   |  |

| Common (Source and Si | Common (Source and Sink)                                |                                                                                                             |     |     |     |      |  |

| tcc                   | deglitch time for comparators on Px_CCy                 |                                                                                                             |     | 3.2 |     | ms   |  |

## **6.12 CC VCONN Parameters**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

| PARAMI                    | ETER                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                             | MIN | TYP  | MAX | UNIT |

|---------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| R <sub>PP_CABLE</sub>     | Rdson of the VCONN path                             | V <sub>PP5V</sub> =5V, I <sub>L</sub> = 250 mA,<br>measure resistance from PP5V<br>to Px_CCy                                                                                                                                                                                                                                |     | 0.4  | 0.7 | Ω    |

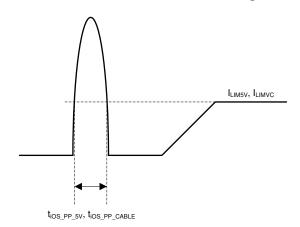

| I <sub>LIMVC</sub>        | short circuit current limit                         | setting 0, $V_{PP5V}$ =5V, $R_L$ =10m $\Omega$ , measure $I_{Px\_CCy}$                                                                                                                                                                                                                                                      | 350 | 410  | 470 | mA   |

| I <sub>LIMVC</sub>        | short circuit current limit                         | setting 1, $V_{PP5V}$ =5V, $R_L$ =10m $\Omega$ , measure $I_{Px\_CCy}$                                                                                                                                                                                                                                                      | 540 | 605  | 670 | mA   |

| I <sub>CC2PP5V</sub>      | Reverse leakage current through VCONN FET           | $\label{eq:convergence} \begin{array}{l} \text{VCONN disabled, T}_{\text{J}} \leqslant 85~^{\circ}\text{C,} \\ \text{V}_{\text{Px\_CCy}} = 5.5~\text{V, V}_{\text{PP5V}} = 0~\text{V,} \\ \text{V}_{\text{Px\_VBUS}} = 5\text{V, LDO forced to} \\ \text{draw from VBUS, measure} \\ \text{I}_{\text{Px\_CCy}} \end{array}$ |     | 0    | 10  | μΑ   |

| t <sub>VCILIM</sub>       | Current clamp deglitch time                         |                                                                                                                                                                                                                                                                                                                             |     | 1.28 |     | ms   |

| t <sub>PP_CABLE_off</sub> | from disable signal to Px_CCy at 10% of final value | I <sub>L</sub> = 250 mA, V <sub>PP5V</sub> = 5V, C <sub>L</sub> =0                                                                                                                                                                                                                                                          | 100 | 171  | 300 | μs   |

| t <sub>iOS_PP_CABLE</sub> | response time to short circuit                      | $V_{PP5V}$ =5V, for short circuit $R_L$ = 10m $\Omega$ .                                                                                                                                                                                                                                                                    |     | 2    |     | μs   |

## **6.13 CC PHY Parameters**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V or V<sub>Px VBUS</sub>  $\geq$  3.9 V

|                     | PARAMETER                                                                                                           | TEST CONDITIONS                                                                         | MIN  | TYP   | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|-------|-----|------|

| Transmitter         |                                                                                                                     |                                                                                         |      |       |     |      |

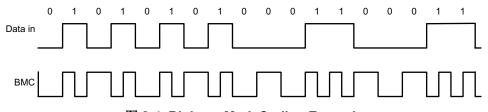

| V <sub>TXHI</sub>   | Transmit high voltage on Px_CCy                                                                                     | Standard External load                                                                  | 1.05 | 1.125 | 1.2 | V    |

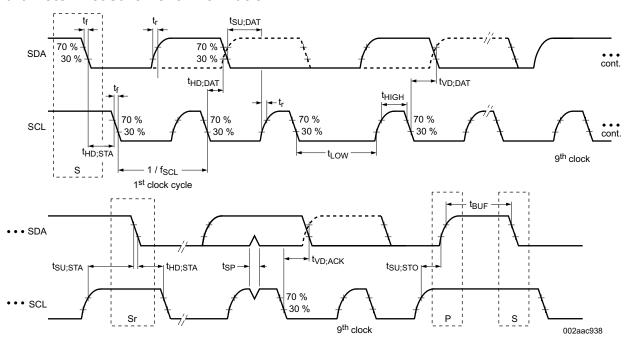

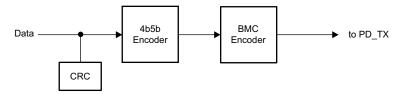

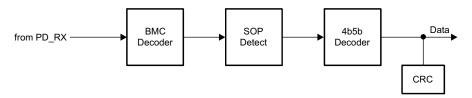

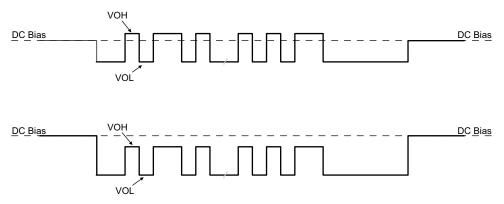

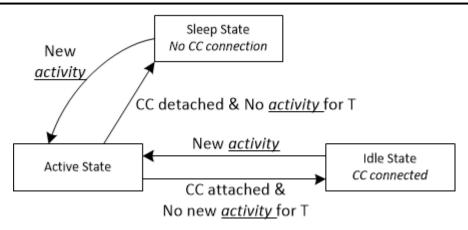

| $V_{TXLO}$          | Transmit low voltage on Px_CCy                                                                                      | Standard External load                                                                  | -75  |       | 75  | mV   |