TPS659037

ZHCSEF7G – DECEMBER 2014 – REVISED FEBRUARY 2019

## 适用于处理器的 TPS659037 电源管理单元 (PMU)

#### 1 器件概述

#### 1.1 特性

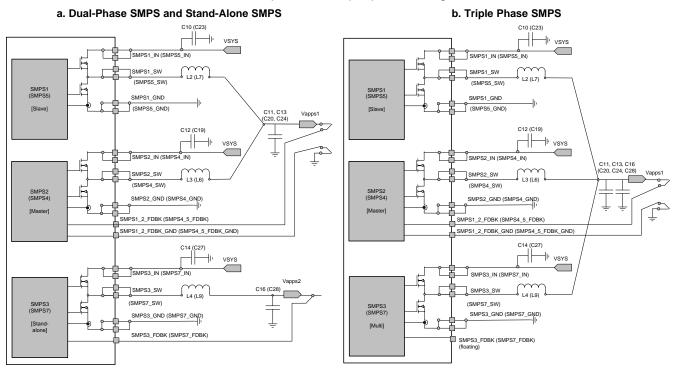

- 七个降压开关模式电源 (SMPS) 稳压器:

- 其中一个输出为 0.7V-1.65V/6A(阶跃为 10mV)

- 支持数字电压调节 (DVS) 控制的双相配置

- 其中一个输出为 0.7V-1.65V/4A(阶跃为 10mV)

- 支持 DVS 控制的双相配置

- 其中一个输出为 0.7V-3.3V/3A(阶跃为 10mV 或 20mV)

- 单相配置

- 该稳压器可搭配 6A 稳压器构成 9A 三相稳压器(通过 DVS 控制)

- 两个 0.7V-3.3V/2A(步长为 10mV 或 20mV)

- 单相配置

- 一个支持 DVS 控制的稳压器,也可配置成 3A 稳压器

- 两个 0.7V-3.3V/1A(步长为 10mV 或 20mV)

- 单相配置

- 一个支持 DVS 控制的稳压器

- 除 1A SMPS 稳压器外的所有稳压器均支持输出 电流测量

- 双相和三相稳压器均支持差分遥感(输出和接地)

- 通过硬件和软件控制的 Eco-mode™高达 5mA, 静态电流为 15μA

- 短路保护

- 电源正常指示(电压和过流指示)

- 内部软启动可限制浪涌电流

- 可通过相位同步将 SMPS 与外部时钟或内部备用时钟同步

- 七个步长为 50mV 的通用低压降稳压器 (LDO):

- 两个 0.9V-3.3V/300mA LDO,由经过预稳压的电源供电

- 两个 0.9V-3.3V/200mA LDO,由经过预稳压的电源供电

- 声性能高达 50mA)

两个供 PMU 内部使用的附加 LDO

短路保护

- 时钟管理 16MHz 晶体振荡器和 32kHz RC 振荡器

一个缓冲式 32kHz 输出

– 一个 0.9V-3.3V/50mA LDO,由经过预稳压的电

- 一个 0.9V-3.3V/高达 100mA 低噪声 LDO (低噪

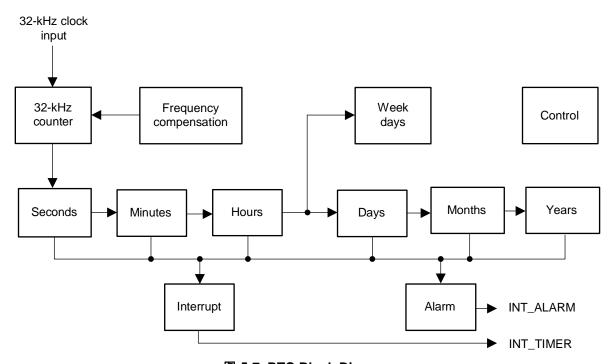

- 具有警报唤醒机制的实时时钟 (RTC)

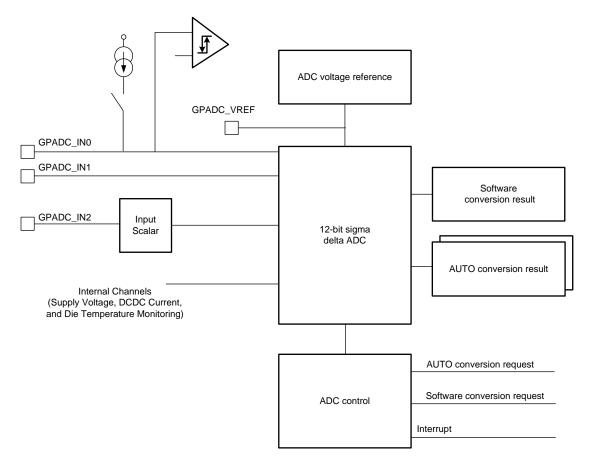

- 具有三个外部输入通道和六个自监控内部通道的 12 位 Σ-Δ 通用模数转换器 (GPADC)

- 过热监控

- 高温警告

源供电

- 一个 100mA USB LDO

- 热关断

- 控制

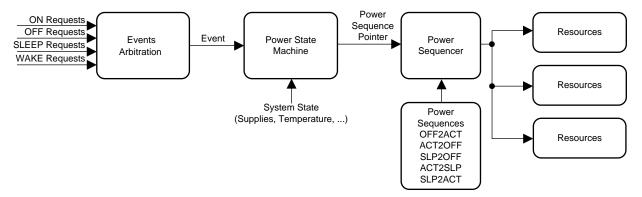

- 可配置上电和断电序列(一次性可编程 [OTP])

- 睡眠和激活状态之间的可配置序列(OTP 可编程)

- 一个可纳入到启动序列中的专用数字输出信号 (REGEN)

- 三个与 **GPIO** 进行多路复用并可纳入到启动序列中的数字输出信号

- 可选控制接口

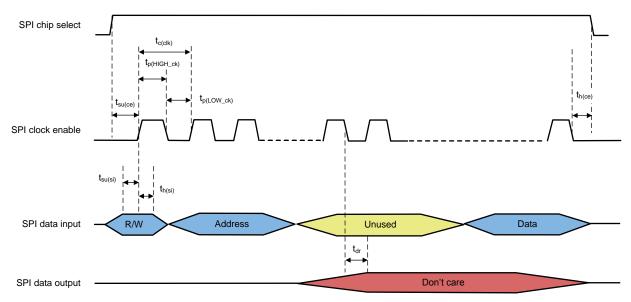

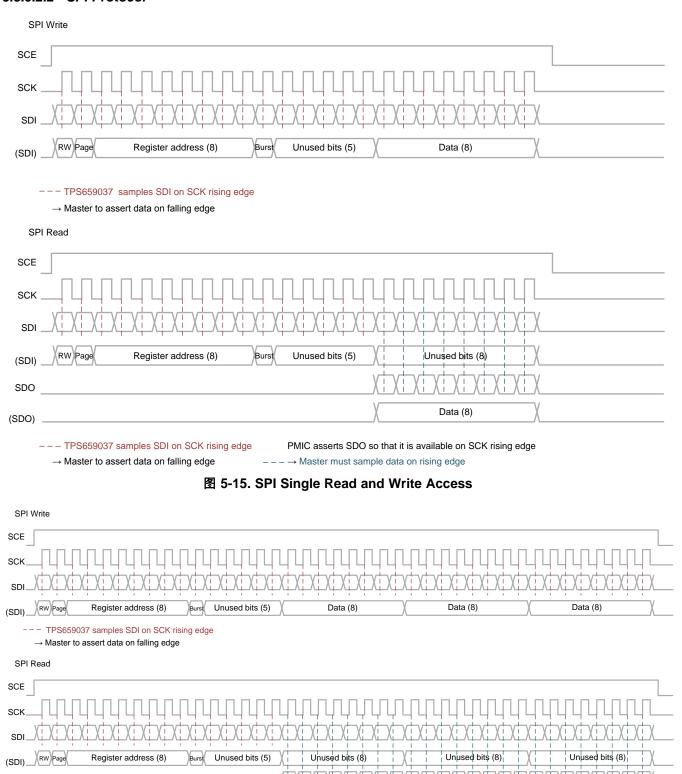

- 一个用于资源配置和 DVS 控制的串行外设接口 (SPI)

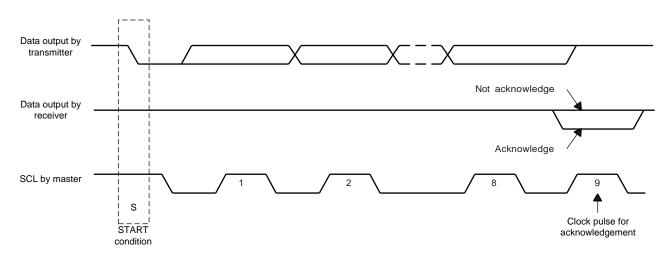

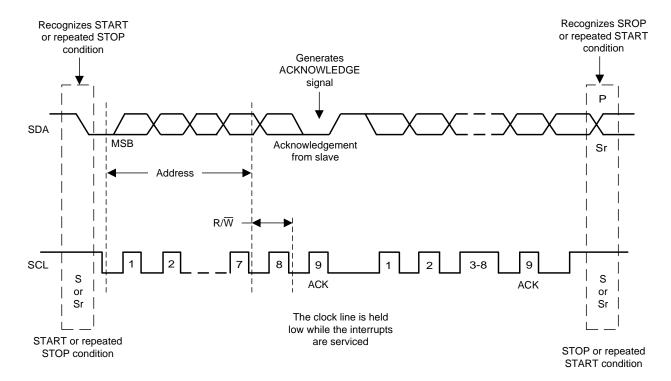

- 两个 I<sup>2</sup>C 接口。其中一个专用于 DVS 控制, 另一个是用于资源配置和 DVS 控制的通用 I<sup>2</sup>C 接口

- 欠压锁定

- 系统电压范围为 3.135V 至 5.25V

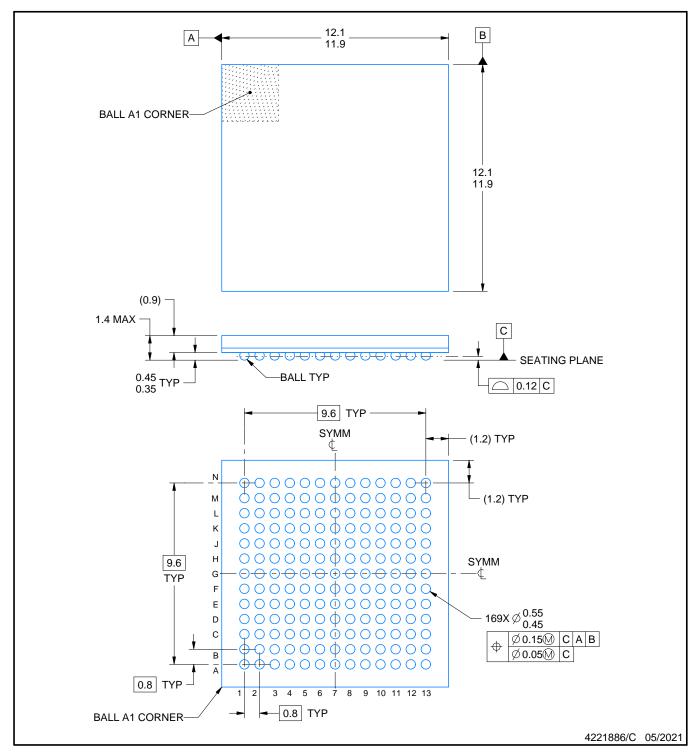

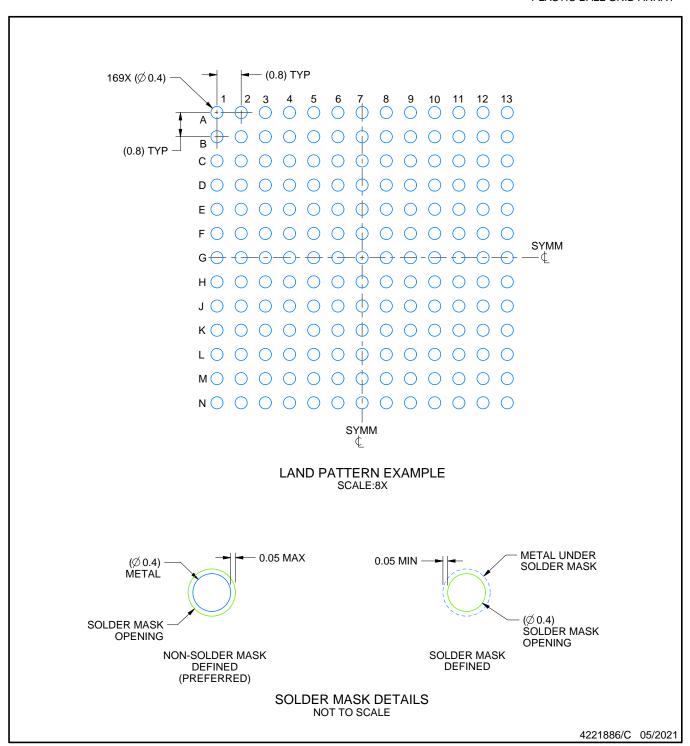

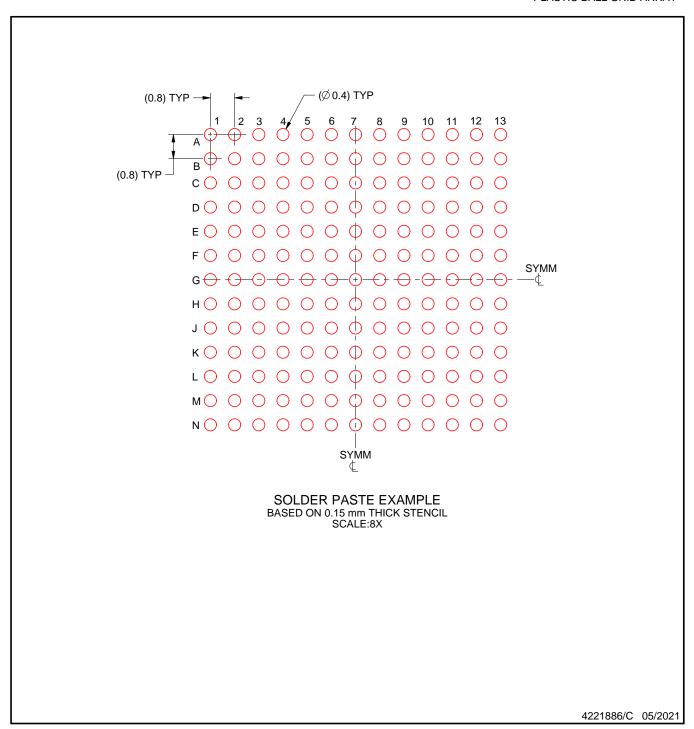

- 封装选项

- 12mm x 12mm、169 引脚 nFBGA 封装,引脚间 距为 0.8mm

#### 1.2 应用

- 工厂自动化

- 可编程逻辑控制器

- 模块上系统

- 人机界面

#### 1.3 说明

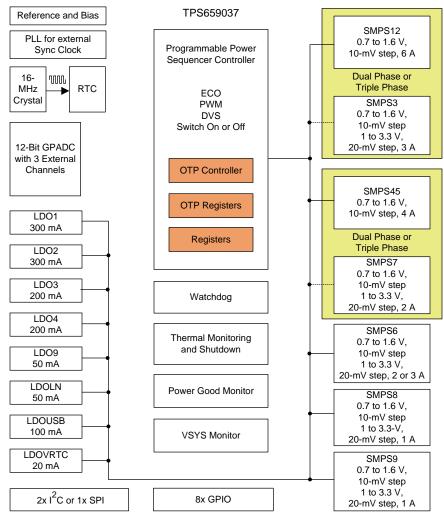

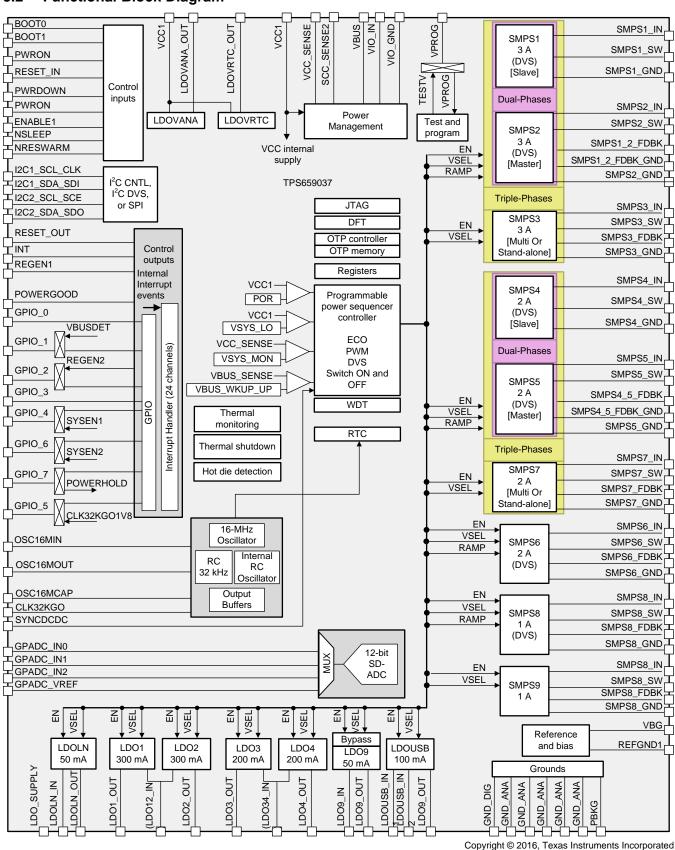

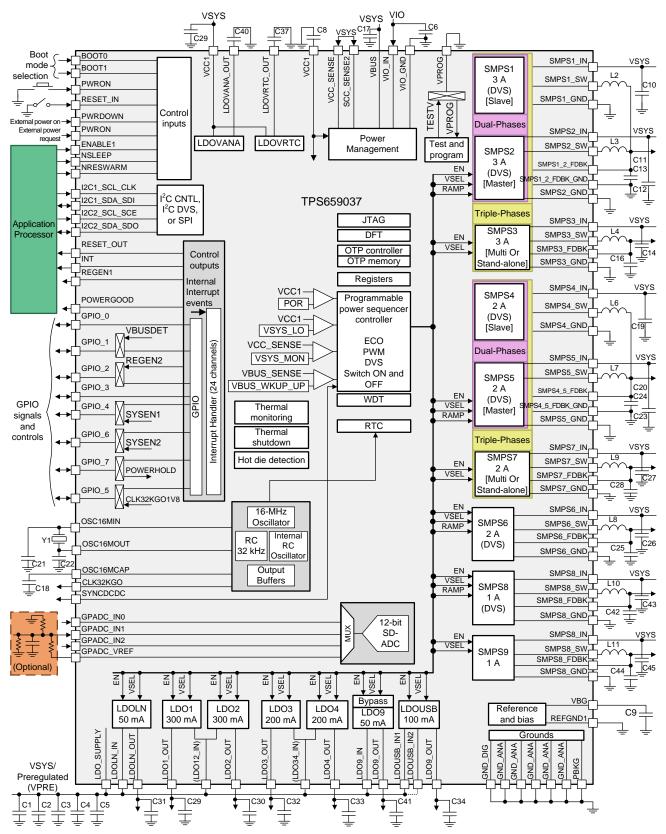

TPS659037 器件是一款集成式电源管理 IC (PMIC)。该器件提供七个可配置的降压转换器,输出电流高达6A,可用于存储器、处理器内核、输入/输出 (I/O) 或 LDO 预稳压。其中一个可配置的降压转换器与另一个3A 稳压器组合后可提供高达 9A 的输出电流。所有这些降压转换器均可与频率介于 1.7MHz 至 2.7MHz 之间的外部时钟源或频率为 2.2MHz 的内部备用时钟同步。

TPS659037 器件提供七个供外部使用的 LDO 稳压器。这些 LDO 稳压器可由系统电源或经过预稳压的电源供电。上电和断电控制器是可配置的,能够支持所有上电和断电序列(基于 OTP)。TPS659037 器件包含一个 32kHz RC 振荡器,可在上电和断电过程中对所有资源进行排序。在需要快速启动的情况下,也可使用 16MHz 晶体振荡器来快速为系统产生一个稳定的 32kHz 频率。所有 LDO 和 SMPS 转换器均可由 SPI 或 I<sup>2</sup>C 接口或通过电源请求信号进行控制。此外,电压调节寄存器允许将 SMPS 转换为 SPI、I<sup>2</sup>C 或项部/底部控制所需的不同电压。

每种封装中都有一个专用引脚可配置为上电序列的一部分,用于控制外部资源。该器件具备通用输入输出 (GPIO) 功能,两个 GPIO 均可配置为上电序列的一部分,用于控制外部资源。电源请求信号通过启用电源 模式控制功能来实现电源优化。该器件包含一个带有三个外部输入通道的通用  $\Sigma$ - $\Delta$  模数转换器 (GPADC)。

TPS659037 器件采用 13 引脚 x 13 引脚 nFBGA 封装, 引脚间距为 0.8mm。

器件信息(1)

| 器件型号      | 封装        | 封装尺寸 (标称值)        |  |  |

|-----------|-----------|-------------------|--|--|

| TPS659037 | ZWS (169) | 12.00mm × 12.00mm |  |  |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品附录。

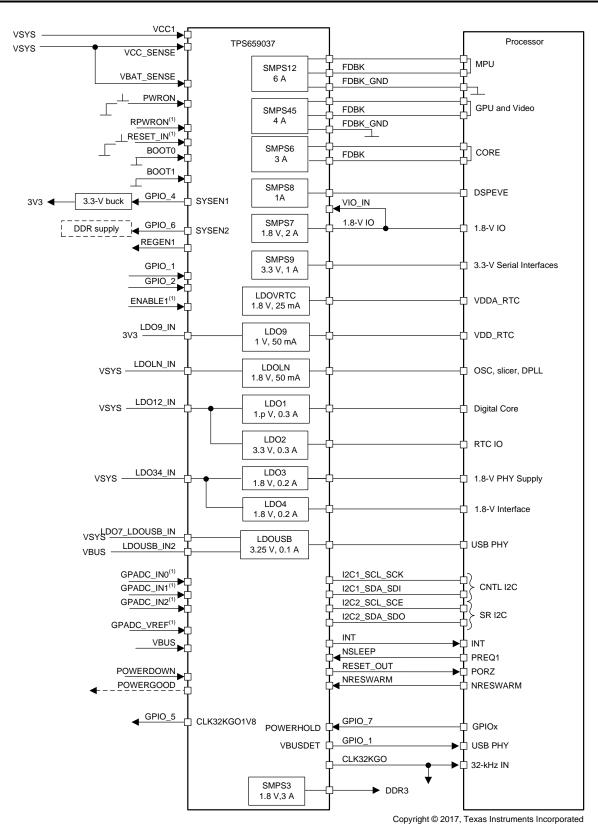

#### 1.4 简化方框图

Copyright © 2016, Texas Instruments Incorporated

## 内容

| I | 器件机   | 既述                                                            | <u>1</u>   |    | 4.16 | Electrical Characteristics: Digital Input Signal             | 0.0 |

|---|-------|---------------------------------------------------------------|------------|----|------|--------------------------------------------------------------|-----|

|   | 1.1   | 特性                                                            | . <u>1</u> |    |      | Parameters                                                   | 23  |

|   | 1.2   | 应用                                                            | _          |    | 4.17 | Electrical Characteristics: Digital Output Signal Parameters | 23  |

|   | 1.3   | 说明                                                            | _          |    | 4.18 | Electrical Characteristics: I/O Pullup and Pulldown.         |     |

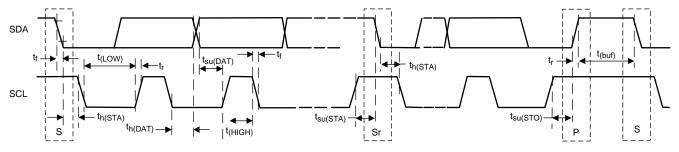

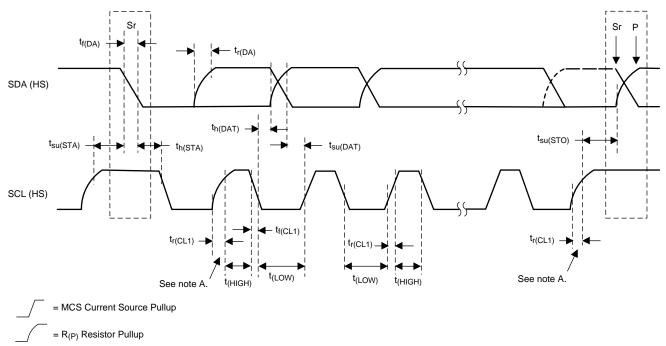

|   | 1.4   | 简化方框图                                                         | _          |    | 4.19 | I <sup>2</sup> C Interface Timing Requirements               |     |

| 2 |       | 历史记录                                                          | _          |    | 4.20 | SPI Timing Requirements                                      |     |

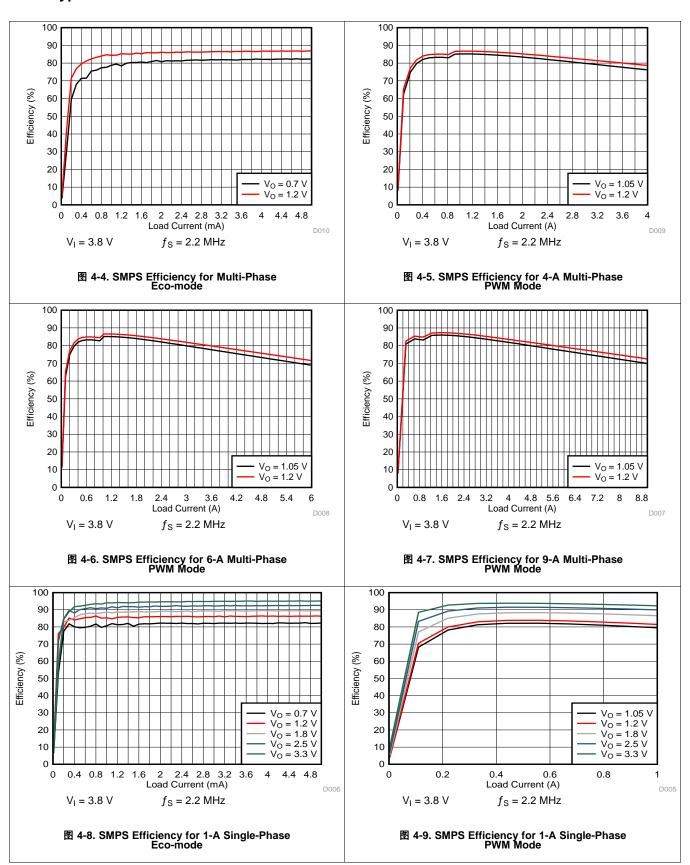

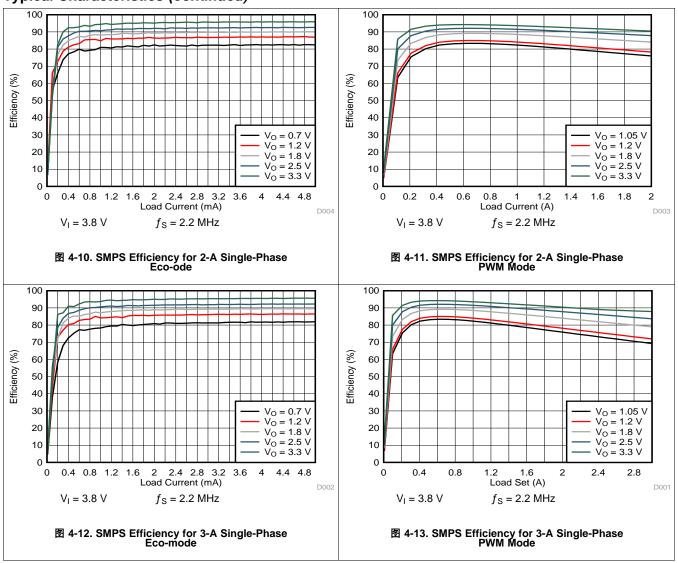

| 3 | Pin C | Configuration and Functions                                   | <u> </u>   |    | 4.21 | Typical Characteristics                                      |     |

| 1 | Spec  | cifications                                                   | <u>12</u>  | 5  |      | iled Description                                             |     |

|   | 4.1   | Absolute Maximum Ratings                                      | <u>12</u>  | J  | 5.1  | Overview                                                     |     |

|   | 4.2   | ESD Ratings                                                   | <u>12</u>  |    | 5.2  | Functional Block Diagram                                     |     |

|   | 4.3   | Recommended Operating Conditions                              | <u>13</u>  |    | 5.3  | Feature Description                                          |     |

|   | 4.4   | Thermal Information                                           | <u>13</u>  |    | 5.4  | Device Functional Modes                                      |     |

|   | 4.5   | Electrical Characteristics: Latch Up Rating                   | <u>13</u>  | 6  |      | ication and Implementation                                   | _   |

|   | 4.6   | Electrical Characteristics: LDO Regulator                     | <u>14</u>  | U  | 6.1  | Application Information                                      |     |

|   | 4.7   | Electrical Characteristics: Dual-Phase (SMPS12                |            |    | 6.2  | • •                                                          | _   |

|   |       | and SMPS45) and Triple-Phase (SMPS123 and SMPS457) Regulators | 16         | 7  | -    | Typical Applicationer Supply Recommendations                 |     |

|   | 4.8   | Electrical Characteristics: Stand-Alone Regulators            | 10         | 8  |      |                                                              |     |

|   | 4.0   | (SMPS3, SMPS6, SMPS7, SMPS8, and SMPS9)                       | 17         | 0  | -    | ut                                                           |     |

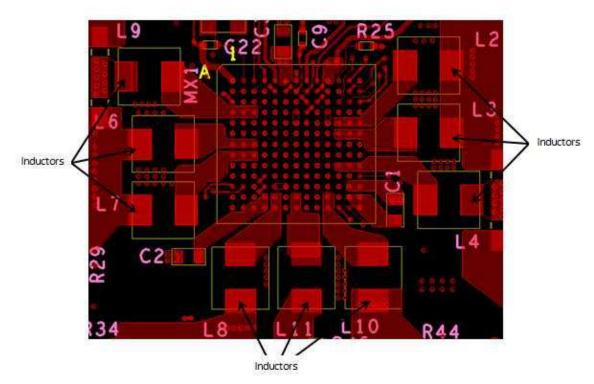

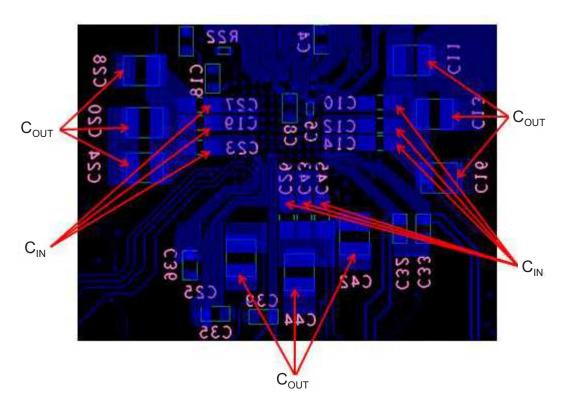

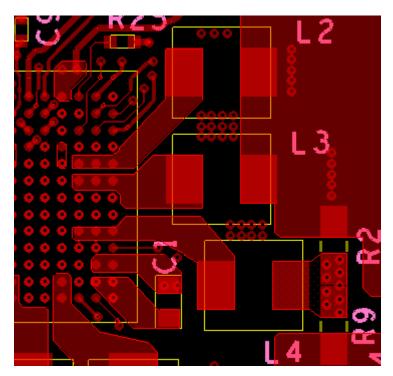

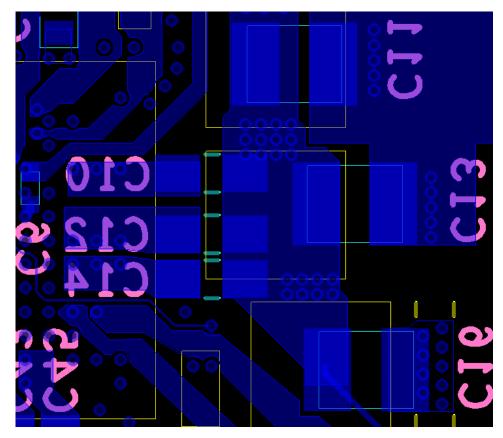

|   | 4.9   | Electrical Characteristics: Reference Generator               |            |    | 8.1  | Layout Guidelines                                            |     |

|   |       | (Bandgap)                                                     | <u>19</u>  | _  | 8.2  | Layout Example                                               | _   |

|   | 4.10  | Electrical Characteristics: 16-MHz Crystal Oscillator,        |            | 9  |      | 和文档支持                                                        |     |

|   |       | 32-kHz RC Oscillator, and Output Buffers                      | <u>19</u>  |    | 9.1  | 器件支持                                                         |     |

|   | 4.11  | Electrical Characteristics: DC-DC Clock Sync                  | <u>20</u>  |    | 9.2  | 文档支持                                                         |     |

|   | 4.12  | Electrical Characteristics: 12-Bit Sigma-Delta ADC.           | <u>20</u>  |    | 9.3  | 接收文档更新通知                                                     | _   |

|   | 4.13  | Electrical Characteristics: Thermal Monitoring and            |            |    | 9.4  | 社区资源                                                         |     |

|   |       | Shutdown                                                      | <u>22</u>  |    | 9.5  | 商标                                                           |     |

|   | 4.14  | Electrical Characteristics: System Control Threshold          | 22         |    | 9.6  | 静电放电警告                                                       | 93  |

|   | 1 15  |                                                               |            |    | 9.7  | Glossary                                                     |     |

|   | 4.15  | Electrical Characteristics: Current Consumption               | <u>22</u>  | 10 | 机械、  | 、封装和可订购信息                                                    | 94  |

## 2 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

## Changes from Revision F (January 2018) to Revision G

Page

| • | Updated the LDOVRTC_OUT pulldown resistor recommendation to only include applicable silicon revisions       | . <u>6</u> |

|---|-------------------------------------------------------------------------------------------------------------|------------|

| • | Changed ESD Ratings for charge device model on 6 pins                                                       | 12         |

| • | Clarified that LDO1 and LDO2 input pins are not included in this minimum recommended operating voltage. See |            |

|   | Electrical Characteristics: LDO Regulators for more information.                                            | 13         |

| • | Changed minimum recommended operating condition of OSC16MIN from 0V to -0.7V                                | 13         |

| • | Added LDO and SMPS output capacitance footnote                                                              | 14         |

| • | Changed VSYS_LO hysteresis from 95mV to 75mV                                                                | 22         |

| • | Updated Caution statement to only include applicable silicon revisions                                      | 31         |

| • | Changed discharge resistance to match electrical characteristics table                                      | 34         |

| • | Added information about shutdown timing during short circuit detection                                      | 37         |

| • | Updated POWERGOOD description to clarify multi-phase operation                                              | 37         |

| • | Updated LDOVRTC note to only include applicable silicon revisions.                                          | 42         |

| • | Added details on identifying device version.                                                                | <u>60</u>  |

| • | Added typical debounce time from POWERHOLD to the enable of the first rail in the power sequence            | 62         |

| • | Added VSYS_LO note for applicable silicon revisions                                                         | 73         |

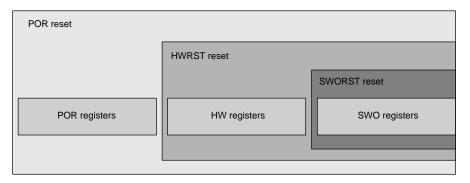

| • | Updated POR requirements to only include applicable silicon revisions                                       | 74         |

| • | SMPS and LDO output capacitance specification further explained                                             | 81         |

| • | Added design considerations for VCC1 capacitance to support loss of power                                   | 81         |

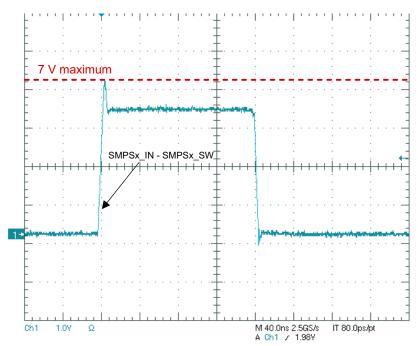

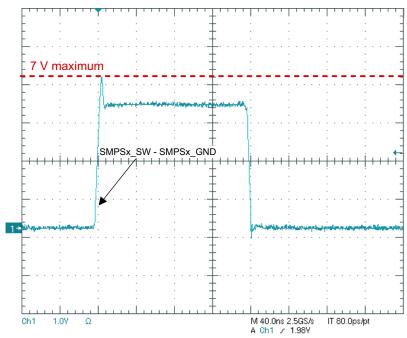

| • | Corrected 9-Vpp with 7V absolute maximum specification in the Layout Guidelines section                     |            |

| <u>.</u> | Updated images and description on differential measurements across high-side and low-side FETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Chang    | ges from Revision E (July 2017) to Revision F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                             |

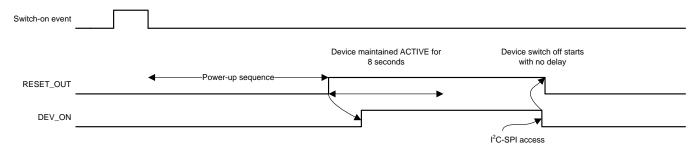

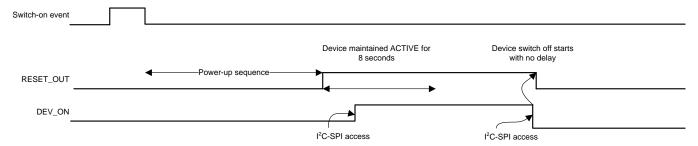

| Chang    | Deleted pullup and pulldown from BOOT0 pin description Deleted the voltage mode to the I/O digital supply voltage, VIO_IN parameter from the Recommended Operating Conditions table.  Added 2-A mode for SMPS6 in the test conditions for high-side and low-side MOSFET forward current limit and low-side MOSFET negative current limit in the Electrical Characteristics: Stand-Alone Regulators (SMPS3, SMPS6, SMPS7, SMPS8, and SMPS9) table.  □添加 the number of active SMPS phases (K) to the equation for the temperature compensated result in the Current Monitoring and Short Circuit Detection section.  □添加 additional description of SMPS short detection and recovery behavior.  □添加 description of VIO power-up timing, and updated start up timing diagram.  □添加 additional description of VSYS_LO functionality.  □更改 静电放电注意事项 声明 | 10<br>13<br>18<br>37<br>37<br>47<br>67           |

| Chang    | ges from Revision D (April 2016) to Revision E  已删除 CLK32KGO from the Startup Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77<br>78                                         |

| Chang    | ges from Revision C (November 2015) to Revision D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                             |

| •        | Changed the LDOVRTC_OUT pin description in the <i>Pin Functions</i> table Changed the typical value for the channel 11 SMPS output current measurement gain factor parameter in the 12-Bit Sigma-Delta ADC Characteristics table Changed the typical value for the channel 11 SMPS output current measurement current offset parameter in the 12-Bit Sigma-Delta ADC Characteristics table  □添加 maximum current of LDOVRTC in BACKUP and OFF states □添加 a note to the LDOVRTC section □添加 additional description of POR in System Voltage Monitoring section Updated part numbers and settings for released devices in the Design Parameters table                                                                                                                                                                                                | <u>21</u><br><u>21</u><br><u>42</u><br><u>42</u> |

| Chang    | ges from Revision B (November 2015) to Revision C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                             |

| •        | 已添加 statement to the <i>Current Monitoring and Short Circuit Detection</i> section that the SMPS_SHORT_REGISTER bit will keep a resource off until it is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                               |

| Chang    | ges from Revision A (September 2015) to Revision B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                             |

| •        | 已更改 将器件状态从预告信息 更改成了量产数据                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                |

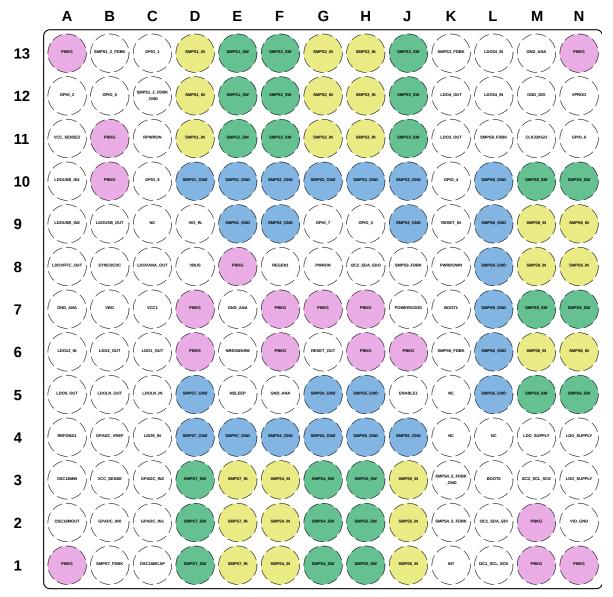

## 3 Pin Configuration and Functions

Figure 3-1. 169-Pin ZWS New Fine Pitch Ball Grid Array (NFBGA) With 0,8-mm Pitch Top View

#### **Pin Functions**

|            | PIN              |     | (4)                     | CONNECTION IF NOT                    |                                                                                                                                                                                   |  |

|------------|------------------|-----|-------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.        | NAME             | 1/0 | PU OR PD <sup>(1)</sup> | USED OR NOT<br>AVAILABLE             | DESCRIPTION                                                                                                                                                                       |  |

| A1         | PBKG             | _   | _                       | Ground                               | Substrate ground                                                                                                                                                                  |  |

| A2         | OSC16MOUT        | 0   | _                       | Floating                             | 16-MHz crystal oscillator output or floating in case of digital clock                                                                                                             |  |

| А3         | OSC16MIN         | I   | _                       | Floating or ground in<br>bypass mode | 16-MHz crystal oscillator input or digital clock input                                                                                                                            |  |

| A4         | REFGND1          | _   | _                       | Ground                               | System reference ground                                                                                                                                                           |  |

| A5         | LDO9_OUT         | 0   | _                       | Floating                             | LDO9 output voltage                                                                                                                                                               |  |

| A6         | LDO12_IN         | I   | _                       | System supply                        | Power input voltage for LDO1 and LDO2 regulators                                                                                                                                  |  |

| A7         | GND_ANA          | _   | _                       | Ground                               | Analog power ground                                                                                                                                                               |  |

| A8         | LDOVRTC_OUT      | 0   | _                       | _                                    | Internal LDOVRTC output voltage. For silicon revisions 1.3 or earlier, rapid power off and on requires a pulldown resistor on the LDOVRTC_OUT pin. See 节 5.4.11 for more details. |  |

| A9         | LDOUSB_IN2       | - 1 | _                       | System supply                        | Power input voltage 2 for LDOUSB regulator                                                                                                                                        |  |

| A10        | LDOUSB_IN1       | - 1 | _                       | System supply                        | Power input voltage 1 for LDOUSB regulator                                                                                                                                        |  |

| A11        | VCC_SENSE2       | I   | _                       | System supply                        | System-supply sense line                                                                                                                                                          |  |

| A12        | GPIO_2           | I/O | PPU<br>PPD              | Floating                             | Primary function: General-purpose input <sup>(2)</sup> or output                                                                                                                  |  |

|            |                  | 0   | _                       | -                                    | Secondary function: REGEN2 — External regulator enable output 2                                                                                                                   |  |

| A13        | PBKG             | _   | _                       | Ground                               | Substrate ground                                                                                                                                                                  |  |

| B1         | SMPS7_FDBK       | I   | _                       | Floating                             | Output voltage-sense (feedback) input for step-down converter, SMPS7                                                                                                              |  |

| B2         | GPADC_IN0        | I   | _                       | Ground                               | Sigma-delta GPADC input 0                                                                                                                                                         |  |

| В3         | VCC_SENSE        | I   | _                       | System supply                        | System-supply sense line                                                                                                                                                          |  |

| B4         | GPADC_VREF       | 0   | _                       | Floating                             | Sigma-delta GPADC output reference voltage                                                                                                                                        |  |

| B5         | LDOLN_OUT        | 0   | _                       | Floating                             | Output voltage for the low-noise dropout regulator, LDOLN                                                                                                                         |  |

| В6         | LDO2_OUT         | 0   | _                       | Floating                             | LDO2 output voltage                                                                                                                                                               |  |

| B7         | VBG              | 0   | _                       | _                                    | Bandgap reference voltage                                                                                                                                                         |  |

| В8         | SYNCDCDC         | I   | _                       | Ground                               | Sync pin to sync DC-DCs with external clock                                                                                                                                       |  |

| В9         | LDOUSB_OUT       | 0   | _                       | Floating                             | LDOUSB output voltage                                                                                                                                                             |  |

| B10<br>B11 | PBKG             | _   | _                       | Ground                               | Substrate ground                                                                                                                                                                  |  |

| B12        | GPIO_0           | I/O | PPD                     | Ground or VSYS (VCC1)                | General-purpose input <sup>(2)</sup> or output                                                                                                                                    |  |

| B13        | SMPS1_2_FDBK     | ı   | _                       | Ground                               | Output voltage-sense (feedback) input for step-down converters, SMPS1 and SMPS2                                                                                                   |  |

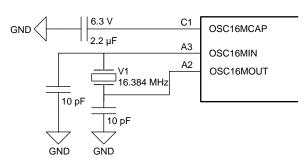

| C1         | OSC16MCAP        | 0   | _                       | Floating                             | Filtering capacitor for the 16-MHz crystal oscillator                                                                                                                             |  |

| C2         | GPADC_IN1        | I   | _                       | Ground                               | Sigma-delta GPADC input 1                                                                                                                                                         |  |

| СЗ         | GPADC_IN2        | I   | _                       | Ground                               | Sigma-delta GPADC input 2                                                                                                                                                         |  |

| C4         | LDO9_IN          | I   | _                       | System supply                        | Power input voltage for LDO9 regulator                                                                                                                                            |  |

| C5         | LDOLN_IN         | - 1 | _                       | System supply                        | Power input voltage for the low-noise dropout regulator, LDOLN                                                                                                                    |  |

| C6         | LDO1_OUT         | 0   | _                       | Floating                             | LDO1 output voltage                                                                                                                                                               |  |

| C7         | VCC1             | I   | _                       | System supply                        | Analog input voltage supply                                                                                                                                                       |  |

| C8         | LDOVANA_OUT      | 0   | _                       | _                                    | Internal LDOVANA output voltage                                                                                                                                                   |  |

| C9         | NC               | _   | _                       | _                                    | Not connected                                                                                                                                                                     |  |

|            |                  | I/O | PPU                     | Ground                               | Primary function: General-purpose input <sup>(2)</sup> or output                                                                                                                  |  |

| C10        | GPIO 5           | 1/0 | PPD <sup>(2)</sup>      | Ground                               | Frimary runction: General-purpose input or output                                                                                                                                 |  |

|            | 0.102            | 0   | _                       | Floating                             | Secondary function: CLK32KGO1V8 — 32-kHz digital-gated output clock available when VRTC is present                                                                                |  |

| C11        | RPWRON           | I   | PU                      | Floating                             | External remote switch-on event                                                                                                                                                   |  |

| C12        | SMPS1_2_FDBK_GND | I   | _                       | Ground                               | Ground-sense (feedback) input for step-down converters, SMPS1 and SMPS2                                                                                                           |  |

| C13        | GPIO_1           | I/O | PPU                     | Floating                             | Primary function: General-purpose input <sup>(2)</sup> or output                                                                                                                  |  |

| 3.5        | J. 10_1          | 0   | PPD                     | 1 loating                            | Secondary function: VBUSDET - VBUS detection                                                                                                                                      |  |

(1) The PU/PD column shows the pullup and pulldown resistors on the digital input lines. The pullup and pulldown resistors are defined as follows:

PU pullupPD pulldown

PPU software-programmable pullupPPD software-programmable pulldown

(2) Default option

## Pin Functions (continued)

|            | PIN CONNECTION IF NOT |     |                         |                          |                                                                               |  |  |

|------------|-----------------------|-----|-------------------------|--------------------------|-------------------------------------------------------------------------------|--|--|

| NO.        | NAME                  | 1/0 | PU OR PD <sup>(1)</sup> | USED OR NOT<br>AVAILABLE | DESCRIPTION                                                                   |  |  |

| D1         |                       |     |                         | AVAILABLE                |                                                                               |  |  |

| D2         | SMPS7_SW              | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS7. Connect the output to an inductor. |  |  |

| D3         |                       |     |                         | 3                        |                                                                               |  |  |

| D4         |                       |     |                         |                          |                                                                               |  |  |

| D5         | SMPS7_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS7                        |  |  |

| D6         |                       |     |                         |                          |                                                                               |  |  |

| D7         | PBKG                  | _   | _                       | Ground                   | Substrate ground                                                              |  |  |

| D8         | VBUS                  | ı   | _                       | Ground                   | VBUS Detection Voltage                                                        |  |  |

| D9         | VIO_IN                | 1   | _                       | System supply            | Digital supply input for GPIOs and I/O supply voltage                         |  |  |

| D10        | SMPS1_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS1                        |  |  |

| D11        |                       |     |                         |                          |                                                                               |  |  |

| D12        | SMPS1_IN              | - 1 | _                       | System supply            | Power input for step-down converter, SMPS1                                    |  |  |

| D13        |                       |     |                         |                          |                                                                               |  |  |

| E1         |                       |     |                         |                          |                                                                               |  |  |

| E2         | SMPS7_IN              | - 1 | _                       | System supply            | Power input for step-down converter, SMPS7                                    |  |  |

| E3         |                       |     |                         |                          |                                                                               |  |  |

| E4         | SMPS7_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS7                        |  |  |

| E5         | NSLEEP                | 1   | PPU <sup>(2)</sup>      | Floating                 | NSLEEP request signal                                                         |  |  |

|            |                       |     | PPD                     | Ů                        |                                                                               |  |  |

| E6         | NRESWARM              | 1   | PPU <sup>(2)</sup>      | Floating                 | Warm reset input                                                              |  |  |

| E7         | GND_ANA               | _   | _                       | Ground                   | Analog power ground                                                           |  |  |

| E8         | PBKG                  | _   | _                       | Ground                   | Substrate ground                                                              |  |  |

| E9         | SMPS1_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS1                        |  |  |

| E10        |                       |     |                         |                          |                                                                               |  |  |

| E11<br>E12 | CMDC4 CW              | 0   |                         | Floating                 | Quitab node of stan down convertor SMDS1. Connect the cutaut to an industor   |  |  |

| E12        | SMPS1_SW              |     | _                       | Floating                 | Switch node of step-down converter, SMPS1. Connect the output to an inductor. |  |  |

| F1         |                       |     |                         |                          |                                                                               |  |  |

| F2         | SMPS4_IN              | 1   | _                       | System supply            | Power input for step-down converter, SMPS4                                    |  |  |

| F3         | CIVII O-I_IIV         |     |                         | Оублонг барргу           | Town input for step down converter, own C4                                    |  |  |

| F4         | SMPS4_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS4                        |  |  |

| F5         | GND_ANA               | _   | _                       | Ground                   | Analog power ground                                                           |  |  |

| F6         |                       |     |                         |                          |                                                                               |  |  |

| F7         | PBKG                  | _   | _                       | Ground                   | Substrate ground                                                              |  |  |

| F8         | REGEN1                | 0   | _                       | Floating                 | External regulator enable output 1                                            |  |  |

| F9         | CMDCC CND             |     |                         | Construct                | Davis results connection for ston down converts. OMDOS                        |  |  |

| F10        | SMPS2_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS2                        |  |  |

| F11        |                       |     |                         |                          |                                                                               |  |  |

| F12        | SMPS2_SW              | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS2. Connect the output to an inductor. |  |  |

| F13        |                       |     |                         |                          |                                                                               |  |  |

| G1         |                       |     |                         |                          |                                                                               |  |  |

| G2         | SMPS4_SW              | 0   | =                       | Floating                 | Switch node of step-down converter, SMPS4. Connect the output to an inductor. |  |  |

| G3         |                       |     |                         |                          |                                                                               |  |  |

| G4         | SMPS4_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS4                        |  |  |

| G5         |                       |     |                         |                          |                                                                               |  |  |

| G6         | RESET_OUT             | 0   | _                       | Floating                 | System reset and power on output (Low → Reset, High → Active or Sleep)        |  |  |

| G7         | PBKG                  | _   | —<br>Bu                 | Ground                   | Substrate ground                                                              |  |  |

| G8         | PWRON                 | 1/0 | PU                      | Floating                 | External power-on event (on-button switch-on event)                           |  |  |

| G9         | GPIO_7                | I/O | PPD PPD(2)              | Ground or VRTC           | Primary function: General-purpose input <sup>(2)</sup> or output              |  |  |

| G10        | CMDC2 CND             | I   | PPU <sup>(2)</sup>      | Cround                   | Secondary function: POWERHOLD input                                           |  |  |

| G10        | SMPS2_GND             | _   | _                       | Ground                   | Power ground connection for step-down converter, SMPS2                        |  |  |

| G11<br>G12 | INI COGMO             | 1   |                         | System supply            | Power input for step-down converter, SMPS2                                    |  |  |

| G12        | SMPS2_IN              | '   | _                       | System supply            | r ower impaction step-down converter, sinifaz                                 |  |  |

| 013        |                       | 1   |                         |                          |                                                                               |  |  |

### Pin Functions (continued)

|                   | Pin Functions (continued) |     |                           |                                  |                                                                                                                                                           |  |  |

|-------------------|---------------------------|-----|---------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | PIN                       | I/O | PU OR PD <sup>(1)</sup>   | CONNECTION IF NOT<br>USED OR NOT | DESCRIPTION                                                                                                                                               |  |  |

| NO.               | NAME                      |     |                           | AVAILABLE                        |                                                                                                                                                           |  |  |

| H1<br>H2<br>H3    | SMPS5_SW                  | 0   | _                         | Floating                         | Switch node of step-down converter, SMPS5. Connect the output to an inductor.                                                                             |  |  |

| H4<br>H5          | SMPS5_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS5                                                                                                    |  |  |

| H6<br>H7          | PBKG                      | _   | _                         | Ground                           | Substrate ground                                                                                                                                          |  |  |

| H8                | I2C2_SDA_SDO              | I/O | _                         | Floating                         | DVS I <sup>2</sup> C serial bidirectional data (external pullup) and SPI data read signal or I <sup>2</sup> C serial bidirectional data (external pullup) |  |  |

| H9                | GPIO_3                    | I   | PPD                       | Ground                           | General-purpose input <sup>(2)</sup> or output                                                                                                            |  |  |

| H10               | SMPS3_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS3                                                                                                    |  |  |

| H11<br>H12<br>H13 | SMPS3_IN                  | I   | _                         | System supply                    | Power input for step-down converter, SMPS3                                                                                                                |  |  |

| J1<br>J2<br>J3    | SMPS5_IN                  | I   | _                         | System supply                    | Power input for step-down converter, SMPS5                                                                                                                |  |  |

| J4                | SMPS5_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS5                                                                                                    |  |  |

| J5                | ENABLE1                   | I   | PPU<br>PPD <sup>(2)</sup> | Floating                         | Peripheral power request input 1                                                                                                                          |  |  |

| J6                | PBKG                      | _   | _                         | Ground                           | Substrate ground                                                                                                                                          |  |  |

| J7                | POWERGOOD                 | 0   | _                         | Floating                         | Indication signal for valid regulator output voltages                                                                                                     |  |  |

| J8                | SMPS9_FDBK                | I   | _                         | Ground                           | Output voltage-sense (feedback) input for step-down converter, SMPS9                                                                                      |  |  |

| J9<br>J10         | SMPS3_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS3                                                                                                    |  |  |

| J11<br>J12<br>J13 | SMPS3_SW                  | 0   | _                         | Floating                         | Switch node of step-down converter, SMPS3. Connect the output to an inductor.                                                                             |  |  |

| K1                | INT                       | 0   | _                         | _                                | Maskable interrupt output request to the host processor                                                                                                   |  |  |

| K2                | SMPS4_5_FDBK              | I   | _                         | Ground                           | Output voltage-sense (feedback) input for step-down converters, SMPS4 and SMPS5                                                                           |  |  |

| КЗ                | SMPS4_5_FDBK_GND          | I   | _                         | Ground                           | Ground-sense (feedback) input for step-down converters, SMPS4 and SMPS5                                                                                   |  |  |

| K4<br>K5          | NC                        | _   | _                         | _                                | Not connected                                                                                                                                             |  |  |

| K6                | SMPS6_FDBK                | I   | _                         | Ground                           | Output voltage sense (feedback) input for step-down converter, SMPS6                                                                                      |  |  |

| K7                | BOOT1                     | I   | _                         | Ground or VRTC                   | Boot pin 1 for power-up sequence selection                                                                                                                |  |  |

| K8                | PWRDOWN                   | I   | PPD                       | Floating                         | Power-down signal                                                                                                                                         |  |  |

| K9                | RESET_IN                  | I   | PPD                       | Floating                         | Reset input                                                                                                                                               |  |  |

| K10               | GPIO_4                    | I/O | PPU<br>PPD <sup>(2)</sup> | Floating                         | Primary function: General-purpose input <sup>(2)</sup> or output                                                                                          |  |  |

|                   |                           | 0   |                           |                                  | Secondary function: SYSEN1 — External system enable                                                                                                       |  |  |

| K11               | LDO3_OUT                  | 0   | _                         | Floating                         | LDO3 output voltage                                                                                                                                       |  |  |

| K12               | LDO4_OUT                  | 0   | _                         | Floating                         | LDO4 output voltage                                                                                                                                       |  |  |

| K13               | SMPS3_FDBK                | 1   | _                         | Floating                         | Output voltage-sense (feedback) input for step-down converter, SMPS3                                                                                      |  |  |

| L1                | I2C1_SCL_SCK              | I/O | _                         | Floating                         | Control I <sup>2</sup> C serial clock (external pullup) and SPI clock signal                                                                              |  |  |

| L2                | I2C1_SDA_SDI              | I/O | _                         | Floating                         | Control I <sup>2</sup> C serial bidirectional data (external pullup) and SPI data signal                                                                  |  |  |

| L3                | BOOT0                     | I   | _                         | Ground or VRTC                   | Boot pin 0 for power-up sequence selection                                                                                                                |  |  |

| L4                | NC                        | _   | _                         | _                                | Not connected                                                                                                                                             |  |  |

| L5<br>L6          | SMPS6_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS6                                                                                                    |  |  |

| L7<br>L8          | SMPS9_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS9                                                                                                    |  |  |

| L9<br>L10         | SMPS8_GND                 | _   | _                         | Ground                           | Power ground connection for step-down converter, SMPS8                                                                                                    |  |  |

| L11               | SMPS8_FDBK                | I   | _                         | Ground                           | Output voltage-sense (feedback) input for step-down converter, SMPS8                                                                                      |  |  |

## Pin Functions (continued)

| PIN |              |     | (1)                     | CONNECTION IF NOT        |                                                                                                                              |  |

|-----|--------------|-----|-------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME         | 1/0 | PU OR PD <sup>(1)</sup> | USED OR NOT<br>AVAILABLE | DESCRIPTION                                                                                                                  |  |

| L12 | LDO34 IN     | 1   |                         | System supply            | Power input voltage for LDO3 and LDO4 regulators                                                                             |  |

| L13 | LDO34_IIV    | '   | _                       | System supply            | Prower input voltage for EDO3 and EDO4 regulators                                                                            |  |

| M1  | PBKG         | _   | _                       | Ground                   | Substrate ground                                                                                                             |  |

| M2  | 1 BRO        |     |                         | Glodila                  | Cubsitate ground                                                                                                             |  |

| МЗ  | I2C2_SCL_SCE | I/O | _                       | Floating                 | DVS I <sup>2</sup> C serial clock (external pullup) and SPI enable signal or I <sup>2</sup> C serial clock (external pullup) |  |

| M4  | LDO_SUPPLY   | I   | _                       | System supply            | Power input voltage for internal LDO                                                                                         |  |

| M5  | SMPS6_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS6. Connect the output to an inductor.                                                |  |

| M6  | SMPS6_IN     | I   | _                       | System supply            | Power input for step-down converter, SMPS6                                                                                   |  |

| M7  | SMPS9_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS9 Connect the output to an inductor.                                                 |  |

| M8  | SMPS9_IN     | - 1 | _                       | System supply            | Power input for step-down converter, SMPS9                                                                                   |  |

| M9  | SMPS8_IN     | - 1 | _                       | System supply            | Power input for step-down converter, SMPS8                                                                                   |  |

| M10 | SMPS8_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS8 Connect the output to an inductor.                                                 |  |

| M11 | CLK32KGO     | 0   | _                       | Floating                 | 32-kHz digital-gated output clock available when VIO_IN input supply is present                                              |  |

| M12 | GND_DIG      | _   | _                       | Ground                   | Digital power ground                                                                                                         |  |

| M13 | GND_ANA      | _   | _                       | Ground                   | Analog power ground                                                                                                          |  |

| N1  | PBKG         | _   | _                       | Ground                   | Substrate ground                                                                                                             |  |

| N2  | VIO_GND      | _   | _                       | Ground                   | Digital ground connection                                                                                                    |  |

| N3  | LDO_SUPPLY   | - 1 | _                       | System supply            | Power input voltage for internal LDO                                                                                         |  |

| N4  | LDO_SUPPLY   | - 1 | _                       | System supply            | Power input voltage for internal LDO                                                                                         |  |

| N5  | SMPS6_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS6. Connect the output to an inductor.                                                |  |

| N6  | SMPS6_IN     | - 1 | _                       | System supply            | Power input for step-down converter, SMPS6                                                                                   |  |

| N7  | SMPS9_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS9 Connect the output to an inductor.                                                 |  |

| N8  | SMPS9_IN     | - 1 | _                       | System supply            | Power input for step-down converter, SMPS9                                                                                   |  |

| N9  | SMPS8_IN     | - 1 | _                       | System supply            | Power input for step-down converter, SMPS8                                                                                   |  |

| N10 | SMPS8_SW     | 0   | _                       | Floating                 | Switch node of step-down converter, SMPS8 Connect the output to an inductor.                                                 |  |

|     |              | I/O | PPU                     | Ground                   | Primary function: General-purpose input <sup>(2)</sup> or output                                                             |  |

| N11 | GPIO_6       |     | PPD <sup>(2)</sup>      |                          | •                                                                                                                            |  |

|     |              | 0   | _                       | Floating                 | Secondary function: SYSEN2 — External system enable                                                                          |  |

| N12 | VPROG        | - 1 | _                       | Ground or floating       | Primary function: OTP programming voltage                                                                                    |  |

|     |              | 0   | _                       | Floating                 | Secondary function: TESTV                                                                                                    |  |

| N13 | PBKG         | _   | _                       | Ground                   | Substrate ground                                                                                                             |  |

### Table 3-1. Summary of Digital Signals and Some Dedicated Analog Signals

| SIGNAL NAME                                                   | POWER DOMAIN AND TOLERANCE LEVEL      | I/O                            | INPUT PU/PD (1)                              | OTP PU/PD SELECTION | OUTPUT TYPE<br>SELECTION                | ACTIVE HIGH OR LOW         | OTP POLARITY<br>SELECTION |

|---------------------------------------------------------------|---------------------------------------|--------------------------------|----------------------------------------------|---------------------|-----------------------------------------|----------------------------|---------------------------|

| PWRON                                                         | VSYS (VCC1)                           | Input                          | PU fixed                                     | N/A (fixed)         | N/A (input)                             | Low                        | No                        |

| RPWRON                                                        | VSYS (VCC1)                           | Input                          | PU fixed                                     | N/A (fixed)         | N/A (input)                             | Low                        | No                        |

| PWRDOWN                                                       | VRTC, fail-safe<br>(5.25-V tolerance) | Input                          | PPD <sup>(2)</sup><br>(Optional External PU) | Yes                 | N/A (input)                             | Low or high <sup>(2)</sup> | Yes                       |

| POWERGOOD                                                     | VRTC                                  | Output                         | N/A (output)                                 | N/A (output)        | Open-drain                              | Low or high <sup>(2)</sup> | Yes                       |

| воото                                                         | VRTC                                  | Input                          | No                                           | No                  | N/A (input)                             | Boot conf.                 | No                        |

| BOOT1                                                         | VRTC                                  | Tri-level input                | PPU or PPD <sup>(2)</sup>                    | No                  | N/A (input)                             | Boot conf.                 | No                        |

| GPIO_0                                                        | VRTC, fail-safe<br>(5.25-V tolerance) | Input <sup>(2)</sup> or output | PPD <sup>(2)</sup>                           | Yes                 | Open-drain                              | Low or high                | No                        |

| GPIO_1 (primary function)                                     |                                       | Input <sup>(2)</sup> or output | PPU/PPD <sup>(2)</sup>                       | Yes                 | Push-pull (2) or open- drain            | Low or high                |                           |

| GPIO_1<br>secondary function:<br>VBUSDET                      | VSYS                                  | Output                         | N/A (output)                                 | N/A (output)        | Push-pull <sup>(2)</sup> or open- drain | High                       | No                        |

| GPIO_2<br>(primary function)                                  |                                       | Input <sup>(2)</sup> or output | PPU or PPD <sup>(2)</sup>                    | Yes                 | Push-pull <sup>(2)</sup> or open- drain | Low or high                |                           |

| GPIO_2<br>secondary function:<br>REGEN2                       | VSYS                                  | Output                         | N/A (output)                                 | N/A (output)        | Push-pull <sup>(2)</sup> or open- drain | High                       | No                        |

| GPIO_3                                                        | VRTC, fail-safe<br>(5.25-V tolerance) | Input <sup>(2)</sup> or output | PPD <sup>(2)</sup>                           | Yes                 | Open-drain                              | Low or high <sup>(2)</sup> | Yes                       |

| GPIO_4 (primary function)                                     |                                       | Input <sup>(2)</sup> or output | PPU/PPD <sup>(2)</sup>                       | No                  |                                         | Low or high                |                           |

| GPIO_4<br>secondary function:<br>SYSEN1                       | VIO (VIO_IN)                          | Output                         | N/A (output)                                 | N/A (output)        | Push-pull                               | High                       | No                        |

| GPIO_5 (primary function)                                     |                                       | Input <sup>(2)</sup> or output | PPU/PPD <sup>(2)</sup>                       | No                  | Push-pull <sup>(2)</sup> or open- drain | Low or high                | No                        |

| GPIO_5<br>secondary function:<br>CLK32KGO1V8 or<br>SYNCCLKOUT | VRTC                                  | Output                         | N/A (output)                                 | N/A (output)        | Push-pull                               | Toggling                   | No                        |

(1) The pullup and pulldown resistors are defined as follows:

ΡU pullup

PD pulldown

PPU software-programmable pullup

PPD software-programmable pulldown

Default option.

www.ti.com.cn

### Table 3-1. Summary of Digital Signals and Some Dedicated Analog Signals (continued)

| SIGNAL NAME                                | POWER DOMAIN AND TOLERANCE LEVEL      | l/O                            | INPUT PU/PD (1)           | OTP PU/PD SELECTION | OUTPUT TYPE<br>SELECTION                             | ACTIVE HIGH OR<br>LOW      | OTP POLARITY<br>SELECTION  |

|--------------------------------------------|---------------------------------------|--------------------------------|---------------------------|---------------------|------------------------------------------------------|----------------------------|----------------------------|

| GPIO_6 (primary function)                  |                                       | Input <sup>(2)</sup> or output | PPU/PPD <sup>(2)</sup>    | No                  |                                                      | Low or high                |                            |

| GPIO_6<br>secondary function:<br>SYSEN2    | VIO (VIO_IN)                          | Output                         | N/A (output)              | N/A (output)        | Push-pull                                            | High                       | No                         |

| GPIO_7 (primary function)                  | VRTC, fail-safe                       | Input <sup>(2)</sup> or output | PPD <sup>(2)</sup>        | Yes                 | Open-drain                                           | Low or high                |                            |

| GPIO_7<br>secondary function:<br>POWERHOLD | (5.25-V tolerance)                    | Input                          | PD fixed                  | No                  | N/A (input)                                          | High                       | No                         |

| NSLEEP                                     | VRTC                                  | Input                          | PPU <sup>(2)</sup> or PPD | No                  | N/A (input)                                          | Low <sup>(2)</sup> or high | No but software possible   |

| ENABLE1                                    | VIO (VIO_IN)                          | Input                          | PPU or PPD <sup>(2)</sup> | No                  | N/A (input)                                          | Low or high <sup>(2)</sup> | No but software possible   |

| REGEN1                                     | VSYS (VCC1)                           | Output                         | N/A (output)              | N/A (output)        | Push-pull or open- drain (OTP selection)             | High                       | No                         |

| RESET_IN                                   | VRTC, fail-safe<br>(5.25-V tolerance) | Input                          | PPD <sup>(2)</sup>        | Yes                 | N/A (input)                                          | Low <sup>(2)</sup> or high | Yes                        |

| RESET_OUT                                  | VIO (VIO_IN)                          | Output                         | N/A (output)              | N/A (output)        | Push-pull                                            | Low                        | No                         |

| NRESWARM                                   | VRTC                                  | Input                          | PPU <sup>(2)</sup>        | No                  | N/A (input)                                          | Low                        | No                         |

| INT                                        | VIO (VIO_IN)                          | Output                         | N/A (output)              | N/A (output)        | Push-pull <sup>(2)</sup> or open- drain              | Low <sup>(2)</sup> or high | No but software possible   |

| CLK32KGO                                   | VIO (VIO_IN)                          | Output                         | N/A (output)              | N/A (output)        | Push-pull                                            | Toggling                   | No                         |

| I2C1_SDA_SDI                               | VIO (VIO_IN)                          | Input or output                | No                        | No                  | Open-drain                                           | High (I <sup>2</sup> C)    | Yes (I <sup>2</sup> C/SPI) |

| I2C1_SCL_SCK                               | VIO (VIO_IN)                          | Input                          | No                        | No                  | N/A (input)                                          | High (I <sup>2</sup> C)    | Yes (I <sup>2</sup> C/SPI) |

| I2C2_SCL_SCE                               | VIO (VIO_IN)                          | Input                          | No                        | No                  | N/A (input)                                          | High (I <sup>2</sup> C)    | Yes (I <sup>2</sup> C/SPI) |

| I2C2_SDA_SD0                               | VIO (VIO_IN)                          | Input or output                | No                        | No                  | Open-drain (I <sup>2</sup> C) or Push-<br>pull (SPI) | High (I <sup>2</sup> C)    | Yes (I <sup>2</sup> C/SPI) |

| GPADC_IN0                                  | VRTC                                  | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| GPADC_IN1                                  | VANA                                  | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| GPADC_IN2                                  | VANA                                  | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| GPADC_VREF                                 | VANA                                  | Output                         | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| OSC16MIN                                   | VRTC                                  | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| OSC16MOUT                                  | VRTC                                  | Output                         | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| VCC_SENSE2                                 | VSYS (VCC1)                           | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

| VCC_SENSE                                  | VSYS (VCC1)                           | Input                          | No                        | No                  | N/A (analog)                                         | Analog                     | No                         |

#### 4 Specifications

#### 4.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)(2)

|                                                                                                                                                                                                            |                                                    |                                     | MIN                      | MAX                      | UNIT |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|--------------------------|--------------------------|------|--|--|

|                                                                                                                                                                                                            | VCC1 pins                                          | VCC1 pins                           |                          |                          |      |  |  |

|                                                                                                                                                                                                            | VCC_SENSE, VCC_SENSE2 pins                         | -0.3                                | 7                        | V                        |      |  |  |

|                                                                                                                                                                                                            | All LDOs and SMPS supply voltage input pins (ex    | cept LDOUSB_IN2)                    | -0.3                     | 6                        | V    |  |  |

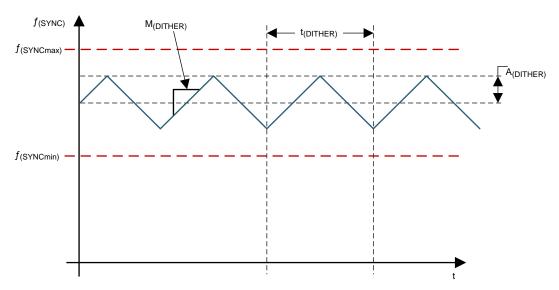

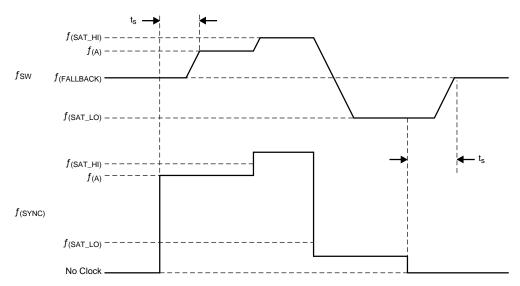

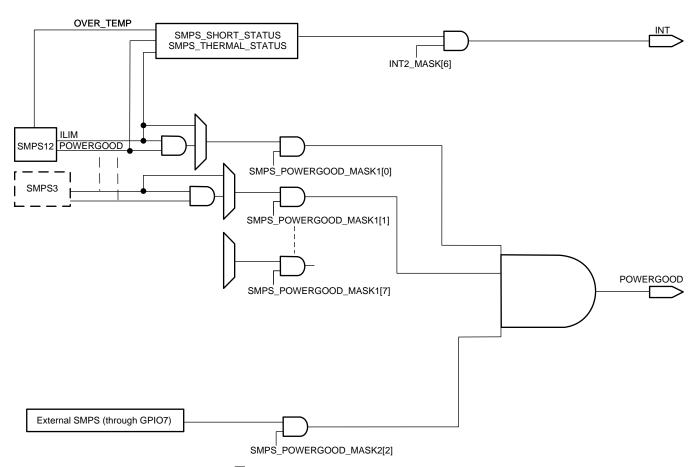

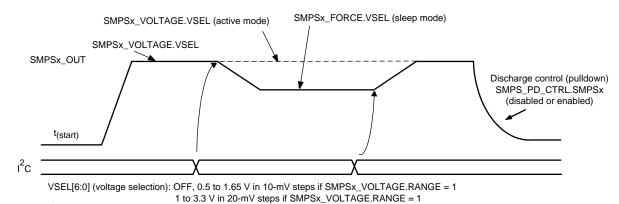

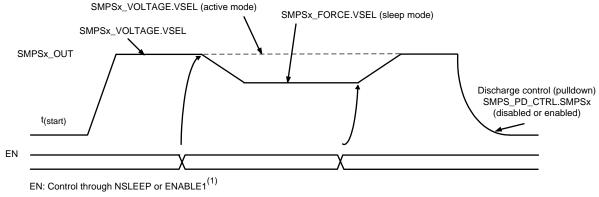

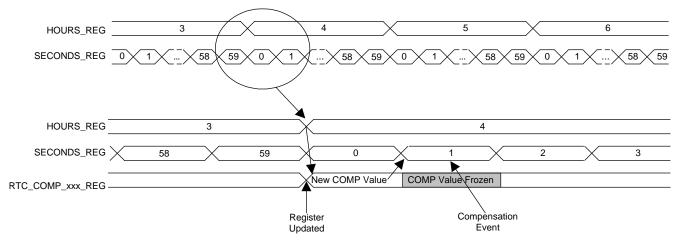

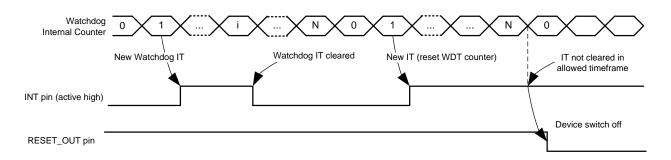

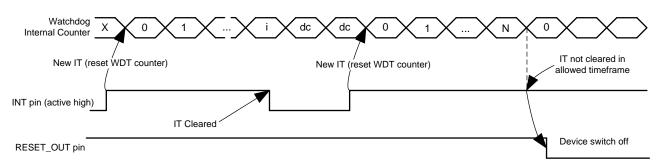

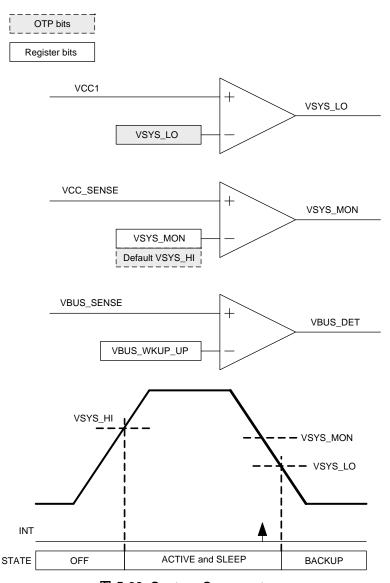

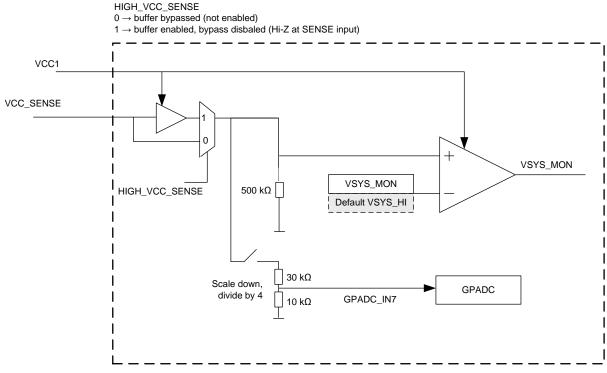

|                                                                                                                                                                                                            | SMPSx_SW pins, 10 ns transient                     |                                     | -2                       | 7                        | V    |  |  |