🕳 Order

Now

#### **TPS53647**

ZHCSDV0B-JUNE 2015-REVISED FEBRUARY 2017

# TPS53647 4 相 D-CAP+ 降压控制器,具有 NVM 和 PMBus™ 接口,适用于 ASIC 电源和高电流负载点

## 1 特性

- 通过引脚设置或 NVM 实现的 8 位可选启动电 压: 0.5V 至 2.5V (步长低至 5mV)

- 1 相、2 相、3 相或 4 相 操作

- PMBus™用于电压、电流、功率、温度和故障条件 遥测的系统接口

- 兼容 1.8V 和 3.3V PMBus 偏置电压

- 故障报告:输出电压、输出电流和温度

- 可通过非易失性存储器 (NVM) 或电阻引脚设置来配置

- 可通过引脚设置或 NVM 编程设定 16个等 级 OCP

- 快速瞬态响应, DCAP+™控制

- 优化了轻负载与重负载条件下的效率

- 支持预偏置启动

- 相电流不均衡检测和报告

- 8级独立的过冲衰减 (OSR) 和下冲衰减 (USR)

- 无驱动器配置,有助于实现高效的高频开关

- 与 CSD95372BQ5MC NexFET™功率级完全兼容

- 精确的可调电压配置

- 300kHz 至 1MHz 频率选择,采用闭环频率控制

- 已获专利 AutoBalance™相位均衡

- 使用 TI 的Fusion Digital Power Designer GUI

- 可编程电流阈值的动态相位减少功能

- 转换电压范围: 4.5V 至 17V

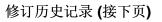

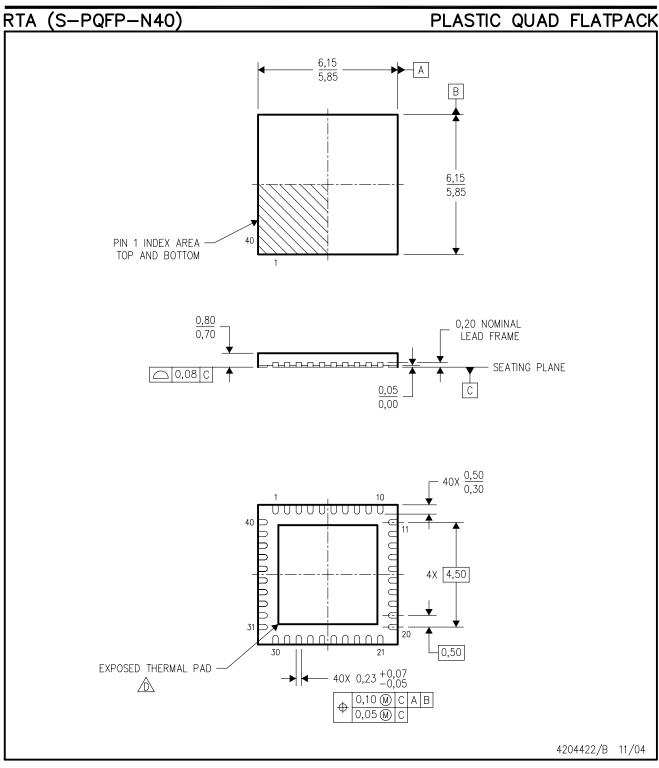

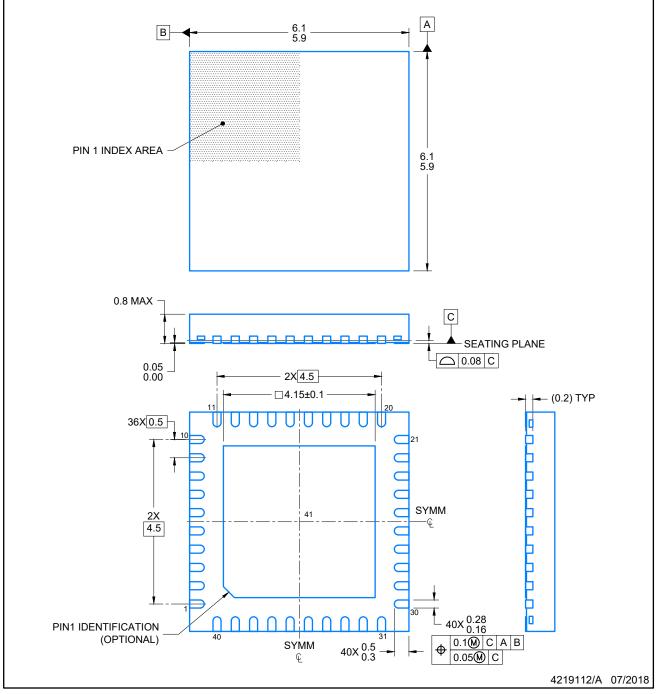

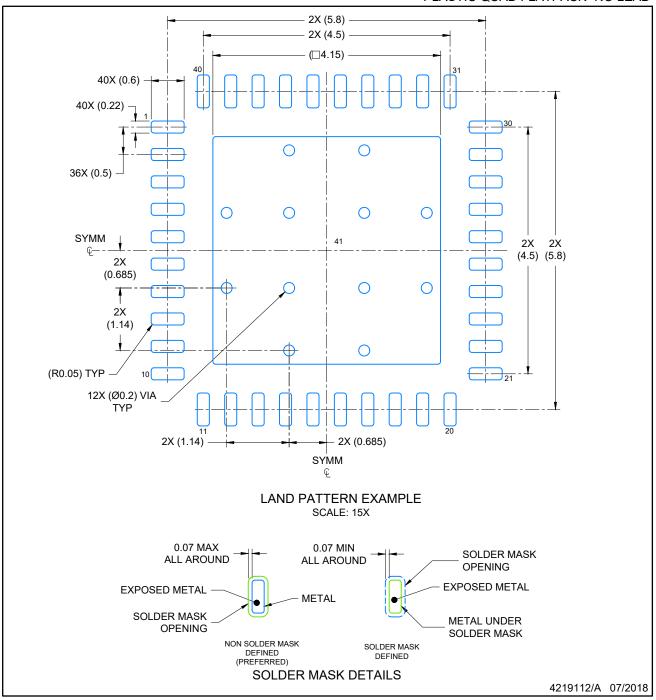

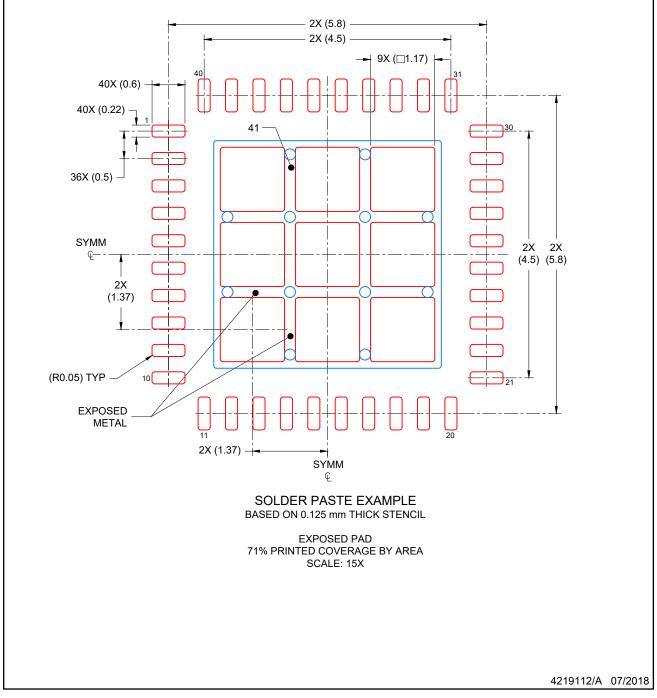

- 小型 6mm x 6mm、40 引脚 QFN PowerPAD™封装

# 2 应用范围

- 通信设备专用集成电路 (ASIC) 电源

- 高密度电源解决方案

- 服务器电源

- 智能电源系统

# 3 说明

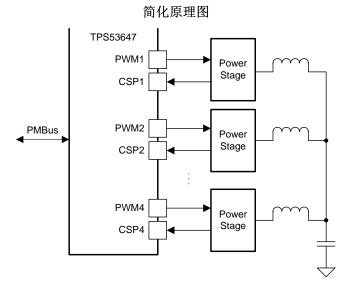

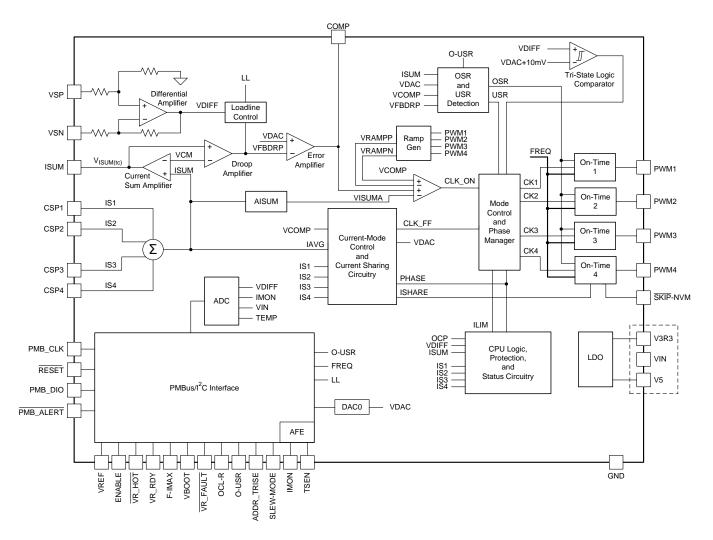

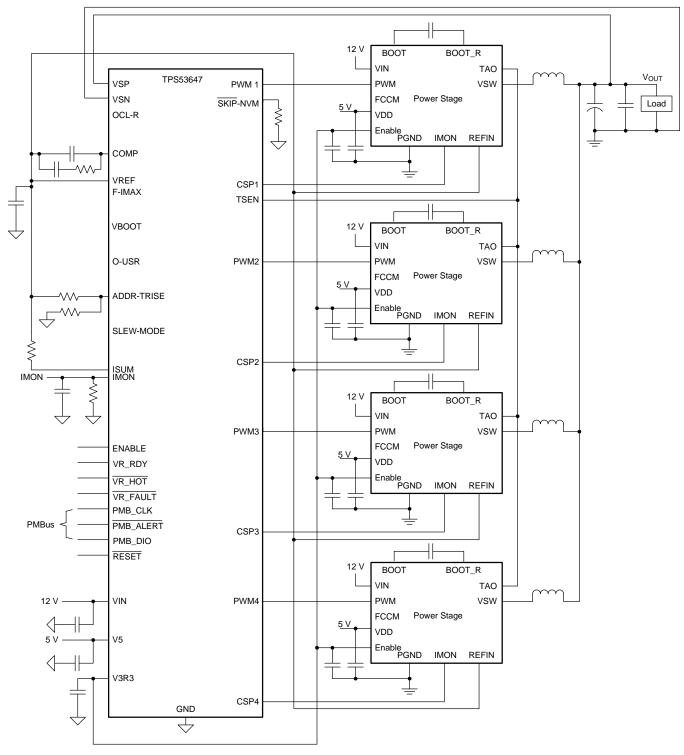

TPS53647 是一款高电流多相位降压控制器。该器件 提供內置非易失性存储器 (NVM) 和 PMBus 接口。此 款产品与 NexFET 功率级 (CSD95372BQ5MC) 兼容。 TPS53647 提供 8 位启动电压选择,输出电压范围为 0.5V 到 2.5V,步长低至 5mV,非常适合具备精确输 出电压设置的高电流应用。具有 D-CAP+ 架构 等高级 特性,支持下冲衰减 (USR) 和过冲衰减 (OSR),可实 现快速瞬态响应、最小的输出电容和高效率。 TPS53647 还提供新型相位交错策略和动态相位减少

功能,可有效提升轻负载条件下的效率。此

外,**TPS53647** 支持 **PMBus** 通信接口,适用于电压、 电流、功率、温度和故障条件遥测系统。部分配置可通 过引脚设置或 **PMBus** 编程设定并存储在非易失性存储 器中,这样可尽量减少外部组件的数量。

**TPS53647** 采用节省空间、耐热增强型 40 引脚 QFN 封装,额定运行温度介于 -40℃ 至 125℃ 之间。

器件信息(1)

| 器件型号     | 封装       | 封装尺寸(标称值)       |

|----------|----------|-----------------|

| TPS53647 | QFN (40) | 6.00mm x 6.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

# 4 修订历史记录

#### Changes from Revision A (September 2016) to Revision B

Page

| • | Updated V3R3 LDO section                                             | 18   |

|---|----------------------------------------------------------------------|------|

| • | 已添加 temperature default value VR_HOT and VR_FAULT Indication section | . 30 |

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **TPS53647**

ZHCSDV0B-JUNE 2015-REVISED FEBRUARY 2017

| • | Corrected factory default value of VOUT_OV_FAULT_RESPONSE command in 表 7 | . 38 |

|---|--------------------------------------------------------------------------|------|

| • | Corrected factory default value of VIN_OV_FAULT_LIMIT command in 表 7     | 38   |

| • | Corrected factory default value of MFR_ID command in 表 7                 | 39   |

| • | Corrected factory default value of MFR_SPECIFIC_44 command in 表 7        | 40   |

## Changes from Original (June 2015) to Revision A

| • | Updated the V <sub>ADDR-TRISE</sub> condition of the PADDR specification in the Electrical Characteristics table from "1.647 V" to "1.615 V"                                                                                                         | 8    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Updated the V <sub>OCL-R</sub> condition of the I <sub>OCLx</sub> specification in the Electrical Characteristics table from "0.8 V" to "0.85 V"                                                                                                     | 9    |

| • | Updated the V <sub>OCL-R</sub> condition of the I <sub>OCLx</sub> specification in the Electrical Characteristics table from "1.0 V" to "0.95 V"                                                                                                     | 9    |

| • | Updated the V <sub>OCL-R</sub> condition of the V <sub>RAMP</sub> specification in the Electrical Characteristics table to "±50 mV"                                                                                                                  | 9    |

| • | Updated the V <sub>SLEW-MODE</sub> condition of the V <sub>MODE</sub> specification in the Electrical Characteristics table from "1.647 V with ±20 mV tolerance" to "1.615 V with ±10 mV tolerance"                                                  | . 11 |

| • | Updated the V <sub>O-USR</sub> condition of the V <sub>USR</sub> specification in the Electrical Characteristics table from " V <sub>O-USR</sub> $\geq$ 1.55 V (USR OFF)" to "1.55 V $\leq$ V <sub>O-USR</sub> $\leq$ 1.6 V "                        | 11   |

| • | Updated the $V_{VBOOT}$ (B <sub>7</sub> B <sub>6</sub> B <sub>5</sub> B <sub>4</sub> ) condition of the $V_{BOOT}$ specification in the Electrical Characteristics table from "<br>1.647 V with ±20 mV tolerance" to "1.615 V with ±10 mV tolerance" | . 12 |

| • | Clarified the READ_VIN (88h) section                                                                                                                                                                                                                 | 69   |

| • | Corrected typographical error in READ_VOUT (8Bh) section                                                                                                                                                                                             | 71   |

| • | Clarified the READ_IOUT (8Ch) section                                                                                                                                                                                                                | 71   |

| • | Clarified the READ_TEMPERATURE_1 (8Dh) section                                                                                                                                                                                                       | 72   |

| • | Clarified the READ_POUT (96h) section                                                                                                                                                                                                                | 73   |

| • | Clarified the READ_POUT (96h) section                                                                                                                                                                                                                | 74   |

| • | Clarified the MFR_SPECIFIC_04 (Read VOUT) (D4h) section                                                                                                                                                                                              | 78   |

| • | Updated the MFR_SPECIFIC_14 (Ramp Height) (DEh) section                                                                                                                                                                                              | 86   |

| • | Clarified the Set the Load-Line section                                                                                                                                                                                                              | 97   |

| • | Updated Table 79                                                                                                                                                                                                                                     | 97   |

| • | Updated Table 82                                                                                                                                                                                                                                     | 98   |

| • | 已添加 接收文档更新通知 部分                                                                                                                                                                                                                                      | 114  |

| • | 已添加                                                                                                                                                                                                                                                  | 114  |

# www.ti.com.cn

Page

# 5 Pin Configuration and Functions

NC = No internal connection

#### **Pin Functions**

| PIN        |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO. |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |  |

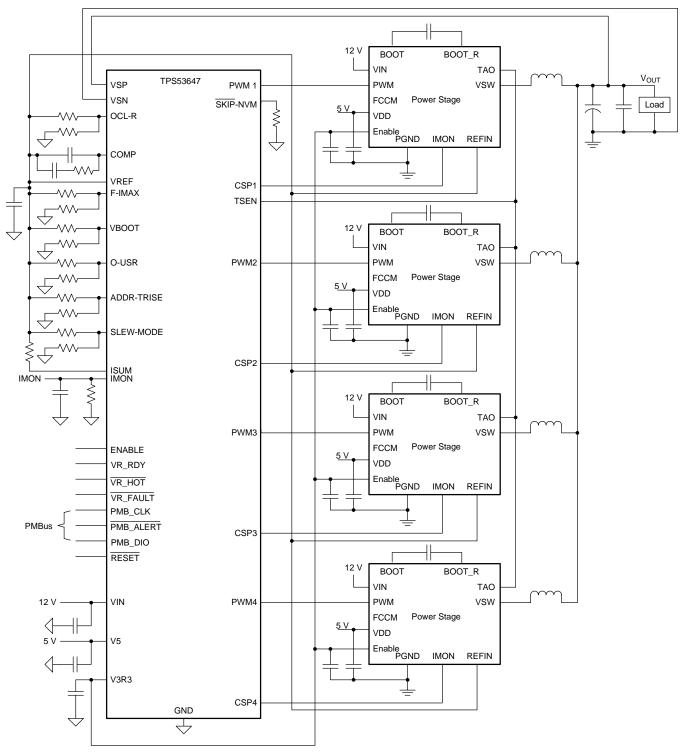

| ADDR-TRISE | 28  | I                  | Voltage divider to VREF pin. A resistor ( $R_{ADDR-TRISE}$ ) connected between this pin and GND sets the 3-bits. Bit 2 and bit 1 set the rise slew rate. Bit 0 Selects the LSB of BOOT voltage. The voltage ( $V_{ADDR-TRISE}$ ) sets 4 bits PMBus address. The device latches these settings when V3R3 powers up.                                                                        |  |

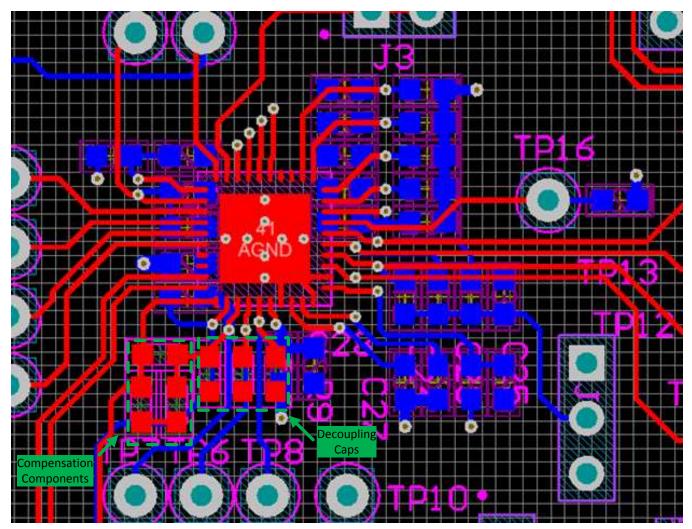

| COMP       | 11  | 0                  | Output of the $g_M$ error amplifier. Resistors and capacitors connected between this pin and the VREF pin set the compensation.                                                                                                                                                                                                                                                           |  |

| CSP1       | 3   |                    |                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CSP2       | 4   |                    | Positive current sense inputs. Connect to the IOUT pin of TI smart power stages (ex: CSD95372BQ5MC). Tie CSP4, CSP3, or CSP2 to the V3R3 pin according to 表 3 to disable the                                                                                                                                                                                                              |  |

| CSP3       | 5   |                    | corresponding phase.                                                                                                                                                                                                                                                                                                                                                                      |  |

| CSP4       | 6   |                    |                                                                                                                                                                                                                                                                                                                                                                                           |  |

| ENABLE     | 23  | I                  | VR enable. 1-V I/O level; 100-ns debounce.                                                                                                                                                                                                                                                                                                                                                |  |

| F-IMAX     | 32  | I                  | Voltage divider to VREF pin. A resistor (R <sub>F-IMAX</sub> ) connected between this pin and GND sets the operating frequency of the controller. The voltage level (V <sub>F-IMAX</sub> ) sets the maximum operating current of the converter. The IMAX value is an 8-bit A/D where V <sub>F-IMAX</sub> = V <sub>VREF</sub> × I <sub>MAX</sub> / 255. Both are latched at V3R3 power-up. |  |

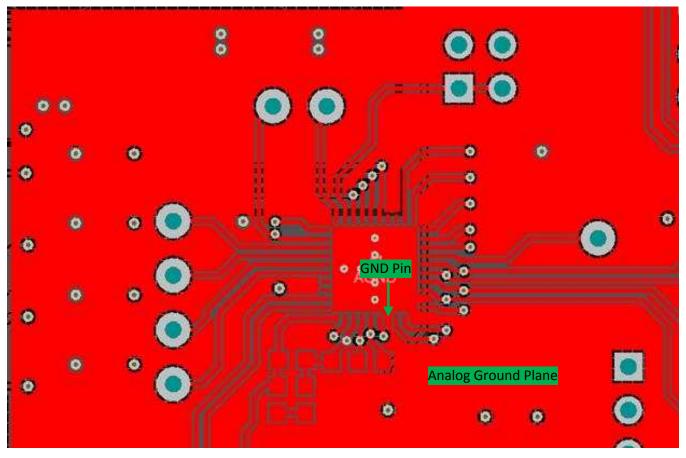

| GND        | 17  | G                  | Ground pin.                                                                                                                                                                                                                                                                                                                                                                               |  |

| GND        | 20  | G                  | Connect these nine to CND. Note this is not IC ground his                                                                                                                                                                                                                                                                                                                                 |  |

|            | 22  | 9                  | Connect these pins to GND. Note this is not IC ground pin.                                                                                                                                                                                                                                                                                                                                |  |

(1) I = Input, O = Output, P = Power, I/O = Bi-directional, GND = ground

TPS53647 ZHCSDV0B – JUNE 2015 – REVISED FEBRUARY 2017

www.ti.com.cn

NSTRUMENTS

Texas

# Pin Functions (continued)

| PIN       |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| IMON      | 2    | ο                  | $V_{IMON} = \frac{I_O \times 5 m\Omega \times R_{IMON}}{35 k\Omega}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ISUM      | 12   | 0                  | A resistor (R <sub>ISUM</sub> ) connected between this pin and VREF pin determines the droop.<br>$V_{ISUM} = \frac{I_O \times 5 m\Omega \times g_{M(isum)} \times R_{ISUM}}{n} + V_{REF}$ (where n is the number of phases)                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|           | 7    |                    | No connection Leave the nin open or pull up to V/2P3 nin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NO        | 8    | _                  | No connection. Leave the pin open or pull up to V3R3 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| NC        | 33   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|           | 34   | _                  | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| OCL-R     | 1    | I                  | A resistor (R <sub>OCL-R</sub> ) connected between this pin and GND and the voltage level (V <sub>OCL-R</sub> ) select 1 of 16 OCL levels (per phase current-limit). V <sub>OCL-R</sub> also sets one of four RAMP levels. The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                                               |  |  |  |

| O-USR     | 30   | I                  | Voltage divider to VREF pin. A resistor ( $R_{O-USR}$ ) connected between this pin and GND selects one of seven OSR thresholds or OFF. The voltage level ( $V_{O-USR}$ ) sets one of seven USR levels or OFF. The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                                                            |  |  |  |

| PMB_ALERT | 25   | 0                  | I <sup>2</sup> C PMBus interrupt line. Open drain. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PMB_CLK   | 24   | I                  | I <sup>2</sup> C PMBus clock. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PMB_DIO   | 26   | I/O                | I <sup>2</sup> C PMBus digital I/O line. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

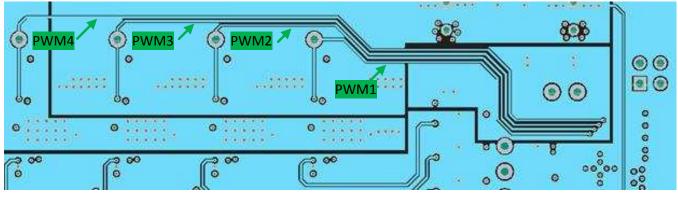

| PWM1      | 38   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PWM2      | 37   | 0                  | DW/M signals for each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| PWM3      | 36 O |                    | PWM signals for each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PWM4      | 35   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

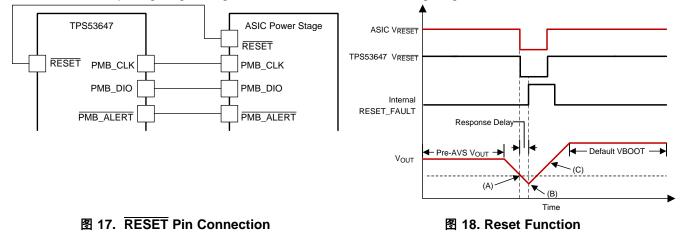

| RESET     | 21   | I                  | Reset pin. If this pin is low for more than 1000 ns, the controller pulls the output voltage to the $\rm V_{BOOT}$ level.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SKIP-NVM  | 39   | ο                  | A resistor (R <sub>SKIP-NVM</sub> ) connected between this pin and GND sets either pinstrap or NVM configurati<br>mode. This pin can also connect to the FCCM pin of TI smart power stages (ex: CSD95372BQ5MC<br>for SKIP or FCCM operation.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SLEW-MODE | 29   | I                  | Voltage divider to VREF pin. A resistor ( $R_{SLEW-MODE}$ ) connected between this pin and GND sets 8 slew rates. The voltage level ( $V_{SLEW-MODE}$ ) sets 4-bit operation modes. Bit 7 for DAC mode (1 for VR12.0; 0 for VR12.5). Bit 6 for the 4-phase interleaving mode (1 for 1/3 and 2/4 two phase interleaving; 0 for 4 phase interleaving individually). Bit 4 for enabling dynamic phase add or drop (1 for enable; 0 for disable). Bit 3 sets zero load-line (1 for zero load-line; 0 for non-zero load-line) The device latches these settings when V3R3 powers up. |  |  |  |

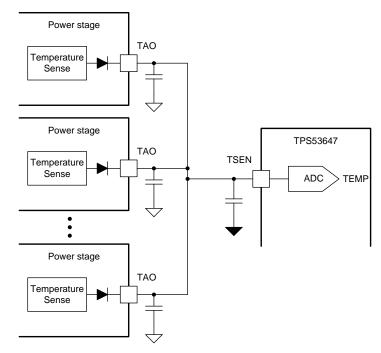

| TSEN      | 40   | I                  | Connect to the TAO/FAULT pin of TI smart power stages (ex: CSD95372BQ5MC) to sense the highest temperature of the power stages and to sense the fault signal from the power stages.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| V3R3      | 14   | 0                  | 3.3-V LDO output. Bypass this pin to GND with a ceramic capacitor with a value of $1-\mu F$ or larger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V5        | 15   | Р                  | 5-V power input. Bypass this pin to GND with a ceramic capacitor with a value of $1-\mu F$ or larger. This pin is used to power all internal analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VBOOT     | 31   | I                  | Voltage divider to VREF pin. A resistor ( $R_{VBOOT}$ ) connected between this pin and GND sets 3 bits (B[3:1]). The voltage level ( $V_{VBOOT}$ ) sets 4 bits (B[7:4]). The total 7 bits set 7 of 8 bits of VID of boot voltage (B[7:1]). The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                               |  |  |  |

| VIN       | 16   | Р                  | Input voltage supply. This pin is also used for input voltage sensing for on-time control and input undervoltage lockout (UVLO).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| VR_RDY    | 18   | 0                  | Power good open-drain output for the controller. This pin is typically pulled up to V3R3 pin through a esistor with a value of $3-k\Omega$ or larger.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VR_FAULT  | 27   | ο                  | VR fault indicator (open-drain). The failures include shorts of the high-side FETs, over temperature, output overvoltage, and overcurrent conditions of the input. The fault signal should be used on the platform to remove the power source either by firing a shunting SCR to blow a fuse or by turning off the AC power supply. When the failure occurs, the VR_FAULT pin is LOW. This pin is typically pulled up to V3R3 pin through a resistor with a value of 3-k $\Omega$ or larger. Leave this pin floating if not used.                                               |  |  |  |

| VR_HOT    | 19   | 0                  | Thermal flag open drain output. Active low. This pin is typically pulled up to V3R3 pin through a resistor with a value of $3$ -k $\Omega$ or larger. Leave this pin floating if not used.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

#### **Pin Functions (continued)**

| PIN         |     | 1/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                          |  |

|-------------|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | 1/0 ( /            | DESCRIPTION                                                                                                                                                                                                                                          |  |

| VREF        | 13  | 0                  | 1.7-V, 500- $\mu$ A, LDO reference voltage. Bypass this pin to GND with a ceramic capacitor with a value of 0.33 $\mu$ F. Connect the VREF pin to the REFIN pin of TI smart power stages (ex: CSD95372BQ5MC) as the current-sense reference voltage. |  |

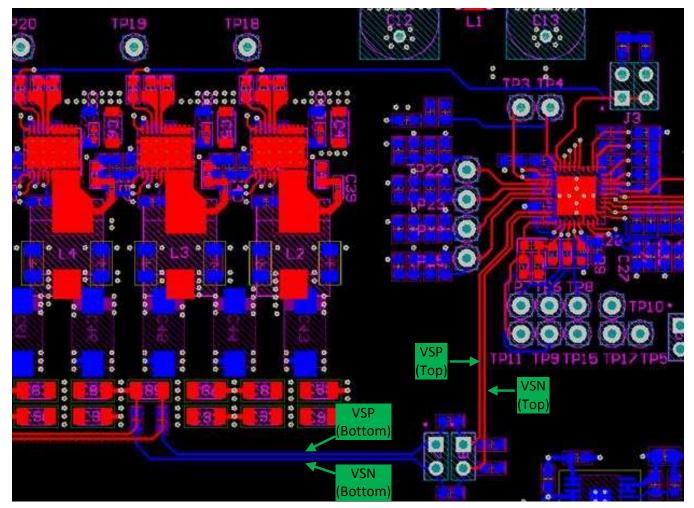

| VSN         | 10  | I                  | Negative input of the remote voltage sense amplifier. Connect this pin directly to the GND of the load.                                                                                                                                              |  |

| VSP         | 9   | I                  | Positive input of the remote voltage sense amplifier. Connect this pin directly to the load.                                                                                                                                                         |  |

| Thermal Pad |     | GND                | Thermal pad. Connect the thermal pad to the ground plane with multiple vias.                                                                                                                                                                         |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                    |                                                                                                                           | MIN  | MAX | UNIT |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                    | VIN                                                                                                                       | -0.3 | 19  |      |

|                    | V5                                                                                                                        | -0.3 | 6   |      |

| Input Voltage      | ADDR-TRISE, CSP1, C <u>SP2, C</u> SP3, CSP4, ENABLE, F-IMAX, OCL-R, O-USR, PMB_CLK, PMB_DIO, RESET, SLEW-MODE, VBOOT, VSP | -0.3 | 3.6 | V    |

|                    | TSEN                                                                                                                      | -0.3 | 6   |      |

|                    | GND, VSN                                                                                                                  | -0.3 | 0.3 |      |

|                    | VREF                                                                                                                      | -0.3 | 1.8 |      |

| Output Voltage     | IMON, ISUM, <u>PMB_ALERT</u> , PWM1, PWM2, PWM3, PWM4, <u>SKIP</u> -NVM, V3R3, VR_RDY, VR_FAULT, VR_HOT                   | -0.3 | 3.6 | V    |

|                    | COMP                                                                                                                      | -0.3 | 6   |      |

| Operating Junction | n Temperature, T <sub>J</sub>                                                                                             | -40  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal GND unless otherwise noted.

## 6.2 Handling Ratings

|                    |                     |                                                                                          | MIN  | MAX | UNIT |

|--------------------|---------------------|------------------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperature | e range                                                                                  | -55  | 150 | °C   |

|                    | Electrostatic       | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -2.5 | 2.5 |      |

| V <sub>(ESD)</sub> | discharge           | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1.5 | 1.5 | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

TEXAS INSTRUMENTS

#### **TPS53647**

ZHCSDV0B-JUNE 2015-REVISED FEBRUARY 2017

www.ti.com.cn

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                    |                                                                                   | MIN  | NOM | MAX        | UNIT |

|----------------|--------------------|-----------------------------------------------------------------------------------|------|-----|------------|------|

|                |                    | VIN                                                                               | 4.5  | 12  | 17         |      |

|                |                    | TSEN                                                                              | -0.1 |     | 5.5        |      |

|                |                    | V5                                                                                | 4.5  | 5   | 5.5        |      |

| VI             | Input voltage      | ADDR-TRISE, F-IMAX, OCL-R, O-USR, SLEW-MODE, VBOOT                                | 0.1  |     | $V_{VREF}$ | V    |

|                |                    | CSP1, CSP2, CSP3, CSP4, VSP                                                       | -0.1 |     | 2.5        |      |

|                |                    | ENABLE, PMB_CLK, PMB_DIO                                                          | -0.1 |     | 3.5        |      |

|                |                    | GND, VSN                                                                          | -0.1 |     | 0.1        |      |

|                |                    | VREF                                                                              | -0.1 |     | 1.72       |      |

|                |                    | V3R3                                                                              | -0.1 | 3.3 | 3.5        |      |

| Vo             | Output voltage     | IMON, ISUM, PMB_ALERT, PWM1, PWM2, PWM3, PWM4, SKIP-NVM, VR_RDY, VR_FAULT, VR_HOT | -0.1 |     | 3.5        | V    |

|                |                    | COMP                                                                              | -0.1 |     | 5.5        |      |

| T <sub>A</sub> | Operating free air | temperature                                                                       | -40  |     | 125        | °C   |

## 6.4 Thermal Information

|                       |                                              | TPS53647 |       |  |  |  |  |

|-----------------------|----------------------------------------------|----------|-------|--|--|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                |          |       |  |  |  |  |

|                       |                                              | 40 PINS  |       |  |  |  |  |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 30.6     |       |  |  |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.2     |       |  |  |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.9      | °C/W  |  |  |  |  |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2      | C/ VV |  |  |  |  |

| Ψјв                   | Junction-to-board characterization parameter | 6.8      |       |  |  |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.8      |       |  |  |  |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

| over recommended free-air temperature range, | , $V_{VIN} = 12 V$ , $V_{V5} = 5 V$ , $V_{VSN} = GND$ , | $V_{VSP} = V_{OUT}$ (unless otherwise noted). |

|----------------------------------------------|---------------------------------------------------------|-----------------------------------------------|

|----------------------------------------------|---------------------------------------------------------|-----------------------------------------------|

|                            | PARAMETER                             | TEST CONDITIONS                                                                                               | MIN   | TYP                    | MAX   | UNIT |

|----------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|------------------------|-------|------|

| SUPPLY: CURF               | RENTS, UVLO, AND POWER-ON RESET       |                                                                                                               |       |                        | ·     |      |

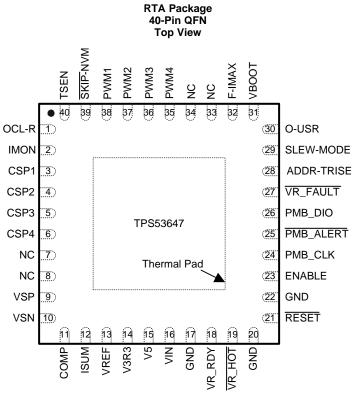

| I <sub>VIN</sub>           | VIN supply current, 4-phase active    | $V_{VDAC} < V_{VSP} < V_{VDAC}$ + 100 mV, ENABLE = HI                                                         |       |                        | 115   | μA   |

| I <sub>V5</sub>            | V5 supply current                     | PMBus Idle, ENABLE = HI                                                                                       |       | 6.1                    | 7     | mA   |

| I <sub>V5SBY</sub>         | V5 standby current                    | ENABLE = LO                                                                                                   |       | 2                      | 2.6   | mA   |

| V <sub>V3R3</sub>          | V3R3 output voltage                   | I <sub>V3R3</sub> = 0 A                                                                                       | 3.2   | 3.3                    | 3.4   | V    |

| V <sub>V3R3(dropout)</sub> | V3R3 load regulation                  | I <sub>V3R3</sub> = 5 mA                                                                                      |       |                        | 100   | mV   |

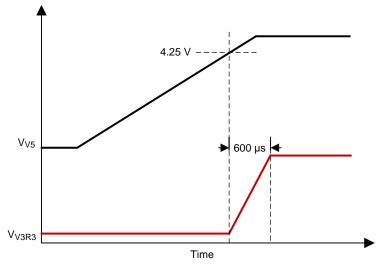

| V <sub>V5UVLOH</sub>       | V5 UVLO OK threshold                  | Ramp up                                                                                                       | 4.1   | 4.25                   | 4.5   | V    |

| V <sub>V5UVLOL</sub>       | V5 UVLO fault threshold               | Ramp down                                                                                                     | 3.95  | 4.05                   | 4.25  | V    |

| V <sub>HYS(V5)</sub>       | V5 UVLO hysteresis                    | Hysteresis                                                                                                    | 0.15  | 0.23                   | 0.3   | V    |

|                            |                                       | MFR_SPEC_16[1:0] = 00                                                                                         | 4.2   | 4.5                    | 4.7   |      |

|                            |                                       | MFR_SPEC_16[1:0] = 01                                                                                         | 6.9   | 7.25                   | 7.45  |      |

| V <sub>VINUVLO</sub>       | VIN UVLO voltage                      | MFR_SPEC_16[1:0] = 10                                                                                         | 8.6   | 9.0                    | 9.25  | V    |

|                            |                                       | MFR_SPEC_16[1:0] = 11                                                                                         | 9.8   | 10.3                   | 10.7  |      |

| V <sub>HYS(VIN)</sub>      | VIN UVLO hysteresis voltage           | Hysteresis voltage                                                                                            |       | 1                      |       | V    |

|                            | DAC AND VREF                          | , ,                                                                                                           |       |                        |       |      |

|                            |                                       | VR12.5: Change VID0 HI to LO to HI                                                                            |       | 10                     |       | mV   |

| V <sub>VIDSTP</sub>        | VID Step size                         | VR12.0: Change VID0 HI to LO to HI                                                                            |       | 5                      |       | mV   |

| V <sub>DAC1</sub>          | Closed Loop VSP tolerance             | VR12.0: 0.61 V $\leq V_{VSP} \leq 0.995$ V, $I_{OUT} = 0$ A, $0$ °C $\leq T_A \leq 85$ °C                     | -6    | ÷                      | 6.5   | mV   |

| V <sub>DAC2</sub>          | Closed Loop VSP tolerance             | $VR12.0: 1 V \le V_{VSP} \le 1.52 V, I_{COUT} = 0 A, 0 °C \le T_A \le 85 °C$                                  | -0.6  |                        | 0.6   | %    |

| V <sub>DAC3</sub>          | Closed Loop VSP tolerance             | $VR12.5: 1.50V \le V_{VSP} \le 2.50 \text{ V}, I_{OUT} = 0 \text{ A}, 0 \text{ °C} \le T_A \le 85 \text{ °C}$ | -1    |                        | 1     | %    |

|                            |                                       | $VR12.0: 0.61 V \le V_{VSP} \le 0.995 V, I_{OUT} = 0 A, -40^{\circ}C \le T_{A} \le 125$                       |       |                        |       |      |

| V <sub>DAC4</sub>          | Closed Loop VSP tolerance             | °C                                                                                                            | -8    |                        | 8     | mV   |

| V <sub>DAC5</sub>          | Closed Loop VSP tolerance             | VR12.0: 1.0 V ≤ $V_{VSP}$ ≤ 1.52 V, $I_{OUT}$ = 0 A, -40 °C ≤ $T_A$ ≤ 125 °C                                  | -0.8  |                        | 0.8   | %    |

| V <sub>DAC6</sub>          | Closed Loop VSP tolerance             | VR12.5: 1.50 V ≤ V <sub>VSP</sub> ≤ 2.50V, $I_{OUT}$ = 0 A, -40°C ≤ $T_A$ ≤ 125 °C                            | -1.1  |                        | 1.0   | %    |

| V <sub>VREF</sub>          | VREF output                           | $4.5 \le V_{V5} \le 5.5 \text{ V}, \text{ I}_{VREF} = 0 \text{ A}$                                            | 1.685 | 1.70                   | 1.717 | V    |

| V <sub>VREFSRC</sub>       | VREF output source                    | I <sub>VREF</sub> = 0 to 500 μA                                                                               | -4    | -1                     |       | mV   |

| V <sub>VREFSNK</sub>       | VREF output sink                      | $I_{VREF} = -500 \text{ to } 0 \ \mu\text{A}$                                                                 |       | 1                      | 4     | mV   |

| CURRENT SEN                | SE: AMPLIFIER AND PHASE BALANCING     | · · ·                                                                                                         |       |                        |       |      |

| G <sub>CSINT</sub>         | Internal current sense gain           | Gain from (CSPx – VREF ) to PWM comparator                                                                    |       | 1.0                    |       | V/V  |

| COMPENSATO                 | R: VOLTAGE POSITIONING AND AMPLIFIEF  | l l                                                                                                           |       |                        |       |      |

| g <sub>M(isum)</sub>       | ISUM amplifier transconductance       | V <sub>VSP</sub> = 1.7 V                                                                                      |       | 500                    |       | μS   |

| g <sub>M(comp)</sub>       | COMP amplifier transconductance       | V <sub>VSP</sub> = 1.7 V                                                                                      |       | 1000                   |       | μS   |

| V <sub>CCLAMPN</sub>       | COMP amplifier negative clamp voltage | (V <sub>VREF</sub> – V <sub>COMP</sub> )                                                                      |       | V <sub>RAMP</sub> + 20 |       | mV   |

| V <sub>CCLAMPP</sub>       | COMP amplifier positive clamp voltage | (V <sub>COMP</sub> - V <sub>VREF</sub> )                                                                      | 2.1   | 2.2                    | 2.3   | V    |

|                            | SE: VSP AND VSN                       |                                                                                                               |       |                        |       |      |

|                            | V/CD issue hiss surrent               | Not in fault, disable or UVLO,                                                                                |       |                        | 200   |      |

| I <sub>VSP</sub>           | VSP input bias current                | $V_{VSP} = V_{VDAC} = 2.3 \text{ V}, V_{VSN} = 0 \text{ V}$                                                   |       |                        | 300   | μA   |

| I <sub>VSN</sub>           | VSN input bias current                | Not in fault, disable or UVLO,<br>$V_{1} = V_{2} = 2.2 V_{1} V_{2} = 0 V_{2}$                                 | -30   | -23                    |       | μA   |

|                            | Transistor registeres                 | $V_{VSP} = V_{VDAC} = 2.3 \text{ V}, V_{VSN} = 0 \text{ V}$                                                   |       | 10                     |       | kO   |

|                            |                                       |                                                                                                               |       | 10                     |       | kΩ   |

| -                          |                                       | BLE) INTERFACE PINS: I/O VOLTAGE AND CURRENT                                                                  |       | 26                     | 50    |      |

| R <sub>RPGDL</sub>         | Open drain pull-down resistance       | VR_RDY, pulldown resistance at 0.31 V                                                                         |       | 36                     | 50    | Ω    |

|                            | Open drain leakage current            | VR_HOT, VR_RDY, hi-Z leakage, apply 3.3 V in off state                                                        | -2    | 0.2                    | 2     | μA   |

| V <sub>RSTL</sub>          | RESET logic low                       |                                                                                                               | 4.0   |                        | 0.8   | V    |

| V <sub>RSTH</sub>          | RESET logic high                      | RESET Pin                                                                                                     | 1.2   |                        |       | V    |

| T <sub>RSTTDLY</sub>       | RESET Delay Time                      |                                                                                                               |       | 1                      |       | μs   |

| V <sub>ENL</sub>           | ENABLE logic low                      |                                                                                                               | ~ ~   |                        | 0.3   | V    |

| V <sub>ENH</sub>           | ENABLE logic high                     |                                                                                                               | 0.8   |                        |       | V    |

| I <sub>ENH</sub>           | I/O 1.1- V leakage                    | Leakage current , $V_{ENABLE} = 1.1 V$                                                                        |       |                        | 25    | μA   |

|                            | FACE PINS: I/O VOLTAGE AND CURRENT    |                                                                                                               |       |                        |       |      |

| V <sub>PMBL</sub>          | PMBus pins logic low                  |                                                                                                               |       |                        | 0.8   | V    |

| V <sub>PMBH</sub>          | PMBus pins logic high                 |                                                                                                               | 1.2   |                        |       | V    |

| I <sub>PMBL</sub>          | Logic low input current               | V <sub>PMBus</sub> =0 V                                                                                       | -10   |                        | 10    | μA   |

| I <sub>PMBH</sub>          | Logic high input current              | V <sub>PMBus</sub> =1.8 V                                                                                     | -10   |                        | 10    | μΑ   |

# **Electrical Characteristics (continued)**

| PARAMETER          |                                               | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                   | MIN TYP | MAX | UNIT |

|--------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| ADDR-TRISE PIN     | PMBUS ADDRESS, SOFT START RISE TH             | ME SETTING                                                                                                                                                                                                                                                                                                                        |         |     |      |

|                    |                                               | $\begin{array}{l} R_{ADDR-TRISE} \leq 20 \; k\Omega \; \text{or} \; R_{ADDR-TRISE} = 24 \; k\Omega \; \text{or} \\ MFR\_SPEC\_12<1:0> = 00b \end{array}$                                                                                                                                                                          | 1       |     |      |

| 0                  |                                               | $R_{ADDR\text{-}TRISE}=30~k\Omega$ or $R_{ADDR\text{-}TRISE}=39~k\Omega$ or MFR_SPEC_12<1:0> = 01b                                                                                                                                                                                                                                | 1/2     |     |      |

| SL <sub>RISE</sub> | slew rate                                     | $\label{eq:RadDR-TRISE} \begin{array}{l} R_{\text{ADDR-TRISE}} = 56 \; k\Omega \; \text{or} \\ MFR\_SPEC\_12<1:0> = 10b \end{array}$                                                                                                                                                                                              | 1/4     |     |      |

|                    |                                               | $R_{aDDR\text{-}TRISE}$ = 100 k $\Omega$ or $R_{aDDR\text{-}TRISE}$ = 150 k $\Omega$ or MFR_SPEC_12<1:0> = 11b                                                                                                                                                                                                                    | 1/8     |     |      |

| BOOT               | BOOT voltage set (B0)                         | $\begin{array}{l} R_{\text{ADDR-TRISE}} \leq 20 \; \text{k}\Omega \; \text{or} \; R_{\text{ADDR-TRISE}} = 30 \; \text{k}\Omega \; \text{or} \; R_{\text{ADDR-TRISE}} = 56 \\ \text{k}\Omega \; \text{or} \; R_{\text{ADDR-TRISE}} = 100 \; \text{k}\Omega, \; \text{or} \; \text{MFR}\_\text{SPEC\_11} \; [0] = 0 \\ \end{array}$ | 0       |     |      |

|                    | BOOT Voltage set (BO)                         | $\begin{array}{l} R_{ADDR\text{-}TRISE} = 24 \ k\Omega \ or \ R_{ADDR\text{-}TRISE} = 39 \ k\Omega \ or \ R_{ADDR\text{-}TRISE} = 75 \\ k\Omega \ or \ R_{ADDR\text{-}TRISE} = 150 \ k\Omega, \ or \ MFR\_SPEC\_11 \ [0] = 1b \end{array}$                                                                                        | 1       |     |      |

|                    |                                               | $V_{ADDR-TRISE} \le 0.053 \text{ V}$ with ±20 mV tolerance                                                                                                                                                                                                                                                                        | 1100000 |     |      |

|                    |                                               | $V_{ADDR-TRISE} = 0.159 V$ with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1100001 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 0.266 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1100010 |     |      |

|                    |                                               | $V_{ADDR-TRISE} = 0.372 V$ with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1100011 |     |      |

|                    |                                               | $V_{ADDR-TRISE}$ = 0.478 V with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1100100 |     |      |

|                    |                                               | $V_{ADDR-TRISE} = 0.584 \text{ V}$ with ±20 mV tolerance                                                                                                                                                                                                                                                                          | 1100101 |     |      |

|                    |                                               | $V_{ADDR-TRISE} = 0.691 V$ with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1100110 |     |      |

| PADDR              | PMBus address bits set (11P₄0P₂P₁P₀)          | $V_{ADDR-TRISE} = 0.797 V$ with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1100111 |     |      |

| FADDR              | Findus address bits set ( $11F_40F_2F_1F_0$ ) | V <sub>ADDR-TRISE</sub> = 0.903 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1110000 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 1.009 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1110001 |     |      |

|                    |                                               | $V_{ADDR-TRISE}$ = 1.116 V with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1110010 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 1.222 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1110011 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 1.328 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1110100 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 1.434 V with ±20 mV tolerance                                                                                                                                                                                                                                                                           | 1110101 |     |      |

|                    |                                               | $V_{ADDR-TRISE}$ = 1.541 V with ±20 mV tolerance                                                                                                                                                                                                                                                                                  | 1110110 |     |      |

|                    |                                               | V <sub>ADDR-TRISE</sub> = 1.615 V with ±10 mV tolerance                                                                                                                                                                                                                                                                           | 1110111 |     |      |

# **Electrical Characteristics (continued)**

over recommended free-air temperature range,  $V_{VIN}$  = 12 V,  $V_{V5}$  = 5 V,  $V_{VSN}$  = GND,  $V_{VSP}$  =  $V_{OUT}$  (unless otherwise noted).

|                   | DADAMETER                                           |                                                                                                                             |     | T\/D |     | ,           |

|-------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------|

|                   |                                                     | TEST CONDITIONS                                                                                                             | MIN | TYP  | MAX | UNIT        |

| OCL-R PIN: 0      | OVERCURRENT THRESHOLDS AND RAME                     |                                                                                                                             |     |      |     |             |

|                   |                                                     | $R_{OCL-R}$ = 20 kΩ and $V_{OCL-R}$ ≤ 0.85 V or<br>MFR_SPEC_00[3:0] = 0000b                                                 | 21  | 24   | 27  |             |

|                   |                                                     | $R_{OCL-R}$ = 24 kΩ and V <sub>OCL-R</sub> ≤ 0.85 V or MFR_SPEC_00[3:0] = 0001b                                             | 25  | 27   | 30  |             |

|                   |                                                     | $R_{OCL-R}$ = 30 kΩ and $V_{OCL-R} \le 0.85$ V or<br>MFR_SPEC_00[3:0] = 0010b                                               | 28  | 30   | 33  |             |

|                   |                                                     | $R_{OCL-R}$ = 39 kΩ and $V_{OCL-R} \le 0.85$ V or<br>MFR_SPEC_00[3:0] = 0011b                                               | 31  | 33   | 36  |             |

|                   |                                                     | $R_{OCL-R} = 56 k\Omega$ and $V_{OCL-R} \le 0.85$ V or<br>MFR_SPEC_00[3:0] = 0100b                                          | 34  | 36   | 39  |             |

|                   |                                                     | $R_{OCL-R} = 75 \text{ k}\Omega$ and $V_{OCL-R} \le 0.85 \text{ V}$ or<br>MFR_SPEC_00[3:0] = 0101b                          | 37  | 39   | 42  |             |

|                   |                                                     | $R_{OCL-R} = 100 \text{ k}\Omega$ and $V_{OCL-R} \le 0.85 \text{ V or}$<br>MFR_SPEC_00[3:0] = 0110b                         | 40  | 42   | 45  |             |

|                   | Phase OCL level (CSPx-VREF)                         | $R_{OCL-R}$ ≥ 150 kΩ and $V_{OCL-R}$ ≤ 0.85 V or<br>MFR_SPEC_00[3:0] = 0111b                                                | 43  | 45   | 48  |             |

| l <sub>OCLx</sub> | (valley current-limit)                              | $R_{OCL-R} = 20 k\Omega$ and $V_{OCL-R} \ge 0.95$ V or<br>MFR_SPEC_00[3:0] = 1000b                                          | 46  | 48   | 51  | A           |

|                   |                                                     | $R_{OCL-R} = 24 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or<br>MFR_SPEC_00[3:0] = 1001b                          | 49  | 51   | 54  |             |

|                   |                                                     | $R_{OCL-R} = 30 k\Omega$ and $V_{OCL-R} \ge 0.95$ V or<br>MFR_SPEC_00[3:0] = 1010b                                          | 52  | 54   | 57  |             |

|                   |                                                     | $R_{OCL-R}$ = 39 kΩ and $V_{OCL-R} \ge 0.95$ V or<br>MFR_SPEC_00[3:0] = 1011b                                               | 55  | 57   | 60  |             |

|                   |                                                     | $R_{OCL-R} = 56 k\Omega$ and $V_{OCL-R} \ge 0.95$ V or<br>MFR_SPEC_00[3:0] = 1100b                                          | 58  | 60   | 63  |             |

|                   |                                                     | $R_{OCL-R} = 75 k\Omega$ and $V_{OCL-R} \ge 0.95$ V or<br>MFR_SPEC_00[3:0] = 1101b                                          | 61  | 63   | 66  |             |

|                   |                                                     | $R_{OCL-R}$ = 100 kΩ and V <sub>OCL-R</sub> ≥ 0.95 V or<br>MFR_SPEC_00[3:0] = 1110b                                         | 64  | 66   | 69  |             |

|                   |                                                     | $R_{OCL-R}$ ≥ 150 kΩ and $V_{OCL-R}$ ≥ 0.95 V or<br>MFR_SPEC_00[3:0] = 1111b                                                | 67  | 69   | 72  |             |

| V <sub>RAMP</sub> | Ramp setting                                        | $V_{OCL-R} = 0.2 V \pm 50mV \text{ or } V_{OCL-R} = 1.0 V \pm 50mV \text{ or } MFR_SPEC_14[2:0] = 001b$                     | 30  | 40   | 50  | $mV_{P\_P}$ |

|                   |                                                     | $V_{OCL-R}$ = 0.4 V $\pm 50mV$ or $V_{OCL-R}$ = 1.2 V $\pm 50mV$ or MFR_SPEC_14[2:0] = 011b                                 | 70  | 80   | 90  |             |

|                   |                                                     | $V_{OCL-R}$ = 0.6 V $\pm 50mV$ or $V_{OCL-R}$ = 1.4 V $\pm 50mV$ or MFR_SPEC_14[2:0] = 110b                                 | 135 | 145  | 155 |             |

|                   |                                                     | $V_{OCL-R}$ = 0.8 V $\pm 50mV$ or $V_{OCL-R}$ = 1.6 V $\pm 50mV$ or MFR_SPEC_14[2:0] = 111b                                 | 180 | 190  | 205 |             |

| F-IMAX PIN:       | FREQUENCY AND IMAX SETTINGS                         |                                                                                                                             |     |      |     |             |

| f <sub>sw</sub>   | Switching frequency (See Switching Characteristics) |                                                                                                                             |     |      |     |             |

|                   |                                                     | $V_{\text{F-IMAX}(\text{min})} = 0.136V \\ I_{\text{MAX}} = (V_{\text{F-IMAX}} / V_{\text{VREF}} \times 256) - 0.5$         | 18  | 20   | 22  |             |

| 1                 |                                                     |                                                                                                                             | 58  | 60   | 62  | ٨           |

| I <sub>MAX</sub>  | IMAX values                                         | $V_{\text{F-IMAX}(\text{min})} = 0.536 \text{ V}$ $I_{\text{MAX}} = (V_{\text{F-IMAX}} / V_{\text{VREF}} \times 256) - 0.5$ | 78  | 80   | 82  | A           |

|                   |                                                     | $V_{\text{F-IMAX}(\text{min})} = 0.803 \text{ V}$ $I_{\text{MAX}} = (V_{\text{F-IMAX}} / V_{\text{VREF}} \times 256) - 0.5$ | 118 | 120  | 122 |             |

|                   |                                                     |                                                                                                                             | -   |      |     |             |

# **Electrical Characteristics (continued)**

|                   | PARAMETER                                     | TEST CONDITIONS                                                                                                                                                                                   | MIN  | ТҮР  | MAX | UNIT  |  |  |

|-------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|--|--|

| SLEW-MODE PIN     | SLEW-MODE PIN: SLEW RATES and MODE SELECTIONS |                                                                                                                                                                                                   |      |      |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE}$ ≤ 20 kΩ<br>or MFR_SPEC_13[2:0] = 000b and MFR_SPEC_07[2] = 0b                                                                                                                     | 0.28 | 0.34 |     |       |  |  |

|                   |                                               | $\label{eq:RsLeW-MODE} \begin{array}{l} R_{SLEW-MODE} = 24 \ k\Omega \\ \mbox{or MFR}\_SPEC\_13[2:0] = 001b \mbox{ and MFR}\_SPEC\_07[2] = 0b \end{array}$                                        | 0.60 | 0.68 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE} = 30$ kΩ<br>or MFR_SPEC_13[2:0] = 010b and MFR_SPEC_07[2] = 0b                                                                                                                     | 0.91 | 1.02 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE}$ = 39 kΩ<br>or MFR_SPEC_13[2:0] = 011b and MFR_SPEC_07[2] = 0b                                                                                                                     | 1.22 | 1.36 |     |       |  |  |

|                   |                                               | $\label{eq:R_slew-MODE} \begin{array}{l} R_{\text{slew-MODE}} = 56 \ \text{k}\Omega \\ \text{or MFR}\_\text{SPEC}\_13[2:0] = 100b \ \text{and} \ \text{MFR}\_\text{SPEC}\_07[2] = 0b \end{array}$ | 1.53 | 1.7  |     |       |  |  |

|                   |                                               | $\label{eq:RsLeW-MODE} \begin{array}{l} R_{SLEW-MODE} = 75 \ k\Omega \\ \mbox{or MFR}\_SPEC\_13[2:0] = 101b \mbox{ and MFR}\_SPEC\_07[2] = 0b \end{array}$                                        | 1.85 | 2.04 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE}$ = 100 k $\Omega$ or MFR_SPEC_13[2:0] = 110b and MFR_SPEC_07[2] = 0b                                                                                                               | 2.16 | 2.38 |     |       |  |  |

| ei.               | Slew rate setting                             | R <sub>SLEW-MODE</sub> ≥ 150 kΩ<br>or MFR_SPEC_13[2:0] = 111b and MFR_SPEC_07[2] = 0b                                                                                                             | 2.48 | 2.74 |     | mV/µs |  |  |

| SL <sub>SET</sub> | Siew rate setting                             | $R_{SLEW-MODE} \le 20 \text{ k}\Omega$<br>or MFR_SPEC_13[2:0] = 000b and MFR_SPEC_07[2] = 1b                                                                                                      | 1.53 | 1.7  |     | πν/μs |  |  |

|                   |                                               | $\label{eq:RsLeW-MODE} \begin{array}{l} R_{SLEW-MODE} = 24 \ k\Omega \\ \text{or MFR}\_SPEC\_13[2:0] = 001b \ \text{and} \ \text{MFR}\_SPEC\_07[2] = 1b \end{array}$                              | 1.85 | 2.04 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE}$ = 30 k $\Omega$ or MFR_SPEC_13[2:0] = 010b and MFR_SPEC_07[2] = 1b                                                                                                                | 2.16 | 2.38 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE}$ = 39 k $\Omega$ or MFR_SPEC_13[2:0] = 011b and MFR_SPEC_07[2] = 1b                                                                                                                | 2.48 | 2.74 |     |       |  |  |

|                   |                                               | $\label{eq:RsLeW-MODE} \begin{array}{l} R_{SLEW-MODE} = 56 \ k\Omega \\ \mbox{or MFR}\_SPEC\_13[2:0] = 100b \ \mbox{and MFR}\_SPEC\_07[2] = 1b \end{array}$                                       | 2.79 | 3.08 |     |       |  |  |

|                   |                                               | $R_{SLEW-MODE} = 75 \text{ k}\Omega$<br>or MFR_SPEC_13[2:0] = 101b and MFR_SPEC_07[2] = 1b                                                                                                        | 3.10 | 3.43 |     |       |  |  |

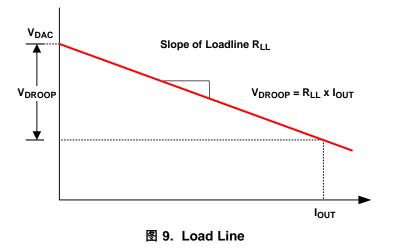

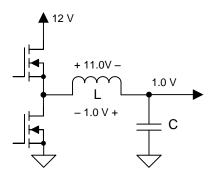

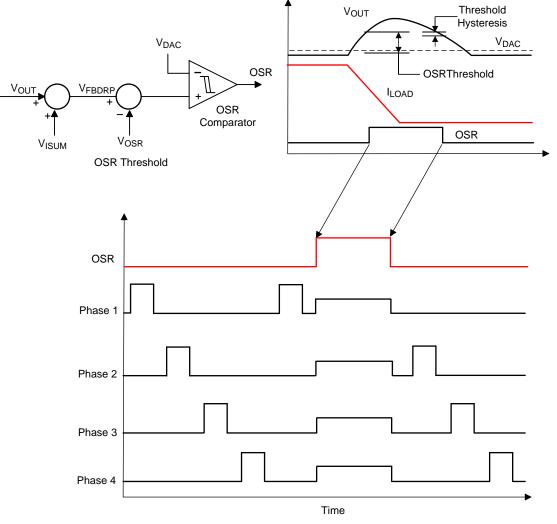

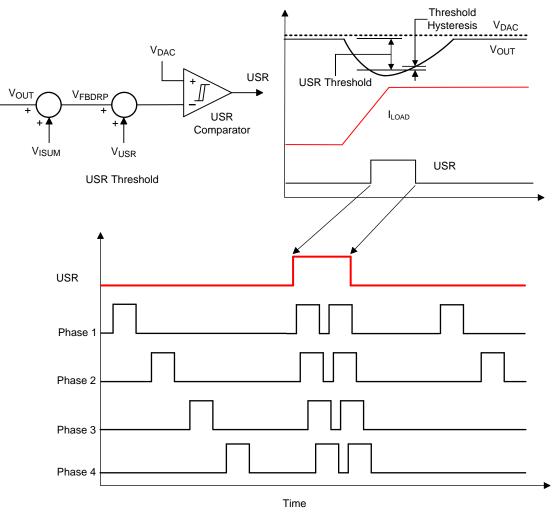

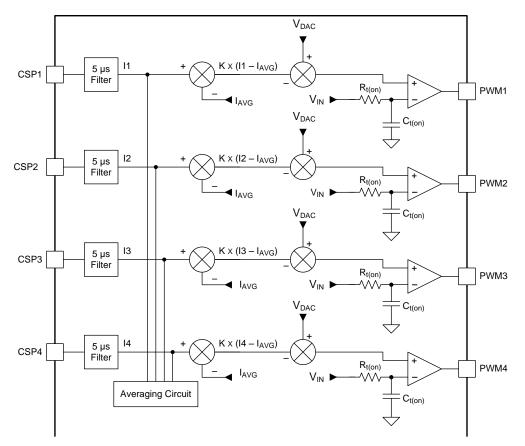

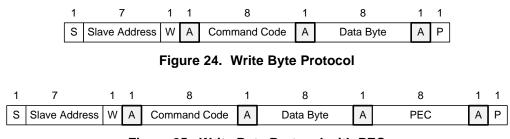

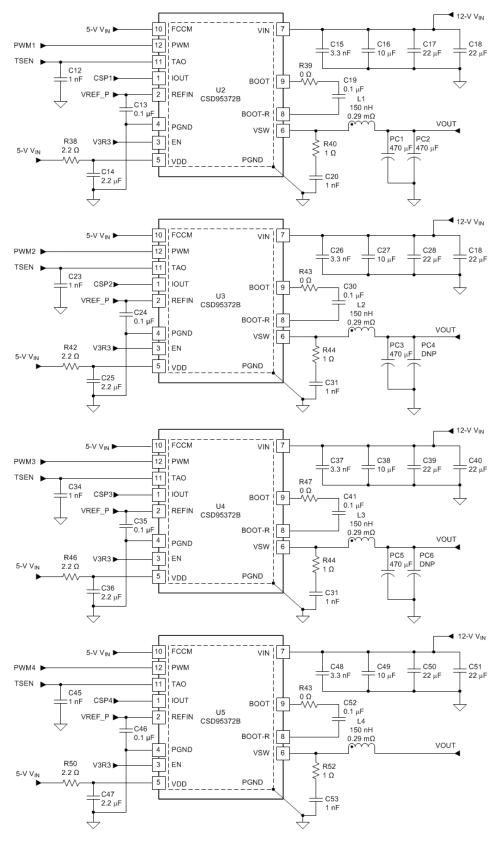

|                   |                                               | $R_{SLEW-MODE}$ = 100 k $\Omega$ or MFR_SPEC_13[2:0] = 110b and MFR_SPEC_07[2] = 1b                                                                                                               | 3.41 | 3.76 |     |       |  |  |