**TPS2596**

ZHCSJQ2A -MAY 2019-REVISED AUGUST 2019

# 具有精确电流监控器和快速过压保护功能的 TPS2596 2.7V 至 19V、 0.125A 至 2A、89mΩ 电子保险丝

#### 1 特性

- 宽输入电压范围: 2.7V 至 19V

- 绝对最大值为 21V

- 低导通电阻: Ron = 89mΩ (典型值)

- 带有可调节欠压锁定 (UVLO) 的高电平有效使能输

- 可用过压保护选项:

- 快速过压钳位(3.8V、5.7V 和 13.8V 引脚可选 阈值),响应时间为 5μs(典型值)

- 可调节过压锁定 (OVLO),响应时间为 1.3μs (典型值)

- 配备负载电流监控器输出 (ILM) 的可调节电流限制

- 电流范围: 0.125A 至 2A

- 电流限制准确度:

- 整个电流范围内为 ±10.4% (最大值)

- 在 1A 电流限制下为 ±5.5% (最大值)

- 不受电气快速瞬变干扰 (IEC 61000-4-4)

- 可调节的输出压摆率控制 (dVdt)

- 提供过热保护 (OTP)

- 故障指示引脚 (FLT)

- UL2367 认证正在处理中

- IEC 62368 CB 认证(正在申请中)

- 小尺寸: 4.91mm x 3.9mm SOIC 封装

#### 2 应用

- 能量计

- UL 60335-1 15W LPC 在电器中的应用

- 冰箱

- 洗碗机

- 洗衣机和烘干机

- 机顶盒

- IP 网络摄像头

#### 3 说明

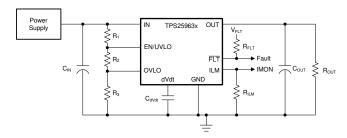

TPS2596xx 系列电子保险丝(集成式 FET 热插拔器件)是采用小型封装且高度集成的电路保护和电源管理解决方案。这些设备只需很少的外部组件即可提供多种保护模式,能够非常有效地抵御过载、短路、电压浪涌和过多浪涌电流。输出电流限制级别可通过单个外部电阻设定。还可能通过测量整个电流限制电阻的压降实现对输出负载电流的准确感应。对 浪涌电流有特别要求的应用可以通过单个外部电容器设定输出转换率。对于TPS25962x 型号,发生输入过压情况时,内部钳位电路会将输出限制在一个安全的固定最大电压(引脚可选),而无需外部组件。TPS25963x 型号使用户可以设置指定的过压截止阈值。

这些器件的额定工作结温范围为 -40℃ 至 +125℃。

#### 器件信息(1)

|              | HI I I II IO |                |  |  |  |  |  |

|--------------|--------------|----------------|--|--|--|--|--|

| 器件型号         | 封装           | 封装尺寸(标称值)      |  |  |  |  |  |

| TPS259620DDA | SOIC (8)     | 4.91mm x 3.9mm |  |  |  |  |  |

| TPS259621DDA | SOIC (8)     | 4.91mm x 3.9mm |  |  |  |  |  |

| TPS259630DDA | SOIC (8)     | 4.91mm x 3.9mm |  |  |  |  |  |

| TPS259631DDA | SOIC (8)     | 4.91mm x 3.9mm |  |  |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

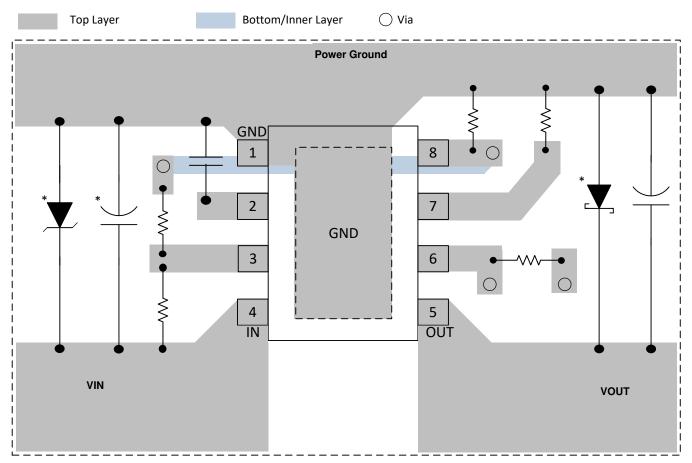

#### 简化原理图

#### TPS25963x 1KV EFT 响应

|   | 目                                       | 录  |                                                              |                |

|---|-----------------------------------------|----|--------------------------------------------------------------|----------------|

| 1 | 特性                                      |    | 8.4 Device Functional Modes                                  | 2!             |

| 2 | 应用 1                                    | 9  | Application and Implementation                               | 27             |

| 3 | 说明 1                                    |    | 9.1 Application Information                                  |                |

| 4 | 修订历史记录                                  |    | 9.2 Typical Application                                      |                |

| 5 | 器件比较表                                   |    | 9.3 System Examples                                          | 3 <sup>-</sup> |

| 6 | Pin Configuration and Functions         | 10 | Power Supply Recommendations                                 | 34             |

| 7 | Specifications 5                        |    | 10.1 Transient Protection                                    | 34             |

| ' | 7.1 Absolute Maximum Ratings            |    | 10.2 Output Short-Circuit Measurements                       | 3!             |

|   |                                         | 11 | Layout                                                       | 36             |

|   | 7.2 ESD Ratings                         |    | 11.1 Layout Guidelines                                       |                |

|   | 7.4 Thermal Information                 |    | 11.2 Layout Example                                          |                |

|   | 7.5 Electrical Characteristics 6        | 12 |                                                              |                |

|   | 7.6 Timing Requirements                 |    | 12.1 文档支持                                                    |                |

|   | 7.7 Switching Characteristics           |    | 12.2 接收文档更新通知                                                |                |

|   | •                                       |    | 12.3 社区资源                                                    |                |

|   | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |    | 12.4 商标                                                      |                |

| 8 | Detailed Description                    |    | 12.5 静电放电警告                                                  |                |

|   | 8.1 Overview                            |    | 12.6 Glossary                                                |                |

|   | 8.2 Functional Block Diagram            | 13 |                                                              |                |

|   | 8.3 Feature Description                 | 13 | 、 小のがく 〒14次7日・2 14 次2 日 12 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |                |

# 4 修订历史记录

| Ch | hanges from Original (May 2019) to Revision A | Page |

|----|-----------------------------------------------|------|

| •  | 将"预告信息"更改为"生产数据"                              | 1    |

# 5 器件比较表

| 部件号       | 过压响应                        | 热关断 <b>(TSD)</b> 响应 |

|-----------|-----------------------------|---------------------|

| TPS259620 | OVC - 3.8V、5.7V、13.8V(引脚可选) | 闭锁                  |

| TPS259621 | OVC - 3.8V、5.7V、13.8V(引脚可选) | 自动重试                |

| TPS259630 | 可调 OVLO                     | 闭锁                  |

| TPS259631 | 可调 OVLO                     | 自动重试                |

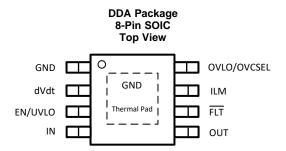

# 6 Pin Configuration and Functions

#### **Pin Functions**

| Р                                                      | IN | 1/0              | DESCRIPTION                                                                                                                                                                                                             |  |  |

|--------------------------------------------------------|----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.                                               |    | .,0              | DECOMI HOM                                                                                                                                                                                                              |  |  |

| GND                                                    | 1  | Ground           | Ground                                                                                                                                                                                                                  |  |  |

| dVdt                                                   | 2  | Analog<br>Output | A capacitor from this pin to GND sets the output turn on slew rate. Leave this pin floating for the fastest turn on slew rate.                                                                                          |  |  |

| EN/UVLO                                                | 3  | Analog Input     | Active High Enable for the Device. A resistor divider can be used to adjust the Undervoltage Lockout threshold. <b>Do not leave floating.</b>                                                                           |  |  |

| IN                                                     | 4  | Power            | Power Input                                                                                                                                                                                                             |  |  |

| OUT                                                    | 5  | Power            | Power Output                                                                                                                                                                                                            |  |  |

| FLT                                                    | 6  | Digital Output   | Active Low indicator which will be pulled low when a fault is detected. It is an open-drain output that requires an external pull-up resistance.                                                                        |  |  |

| ILM                                                    | 7  | Analog<br>Output | This is a dual function pin used to limit and monitor the output current. An external resistor from this pin to GND sets the output current limit. The pin voltage can also be used to monitor the output load current. |  |  |

| OVLO                                                   |    | A                | TPS25963x: A resistor divider can be used to adjust the Overvoltage Lockout threshold. Do not leave floating.                                                                                                           |  |  |

| OVCSEL  8 Analog Input TPS25962x: Overvoltage details. |    | Analog Input     | <b>TPS25962x:</b> Overvoltage Clamp level select pin. Refer to <i>Overvoltage Clamp</i> for more details.                                                                                                               |  |  |

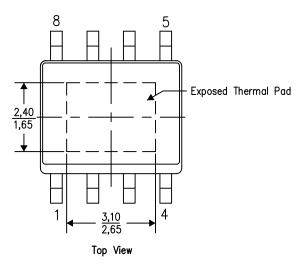

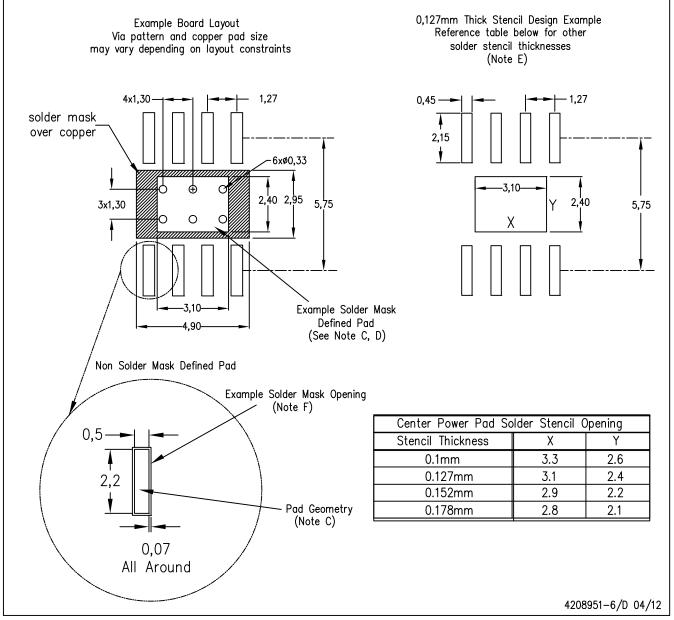

| Thermal pad                                            |    | Ground           | The Exposed Pad is used primarily for heat dissipation and must be connected to system ground plane for best thermal performance.                                                                                       |  |  |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                      | PARAMETER                                            | PIN         | MIN M                             | AX  | UNITS |

|----------------------|------------------------------------------------------|-------------|-----------------------------------|-----|-------|

|                      | Maximum Input Voltage Range                          | INI         | -0.3                              | 21  | V     |

| $V_{IN}$             | Maximum Input Voltage Range (T <sub>A</sub> = 25 °C) | IN          |                                   | 22  | V     |

| V <sub>OUT</sub>     | Maximum Output Voltage Range                         | OUT         | -0.3 min (21, V <sub>IN</sub> + 0 | .3) | V     |

| V <sub>EN/UVLO</sub> | Maximum Enable Pin Voltage Range                     | EN/UVLO     | -0.3                              | 7   | V     |

| V <sub>OV</sub>      | Maximum OVCSEL/OVLO Pin Voltage Range                | OVCSEL/OVLO | -0.3                              | 7   | V     |

| V <sub>dVdT</sub>    | Maximum dVdT Pin Voltage Range                       | DVDT        |                                   | 2.5 | V     |

| $V_{FLTB}$           | Maximum FLTb Pin Voltage Range                       | FLT         | -0.3                              | 7   | V     |

| I <sub>FLTB</sub>    | Maximum FLTb Pin Sink Current                        | FLT         |                                   | 10  | mA    |

| I <sub>MAX</sub>     | Maximum Continuous Switch Current                    | IN to OUT   | Internally Limited                |     | Α     |

| TJ                   | Junction temperature                                 |             | Internally Limited                |     | °C    |

| T <sub>LEAD</sub>    | Maximum Lead Temperature                             |             | 3                                 | 800 | °C    |

| T <sub>stg</sub>     | Storage temperature                                  |             | <b>-65</b> 1                      | 50  | °C    |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                                                                         | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|-------|------|

| M                  | Clastrostatia diaphara  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>             | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                               | PIN       | MIN | MAX               | UNITS |

|----------------------|-----------------------------------------|-----------|-----|-------------------|-------|

| $V_{IN}$             | Input Voltage Range                     | IN        | 2.7 | 19 <sup>(1)</sup> | V     |

| V <sub>OUT</sub>     | Output Voltage Range                    | OUT       |     | $V_{IN} + 0.3$    | V     |

| V <sub>EN/UVLO</sub> | Enable Pin Voltage Range                | EN/UVLO   |     | 6 <sup>(2)</sup>  | V     |

| V <sub>OV</sub>      | OVLO Pin Voltage Range (TPS25963x Only) | OVLO      | 0.5 | 2                 | V     |

| $V_{dVdT}$           | dVdT Pin Capacitor Voltage Rating       | DVDT      | 4   |                   | V     |

| $V_{FLTB}$           | FLTB Pin Voltage Range                  | FLT       |     | 6                 | V     |

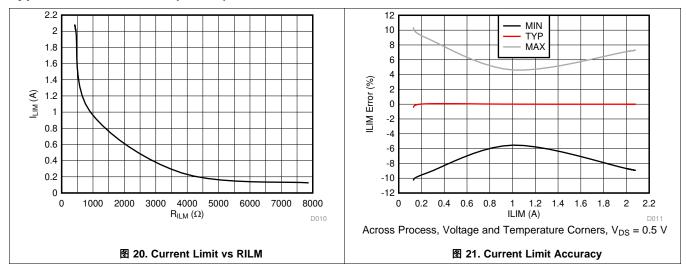

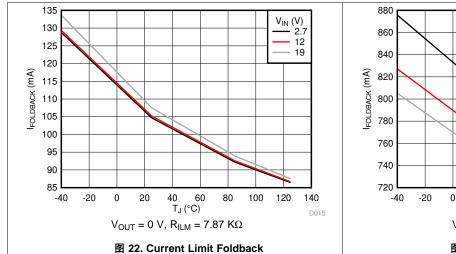

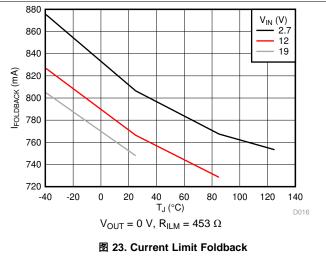

| R <sub>ILM</sub>     | ILM Pin Resistance                      | ILM       | 453 | 7869              | Ω     |

| I <sub>MAX</sub>     | Continuous Switch Current               | IN to OUT |     | 2                 | Α     |

| TJ                   | Junction temperature                    |           | -40 | 125               | °C    |

<sup>(1)</sup> For TPS25962x, the input voltage should be limited to the selected Output Voltage Clamp Option as listed in the Electrical Characteristics section

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> For supply voltages below 6V, it is okay to pull up the EN pin to IN through a resistor of 100 KΩ or higher. For supply voltages greater than 6V, it is recommended to use an appropriate resistor divider between IN, EN and GND to ensure the voltage at the EN pin is within the specified limits.

#### 7.4 Thermal Information

|                 |                                              | TPS2596X             |      |

|-----------------|----------------------------------------------|----------------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>                | DDA (SOIC-EP)        | UNIT |

|                 |                                              | 8 PINS               |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 52.7 <sup>(2)</sup>  | °C/W |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 119.8 <sup>(3)</sup> | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 8.9 <sup>(2)</sup>   | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 17.5 <sup>(3)</sup>  | °C/W |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 27.1 <sup>(2)</sup>  | °C/W |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 68.1 <sup>(3)</sup>  | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

(Test conditions unless otherwise noted)  $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 125^{\circ}\text{C}$ ,  $\text{V}_\text{IN} = 12~\text{V}$ ,  $\text{R}_\text{ILM} = 453~\Omega$ ,  $\text{C}_\text{dVdT} = \text{Open}$ , OUT = Open. All voltages referenced to GND.

|                     | PARAMETER                                                                                | TEST CONDITIONS                                                                                             | MIN    | TYP    | MAX      | UNITS |

|---------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|--------|----------|-------|

| INPUT SUF           | PPLY (IN)                                                                                |                                                                                                             |        |        |          |       |

|                     |                                                                                          | TPS25963x                                                                                                   |        | 193    | 259      | μΑ    |

| IQ                  | IN quiescent current                                                                     | TPS25962x                                                                                                   |        | 206    | 266      | μA    |

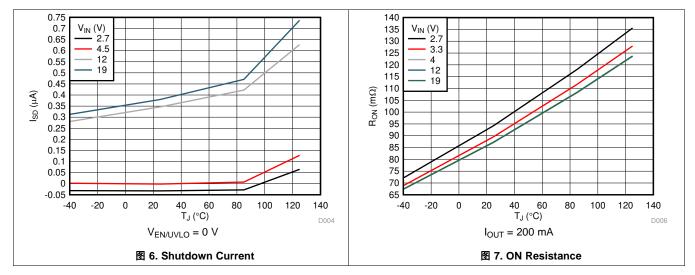

|                     | IN Shutdown Current                                                                      | V <sub>IN</sub> < 4 V, V <sub>EN/UVLO</sub> < V <sub>SD</sub>                                               |        |        | 0.1      | μΑ    |

| I <sub>SD</sub>     |                                                                                          | V <sub>IN</sub> ≥ 4 V, V <sub>EN/UVLO</sub> < V <sub>SD</sub>                                               |        | 0.4    | 1.132    | μΑ    |

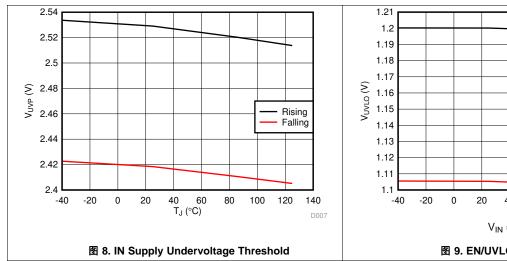

| V <sub>UVP(R)</sub> | IN Undervoltage Protection                                                               | V <sub>IN</sub> Rising                                                                                      | 2.46   | 2.53   | 2.58     | V     |

| $V_{UVP(F)}$        | threshold                                                                                | V <sub>IN</sub> Falling                                                                                     | 2.36   | 2.42   | 2.46     | V     |

|                     | IN Undervoltage Protection<br>Hysteresis                                                 |                                                                                                             |        | 110    |          | mV    |

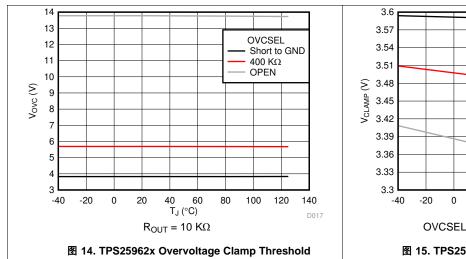

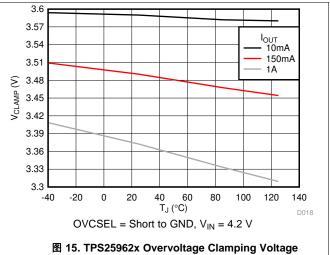

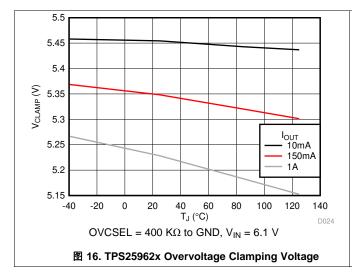

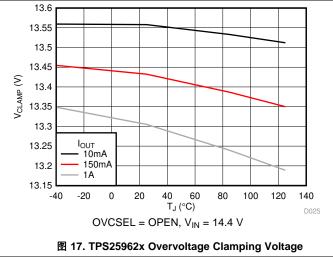

| OUTPUT V            | OLTAGE CLAMP (OUT) - TPS259                                                              | 962X                                                                                                        |        |        | <u> </u> |       |

|                     |                                                                                          | $R_{OVCSEL}$ = Short to GND,<br>$R_{OUT}$ = 10 K $\Omega$                                                   | 3.75   | 3.83   | 3.92     | V     |

| V <sub>OVC</sub>    | Overvoltage Clamp<br>Threshold                                                           | $R_{OVCSEL} = 400 \text{ K}\Omega \text{ to GND},$<br>$R_{OUT} = 10 \text{ K}\Omega$                        | 5.54   | 5.69   | 5.83     | V     |

|                     |                                                                                          | $R_{OVCSEL} = OPEN, R_{OUT} = 10$<br>$K\Omega$                                                              | 12.97  | 13.77  | 14.52    | V     |

|                     |                                                                                          | R <sub>OVCSEL</sub> = Short to GND,<br>I <sub>OUT</sub> = 10 mA                                             | 3.47   | 3.59   | 3.7      | V     |

| $V_{CLAMP}$         | Output Voltage During Clamping                                                           | $R_{OVCSEL} = 400 \text{ K}\Omega \text{ to GND},$<br>$I_{OUT} = 10 \text{ mA}$                             | 5.28   | 5.45   | 5.61     | V     |

|                     |                                                                                          | R <sub>OVCSEL</sub> = OPEN, I <sub>OUT</sub> = 10 mA                                                        | 13.13  | 13.58  | 13.97    | V     |

| оитрит с            | CURRENT LIMIT AND MONITOR (                                                              | ILM)                                                                                                        |        |        |          |       |

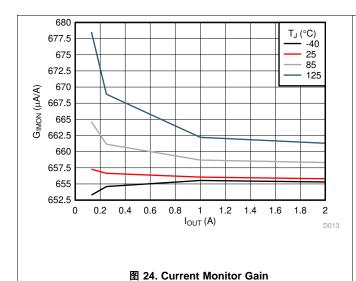

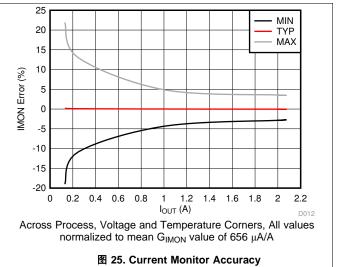

| _                   | Current monitor gain                                                                     | I <sub>OUT</sub> = 0.13 A                                                                                   | 531.22 | 653.21 | 800.00   | μΑ/Α  |

| G <sub>IMON</sub>   | as measured on ILM pin ( $I_{\rm ILM}$ / $I_{\rm OUT}$ )                                 | I <sub>OUT</sub> = 2 A                                                                                      | 635.77 | 657.15 | 684.05   | μA/A  |

|                     |                                                                                          | $R_{ILM} = 7.87 \text{ K}\Omega, V_{DS} = 0.5$<br>V, $-40^{\circ}\text{C} \le T_{A} \le 80^{\circ}\text{C}$ | 0.113  | 0.125  | 0.139    | Α     |

|                     |                                                                                          | $R_{ILM} = 3.83 \text{ K}\Omega, V_{DS} = 0.5 \text{ V}$                                                    | 0.224  | 0.247  | 0.269    | Α     |

| LIM                 | I <sub>OUT</sub> Current Limit                                                           | $R_{ILM} = 909 \Omega, V_{DS} = 0.5 V$                                                                      | 0.949  | 1.005  | 1.051    | Α     |

|                     |                                                                                          | $R_{ILM} = 453 \Omega, V_{DS} = 0.5 V$                                                                      | 1.83   | 2.004  | 2.147    | Α     |

|                     |                                                                                          | R <sub>ILM</sub> = OPEN                                                                                     |        | 0      |          | Α     |

| Ісв                 | I <sub>OUT</sub> Circuit Breaker<br>Threshold<br>during R <sub>ILM</sub> Short condition | R <sub>ILM</sub> = Short to GND (Single<br>Point Failure Test IEC<br>62368-1)                               |        |        | 1.5      | А     |

<sup>(2)</sup> With exposed pad soldered to PCB

<sup>(3)</sup> Without exposed pad soldered to PCB

# **Electrical Characteristics (continued)**

(Test conditions unless otherwise noted) –40°C ≤  $T_J$  ≤ 125°C,  $V_{IN}$  = 12 V ,  $R_{ILM}$  = 453  $\Omega$  ,  $C_{dVdT}$  = Open, OUT = Open. All voltages referenced to GND.

|                      | PARAMETER                                             | TEST CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS     |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-----------|

| ON-RESIST            | ANCE (IN TO OUT)                                      |                                                                                 |       |       |       |           |

|                      |                                                       | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = 25 °C         |       | 97    | 99.8  | mΩ        |

| R <sub>ON</sub>      |                                                       | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 85 °C  |       |       | 125.4 | mΩ        |

|                      | ON State Resistance                                   | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 125 °C |       |       | 143.4 | $m\Omega$ |

|                      | ON State Resistance                                   | $V_{IN} > 4 \text{ V}, I_{OUT} = 0.2 \text{ A}, T_{J} = 25 \text{ °C}$          |       | 89    | 92.6  | mΩ        |

|                      |                                                       | V <sub>IN</sub> > 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 85 °C  |       |       | 115.3 | mΩ        |

|                      |                                                       | V <sub>IN</sub> > 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 125 °C |       |       | 131   | $m\Omega$ |

| ENABLE/U             | NDERVOLTAGE LOCK OUT (E                               | N/UVLO)                                                                         |       |       |       |           |

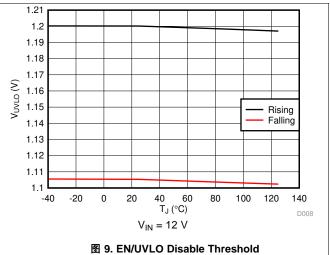

| V <sub>UVLO(R)</sub> | LIVII O Throokald                                     | V <sub>EN</sub> Rising                                                          | 1.18  | 1.2   | 1.22  | V         |

| V <sub>UVLO(F)</sub> | UVLO Threshold                                        | V <sub>EN</sub> Falling                                                         | 1.08  | 1.1   | 1.13  | V         |

| ` '                  | UVLO Hysteresis                                       |                                                                                 |       | 95    |       | mV        |

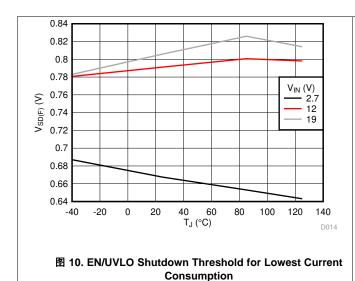

| V <sub>SD</sub>      | V <sub>EN</sub> threshold for lowest shutdown current | V <sub>EN</sub> Falling                                                         | 0.53  |       | 1.05  | V         |

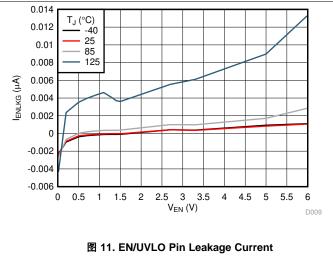

| I <sub>ENLKG</sub>   | EN leakage current                                    |                                                                                 | -0.1  |       | 0.1   | μΑ        |

| OVERVOL1             | AGE LOCKOUT (OVLO) - TPS                              | 25963X                                                                          |       |       |       |           |

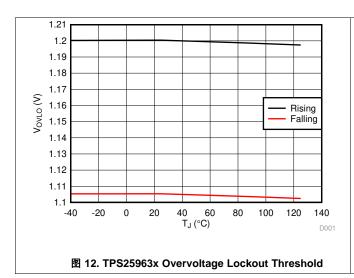

| V <sub>OVLO(R)</sub> | OVII O There also also                                | V <sub>OVLO</sub> Rising                                                        | 1.17  | 1.2   | 1.22  | V         |

| V <sub>OVLO(F)</sub> | OVLO Threshold                                        | V <sub>OVLO</sub> Falling                                                       | 1.08  | 1.1   | 1.13  | V         |

| ` '                  | OVLO Hysteresis                                       |                                                                                 |       | 95    |       | mV        |

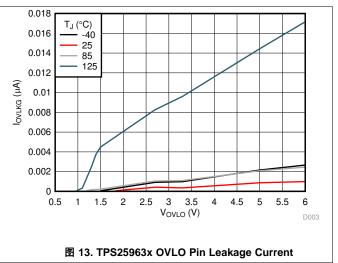

| I <sub>OVLKG</sub>   | OVLO pin leakage current                              | 0.5 ≤ V <sub>OVLO</sub> ≤1.5V                                                   | -0.1  |       | 0.1   | uA        |

| FAULT IND            | ICATION (FLT)                                         |                                                                                 |       |       | "     |           |

| R <sub>FLTB</sub>    | FLT Internal Pull-down resistance                     | FLT asserted                                                                    |       | 11.52 |       | Ω         |

| I <sub>FLTLKG</sub>  | FLT pin leakage current                               | FLT de-asserted, pull-up voltage 6 V                                            | -1    |       | 1     | μΑ        |

| OVERTEME             | PERATURE PROTECTION (OTF                              | ?)                                                                              |       |       | •     |           |

| TSD                  | Thermal Shutdown Rising Threshold                     | T <sub>J</sub> Rising                                                           |       | 157   |       | °C        |

| TSD <sub>HYS</sub>   | Thermal Shutdown<br>Hysteresis                        | T <sub>J</sub> Falling                                                          |       | 11.5  |       | °C        |

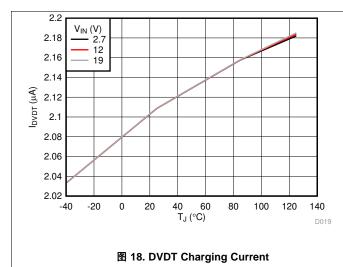

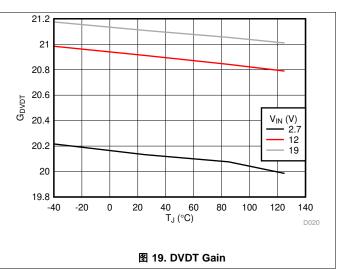

| DVDT                 |                                                       |                                                                                 |       |       |       |           |

| I <sub>DVDT</sub>    | dVdt Pin Charging Current                             |                                                                                 | 1.89  | 2.11  | 2.33  | μΑ        |

| G <sub>DVDT</sub>    | DVDT gain                                             |                                                                                 | 20.31 | 20.93 | 21.5  | V         |

#### 7.6 Timing Requirements

Typical Values are taken at  $T_J = 25^{\circ}$ C unless specifically noted otherwise.

|                      | PARAMETER                                   | TEST CONDITIONS                                                                     | MIN | TYP | MAX | UNITS |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>LIM</sub>     | Current limit response time                 | I <sub>OUT</sub> > 20% over I <sub>LIM</sub> to I <sub>OUT</sub> ≤ I <sub>LIM</sub> |     | 87  |     | μs    |

| t <sub>SC</sub>      | Short circuit response time                 | V <sub>OUT</sub> ↓ to I <sub>OUT</sub> ≤ I <sub>LIM</sub>                           |     | 5   |     | μs    |

| t <sub>OVLO</sub>    | Overvoltage lockout response time           | TPS25963x Only                                                                      |     | 1.3 |     | μs    |

| tovc                 | Output clamp response time                  | TPS25962x Only , I <sub>OUT</sub> = 2 A                                             |     | 5   |     | μs    |

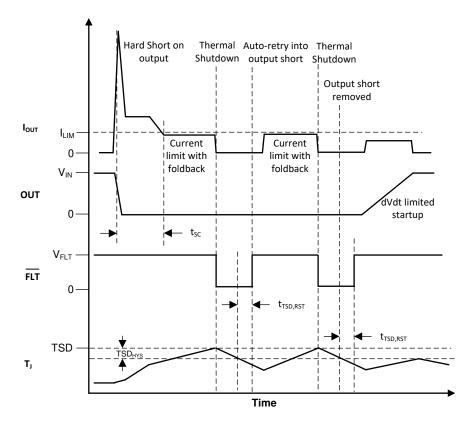

| t <sub>TSD,RST</sub> | Thermal Shutdown Auto-<br>Retry<br>Interval | TPS2596x1 Only                                                                      |     | 95  |     | ms    |

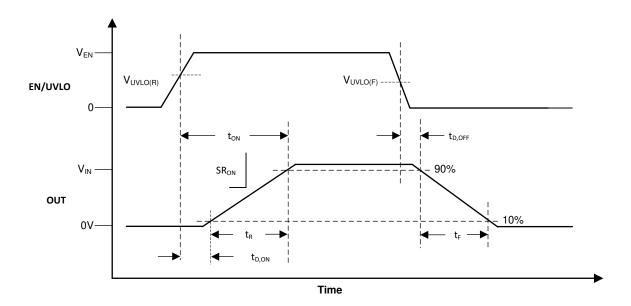

#### 7.7 Switching Characteristics

The output rising slew rate is internally controlled and constant across the entire operating voltage range to ensure the turn-on timing is not affected by the load conditions. The rising slew rate can be adjusted by adding capacitance from the dVdt pin to ground. As  $C_{dVdt}$  is increased, it will slow the rising slew rate (SR). See Slew Rate and Inrush Current Control (dVdt) section for more details. The fall time, however, is dependent on the RC time constant of the load capacitance ( $C_{OUT}$ ) and Load Resistance ( $R_L$ ). The Switching Characteristics are only valid for the power-up sequence where the supply is available in steady state condition and the load voltage is completely discharged before the device is enabled. Typical Values are taken at  $T_J = 25~^{\circ}\text{C}$  unless specifically noted otherwise.  $R_{OUT} = 100~\Omega$ ,  $C_{OUT} = 1~\mu\text{F}$ .

|                   | PARAMETER               | V <sub>IN</sub> | C <sub>dVdt</sub> = Open | C <sub>dVdt</sub> = 3300pF | UNIT |

|-------------------|-------------------------|-----------------|--------------------------|----------------------------|------|

|                   |                         | 2.7 V           | 28.9                     | 12.1                       |      |

| SR <sub>ON</sub>  | Output Rising slew rate | 5 V             | 42.7                     | 13.1                       | V/ms |

|                   |                         | 12 V            | 75.1                     | 13.6                       |      |

|                   |                         | 2.7 V           | 77.5                     | 216.5                      |      |

| t <sub>D,ON</sub> | Turn on delay           | 5 V             | 78.9                     | 247.3                      | μs   |

|                   |                         | 12 V            | 82.9                     | 314.9                      |      |

|                   |                         | 2.7 V           | 74.7                     | 182.4                      |      |

| t <sub>R</sub>    | Rise time               | 5 V             | 94.1                     | 311.0                      | μs   |

|                   |                         | 12 V            | 128.4                    | 707.8                      |      |

|                   |                         | 2.7 V           | 152.2                    | 398.9                      |      |

| t <sub>ON</sub>   | Turn on time            | 5 V             | 173                      | 558.4                      | μs   |

|                   |                         | 12 V            | 211.3                    | 1022.7                     |      |

|                   |                         | 2.7 V           | 12.2                     | 12.3                       |      |

| $t_{D,OFF}$       | Turn off delay          | 5 V             | 11.6                     | 11.9                       | μs   |

|                   |                         | 12 V            | 10.3                     | 10.4                       |      |

图 1. TPS2596xx Switching Times

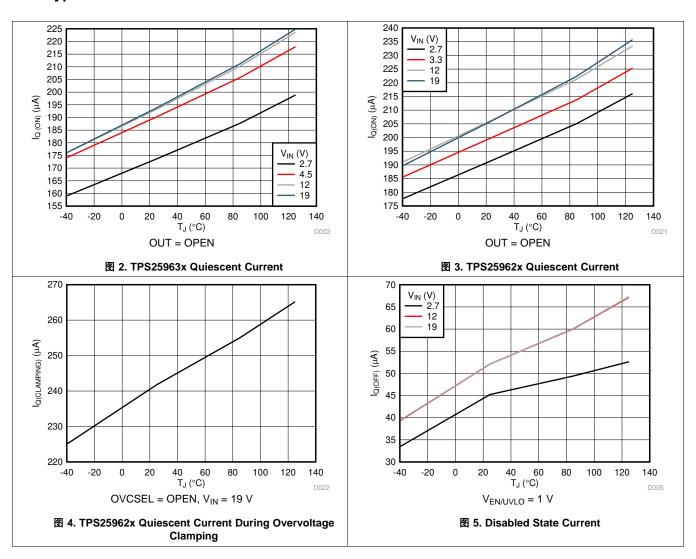

#### 7.8 Typical Characteristics

# TEXAS INSTRUMENTS

# TEXAS INSTRUMENTS

# TEXAS INSTRUMENTS

#### 8 Detailed Description

#### 8.1 Overview

The TPS2596xx is an integrated eFuse device that is used to manage load voltage and load current. The device provides various factory programmed settings and user manageable settings, which allow device configuration for handling different transient and steady state supply and load fault conditions, thereby protecting the input supply and the downstream circuits connected to the device. The device also uses an in-built thermal shutdown mechanism to protect itself during these fault events.

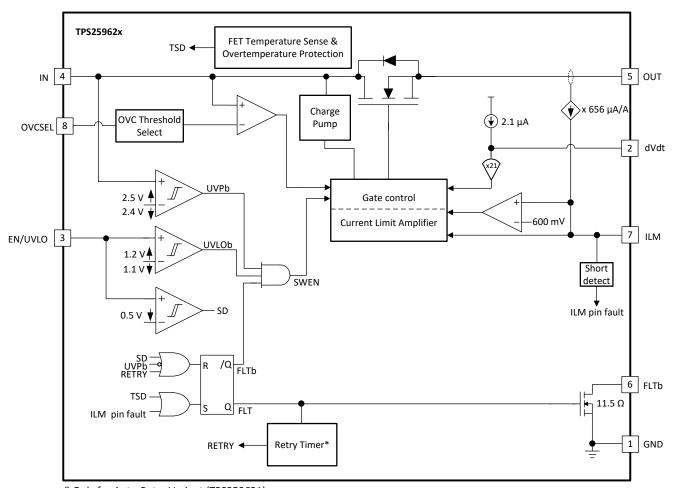

#### 8.2 Functional Block Diagram

\* Only for Auto-Retry Variant (TPS259621)

#### Functional Block Diagram (接下页)

\* Only for Auto-Retry Variant (TPS259631)

#### 8.3 Feature Description

#### 8.3.1 Undervoltage Protection (UVP) and Undervoltage Lockout (UVLO)

TPS2596xx constantly monitors the input supply to ensure that the load is powered up only when the voltage is at a sufficient level. During the start-up condition, the device waits for the input supply to rise above an internal fixed threshold  $V_{\text{UVP}(R)}$  before it proceeds to turn ON the FET. Similarly, during the ON condition, if the input supply falls below the UVP threshold  $V_{\text{UVP}(F)}$ , the FET is turned OFF. The UVP rising and falling thresholds are slightly different, thereby providing some hysteresis and ensuring stable operation around the threshold voltage.

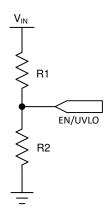

The TPS2596xx devices also provide an user adjustable UVLO mechanism to ensure that the load is powered up only when the voltage is at a sufficient level. This can be achieved by dividing the input supply and feeding it to the EN/UVLO pin. Whenever the voltage at the EN/UVLO pin falls below a threshold  $V_{UVLO(F)}$ , the device turns OFF the FET. The FET is turned ON again when the voltage rises above the threshold  $V_{UVLO(R)}$ . The rising and falling thresholds on this pin are slightly different, thereby providing some hysteresis and ensuring stable operation around the threshold voltage.

The user must choose the resistor divider values appropriately to map the desired input undervoltage level to the UVLO threshold of the part.

#### Feature Description (接下页)

图 44. Adjustable Undervoltage Lockout

$$VIN(UV) = VUVLO(F) \times \frac{(R_1 + R_2)}{R_2}$$

(1)

#### 8.3.2 Overvoltage Protection

The TPS2596xx devices provide 2 ways to handle an input overvoltage condition.

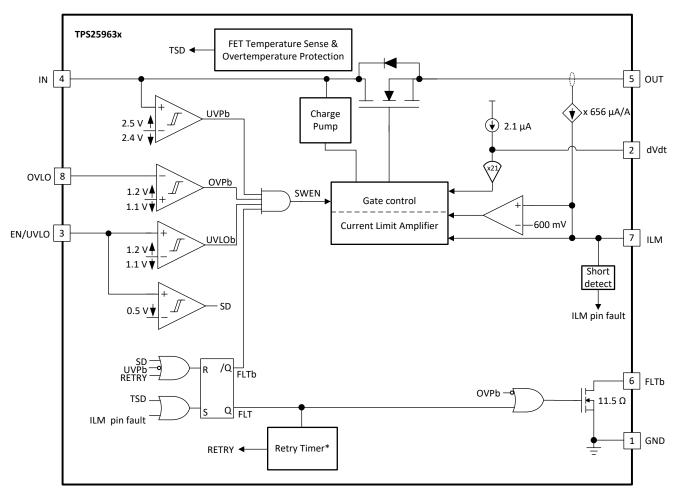

#### 8.3.2.1 Overvoltage Lockout

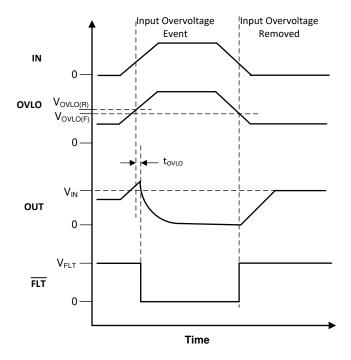

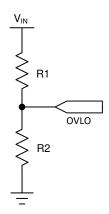

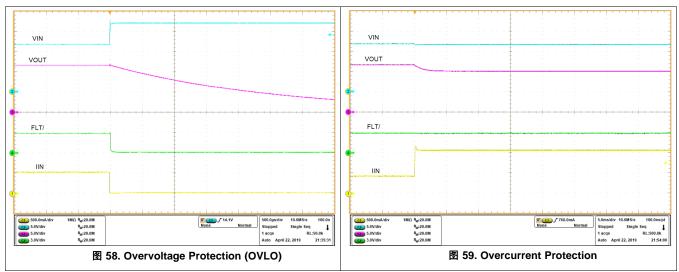

The TPS25963x variants provide an user adjustable OVLO mechanism to ensure that the supply to the load is cut off if the input supply voltage exceeds a certain level. This can be achieved by dividing the input supply and feeding it to the OVLO pin. Whenever the voltage at the OVLO pin rises above a threshold  $V_{\text{OVLO(R)}}$ , the device turns OFF the FET. When the voltage at the OVLO pin falls below the threshold  $V_{\text{OVLO(F)}}$ , the FET is turned ON again. The rising and falling thresholds on this pin are slightly different, thereby providing some hysteresis and ensuring stable operation around the threshold voltage.

图 45. TPS25963x Overvoltage Lockout Response

#### Feature Description (接下页)

The user should choose the resistor divider values appropriately to map the desired input overvoltage level to the OVLO threshold of the part.

图 46. TPS25963x Adjustable Overvoltage Lockout

$$V_{IN(OV)} = V_{OVLO(R)} \times \frac{(R_1 + R_2)}{R_2}$$

(2)

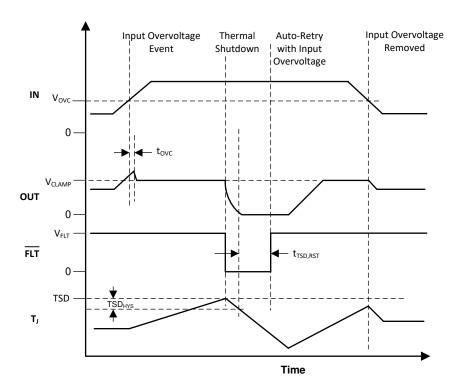

#### 8.3.2.2 Overvoltage Clamp

The TPS25962x variants provide a mechanism to clamp the output voltage to a user-selectable level quickly if the input voltage crosses a certain threshold. This ensures the load is not exposed to high voltages during any input overvoltage events and lowers the dependence on external protection devices (such as TVS/Zener diodes) in this condition. Once the input supply voltage rises above the OVC threshold voltage  $V_{OVC}$ , the device responds by clamping the voltage to  $V_{CLAMP}$  within a very short response time  $t_{OVC}$ . As long as an overvoltage condition is present on the input, the output voltage will be clamped to  $V_{CLAMP}$ . When the input drops below the output clamp threshold  $V_{OVC}$ , the clamp releases the output voltage as shown in  $\boxed{8}$  47.

#### Feature Description (接下页)

图 47. TPS25962x Overvoltage Clamp Response

The OVC threshold can be configured to one of 3 pre-defined levels by connecting the OVCSEL pin as shown in 表 1.

表 1. TPS25962x Overvoltage Clamp Threshold Selection

| OVCSEL Pin Connection                            | OVC Threshold (typ) |

|--------------------------------------------------|---------------------|

| Shorted to GND                                   | 3.8 V               |

| Connected to GND through 400 K $\Omega$ resistor | 5.7 V               |

| Open                                             | 13.7 V              |

During the overvoltage clamp condition, there could be significant heat dissipation in the internal FET depending on the  $V_{IN}$  -  $V_{OUT}$  voltage drop and the current ( $I_{OUT}$ ) through the FET leading to thermal shutdown if the condition persists for an extended period of time. In this case, the device would either stay latched-off or start an auto-retry cycle as explained in the *Overtemperature Protection (OTP)* section.

#### 8.3.3 Inrush Current, Overcurrent and Short Circuit Protection

The TPS2596xx devices incorporate three levels of protection against overcurrent:

- Adjustable slew rate for inrush current control (dVdt)

- Active current limiting with adjustable limit (I<sub>LIM</sub>) for overcurrent protection

- Fast short-circuit response to protect against hard short-circuits

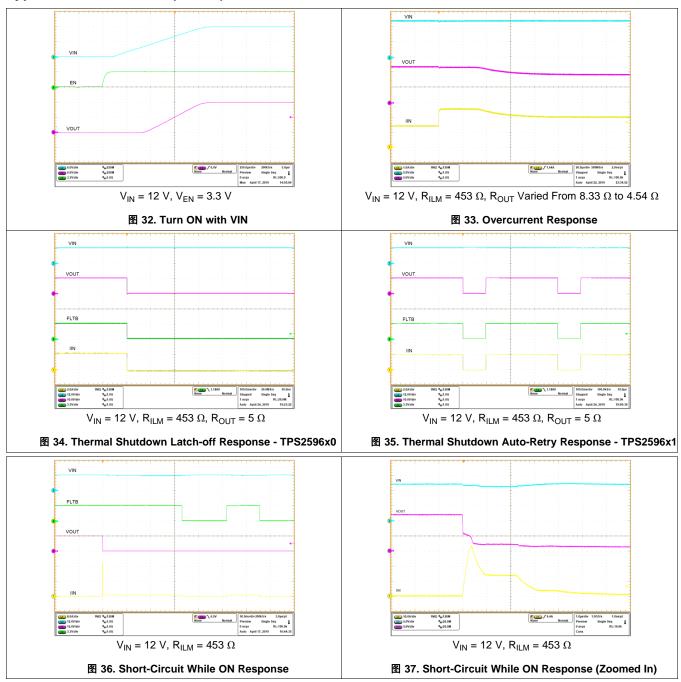

#### 8.3.3.1 Slew Rate and Inrush Current Control (dVdt)

The inrush current during turn on is directly proportional to the load capacitance and rising slew rate. 公式 3 can be used to find the slew rate  $SR_{ON}$  required to limit the inrush current  $I_{INRUSH}$  for a given load capacitance  $C_{OUT}$ .

$$SR(mV/\mu s) = \frac{IINRUSH(mA)}{CL(\mu F)}$$

(3)

For loads requiring a slower rising slew rate, a capacitor can be connected to the dVdt pin to adjust the rising slew rate and lower the inrush current during turn on. The required  $C_{dVdt}$  capacitance value to produce a given slew rate can be calculated using  $\Delta \vec{x}$  4.

$$C_{dVdt}(pF) = \frac{42000}{SR(mV/\mu s)}$$

(4)

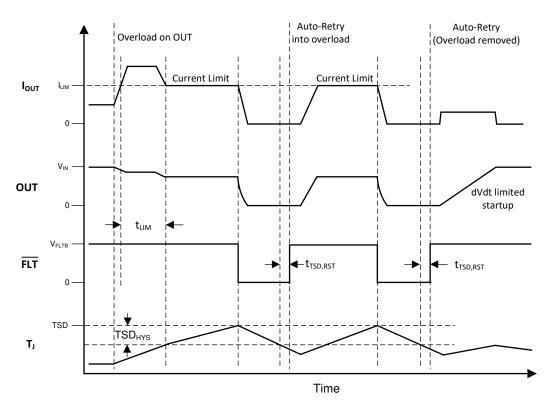

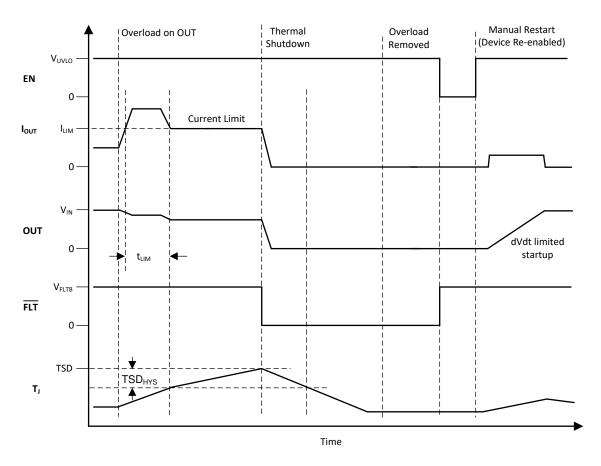

#### 8.3.3.2 Active Current Limiting

The load current is monitored during start-up and normal operation. When the load current exceeds the current limit  $I_{LIM}$  programmed by  $R_{ILM}$  resistor, the device regulates the current to the set limit  $I_{LIM}$  within  $t_{LIM}$ . The device exits current limiting when the load current falls below  $I_{LIM}$ . 公式 5 can be used to find the  $R_{ILM}$  value for a desired current limit.

$$\mathsf{RILM}(\Omega) = \frac{903}{\mathsf{ILIM}(\mathsf{A}) - 0.0112} \tag{5}$$

In the current limiting state, the output voltage drops resulting in increased power dissipation in the internal FET leading to thermal shutdown if the condition persists for an extended period of time. In this case, the device either stays latched-off or starts an auto-retry cycle as explained in the *Overtemperature Protection (OTP)* section.

图 48. TPS2596x1 Overcurrent Response (Auto-retry)

图 49. TPS2596x0 Overcurrent Response (Latch-off)

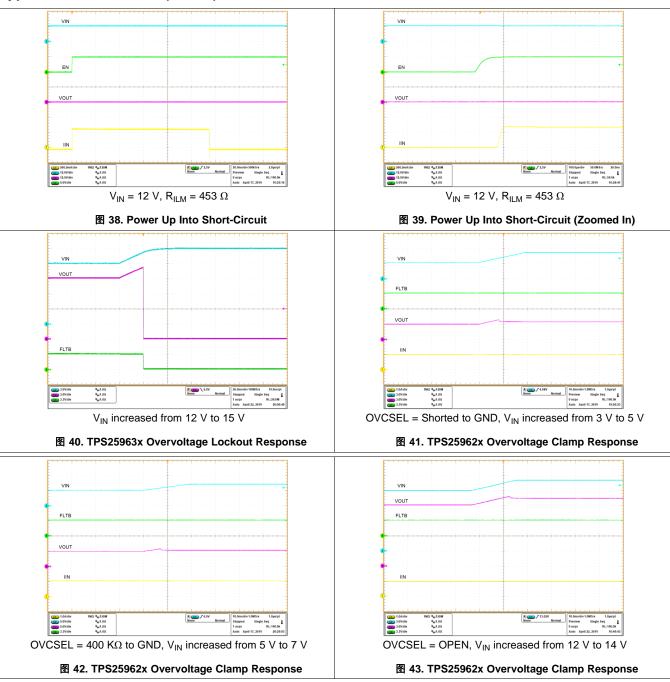

#### 8.3.3.3 Short-Circuit Protection

The current through the device increases very rapidly during a short-circuit event. If the current exceeds 1.5 x  $I_{LIM}$ , the device engages a fast current clamping circuit to regulate down the current faster than the nominal overcurrent response time ( $t_{LIM}$ ). The device does not completely turn off the power FET to ensure uninterrupted power in the event of transient overcurrents or supply transients. The device stops limiting the current once the load current falls below the programmed  $I_{LIM}$  threshold.

The output voltage drops in the current limiting state, resulting in increased power dissipation in the internal FET and might lead to thermal shutdown if the condition persists for an extended period of time. In this case, the device either stays latched-off or starts an auto retry cycle as explained in the *Overtemperature Protection (OTP)* section.

图 50. TPS2596xx Short Circuit Response

#### 8.3.4 Analog Load Current Monitor (IMON)

The device allows the system to monitor the output load current accurately by providing an analog current on the ILM pin which is proportional to the current ( $I_{OUT}$ ) through the FET. The user can sense the voltage ( $V_{ILM}$ ) across the  $R_{ILM}$  to get a measure of the output load current.

$$IOUT(A) = \frac{VILM(V)}{GIMON(\mu A / A)x RILM(\Omega)}$$

(6)

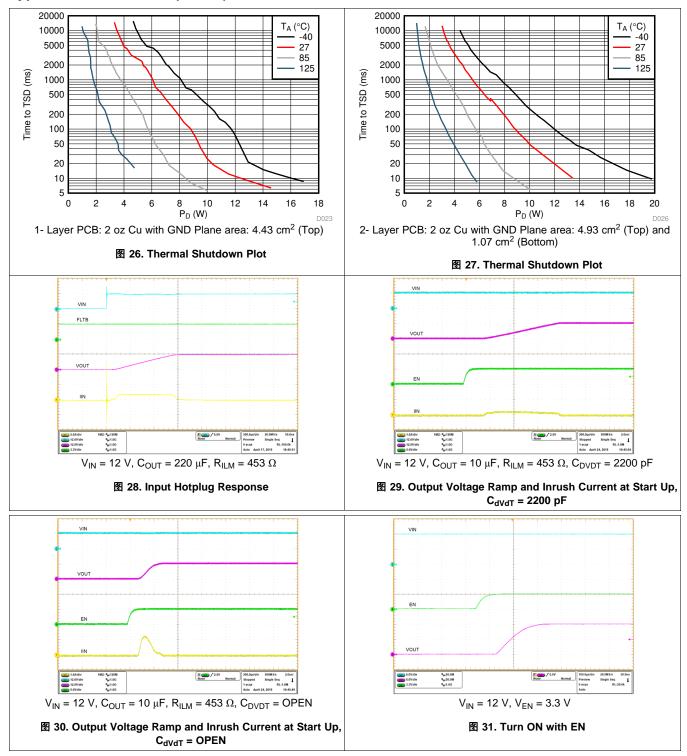

#### 8.3.5 Overtemperature Protection (OTP)

Thermal Shutdown will occur when the junction temperature (T<sub>J</sub>) exceeds the thermal shutdown threshold (TSD). When the TPS2596x0 variant detects thermal overload, it will be shut down and remain latched off until the device is power cycled or re-enabled by toggling the EN/UVLO pin. When the TPS2596x1 variant detects thermal overload, it will remain off until it has cooled down sufficiently. Once the TPS2596x1 junction has cooled down below TSD - TSD<sub>HYS</sub>, it will remain off for an additional delay of t<sub>TSD,RST</sub> after which it will automatically retry to turn on if it is still enabled.

表 2. TPS2596x Thermal Shutdown

| Device Enter TSD       |                      | Exit TSD                                                                                                            |

|------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| TPS2596x0 (Latch-Off)  | T <sub>J</sub> ≥ TSD | $T_J$ < TSD - TSD <sub>HYS</sub> and Power Cycle ( $V_{IN}$ < $V_{UVP(F)}$ ) / Enable Cycle ( $V_{EN}$ < $V_{SD}$ ) |

| TPS2596x1 (Auto-Retry) | T <sub>J</sub> ≥ TSD | $T_J < TSD - TSD_{HYS}$ and $t_{TSD-RST}$ timer expired                                                             |

#### 8.3.6 Fault Indication

表 3 summarizes the protection response to various fault conditions.

表 3. Fault Response

| Event / Fault        | Protection Response             | FLT Asserted | FLT Delay         |

|----------------------|---------------------------------|--------------|-------------------|

| Overtemperature      | Shutdown                        | Yes          |                   |

| Undervoltage         | Cut-off                         | No           |                   |

| 0                    | Clamp (OVC - TPS25962x only)    | No           |                   |

| Overvoltage          | Cut-off (OVLO - TPS25963x only) | Yes          | t <sub>OVLO</sub> |

| Overcurrent          | Current Limit                   | No           |                   |

| Short-Circuit        | Current Limit                   | No           |                   |

| ILM Pin Short to GND | Shut down                       | Yes          |                   |

| ILM Pin Open         | Shut down                       | No           |                   |

When the device turns off due to one of these fault conditions, the FLT pin is pulled low.

Power cycling the part or pulling the EN/UVLO pin voltage below  $V_{SD}$  clears the fault and the  $\overline{FLT}$  pin is deasserted. It also clears the  $t_{TSD,RST}$  timer (Auto-retry variants only). Pulling the EN/UVLO just below the UVLO threshold (V<sub>UVLO(F)</sub>) has no impact on the device in this condition. This is true for both Latch-off (TPS2596x0) and Auto-retry (TPS2596x1) variants.

For Auto-retry (TPS2596x1) variants, at the end of the t<sub>TSD,RST</sub> timer after a fault, the device restarts automatically and the FLT pin is de-asserted.

#### 8.4 Device Functional Modes

The features of the device depend on the operating mode.

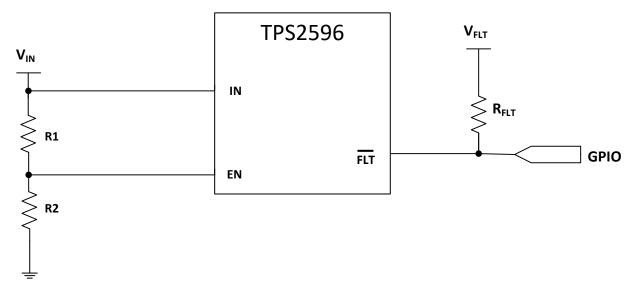

#### 8.4.1 Enable and Fault Pin Functional Mode 1: Single Device, Self-Controlled

In this mode of operation, the device is enabled by the VIN voltage without the need of an external processor to drive the ENABLE pin. The FLT pin is optionally monitored by an external host as shown in \begin{align\*} \begin{align\*} \text{S1}. \\ \text{S2}. \\ \text{S1}. \\ \text{S2}. \\ \text{S2

图 51. Single Device, Self-Controlled

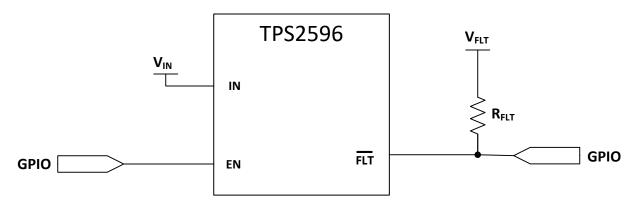

#### 8.4.2 Enable and Fault Pin Functional Mode 2: Single Device, Host-Controlled

In this mode of operation, the device is enabled by the VIN voltage without the need of an external processor to drive the ENABLE pin. The FLT pin is optionally monitored by an external host as shown in \begin{align\*} \begin{align\*} \text{S3}. \\ \end{align\*}

#### Device Functional Modes (接下页)

图 52. Single Device, Self-Controlled

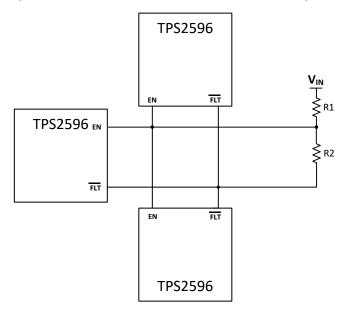

#### 8.4.3 Enable and Fault Pin Functional Mode 3: Multiple Devices, Self-Controlled

In this mode of operation, the devices are self-controlled (no host present). The EN and  $\overline{\text{FLT}}$  pins of multiple devices are shorted together as shown in 852. In this configuration, when any one of the TPS2596xx devices detects a fault, it automatically disables the other TPS2596xx devices in the system.

图 53. Multiple Devices, Self-Controlled

#### 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The TPS2596xx device is an integrated eFuse that is typically used for hot-swap and power rail protection applications. The device operates from 2.7 V to 19 V with adjustable current limit and undervoltage protection. The device aids in controlling the in-rush current and provides precise current limiting during overload conditions for systems such as energy meters, white goods, building automation and adapter input protection. The device also provides robust protection for multiple faults on the sub-system rail.

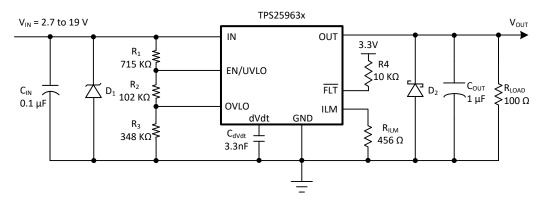

The following design procedure can be used to select the supporting component values based on the application requirement.

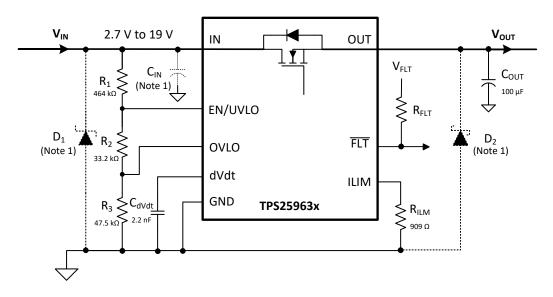

#### 9.2 Typical Application

#### 9.2.1 Precision Current Limiting and Protection for White Goods

(1) C<sub>IN</sub> is optional and 0.1 μF is recommended to suppress transients due to the inductance of PCB routing or from input wiring. If system needs to pass IEC 61000-4-4 EFT test, minimum C<sub>IN</sub> of 1 μF should be used to prevent eFuse from turning off during EFT bursts.

图 54. Typical Application Schematic: Simple eFuse for White Goods

#### 9.2.2 Design Requirements

表 4. Design Parameters

| DESIGN PARAMETER                                   | EXAMPLE VALUE |

|----------------------------------------------------|---------------|

| Input voltage , V <sub>IN</sub>                    | 12 V          |

| Undervoltage lockout set point, V <sub>UV</sub>    | 8 V           |

| Overvoltage protection set point , V <sub>OV</sub> | 13.7 V        |

| Overvoltage protection type                        | Lock-out      |

| Load at start-up, R <sub>L(SU)</sub>               | 24 Ω          |

#### Typical Application (接下页)

#### 表 4. Design Parameters (接下页)

| DESIGN PARAMETER                             | EXAMPLE VALUE |  |  |  |

|----------------------------------------------|---------------|--|--|--|

| Current limit, I <sub>LIM</sub>              | 1 A           |  |  |  |

| Load capacitance, C <sub>OUT</sub>           | 100 μF        |  |  |  |

| Maximum ambient temperatures, T <sub>A</sub> | 85°C          |  |  |  |

#### 9.2.3 Detailed Design Procedure

The designer must know the following:

- Normal input operation voltage

- Maximum output capacitance

- Maximum current limit

- · Load during start-up

- Maximum ambient temperature of operation

This design procedure seeks to control the junction temperature of device under both static and transient conditions by proper selection of output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria. A spreadsheet design tool *TPS2596 Design Calculator* is also available for simplified calculations.

#### 9.2.3.1 Programming the Current-Limit Threshold: R<sub>ILM</sub> Selection

The R<sub>ILM</sub> resistor at the ILM pin sets the over load current limit, this can be set using 公式 7.

$$R_{\text{ILM}}(\Omega) = \frac{903}{I_{\text{LIM}(A)} - 0.0112} = \frac{903}{1 - 0.0112} = 913.2 \ \Omega \tag{7}$$

Choose closest standard value resistor: 909  $\Omega$  with 1% tolerance.

#### 9.2.3.2 Undervoltage and Overvoltage Lockout Set Point

The undervoltage lockout (UVLO) and overvoltage lockout (OVLO) trip point is adjusted using the external voltage divider network of  $R_1$ ,  $R_2$  and  $R_3$ as connected between IN, EN/UVLO, OVLO and GND pins of the device. The values required for setting the undervoltage and overvoltage are calculated solving  $\Delta \pm 8$  and  $\Delta \pm 9$ .

$$V_{UVLO} = \frac{R_2 + R_3}{(R_1 + R_2 + R_3)} \times V_{IN(UV)}$$

(8)

$$V_{OVLO} = \frac{R_3}{\left(R_1 + R_2 + R_3\right)} \times V_{IN(OV)}$$

(9)

Where  $V_{UVLO(R)}$  is UVLO rising threshold (1.2 V). Because  $R_1$ ,  $R_2$  and  $R_3$  leak the current from input supply  $V_{IN}$ , these resistors must be selected based on the acceptable leakage current from input power supply  $V_{IN}$ .

The current drawn by  $R_1$ ,  $R_2$  and  $R_3$  from the power supply is  $I_{R_{123}} = V_{IN} / (R_1 + R_2 + R_3)$ .

However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current, I<sub>R123</sub> must be chosen to be 20 times greater than the leakage current expected.

From the device electrical specifications,  $V_{OVLO}=1.2~V$  and  $V_{UVLO}=1.2~V$ . For design requirements,  $V_{OV}=13.7~V$  and  $V_{UV}=8~V$ . To solve the equation, first choose the value of  $R_3=47~k\Omega$  and use  $\Delta \vec{\Xi}$  9 to solve for  $(R_1+R_2)=489.58~k\Omega$ . Use Equation 8 and value of  $(R_1+R_2)$  to solve for  $R_2=33.48~k\Omega$  and finally  $R_1=456.1~k\Omega$ . Using the closest standard 1% resistor values gives  $R_1=464~k\Omega$ ,  $R_2=33.2~k\Omega$ , and  $R_3=47.5~k\Omega$ .

#### 9.2.3.3 Setting Output Voltage Ramp Time ( $T_{dVdT}$ )

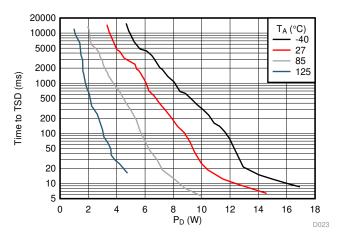

For a successful design, the junction temperature of device must be kept below the absolute maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The required ramp-up capacitor  $C_{dVdT}$  is calculated considering the two possible cases (see Case 1: Start-Up Without Load. Only Output Capacitance  $C_{OUT}$  Draws Current and Case 2: Start-Up With Load. Output Capacitance  $C_{OUT}$  and Load Draw Current).

#### 9.2.3.3.1 Case 1: Start-Up Without Load. Only Output Capacitance Cout Draws Current

During start-up, as the output capacitor charges, the voltage drop as well as the power dissipated across the internal FET decreases. The average power dissipated in the device during start-up is calculated using 公式 11.

For TPS2596xx device, the inrush current is determined as shown in 公式 10.

$$I_{\text{INRUSH}} = C_{\text{OUT}} \times \frac{V_{\text{IN}}}{T_{\text{dVdT}}}$$

(10)

Power dissipation during start-up is shown in 公式 11.

$$P_{D(INRUSH)} = 0.5 \times V_{IN} \times I_{INRUSH}$$

(11)

公式 11 assumes that load does not draw any current until the output voltage has reached its final value.

#### 9.2.3.3.2 Case 2: Start-Up With Load. Output Capacitance Cour and Load Draw Current

When the load draws current during the turnon sequence, there is additional power dissipated. Considering a resistive load during start-up  $R_{L(SU)}$ , load current ramps up proportionally with increase in output voltage during  $T_{dVdT}$  time. Equations 12 to 15 show the average power dissipation in the internal FET during charging time due to resistive load.

$$\mathsf{P}_{\mathsf{D}(\mathsf{LOAD})} = \left(\frac{1}{6}\right) \times \frac{\mathsf{V}_{\mathsf{IN}}^2}{\mathsf{R}_{\mathsf{L}(\mathsf{SU})}} \tag{12}$$

Total power dissipated in the device during start-up is 公式 13.

$$P_{D(STARTUP)} = P_{D(INRUSH)} + P_{D(LOAD)}$$

(13)

Total current during start-up is given by 公式 14.

$$I_{STARTUP} = I_{INRUSH} + I_{L}(t)$$

(14)

If  $I_{STARTUP} > I_{LIMIT}$ , the device limits the current to  $I_{LIMIT}$  and the current-limited charging time is determined by  $\stackrel{\smile}{\Delta}$  15.

$$T_{\text{dvdT}(\text{Current-Limited})} = C_{\text{OUT}} \times R_{\text{L(SU)}} \times \left[ \frac{I_{\text{LIMIT}}}{I_{\text{INRUSH}}} - 1 + LN \left( \frac{I_{\text{INRUSH}}}{I_{\text{LIMIT}} - \frac{V_{\text{IN}}}{R_{\text{L(SU)}}}} \right) \right]$$

(15)

The power dissipation, with and without load, for selected start-up time must not exceed the shutdown limits as shown in ₹ 55.

图 55. Thermal Shutdown Limit Plot

For the design example under discussion, select ramp-up capacitor  $C_{dVdt} = 22000$  pF. The default slew rate for  $C_{dVdt} = 22000$  pF is 1.9 mV/ $\mu$ s. With slew rate of 1.9 mV/ $\mu$ s, the ramp-up time  $T_{dVdt}$  for 12 V input is 6.3 ms.

The inrush current drawn by the load capacitance  $C_{OUT}$  during ramp-up using  $\Delta \vec{x}$  16.

$$I_{INRUSH} = \frac{100 \ \mu F \times 1.9 \ mV}{\mu s} = 190 \ mA \tag{16}$$

The inrush power dissipation is calculated using 公式 17.

$$P_{D(INRUSH)} = 0.5 \times 12 \times 190 \text{ m} = 1.14 \text{ W}$$

(17)

For 1.14 W of power loss, the thermal shutdown time of the device must not be less than the ramp-up time  $T_{dVdt}$  to avoid the false trip at the maximum operating temperature. 855 shows the thermal shutdown limit at  $T_A = 85$  °C, for 1.14 W of power, the shutdown time is infinite. Therefore, it is safe to use 6.3 ms as the start-up time without any load on the output.

The additional power dissipation when a  $10-\Omega$  load is present during start-up is calculated using 公式 18.

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{12 \times 12}{24} = 1W$$

(18)

The total device power dissipation during start-up is given in 公式 19.

$$P_{D(STARTUP)} = 1 + 1.14 = 2.24 \text{ W}$$

(19)

$\boxtimes$  55 shows  $T_A = 85$  °C and the thermal shutdown time for 2.24 W is approximately 2000 ms, which increases the margins further for shutdown time and ensures successful operation during start up and steady state conditions.

When  $C_{\text{OUT}}$  is large, there is a need to decrease the power dissipation during start-up. This can be done by increasing the value of the  $C_{\text{dVdt}}$  capacitor.

#### 9.2.4 Support Component Selection: $R_{FLT}$ and $C_{IN}$

Referring to application schematics,  $R_{FLT}$  is required only if  $\overline{FLT}$  is used; The resistor serves as pull-up for the open-drain output driver. The current sunk by this pin should not exceed 10 mA.  $C_{IN}$  is a bypass capacitor to help control transient voltages, unit emissions, and local supply noise. Where acceptable, a value in the range from 0.001  $\mu F$  to 0.1  $\mu F$  is recommended for  $C_{IN}$ .

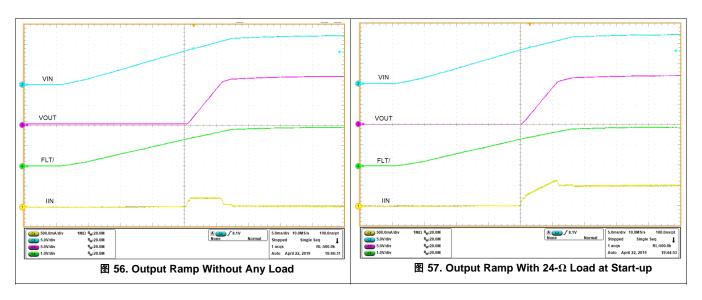

#### 9.2.5 Application Curves

#### 9.3 System Examples

The TPS2596xx provides a simple solution for current limiting, inrush current control and supervision of power rails for wide range of applications operating at 2.7 V to 19 V and delivering up to 2 A.

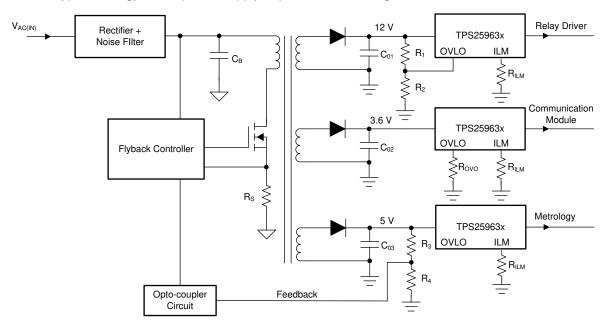

#### 9.3.1 Current Limiting and Overvoltage Protection and for Energy Meter Power Rails

Energy meters generally use a single AC/DC power supply (for example: flyback converter) with multiple DC outputs for powering blocks like Metrology (analog front-end, microcontroller, memory), Real Time Clock (RTC), Relay (for remote load connect/disconnect) and Communications module. Metrology is the most critical subsystem and is required to operate uninterrupted under all conditions, even if a fault occurs in any of the supplementary blocks. One solution would be to oversize the power supply design so that it can handle the excess current demands during a fault condition, which increases the cost of the meter. A more elegant and cost-optimized solution would be to add an eFuse like TPS2596xx on the supplementary power rails, which provides accurate current limiting and fast short-circuit protection, thereby ensuring reliable operation of the metrology block without increasing the size or cost of the power supply. Apart from that, the TPS2596xx provides additional benefits such as:

Overvoltage Protection (Lock-out and Clamp) to shield down-stream low voltage circuits from harmful overvoltages arising from poor cross-regulation between windings or AC input voltage surges.

#### System Examples (接下页)

Disconnect supply to rarely used loads to minimize power consumption

图 60 shows a typical energy meter power supply implementation using TPS2596xx.

图 60. Energy Meter Power Rail Protection Example

TIDA-010037 demonstrates energy meter design using eFuse for protecting auxiliary rails.

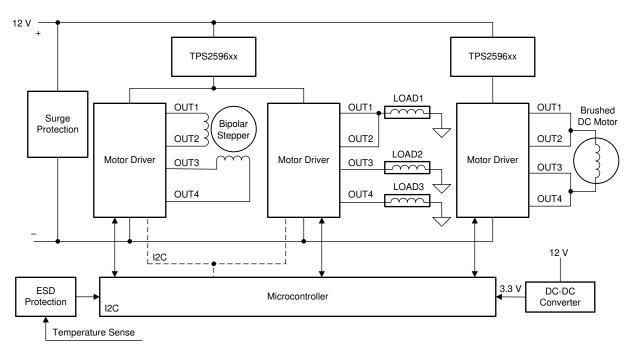

#### 9.3.2 Precision Current Limiting and Protection in Appliances

Household and similar electrical appliances are subjected to various tests (for example: needle flame, glow wire) as part of the certification for electrical and fire safety compliance as per the regulations. Special precautions need to be taken in the design to pass these tests, which include the use of higher grade flame retardant plastic material for the housing enclosures. There are certain provisions in the standard which can be leveraged to make the certification easier, faster and also reduce the cost of plastic materials. For example, any node which has less than 15 W of power available to it is classified as a LPC (Low Power Circuit as per the definition in IEC 60335-1) and deemed to be safe. All circuits or sub-systems further downstream from a LPC node are exempt from the aforementioned tests.

eFuses like TPS2596xx are a simple and cost effective way to limit the power delivered to the downstream load. The key parameter to be considered is the current imit tolerance and accuracy, which determines how high one can set the nominal current limit without exceeding the 15-W power limit on the upper end. On the lower end, it determines the maximum power the load can draw in normal conditions without hitting the current limit. TPS2596xx provides a current limit accuracy of ±5 % (at room temperature), which allows the load to use nearly 90% out of the 15-W limit under normal operating conditions.

In contrast, an alternative current limiting solution with wider current limit tolerance, say ±25 % would leave only 50 % out of 15 W for the load circuit to operate under normal conditions. This places severe constraints on the load circuit design and/or capabilities.

■ 61 shows a sub-system example of a refrigerator and freezer system where TPS2596xx is used for precision current limiting and protection of 15-W rails to ease the qualification as low-power circuit as per IEC 60335-1.

#### System Examples (接下页)

图 61. Appliances 15-W LPC Implementation Example

TIDA-010004 demonstrates a multi-load drive using single driver chip with eFuse for protection and 15-W LPC implementation.

Refer to this *Designing Low-Power Circuits* (LPCs) using TPS2596 for Household and similar Appliances application note for a detailed insight into implementing power limited circuits using eFuses.

#### 10 Power Supply Recommendations

The TPS2596xx devices are designed for a supply voltage range of 2.7 V  $\leq$  VIN  $\leq$  19 V. An input ceramic bypass capacitor higher than 0.1  $\mu$ F is recommended if the input supply is located more than a few inches from the device. The power supply must be rated higher than the set current limit to avoid voltage droops during overcurrent and short-circuit conditions.

#### 10.1 Transient Protection

In the case of a short circuit and overload current limit when the device interrupts current flow, the input inductance generates a positive voltage spike on the input, and the output inductance generates a negative voltage spike on the output. The peak amplitude of voltage spikes (transients) is dependent on the value of inductance in series to the input or output of the device. Such transients can exceed the absolute maximum ratings of the device if steps are not taken to address the issue. Typical methods for addressing transients include:

- · Minimize lead length and inductance into and out of the device.

- Use a large PCB GND plane.

- Use a Schottky diode across the output to absorb negative spikes.

- Use a low-value ceramic capacitor  $C_{\text{IN}}$  = 0.001  $\mu\text{F}$  to 0.1  $\mu\text{F}$  to absorb the energy and dampen the transients. The approximate value of input capacitance can be estimated with  $\Delta$  $\pm$ 20:

$$VSPIKE(Absolute) = VIN + ILOAD \times \sqrt{\frac{LIN}{CIN}}$$

(20)

#### where

- V<sub>IN</sub> is the nominal supply voltage

- I<sub>LOAD</sub> is the load current

- · LIN equals the effective inductance seen looking into the source

- C<sub>IN</sub> is the capacitance present at the input

NOTE: Systems which need to pass IEC 61000-4-4 tests for immunity to Electrical Fast Transients (EFT) should use a minimum  $C_{IN}$  of 1  $\mu$ F to ensure the TPS2596xx does not turn OFF during the EFT burst.

Some applications may require the addition of a Transient Voltage Suppressor (TVS) to prevent transients from exceeding the absolute maximum ratings of the device. The circuit implementation with optional protection components (a ceramic capacitor, TVS and Schottky diode) is shown in 862.

图 62. Circuit Implementation with Optional Protection Components

#### 10.2 Output Short-Circuit Measurements

It is difficult to obtain repeatable and similar short-circuit testing results. The following contribute to variation in results:

- · Source bypassing

- Input leads

- Circuit layout

- · Component selection

- · Output shorting method

- · Relative location of the short

- Instrumentation

The actual short exhibits a certain degree of randomness because it microscopically bounces and arcs. Ensure that configuration and methods are used to obtain realistic results. Do not expect to see waveforms exactly like those in this data sheet because every setup is different.

#### 11 Layout

#### 11.1 Layout Guidelines

- For all applications, a ceramic decoupling capacitor of 0.01 μF or greater is recommended between the IN terminal and GND terminal. For hot-plug applications, where input power-path inductance is negligible, this capacitor can be eliminated or minimized.

- The optimal placement of the decoupling capacitor is closest to the IN and GND terminals of the device. Care must be taken to minimize the loop area formed by the bypass-capacitor connection, the IN terminal, and the GND terminal of the IC. See <a> 63</a> for a PCB layout example.

- High current-carrying power-path connections must be as short as possible and must be sized to carry at least twice the full-load current.

- The GND terminal must be tied to the PCB ground plane at the terminal of the IC. The PCB ground must be a

copper plane or island on the board.

- · Locate the following support components close to their connection pins:

- $-R_{ILM}$

- C<sub>dVdT</sub>

- Resistor network for the EN/UVLO pin

- Resistor network for the OVLO pin for TPS25693x variants

- Pull-down resistor on the OVCSEL pin for TPS25692x variants

Connect the other end of the component to the GND pin of the device with shortest trace length. The trace routing from the  $R_{ILM}$ ,  $C_{dVdT}$  and  $R_{OVCSEL}$  (for TPS25962x variants) components to the device pins must be as short as possible to reduce parasitic effects on the current limit, soft-start timing and overvoltage clamp response. These traces must not have any coupling to switching signals on the board.

- Protection devices such as TVS, snubbers, capacitors, or diodes must be placed physically close to the

device they are intended to protect. These protection devices must be routed with short traces to reduce

inductance. For example, a protection Schottky diode is recommended to address negative transients due to

switching of inductive loads, and it must be physically close to the OUT pins.

- Obtaining acceptable performance with alternate layout schemes is possible. The Layout Example shown in 8 63 has been shown to produce good results and is intended as a guideline.

## 11.2 Layout Example

${}^{*}$  Optional: Needed only to suppress the transients caused by inductive load switching

图 63. TPS2596xx Layout Example

#### 12 器件和文档支持

#### 12.1 文档支持

#### 12.1.1 相关文档

请参阅如下相关文档:

- 《电子保险丝的基本知识》

- 《TPS2596EVM: TPS2596xx 评估模块》

- 《TPS2596 设计计算器》

- 《使用 TPS2596 为家用或类似用途电器设计低功耗电路 (LPC)》

- 《TIDA-010037 高精度分相 CT 电量计》

- 《TIDA-010004 基于单个驱动器且受全面保护的 12V 步进、刷式直流和执行器驱动器》

#### 12.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com. 上的器件产品文件夹。单击右上角的通知我进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 12.3 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.5 静电放电警告

能会

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

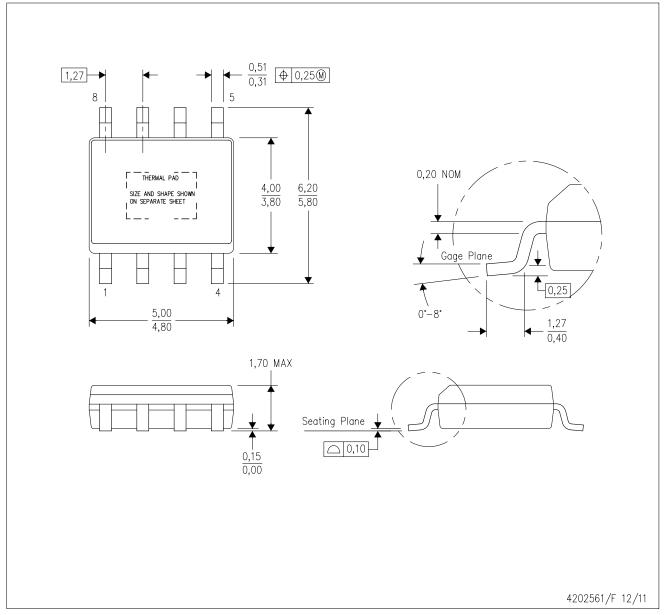

#### 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com

10-Nov-2025

#### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins           | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|--------------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TPS259620DDAR         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259620           |

| TPS259620DDAR.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259620           |

| TPS259620DDAT         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259620           |

| TPS259620DDAT.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259620           |

| TPS259621DDAR         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259621           |

| TPS259621DDAR.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259621           |

| TPS259621DDAT         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259621           |

| TPS259621DDAT.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259621           |

| TPS259630DDAR         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259630           |

| TPS259630DDAR.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259630           |

| TPS259630DDAT         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259630           |

| TPS259630DDAT.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259630           |

| TPS259631DDAR         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259631           |

| TPS259631DDAR.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259631           |

| TPS259631DDAT         | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259631           |

| TPS259631DDAT.A       | Active     | Production    | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 259631           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

#### PACKAGE OPTION ADDENDUM

www.ti.com 10-Nov-2025

- (2) Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 17-Jul-2020

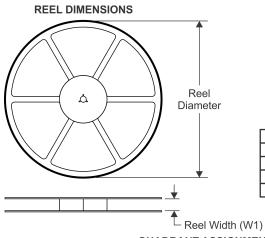

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS + K0 - P1 - B0 W Cavity - A0 -

| _ |    |                                                           |

|---|----|-----------------------------------------------------------|

|   |    | Dimension designed to accommodate the component width     |

|   | B0 | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

| ı | P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device        | Package<br>Type    | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|--------------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS259620DDAR | SO<br>Power<br>PAD | DDA                | 8    | 2500 | 330.0                    | 12.8                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS259620DDAT | SO<br>Power<br>PAD | DDA                | 8    | 250  | 330.0                    | 12.8                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS259621DDAR | SO<br>Power<br>PAD | DDA                | 8    | 2500 | 330.0                    | 12.8                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS259621DDAT | SO<br>Power<br>PAD | DDA                | 8    | 250  | 330.0                    | 12.8                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS259630DDAR | SO<br>Power<br>PAD | DDA                | 8    | 2500 | 330.0                    | 12.8                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |