TPS25940-Q1

ZHCSF29E - MAY 2016 - REVISED JANUARY 2021

# 具有集成式电池短路保护功能的 TPS25940xx-Q1 2.7V 至 18V 电子保险丝

# 1 特性

- 适用于汽车电子应用

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1: -40°C 至 +125°C 环境工作 温度范围

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C5

- 2.7V至 18V 工作电压, 20V(最大值)

- 总 R<sub>ON</sub>: 42mΩ(典型值)

- 可调节电流限值: 0.6A 至 5.3A (±8%)

- IMON 电流指示器输出

- 针对 TPS25940-Q1/TPS25940L-Q1 的 ±8% 精

- 可调节欠压阈值和过压阈值 (±2%)

- 反向电流阻断

- 1μs 反向电压关断

- 可编程 dV<sub>o</sub>/dt 控制

- 电源正常和故障输出

- 电池短路保护

- 接地短路保护

- TPS25940-Q1/TPS259401A-Q1:自动重试

- TPS25940L-Q1:闭锁

#### 2 应用

- 汽车信息娱乐系统

- 高级驾驶员辅助系统 (ADAS) 摄像头和雷达传感器

- USB 集线器

- 电源多路复用

- 保持电源管理

## 3 说明

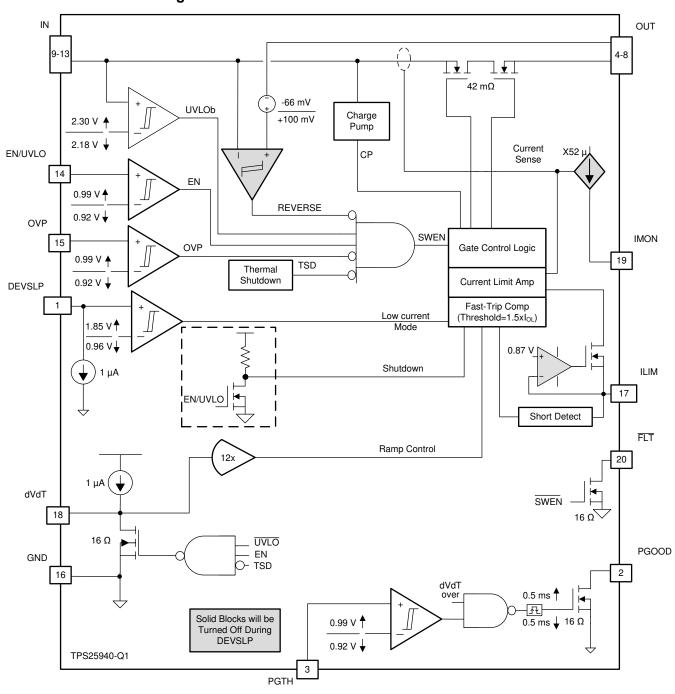

TPS25940xx-Q1 电子保险丝电源开关是功能丰富的紧 凑型电源管理器件,具有一整套保护功能。宽工作范围 可实现对很多常用直流总线电压的控制。该器件集成的 背靠背场效应晶体管 (FET) 可提供双向电流控制,很 好地适用于防止系统中的负载侧储能流回故障电源总 线。

负载、电源和器件保护由很多可编程特性提供,其中包 括过流,dVo/dt 斜率和过压、欠压阈值。为了实现系统 状态监视和下游负载控制,此器件提供 PGOOD、FLT 和精密电流监视输出。精确的可编程欠压和过压阈值及 模式简化了电源管理设计。

TPS25940xx-Q1 可监视 V<sub>(IN)</sub> 和 V<sub>(OUT)</sub>,以便在 V<sub>(IN)</sub> < (V<sub>(OUT)</sub> - 66mV) 时提供真正的反向电流阻断。该功 能可在输出端发生电池短路故障期间为电源总线提供过 压保护支持。

#### 器件信息(1)

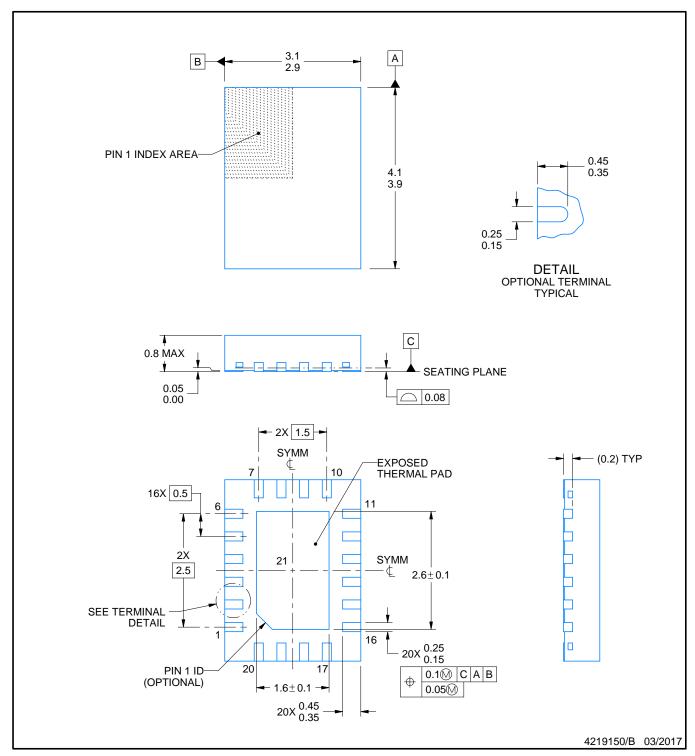

| 器件型号          | 封装                                      | 封装尺寸(标称值)       |

|---------------|-----------------------------------------|-----------------|

| TPS25940-Q1   |                                         |                 |

| TPS25940L-Q1  | 超薄四方扁平无引线<br> (WQFN) (20)               | 3.00mm x 4.00mm |

| TPS259401A-Q1 | (************************************** |                 |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

输出端电池短路检测与保护

# **Table of Contents**

| 1 特性                                 | 1 | 9.4 Device Functional Modes             | <mark>2</mark> 3 |

|--------------------------------------|---|-----------------------------------------|------------------|

| 2 应用                                 |   | 10 Application and Implementation       |                  |

| - <i>二</i> /,7.<br>3 说明              |   | 10.1 Application Information            |                  |

| 4 Revision History                   |   | 10.2 Typical Application                |                  |

| 5 Device Comparison Table            |   | 11 Power Supply Recommendations         | 38               |

| 6 Pin Configuration and Functions    |   | 11.1 Transient Protection               | 38               |

| 7 Specifications                     |   | 11.2 Output Short-Circuit Measurements  | 39               |

| 7.1 Absolute Maximum Ratings         |   | 12 Layout                               | 40               |

| 7.2 ESD Ratings                      |   | 12.1 Layout Guidelines                  | 40               |

| 7.3 Recommended Operating Conditions |   | 12.2 Layout Example                     |                  |

| 7.4 Thermal Information              |   | 13 Device and Documentation Support     |                  |

| 7.5 Electrical Characteristics       |   | 13.1 Documentation Support              | 42               |

| 7.6 Timing Requirements              |   | 13.2 支持资源                               | 42               |

| 7.7 Typical Characteristics          |   | 13.3 Trademarks                         |                  |

| 8 Parametric Measurement Information |   | 13.4 静电放电警告                             | 42               |

| 9 Detailed Description               |   | 13.5 术语表                                |                  |

| 9.1 Overview                         |   | 14 Mechanical, Packaging, and Orderable |                  |

| 9.2 Functional Block Diagram         |   | Information                             | 42               |

| 9.3 Feature Description              |   |                                         |                  |

|                                      |   |                                         |                  |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Changes from Revision D (September 2018) to Revision E (January 2021) | Page |

|-----------------------------------------------------------------------|------|

| • 更新了整个文档的表、图和交叉参考的编号格式                                               | 1    |

| • 向数据表添加了 TPS259401A-Q1 型号                                            | 1    |

| Added Device Comparison table                                         | 3    |

| Changes from Revision C (July 2018) to Revision D (September 2018)    | Page |

| Changed internal ramp rate of 12 V/ms for output to 30 V/ms           | 19   |

| Changes from Revision B (November 2017) to Revision C (July 2018)     | Page |

| • 从"量产数据"更改为"混合量产"                                                    | 1    |

| • 添加了闭锁型号 (TPS25940L-Q1)                                              | 1    |

| Changes from Revision A (June 2016) to Revision B (November 2017)     | Page |

| • 向 <i>应用信息</i> 部分添加了 9.2.4.3 小节 "使用 TPS25940-Q1 进行过载检测"              | 1    |

| Changes from Revision * (May 2016) to Revision A (June 2016)          | Page |

| • 将器件状态从产品预发布更改为量产数据                                                  | 1    |

# **5 Device Comparison Table**

| Part Number   | Fault Response | R <sub>DSON</sub> (max) | Minimum Current<br>Limit | IMON Accuracy (max) |

|---------------|----------------|-------------------------|--------------------------|---------------------|

| TPS25940-Q1   | Auto-Retry     | <b>64 m</b> Ω           | 0.5 A                    | 8 %                 |

| TPS25940L-Q1  | Latch-off      | 64 m Ω                  | 0.5 A                    | 8 %                 |

| TPS259401A-Q1 | Auto-Retry     | 85 m Ω                  | 1 A                      | Not specified       |

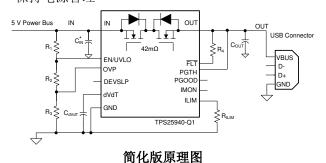

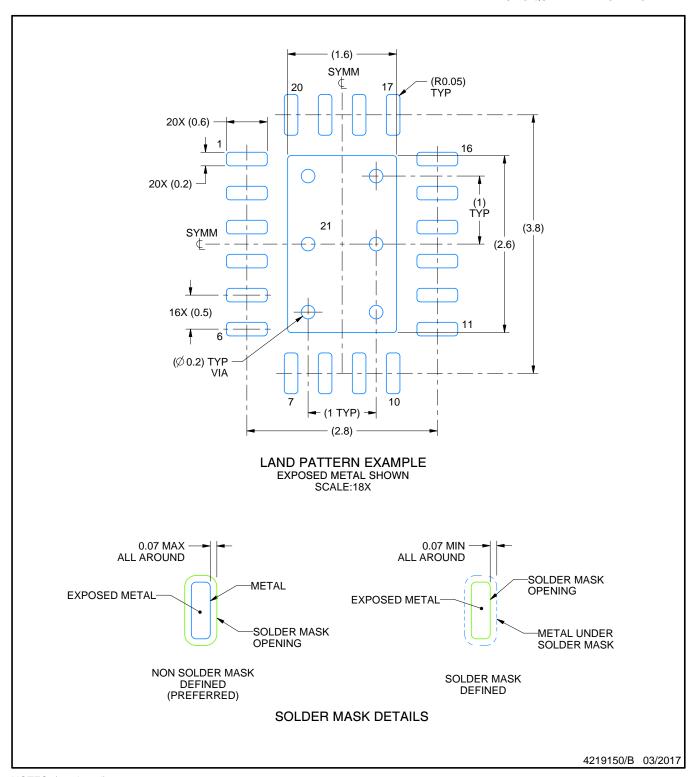

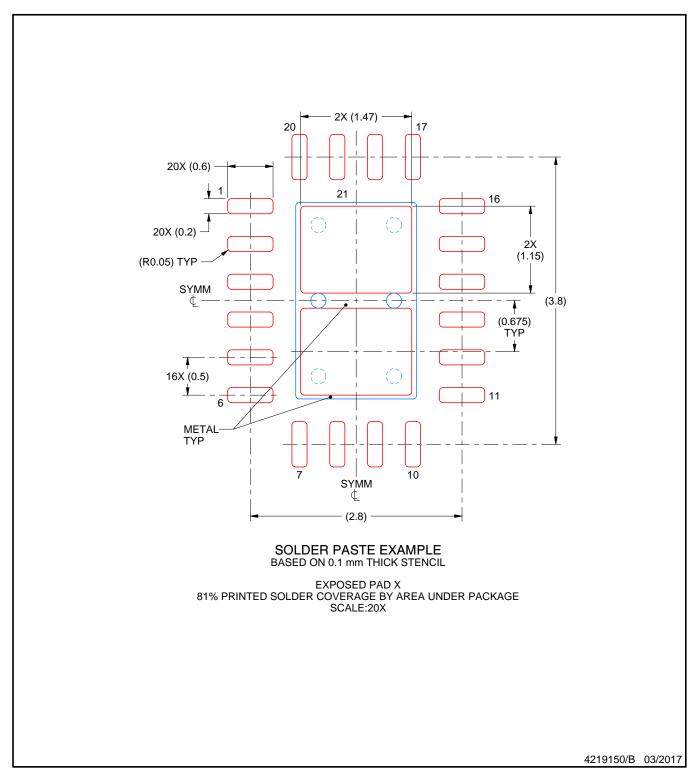

# **6 Pin Configuration and Functions**

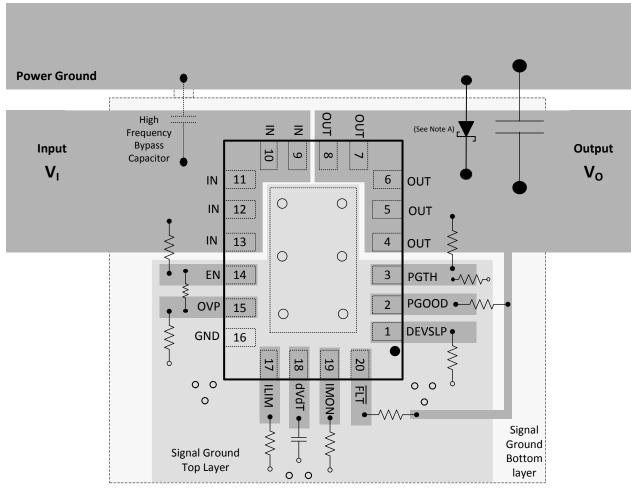

图 6-1. RVC Package 20-Pin WQFN Top View

表 6-1. Pin Functions

|     | PIN     | TYPE | DESCRIPTION                                                                                                                                                                                                    |

|-----|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME    | ITPE | DESCRIPTION                                                                                                                                                                                                    |

| 1   | DEVSLP  | ı    | Active high. DevSleep mode control. A high at this pin activates the DevSleep mode (low power mode). If unused, leave floating or connect it to GND.                                                           |

| 2   | PGOOD   | 0    | Active high. A high indicates PGTH has crossed the threshold value. It is an open drain output. If unused, leave floating.                                                                                     |

| 3   | PGTH    | I    | Positive input of PGOOD comparator. If unused connect to OUT or GND.                                                                                                                                           |

| 4   |         |      |                                                                                                                                                                                                                |

| 5   |         |      |                                                                                                                                                                                                                |

| 6   | OUT     | 0    | Power output of the device.                                                                                                                                                                                    |

| 7   |         |      |                                                                                                                                                                                                                |

| 8   |         |      |                                                                                                                                                                                                                |

| 9   |         |      |                                                                                                                                                                                                                |

| 10  |         |      |                                                                                                                                                                                                                |

| 11  | IN      | 1    | Power input and supply voltage of the device.                                                                                                                                                                  |

| 12  |         |      |                                                                                                                                                                                                                |

| 13  |         |      |                                                                                                                                                                                                                |

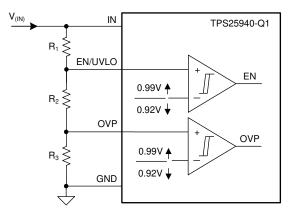

| 14  | EN/UVLO | 1    | Input for setting programmable undervoltage lockout threshold. An undervoltage event opens internal FET and assert FLT to indicate power-failure.                                                              |

| 15  | OVP     | 1    | Input for setting programmable overvoltage protection threshold. An overvoltage event opens the internal FET and assert FLT to indicate overvoltage.                                                           |

| 16  | GND     | _    | Ground. The GND terminal must be connected to the exposed PowerPAD. This PowerPAD must be connected to a PCB ground plane using multiple vias for good thermal performance.                                    |

| 17  | ILIM    | I/O  | A resistor from this pin to GND sets the overload and short-circuit current limit.                                                                                                                             |

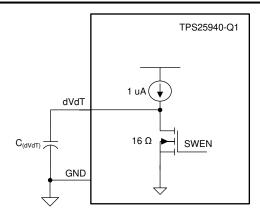

| 18  | dVdT    | I/O  | A capacitor from this pin to GND sets the ramp rate of output voltage.                                                                                                                                         |

| 19  | IMON    | 0    | This pin sources a scaled down ratio of current through the internal FET. A resistor from this pin to GND converts current to proportional voltage, used as analog current monitor. If unused, leave floating. |

| 20  | FLT     | 0    | Fault event indicator, goes low to indicate fault condition because of undervoltage, overvoltage, reverse voltage and thermal shutdown event. It is an open drain output. If unused, leave floating.           |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                              |                                                 | MIN                            | MAX              | UNIT |

|--------------------------------------------------------------|-------------------------------------------------|--------------------------------|------------------|------|

|                                                              | IN, OUT, PGTH, PGOOD, EN/UVLO, OVP, DEVSLP, FLT | - 0.3                          | 20               |      |

| Input valtage                                                | IN, OUT (10 ms transient)                       |                                | 22               | V    |

| Input voltage                                                | dVdT, ILIM                                      | - 0.3                          | 3.6              | V    |

|                                                              | IMON                                            | - 0.3                          | 7                |      |

| Sink current                                                 | PGOOD, FLT, dVdT                                |                                | 10               | mA   |

| Maximum continuous switch current, $T_A = 85^{\circ}C^{(2)}$ | I <sub>MAX</sub>                                |                                | 4.78             | Α    |

| Source current                                               | dVdT, ILIM, IMON                                | Ir                             | nternally Limite | d    |

| Continuous power dissipation                                 |                                                 | See the Thermal Information ta |                  |      |

| Maximum junction temperature                                 | T <sub>J</sub>                                  | - 40                           | 150              | °C   |

| Storage temperature                                          | T <sub>stg</sub>                                | - 65                           | 150              | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|        |                                            |                                                         | VALUE | UNIT |

|--------|--------------------------------------------|---------------------------------------------------------|-------|------|

| V      | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±3000 | V    |

| V(ESD) |                                            | Charged-device model (CDM), per AEC Q100-011            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                             |                                | MIN  | NOM | MAX | UNIT |

|---------------------------------------------|--------------------------------|------|-----|-----|------|

| IN                                          |                                | 2.7  |     | 18  |      |

| EN/UVLO, OVP, DEVSLP, OUT, PGTH, PGOOD, FLT | Input voltage                  | 0    |     | 18  | v    |

| dVdT, ILIM                                  |                                | 0    |     | 3   |      |

| IMON                                        |                                | 0    |     | 6   |      |

| ILIM                                        | Resistance                     | 16.9 |     | 150 | k 0  |

| IMON                                        | Resistance                     | 1    |     |     | kΩ   |

| OUT                                         | External canacitance           | 0.1  |     |     | μF   |

| dVdT                                        | External capacitance           |      |     | 470 | nF   |

| TJ                                          | Operating junction temperature | - 40 | 25  | 125 | °C   |

<sup>(2)</sup> Assumes 15 K power-on-hours at 100% duty cycle. This information is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI's semiconductor products.

## 7.4 Thermal Information

|                      |                                              | TPS25940xx-Q1 |      |

|----------------------|----------------------------------------------|---------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RVC (WQFN)    | UNIT |

|                      |                                              | 20 PINS       |      |

| R <sub>0</sub> JA    | Junction-to-ambient thermal resistance       | 38.1          | °C/W |

| R <sub>0</sub> JCtop | Junction-to-case (top) thermal resistance    | 40.5          | °C/W |

| R <sub>0</sub> JB    | Junction-to-board thermal resistance         | 13.6          | °C/W |

| ψJT                  | Junction-to-top characterization parameter   | 0.6           | °C/W |

| ψ ЈВ                 | Junction-to-board characterization parameter | 13.7          | °C/W |

| R <sub>0</sub> JCbot | Junction-to-case (bottom) thermal resistance | 3.4           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

$^-$  40°C  $\leq$  T<sub>J</sub> = T<sub>A</sub>  $\leq$  125°C, 2.7 V  $\leq$  V<sub>(IN)</sub> = 18 V, V<sub>(EN /UVLO)</sub> = 2 V, V<sub>(OVP)</sub> = V<sub>(DEVSLP)</sub> = V<sub>(PGTH)</sub> = 0 V, R<sub>(ILIM)</sub> = 150 k Ω, C<sub>(OUT)</sub> = 1 μF, C<sub>(dVdT)</sub> = OPEN, PGOOD = FLT = IMON = OPEN. Positive current into terminals. All voltages referenced to GND (unless otherwise noted)

|                          | PARAMETER                                                                | TEST CONDITIONS                                                             | MIN   | TYP  | MAX   | UNIT |

|--------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|-------|------|

| SUPPLY VOL               | TAGE AND INTERNAL UNDERVOLTAGI                                           | ELOCKOUT                                                                    |       |      |       |      |

| V <sub>(IN)</sub>        | Operating input voltage                                                  |                                                                             | 2.7   |      | 18    | V    |

| V <sub>(UVR)</sub>       | Internal UVLO threshold, rising                                          |                                                                             | 2.2   | 2.3  | 2.4   | V    |

| V <sub>(UVRhys)</sub>    | Internal UVLO hysteresis                                                 |                                                                             | 105   | 116  | 125   | mV   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 3 V                       | 140   | 210  | 300   |      |

| I <sub>Q (ON)</sub>      | Supply current, enabled                                                  | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 12 V                      | 140   | 199  | 260   | μΑ   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 18 V                      | 140   | 202  | 270   |      |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 3 V                       | 4     | 8.6  | 15    |      |

| I <sub>Q (OFF)</sub>     | Supply current, disabled                                                 | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 12 V                      | 6     | 15   | 20    | μΑ   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 18 V                      | 8     | 18.5 | 25    |      |

| I <sub>Q (DEVSLP)</sub>  | Supply current, devSleep mode                                            | V <sub>(DEVSLP)</sub> = 0 V, V <sub>(IN)</sub> = 2.7 V to 18 V              | 70    | 95   | 130   | μΑ   |

| ENABLE AND               | UNDERVOLTAGE LOCKOUT (EN/UVL                                             | O) INPUT                                                                    |       | -    | ,     |      |

| V <sub>(ENR)</sub>       | EN/UVLO threshold voltage, rising                                        |                                                                             | 0.97  | 0.99 | 1.01  | V    |

| V <sub>(ENF)</sub>       | EN/UVLO threshold voltage, falling                                       |                                                                             | 0.9   | 0.92 | 0.94  | V    |

| V <sub>(SHUTF)</sub>     | EN threshold voltage for Low I <sub>Q</sub> shutdown, falling            |                                                                             | 0.3   | 0.47 | 0.63  | V    |

| V <sub>(SHUTF hys)</sub> | EN hysteresis for low I <sub>Q</sub> shutdown, hysteresis <sup>(1)</sup> |                                                                             |       | 66   |       | mV   |

| I <sub>EN</sub>          | EN Input leakage current                                                 | 0 V ≤ V <sub>(EN/UVLO)</sub> ≤ 18 V                                         | - 100 | 0    | 100   | nA   |

| OVER VOLTA               | GE PROTECTION (OVP) INPUT                                                |                                                                             |       |      |       |      |

| V <sub>(OVPR)</sub>      | Overvoltage threshold voltage, rising                                    |                                                                             | 0.97  | 0.99 | 1.01  | V    |

| V <sub>(OVPF)</sub>      | Overvoltage threshold voltage, falling                                   |                                                                             | 0.9   | 0.92 | 0.94  | V    |

| I <sub>(OVP)</sub>       | OVP input leakage current                                                | 0 V ≤ V <sub>(OVP)</sub> ≤ 5 V                                              | - 100 | 0    | 100   | nA   |

| DEVSLP MOD               | E INPUT (DEVSLP): ACTIVE HIGH                                            |                                                                             |       |      |       |      |

| V <sub>(DEVSLPR)</sub>   | DEVSLP threshold voltage, rising                                         |                                                                             | 1.6   | 1.85 | 2     | V    |

| V <sub>(DEVSLPF)</sub>   | DEVSLP threshold voltage, falling                                        |                                                                             | 0.8   | 0.96 | 1.1   | V    |

| I <sub>(DEVSLP)</sub>    | DEVSLP input leakage current                                             | $0.2 \text{ V} \leqslant \text{V}_{\text{(DEVSLP)}} \leqslant 18 \text{ V}$ | 0.6   | 1    | 1.25  | μA   |

| OUTPUT RAM               | IP CONTROL (dVdT)                                                        |                                                                             |       |      |       |      |

| I <sub>(dVdT)</sub>      | dVdT charging current                                                    | V <sub>(dVdT)</sub> = 0 V                                                   | 0.85  | 1    | 1.15  | μA   |

| R <sub>(dVdT)</sub>      | dVdT discharging resistance                                              | EN/UVLO = 0 V, I <sub>(dVdT)</sub> = 10 mA sinking                          |       | 16   | 24    | Ω    |

| V <sub>(dVdTmax)</sub>   | dVdT maximum capacitor voltage                                           |                                                                             | 2.6   | 2.88 | 3.1   | V    |

| GAIN <sub>(dVdT)</sub>   | dVdT to OUT gain                                                         | △ V <sub>(OUT)</sub> △ V <sub>(dVdT)</sub>                                  | 11.65 | 11.9 | 12.05 | V/V  |

Submit Document Feedback

Product Folder Links: TPS25940-Q1

# 7.5 Electrical Characteristics (continued)

$^-$  40°C  $\leq$  T<sub>J</sub> = T<sub>A</sub>  $\leq$  125°C, 2.7 V  $\leq$  V<sub>(IN)</sub> = 18 V, V<sub>(EN /UVLO)</sub> = 2 V, V<sub>(OVP)</sub> = V<sub>(DEVSLP)</sub> = V<sub>(PGTH)</sub> = 0 V, R<sub>(ILIM)</sub> = 150 k Ω, C<sub>(OUT)</sub> = 1 μF, C<sub>(dVdT)</sub> = OPEN, PGOOD = FLT = IMON = OPEN. Positive current into terminals. All voltages referenced to GND (unless otherwise noted)

|                            | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                            | MIN   | TYP                                    | MAX   | UNIT      |

|----------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------|-------|-----------|

| CURRENT LIMI               | T PROGRAMMING (ILIM)                                                                        |                                                                                                                            |       |                                        |       |           |

| V <sub>(ILIM)</sub>        | ILIM bias voltage                                                                           |                                                                                                                            |       | 0.87                                   |       | V         |

|                            |                                                                                             | $R_{(ILIM)}$ = 150 k $\Omega$ , $(V_{(IN)} - V_{(OUT)})$ = 1 V, Only for TPS25940-Q1/TPS25940L-Q1                          | 0.53  | 0.58                                   | 0.63  |           |

|                            |                                                                                             | R <sub>(ILIM)</sub> = 88.7 kΩ, (V <sub>(IN)</sub> − V <sub>(OUT)</sub> ) = 1 V                                             | 0.9   | 0.99                                   | 1.07  |           |

|                            |                                                                                             | R <sub>(ILIM)</sub> = 42.2 kΩ, (V <sub>(IN)</sub> - V <sub>(OUT)</sub> ) = 1 V                                             | 1.92  | 2.08                                   | 2.25  |           |

|                            | Current limit <sup>(2)</sup>                                                                | $R_{(ILIM)} = 20 \text{ k}\Omega$ , $(V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                                 | 4.09  | 4.45                                   | 4.81  | Α         |

| I <sub>(LIM)</sub>         | Current mint                                                                                | $R_{(ILIM)} = 16.9 \text{ k} \Omega$ , $(V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                              | 4.78  | 5.2                                    | 5.62  |           |

|                            |                                                                                             | R <sub>(ILIM)</sub> = OPEN, Open resistor current limit (single point failure test: UL60950)                               | 0.35  | 0.45                                   | 0.55  |           |

|                            |                                                                                             | R <sub>(ILIM)</sub> = SHORT, Shorted resistor current limit (single point failure test: UL60950)                           | 0.55  | 0.67                                   | 0.8   |           |

| I <sub>(DEVSLP(LIM))</sub> | DevSleep mode current limit                                                                 |                                                                                                                            | 0.55  | 0.67                                   | 0.8   | Α         |

|                            |                                                                                             | $R_{(ILIM)} = 42.2 \text{ k}\Omega$ , $V_{(VIN)} = 12 \text{ V}$ , $(V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                  | 1.91  | 2.07                                   | 2.24  |           |

| Ios                        | Short-circuit current limit (2)                                                             | $R_{(ILIM)} = 20 \text{ k}\Omega$ , $V_{(VIN)} = 12 \text{ V}$ , $(V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                    | 4     | 4.4                                    | 4.7   | Α         |

|                            |                                                                                             | $R_{(ILIM)} = 16.9 \text{ k}\Omega$ , $V_{(VIN)} = 12 \text{ V}$ , $(V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                  | 4.7   | 5.11                                   | 5.52  |           |

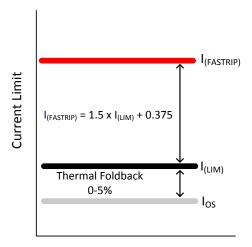

| I <sub>(FASTRIP)</sub>     | Fast-trip comparator threshold <sup>(1)</sup> (2)                                           | (iiii) (iii) (con)                                                                                                         |       | 1.5 x<br>I <sub>(LIM)</sub> +<br>0.375 |       | Α         |

| CURRENT MON                | IITOR OUTPUT (IMON)                                                                         |                                                                                                                            | •     |                                        |       |           |

| GAIN <sub>(IMON)</sub>     | Gain factor I <sub>(IMON)</sub> :I <sub>(OUT)</sub>                                         | 1 A ≤ I <sub>(OUT)</sub> ≤ 5 A                                                                                             |       | 52.3                                   |       | μA/A      |

|                            |                                                                                             | 1 A $\leq$ I $_{(OUT)}$ $\leq$ 5 A, Only for TPS25940-Q1/TPS25940L-Q1                                                      | 47.78 | 52.3                                   | 57.23 | μA/A      |

| MOSFET - PO                | WER SWITCH                                                                                  |                                                                                                                            | ·     |                                        |       |           |

|                            |                                                                                             | $1 \text{ A} \leqslant I_{(OUT)} \leqslant 5 \text{ A}, T_J = 25^{\circ}\text{C}$                                          | 34    | 42                                     | 49    |           |

| R <sub>ON</sub>            | IN to OUT - ON resistance                                                                   | $1 \text{ A} \leqslant I_{(OUT)} \leqslant 5 \text{ A}, -40^{\circ}\text{C} \leqslant T_{J} \leqslant +85^{\circ}\text{C}$ | 26    | 42                                     | 58    | $m\Omega$ |

|                            |                                                                                             | $1~\text{A} \leqslant I_{(OUT)} \leqslant 5~\text{A},~-40^{\circ}\text{C} \leqslant T_{J} \leqslant +125^{\circ}\text{C}$  | 26    | 42                                     | 64    |           |

|                            |                                                                                             | 1 A $\leq$ I $_{(OUT)}$ $\leq$ 5 A, $$ – 40°C $\leq$ T $_{J}$ $\leq$ +125°C, Only for TPS259401A-Q1                        |       | 55                                     | 85    | mΩ        |

| PASS FET OUT               | PUT (OUT)                                                                                   |                                                                                                                            |       |                                        |       |           |

|                            | OUT I I I I I I I I                                                                         | V <sub>(IN)</sub> = 18 V, V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(OUT)</sub> = 0 V (sourcing)                                | - 2   | 0                                      | 2     |           |

| I <sub>lkg(OUT)</sub>      | OUT leakage current in off state                                                            | V <sub>(IN)</sub> = 2.7 V, V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(OUT)</sub> = 18 V (sinking)                               | 6     | 13                                     | 20    | μA        |

| V <sub>(REVTH)</sub>       | V <sub>(IN)</sub> - V <sub>(OUT)</sub> threshold for reverse protection comparator, falling |                                                                                                                            | - 77  | - 66                                   | - 55  | mV        |

| V <sub>(FWDTH)</sub>       | V <sub>(IN)</sub> - V <sub>(OUT)</sub> threshold for reverse protection comparator, rising  |                                                                                                                            | 86    | 100                                    | 114   | mV        |

| FAULT FLAG ( I             | FLT): ACTIVE LOW                                                                            |                                                                                                                            |       |                                        |       |           |

| R <sub>(FLT)</sub>         | FLT internal pull-down resistance                                                           | V <sub>(OVP)</sub> = 2 V, I <sub>(FLT)</sub> = 5 mA sinking                                                                | 10    | 18                                     | 30    | Ω         |

| I <sub>(FLT)</sub>         | FLT input leakage current                                                                   | $0 \text{ V} \leqslant V_{(FLT)} \leqslant 18 \text{ V}$                                                                   | - 1   | 0                                      | 1     | μA        |

| POSITIVE INPU              | T for POWER-GOOD COMPARATOR                                                                 | (PGTH)                                                                                                                     |       |                                        |       |           |

| V <sub>(PGTHR)</sub>       | PGTH threshold voltage, rising                                                              |                                                                                                                            | 0.97  | 0.99                                   | 1.01  | V         |

| V <sub>(PGTHF)</sub>       | PGTH threshold voltage, falling                                                             |                                                                                                                            | 0.9   | 0.92                                   | 0.94  | V         |

| I <sub>(PGTH)</sub>        | PGTH input leakage current                                                                  | $0 \text{ V} \leqslant \text{V}_{(PGTH)} \leqslant 18 \text{ V}$                                                           | - 100 | 0                                      | 100   | nA        |

| POWER-GOOD                 | COMPARATOR OUTPUT (PGOOD):                                                                  | ACTIVE HIGH                                                                                                                |       |                                        |       |           |

| R <sub>(PGOOD)</sub>       | PGOOD internal pull-down resistance                                                         | V <sub>(PGTH)</sub> = 0V, I <sub>(PGOOD)</sub> = 5 mA sinking                                                              | 10    | 20                                     | 35    | Ω         |

| I <sub>(PGOOD)</sub>       | PGOOD input leakage current                                                                 | $0 \text{ V} \leq \text{V}_{(PGOOD)} \leq 18 \text{ V}$                                                                    | - 1   | 0                                      | 1     | μA        |

| THERMAL SHU                | T DOWN (TSD)                                                                                |                                                                                                                            |       |                                        |       |           |

| T <sub>(TSD)</sub>         | TSD threshold <sup>(1)</sup>                                                                |                                                                                                                            |       | 160                                    |       | °C        |

## 7.5 Electrical Characteristics (continued)

$^-$  40°C  $\lesssim$  T<sub>J</sub> = T<sub>A</sub>  $\lesssim$  125°C, 2.7 V  $\lesssim$  V<sub>(IN)</sub> = 18 V, V<sub>(EN /UVLO)</sub> = 2 V, V<sub>(OVP)</sub> = V<sub>(DEVSLP)</sub> = V<sub>(PGTH)</sub> = 0 V, R<sub>(ILIM)</sub> = 150 k Ω, C<sub>(OUT)</sub> = 1 μF, C<sub>(dVdT)</sub> = OPEN, PGOOD = FLT = IMON = OPEN. Positive current into terminals. All voltages referenced to GND (unless otherwise noted)

|                       | PARAMETER                     | TEST CONDITIONS            | MIN        | TYP | MAX | UNIT |

|-----------------------|-------------------------------|----------------------------|------------|-----|-----|------|

| T <sub>(TSDhys)</sub> | TSD hysteresis <sup>(1)</sup> |                            |            | 12  |     | °C   |

|                       | Thermal fault response        | TPS25940-Q1, TPS259401A-Q1 | Auto-retry |     |     |      |

|                       |                               | TPS25940L-Q1               | Latch-off  |     |     |      |

- (1) These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

- (2) Pulse-testing techniques maintain junction temperature close to ambient temperature. Thermal effects must be taken into account separately.

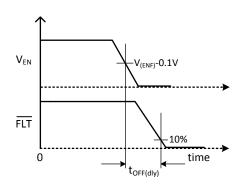

## 7.6 Timing Requirements

$^-$  40°C ≤ T<sub>J</sub> = T<sub>A</sub> ≤ 125°C, 2.7 V ≤ V<sub>(IN)</sub> = 18 V, V<sub>(EN /UVLO)</sub> = 2 V, V<sub>(OVP)</sub> = V<sub>(DEVSLP)</sub> = V<sub>(PGTH)</sub> = 0 V, R<sub>(ILIM)</sub> = 150 k Ω, C<sub>(OUT)</sub> = 1 μF, C<sub>(dVdT)</sub> = OPEN, PGOOD = FLT = IMON = OPEN. Positive current into terminals. All voltages referenced to GND (unless otherwise noted). See  $\boxed{8}$  8-1 for the timing diagrams.

|                           | PARAMETER                           | TEST CONDITIONS                                                                                              | MIN TYP                            | MAX  | UNIT |  |

|---------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|------|------|--|

| ENABLE and                | UVLO INPUT                          |                                                                                                              |                                    | -    |      |  |

| t <sub>ON(dly)</sub>      | EN turnon delay                     | EN/UVLO † (100 mV above $V_{(ENR)}$ ) to $V_{(OUT)}$ = 100 mV, $C_{(dVdT)}$ < 0.8 nF                         | 220                                |      | μs   |  |

|                           |                                     | EN/UVLO † (100 mV above $V_{(ENR)}$ ) to $V_{(OUT)}$ = 100 mV, $C_{(dVdT)} \ge 0.8$ nF, $[C_{(dVdT)}$ in nF] | 100 + 150 ×<br>C <sub>(dVdT)</sub> |      | μs   |  |

| t <sub>OFF(dly)</sub>     | EN turnoff delay                    | EN/UVLO ↓ (100 mV below V <sub>(ENF)</sub> ) to FLT ↓                                                        | 2                                  |      | μs   |  |

| OVERVOLTA                 | GE PROTECTION INPUT (OVP)           |                                                                                                              |                                    |      |      |  |

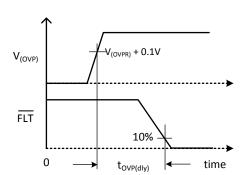

| t <sub>OVP(dly)</sub>     | OVP disable delay                   | OVP $\uparrow$ (100 mV above V <sub>(OVPR)</sub> ) to $\overline{\text{FLT}} \downarrow$                     | 2                                  |      | μs   |  |

| OUTPUT RAI                | MP CONTROL (dV/dT )                 |                                                                                                              |                                    | 1    |      |  |

| t <sub>dVdT</sub>         | Output ramp time                    | EN/UVLO $\uparrow$ to $V_{(OUT)} = 4.5 \text{ V}$ , with $C_{(dVdT)} = \text{open}$                          | 0.12                               |      | ms   |  |

|                           |                                     | EN/UVLO $\uparrow$ to $V_{(OUT)} = 11 \text{ V, with } C_{(dVdT)} = \text{open}$                             | 0.25 0.37                          | 0.5  |      |  |

|                           |                                     | EN/UVLO $\uparrow$ to $V_{(OUT)} = 11 \text{ V, with } C_{(dVdT)} = 1 \text{ nF}$                            | 0.97                               |      |      |  |

| CURRENT LI                | MIT                                 |                                                                                                              |                                    |      |      |  |

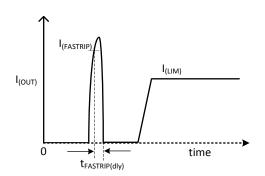

| t <sub>FASTRIP(dly)</sub> | Fast-trip comparator delay          | I <sub>(OUT)</sub> > I <sub>(FASTRIP)</sub>                                                                  | 200                                |      | ns   |  |

| REVERSE PR                | ROTECTION COMPARATOR                |                                                                                                              |                                    | ·    |      |  |

| t <sub>REV(dly)</sub>     | Reverse protection comparator delay | $(V_{(IN)} - V_{(OUT)}) \downarrow (1 \text{ mV overdrive below } V_{(REVTH)}) \text{ to } \overline{FLT}$   | 10                                 |      | μs   |  |

|                           |                                     | $(V_{(IN)} - V_{(OUT)}) \downarrow (10 \text{ mV overdrive below } V_{(REVTH)}) \text{ to } \overline{FLT}$  | 1                                  |      |      |  |

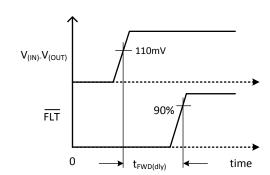

| t <sub>FWD(dly)</sub>     |                                     | $(V_{(IN)} - V_{(OUT)}) \uparrow (10 \text{ mV overdrive above } V_{(FWDTH)}) \text{ to}$                    | 3.1                                |      |      |  |

| POWER-GOO                 | DD COMPARATOR OUTPUT (PGOOD): A     | CTIVE HIGH                                                                                                   |                                    |      |      |  |

| t <sub>PGOODR</sub>       | DOOOD dalaas (da alitab) tiraa      | Rising edge                                                                                                  | 0.42 0.54                          | 0.66 | ms   |  |

| t <sub>PGOODF</sub>       | PGOOD delay (de-glitch) time        | Falling edge                                                                                                 | 0.42 0.54                          | 0.66 | ms   |  |

| THERMAL SI                | HUT DOWN (TSD)                      |                                                                                                              |                                    |      |      |  |

|                           | Retry delay in TSD                  | TPS25940-Q1/TPS259401A-Q1 Only                                                                               | 128                                |      | ms   |  |

Product Folder Links: TPS25940-Q1

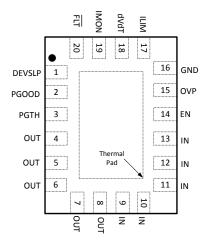

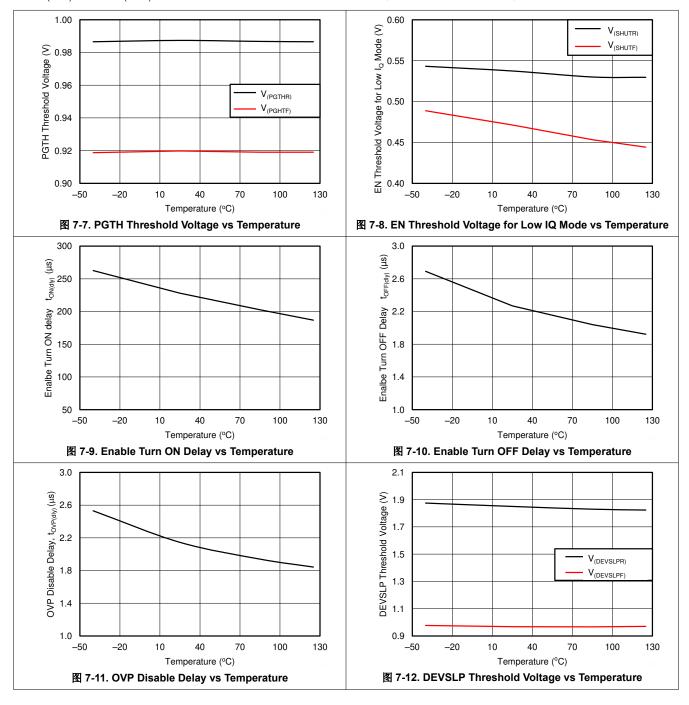

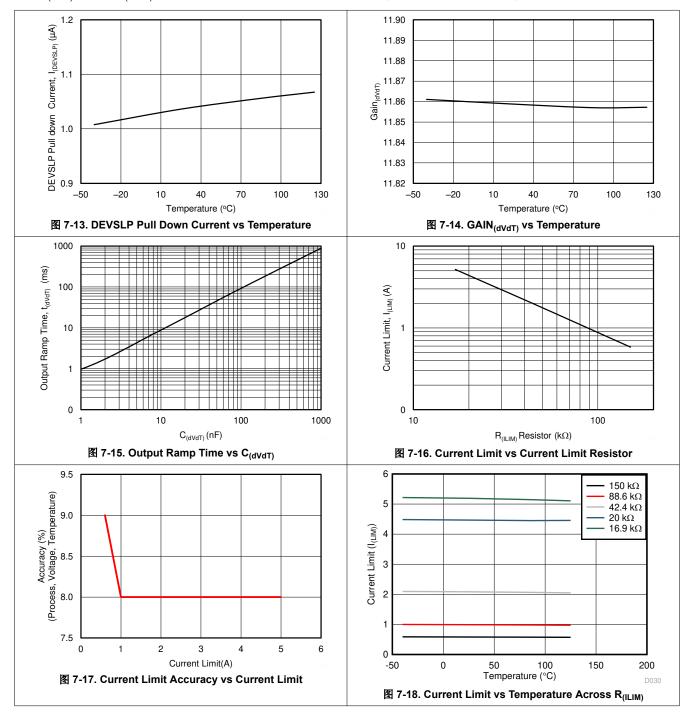

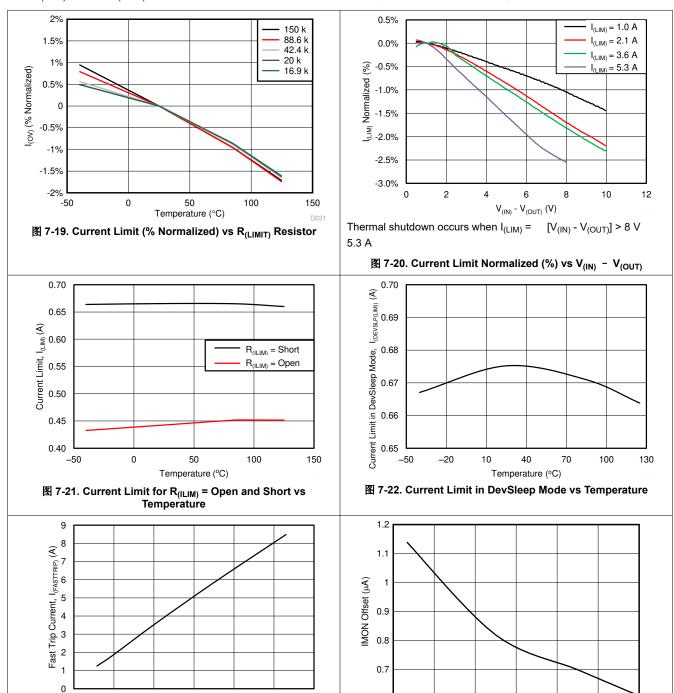

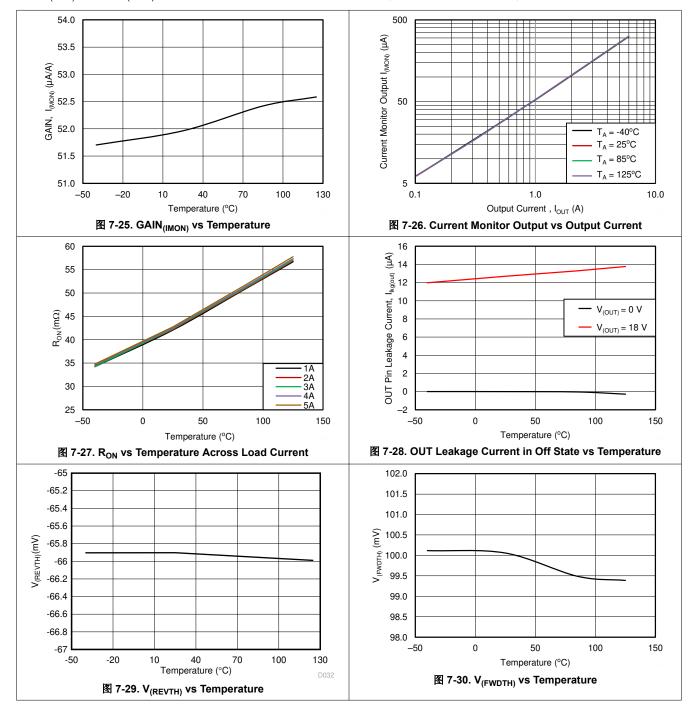

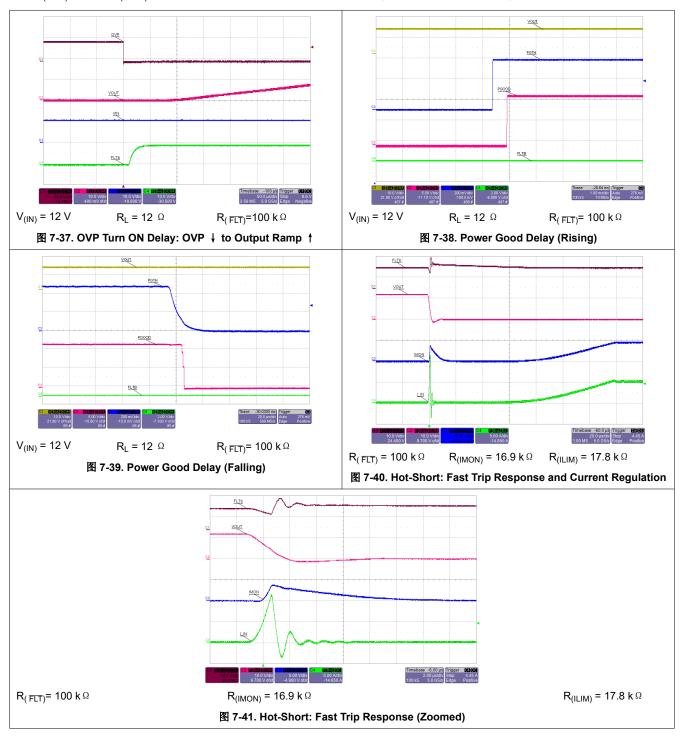

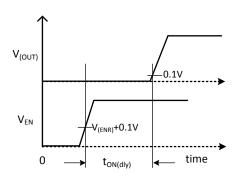

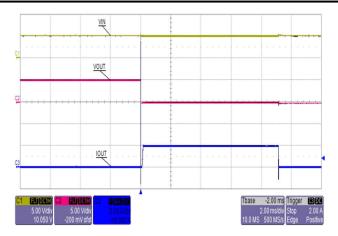

## 7.7 Typical Characteristics

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(\text{IN})}$  = 12 V,  $V_{(\text{EN/UVLO})}$  = 2 V,  $V_{(\text{OVP})}$  =  $V_{(\text{DEVSLP})}$  =  $V_{(\text{PGTH})}$  = 0 V,  $V_{(\text{ILIM})}$  = 150 k  $\Omega$  ,  $V_{(\text{OUT})}$  = 1  $V_{(\text{COUT})}$  = 0 PEN, PGOOD = FLT = IMON = OPEN. (unless stated otherwise)

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(IN)}$  = 12 V,  $V_{(EN/UVLO)}$  = 2 V,  $V_{(OVP)}$  =  $V_{(DEVSLP)}$  =  $V_{(PGTH)}$  = 0 V,  $V_{(ILIM)}$  = 150 k  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 PEN, PGOOD =  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 0

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(IN)}$  = 12 V,  $V_{(EN/UVLO)}$  = 2 V,  $V_{(OVP)}$  =  $V_{(DEVSLP)}$  =  $V_{(PGTH)}$  = 0 V,  $V_{(ILIM)}$  = 150 k  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 PEN, PGOOD =  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 0

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(IN)}$  = 12 V,  $V_{(EN/UVLO)}$  = 2 V,  $V_{(OVP)}$  =  $V_{(DEVSLP)}$  =  $V_{(PGTH)}$  = 0 V,  $V_{(ILIM)}$  = 150 k  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 PEN, PGOOD =  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 0

Submit Document Feedback

Current Limit  $I_{(LIM)}$  (A)

图 7-23. Fast Trip Threshold vs Current Limit

Copyright © 2021 Texas Instruments Incorporated

D022

Temperature (°C)

图 7-24. IMON Offset vs Temperature

0.6 -50

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(IN)}$  = 12 V,  $V_{(EN/UVLO)}$  = 2 V,  $V_{(OVP)}$  =  $V_{(DEVSLP)}$  =  $V_{(PGTH)}$  = 0 V,  $V_{(ILIM)}$  = 150 k  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 PEN, PGOOD =  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 0

Copyright © 2021 Texas Instruments Incorporated

Conditions are  $-40^{\circ}\text{C} \leqslant T_{A}$  =  $T_{J} \leqslant 125^{\circ}\text{C}$ ,  $V_{(IN)}$  = 12 V,  $V_{(EN/UVLO)}$  = 2 V,  $V_{(OVP)}$  =  $V_{(DEVSLP)}$  =  $V_{(PGTH)}$  = 0 V,  $V_{(ILIM)}$  = 150 k  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 PEN, PGOOD =  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 1  $V_{COUT}$  = 1  $V_{COUT}$  = 0 V,  $V_{COUT}$  = 0

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Conditions are  $-40^{\circ}\text{C} \leqslant T_{\text{A}} = T_{\text{J}} \leqslant 125^{\circ}\text{C}$ ,  $V_{(\text{IN})} = 12 \text{ V}$ ,  $V_{(\text{EN/UVLO})} = 2 \text{ V}$ ,  $V_{(\text{OVP})} = V_{(\text{DEVSLP})} = V_{(\text{PGTH})} = 0 \text{ V}$ ,  $R_{(\text{ILIM})} = 150 \text{ k}\,\Omega$ ,  $C_{(\text{OUT})} = 1 \text{ \muF}$ ,  $C_{(\text{dVdT})} = \text{OPEN}$ , PGOOD = FLT = IMON = OPEN. (unless stated otherwise)

Copyright © 2021 Texas Instruments Incorporated

# **8 Parametric Measurement Information**

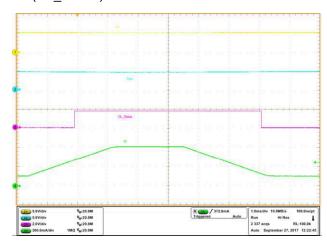

图 8-1. Timing Diagrams

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 9 Detailed Description

#### 9.1 Overview

The TPS25940xx-Q1 device is a smart eFuse with integrated back-to-back FETs and enhanced built-in protection circuitry. It provides robust protection for all systems and applications powered from 2.7 V to 18 V.

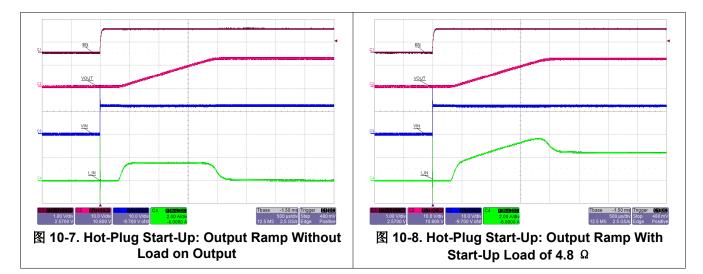

For hot-plug-in boards, the device provides hot-swap power management with in-rush current control and programmable output ramp-rate. The device integrates overcurrent and short circuit protection. The precision overcurrent limit helps to minimize over design of the input power supply, while the fast response short circuit protection immediately isolates the load from input when a short circuit is detected. The device allows the user to program the overcurrent limit threshold between 0.6 A and 5.3 A via an external resistor.

The device provides precise monitoring of voltage bus for brown-out and overvoltage conditions and asserts fault for downstream system. Its overall threshold accuracy of 2% ensures tight supervision of bus, eliminating the need for a separate supply voltage supervisor chip.

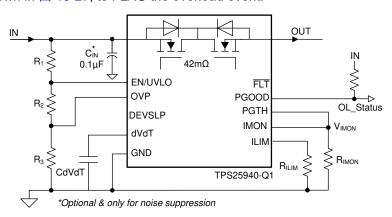

The device is designed to protect systems such as USB hubs against sudden output short to battery events. The device monitors  $V_{(IN)}$  and  $V_{(OUT)}$  to provide true reverse blocking from output when output short to battery fault condition or input power fail condition is detected.

The additional features include:

- Precise current monitor output for health monitoring of the system

- Additional power good comparator with precision internal reference for output or any other rail voltage monitoring

- · Over temperature protection to safely shutdown in the event of an overcurrent event

- De-glitched fault reporting for brown-out and overvoltage faults

- · A choice of latched or automatic restart mode

# 9.2 Functional Block Diagram

## 9.3 Feature Description

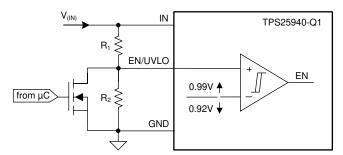

#### 9.3.1 Enable and Adjusting Undervoltage Lockout

The EN/UVLO pin controls the ON and OFF state of the internal FET. A voltage  $V_{(EN/UVLO)} < V_{(ENF)}$  on this pin turns off the internal FET, thus disconnecting IN from OUT, while voltage below  $V_{(SHUTF)}$  takes the device into shutdown mode, with  $I_Q$  less than 15  $\mu$ A to ensure minimal power loss. Cycling EN/UVLO low and then back high resets the TPS25940L-Q1 that has latched off due to a fault condition.

The internal de-glitch delay on EN/UVLO falling edge is kept low for quick detection of power failure. For applications where a higher de-glitch delay on EN/UVLO is desired, or when the supply is particularly noisy, it is recommended to use an external bypass capacitor from EN/UVLO terminal to GND.

The undervoltage lock out can be programmed by using an external resistor divider from supply IN terminal to EN/UVLO terminal to GND as shown in Second 9-1. When an undervoltage or input power fail event is detected, the internal FET is quickly turned off, and FLT is asserted. If the Under-Voltage Lock-Out function is not needed, the EN/UVLO terminal must be connected to the IN terminal. EN/UVLO terminal must not be left floating.

The device also implements internal undervoltage-lockout (UVLO) circuitry on the IN terminal. The device disables when the IN terminal voltage falls below internal UVLO Threshold  $V_{(UVF)}$ . The internal UVLO threshold has a hysteresis of 115 mV.

图 9-1. UVLO and OVP Thresholds Set By  $R_1$ ,  $R_2$  and  $R_3$

## 9.3.2 Overvoltage Protection (OVP)

The device incorporates circuit to protect system during overvoltage conditions. A resistor divider connected from the supply to OVP terminal to GND (as shown in  $\boxtimes$  9-1) programs the overvoltage threshold. A voltage more than  $V_{(OVPR)}$  on OVP pin turns off the internal FET and protects the downstream load. This pin must be tied to GND when not used.

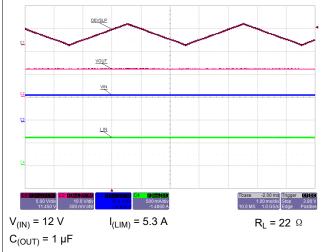

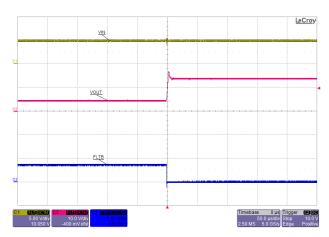

## 9.3.3 Hot Plug-In and In-Rush Current Control

The device is designed to control the in-rush current upon insertion of a card into a live backplane or other "hot" power source. This limits the voltage sag on the backplane's supply voltage and prevents unintended resets of the system power. A slew rate controlled startup (dVdT) also helps to eliminate conductive and radiative interferences. An external capacitor connected from the dVdT pin to GND defines the slew rate of the output voltage at power-on (as shown in 图 9-2). Equation governing slew rate at start-up is shown in 方程式 1.

Copyright © 2021 Texas Instruments Incorporated

图 9-2. Output Ramp Up Time t<sub>dVdT</sub> is Set by C<sub>(dVdT)</sub>

$$I_{(dVdT)} = \left(\frac{C_{(dVdT)}}{GAIN_{(dVdT)}}\right) \times \left(\frac{dV_{(OUT)}}{dt}\right)$$

(1)

#### where

- $I_{(dVdT)} = 1 \mu A \text{ (typical)}$  $dV_{(OUT)}$

- dt = Desired output slew rate

- GAIN<sub>(dVdT)</sub> = dVdT to OUT gain = 12

The total ramp time  $(t_{dVdT})$  of  $V_{(OUT)}$  for 0 to  $V_{(IN)}$  can be calculated using 方程式 2.

$$t_{dVdT} = 8.3 \times 10^4 \times V_{(IN)} \times C_{(dVdT)}$$

(2)

The inrush current, I(INRUSH) can be calculated as shown in 方程式 3.

$$I_{\text{(INRUSH)}} = C_{\text{(OUT)}} \times V_{\text{(IN)}} / t_{\text{dVdT}}. \tag{3}$$

The dVdT pin can be left floating to obtain a predetermined slew rate ( $t_{dVdT}$ ) on the output. When terminal is left floating, the device sets an internal ramp rate of 30 V/ms for output ( $V_{(OUT)}$ ) ramp.

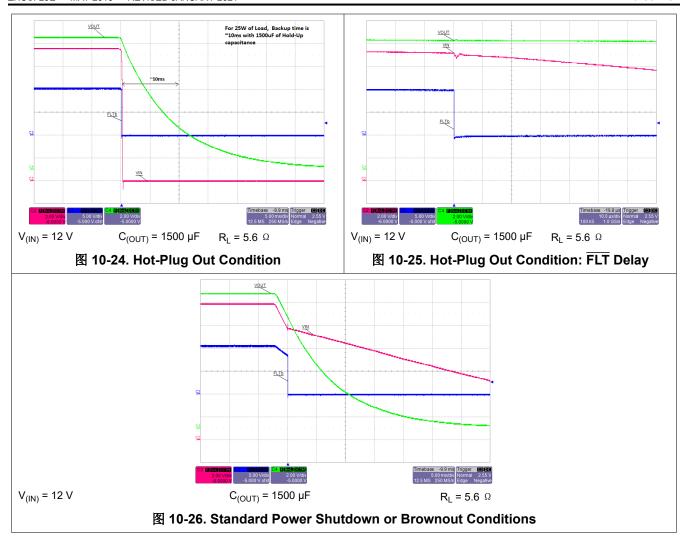

$\boxtimes$  10-7 and  $\boxtimes$  10-8 illustrate the inrush current control behavior of the device. For systems where load is present during start-up, the current never exceeds the overcurrent limit set by  $R_{(ILIM)}$  resistor for the application. For defining appropriate charging time-rate under different load conditions, see the *Setting Output Voltage Ramp Time* ( $T_{dVdT}$ ) section.

#### 9.3.4 Overload and Short Circuit Protection

At all times load current is monitored by sensing voltage across an internal sense resistor. During overload events, current is limited to the current limit ( $I_{(LIM)}$ ) programmed by  $R_{(ILIM)}$  resistor as shown in 方程式 4.

$$I_{(LIM)} = \frac{89}{R_{(ILIM)}} \tag{4}$$

#### where

- · I(LIM) is overload current limit in Ampere

- $R_{(ILIM)}$  is the current limit resistor in  $k \Omega$

The device incorporates two distinct levels: a current limit  $(I_{(LIM)})$  and a fast-trip threshold  $(I_{(FASTRIP)})$ . Fast trip and current limit operation are shown in  $\boxed{\$}$  9-3.

Bias current on ILIM pin directly controls current-limiting behavior of the device, and PCB routing of this node must be kept away from any noisy (switching) signals.

#### 9.3.4.1 Overload Protection

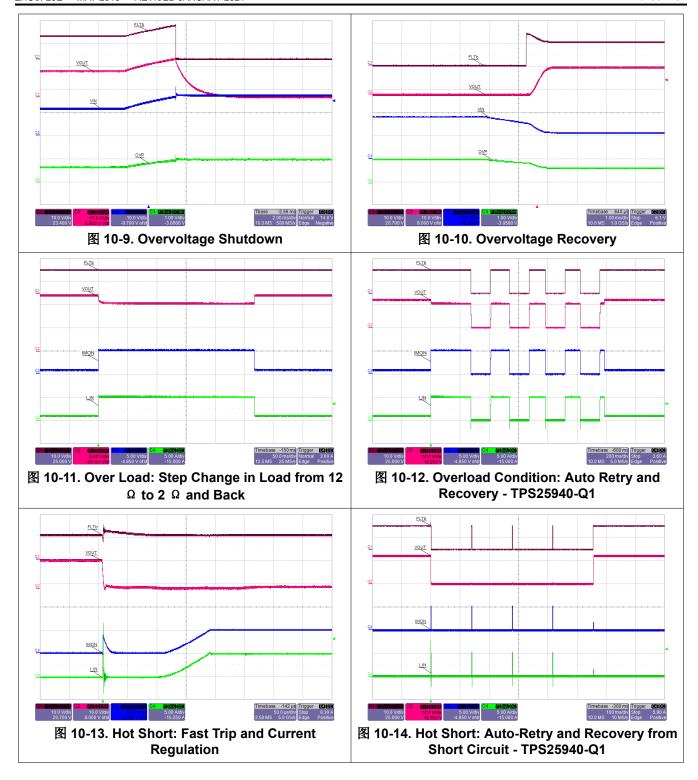

For overload conditions, the internal current-limit amplifier regulates the output current to  $I_{(LIM)}$ . The output voltage droops during the current regulation, resulting in increased power dissipation in the device. If the device junction temperature reaches the thermal shutdown threshold  $(T_{(TSD)})$ , the internal FET is turned off. When in thermal shutdown, the TPS25940L-Q1 version stays latched off, whereas the TPS25940-Q1/TPS259401A-Q1 versions commence an auto-retry cycle 128 ms after  $T_J < [T_{(TSD)} - 12^{\circ}C]$ . During thermal shutdown, the fault pin  $\overline{FLT}$  pulls low to signal a fault condition.  $\boxed{8}$  10-11 and  $\boxed{8}$  10-12 illustrate overload behavior.

#### 9.3.4.2 Short Circuit Protection

During a transient short circuit event, the current through the device increases very rapidly. As current-limit amplifier cannot respond quickly to this event because of its limited bandwidth, the device incorporates a fast-trip comparator, with a threshold  $I_{(FASTRIP)}$ . This comparator shuts down the pass device within 1µs, when the current through internal FET exceeds  $I_{(FASTRIP)}$  ( $I_{(OUT)} > I_{(FASTRIP)}$ ), and terminates the rapid short-circuit peak current. The trip threshold is set to more than 50% of the programmed overload current limit ( $I_{(FASTRIP)} = 1.5 \times I_{(LIM)} + 0.375$ ). The fast-trip circuit holds the internal FET off for only a few microseconds, after which the device turns back on slowly, allowing the current-limit loop to regulate the output current to  $I_{(LIM)}$ . Then, device behaves similar to overload condition.  $\boxed{8}$  10-13 through  $\boxed{8}$  10-14 illustrate the behavior of the system when the current exceeds the fast-trip threshold.

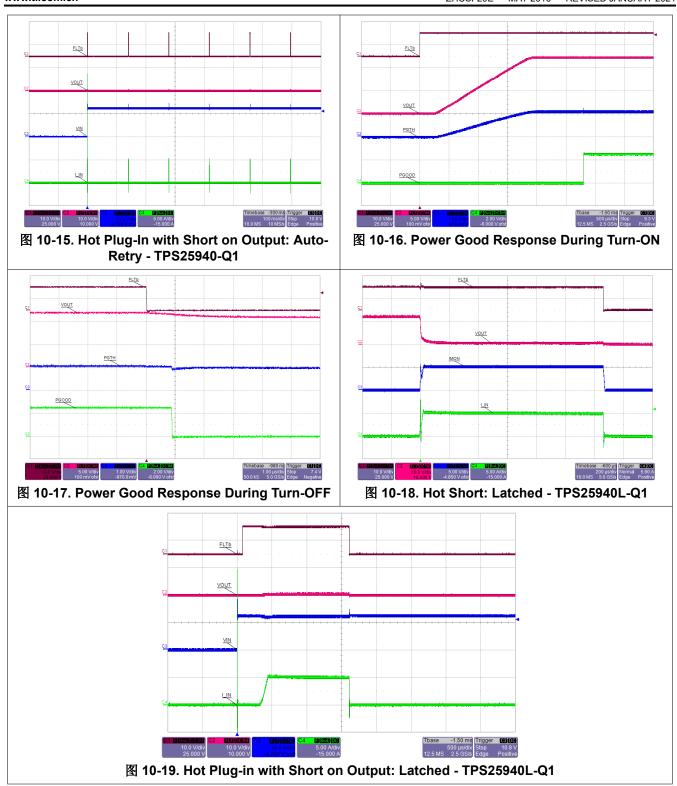

## 9.3.4.3 Start-Up with Short on Output

During start-up into a short circuit current is limited to  $I_{(LIM)}$ .  $\boxtimes$  9-3 and  $\boxtimes$  10-15 illustrate start-up with a short on the output. This feature helps in quick fault isolation and hence ensures stability of the DC bus.

#### 9.3.4.4 Constant Current Limit Behavior During Overcurrent Faults

When power dissipation in the internal FET [ $P_D = (V_{(IN)} - V_{(OUT)}) \times I_{(OUT)}$ ] > 10 W, there is approximately 0% to 5% thermal fold back in the current limit value so that  $I_{(LIM)}$  drops to  $I_{OS}$ . Eventually, the device shuts down because of over temperature.

图 9-3. Fast-Trip Current

#### 9.3.5 FAULT Response

The FLT open-drain output is asserted (active low) during undervoltage, overvoltage, reverse voltage-current and thermal shutdown conditions. The FLT signal remains asserted until the fault condition is removed and the device resumes normal operation. The device is designed to eliminate false fault reporting by using an internal "de-glitch" circuit for undervoltage and overvoltage (2.2-µs typical) conditions without the need for external circuitry. This ensures that fault is not accidentally asserted during transients on input bus.

Copyright © 2021 Texas Instruments Incorporated

Connect  $\overline{FLT}$  with a pull up resistor to Input or Output voltage rail.  $\overline{FLT}$  may be left open or tied to ground when not used.  $V_{(IN)}$  falling below  $V_{(IVF)} = 2.1$  V resets  $\overline{FLT}$ .

#### 9.3.6 Current Monitoring

The current source at IMON terminal is configured to be proportional to the current flowing from IN to OUT. This current can be converted to a voltage using a resistor  $R_{(IMON)}$  from IMON terminal to GND terminal. This voltage, computed using 方程式 6, can be used as a means of monitoring current flow through the system.

The maximum voltage range for monitoring the current  $(V_{(IMONmax)})$  is limited to minimum( $[V_{(IN)} - 2.2 V]$ , 6 V) to ensure linear output. This puts limitation on maximum value of  $R_{(IMON)}$  resistor and is determined by 方程式 5.

$$R_{(IMONmax)} = \frac{\text{minimum } (V_{(IN)} - 2.2, 6)}{1.6 \times I_{(LIM)} \times GAIN_{(IMON)}}$$

(5)

The output voltage at IMON terminal is calculated from 方程式 6.

$$V_{(IMON)} = [I_{(OUT)} \times GAIN_{(IMON)} + I_{(IMON_OS)}] \times R_{(IMON)}$$

(6)

#### where

- GAIN<sub>(IMON)</sub> = Gain factor I<sub>(IMON)</sub>:I<sub>(OUT)</sub> = 52 μA/A

- I<sub>(OUT)</sub> = Load current

- $I_{(IMON OS)} = 0.8 \mu A \text{ (typical)}$

This pin must not have a bypass capacitor to avoid delay in the current monitoring information.

The voltage at IMON pin can be digitized using an ADC (such as ADS1100, SBAS239) to read the current monitor information over an I<sup>2</sup>C bus.

#### 9.3.7 Power Good Comparator

The device incorporates a Power Good comparator for co-ordination of status to downstream DC-DC converters or system monitoring circuits. The comparator has an internal reference of  $V_{(PGTHR)} = 0.99 \text{ V}$  at negative terminal and positive terminal PGTH can be utilized for monitoring of either input or output of the device. The comparator output PGOOD is an open-drain active high signal, which can be used to indicate the status to downstream units. PGOOD is asserted high when internal FET is fully enhanced and PGTH pin voltage is higher than internal reference  $V_{(PGTHR)}$ .

The PGOOD signal has deglitch time incorporated to ensure that internal FET is fully enhanced before heavy load is applied by downstream converters. Rising de-glitch delay is determined by 方程式 7.

$$t_{PGOOD(degl)} = Maximum\{(3.5 \times 10^6 \times C_{(dVdT)}), t_{PGOODR}\}$$

(7)

Connect the PGOOD pin with a pull up resistor to Input or Output voltage rail. PGOOD may be left open or tied to ground when not used.

#### 9.3.8 IN, OUT and GND Pins

The device has multiple pins for input (IN) and output (OUT).

All IN pins must be connected together and to the power source. A ceramic bypass capacitor close to the device from IN to GND is recommended to alleviate bus transients. The recommended operating voltage range is 2.7 V - 18 V.

Similarly all OUT pins must be connected together and to the load.  $V_{(OUT)}$  in the ON condition, is calculated using 方程式 8.

$$V_{(OUT)} = V_{(IN)} - (R_{ON} \times I_{(OUT)})$$

(8)

where,  $R_{\text{ON}}$  is the total ON resistance of the internal FET.

Instruments www.ti.com.cn

GND terminal is the most negative voltage in the circuit and is used as a reference for all voltage reference unless otherwise specified.

#### 9.3.9 Thermal Shutdown

Internal over temperature shutdown disables turns off the FET when T<sub>J</sub> > 160°C (typical). The TPS25940L-Q1 version stays latched off, whereas TPS25940-Q1/TPS259401A-Q1 versions commence an auto-retry cycle 128 ms after T<sub>J</sub> drops below [T<sub>(TSD)</sub> - 12°C]. During the thermal shutdown, the fault pin FLT pulls low to signal a fault condition.

#### 9.4 Device Functional Modes

#### 9.4.1 DevSleep Mode

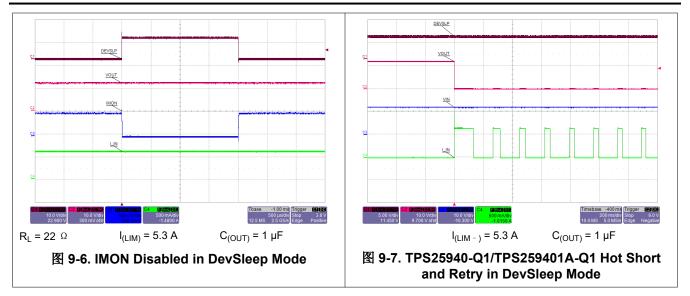

The TPS25940xx-Q1 device provides a dedicated DevSleep interface terminal (DEVSLP) to drive the device in low power mode. When pulled high, it puts the device in low power DevSleep mode. In this mode, the quiescent current consumption of the device is limited to less than 130 µA (95-µA typical). During this mode, the output voltage remains active, the overload current limit is set to I<sub>(DEVSLP(LIM))</sub> and functionality of reverse comparator and current monitoring is disabled. All other protections are kept active ensuring the safety of the system even in DevSleep mode.

User must ensure that load currents on the bus are limited to less than I<sub>(DEVSLP(LIM))</sub>, when the device is driven to DevSleep mode. Also, while coming out of DevSleep, it is important to sequence the TPS25940xx-Q1 earlier than the load. Otherwise, the load can exceed I(DEVSLP(LIM)) and cause the TPS25940xx-Q1 to enter the overload mode.

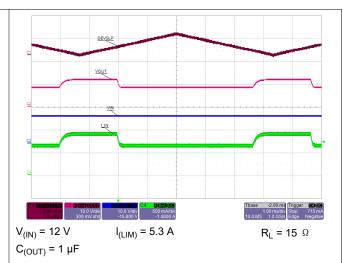

IN and OUT of DevSleep Mode with 550-mA Load through TPS25940-Q1/TPS259401A-Q1 Hot Short and Retry in DevSleep Mode illustrate the behavior of the system in DevSleep mode.

图 9-4. IN and OUT of DevSleep Mode with 550-mA Load

图 9-5. IN and OUT of DevSleep Mode with 800-mA Load. In DevSleep, Load Current Gets Limited to I(DEVSLP(LIM))

#### 9.4.2 Shutdown Control

The internal FET and hence the load current can be remotely switched off by taking the UVLO pin below its 0.6-V threshold with an open collector or open drain device as shown in  $\boxed{8}$  9-8. The device quiescent current is reduced to less than 20  $\mu$ A in this state. Upon releasing the UVLO pin the device turns on with soft-start cycle.

图 9-8. Shutdown Control

# 10 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 10.1 Application Information

The TPS25940xx-Q1 device is a smart eFuse. It is typically used for Hot-Swap and Power rail protection applications. It operates from 2.7 V to 18 V with programmable current limit, overvoltage and undervoltage protection. The device aids in controlling the in-rush current and provides fast turn-off during reverse voltage conditions for systems such as USB ports prone to Short-to-Battery faults, Servers, Power Back-up Storage units and RAID cards. The device also provides robust protection for multiple faults on the sub-system rail.

The Detailed Design Procedure section can be used to select component values for the device.

Alternatively, the WEBENCH® software may be used to generate a complete design. The WEBENCH® software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. Additionally, a spreadsheet design tool *TPS25940 Design Calculator* is available on web folder.

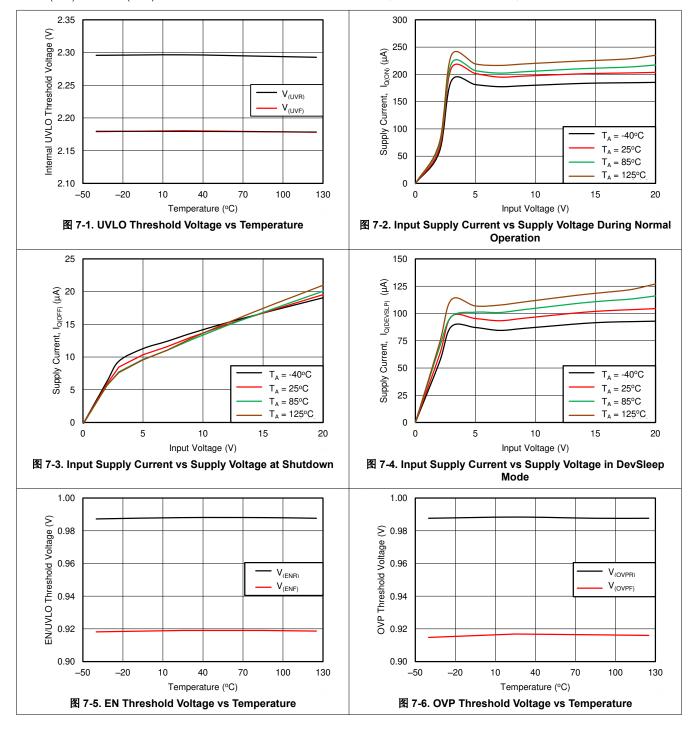

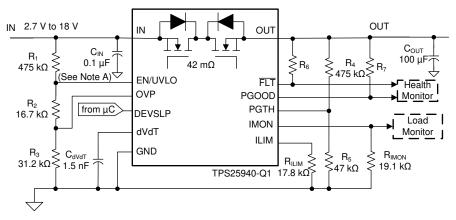

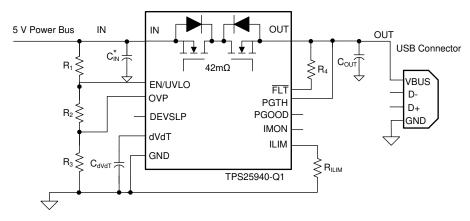

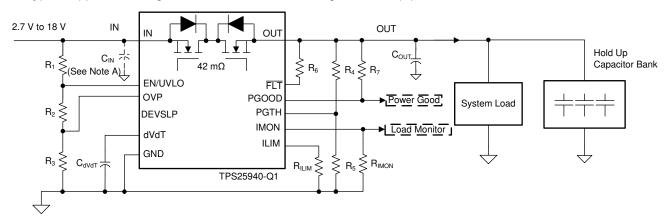

## 10.2 Typical Application

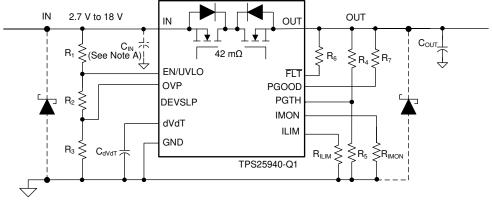

C<sub>IN</sub>: Optional and only for noise suppression.

图 10-1. Typical Application Schematic

#### 10.2.1 Design Requirements

表 10-1 lists the Design Parameters.

表 10-1. Design Parameters

| DESIGN PARAMETER                                     | EXAMPLE VALUE |

|------------------------------------------------------|---------------|

| Input voltage, V <sub>(IN)</sub>                     | 12 V          |

| Undervoltage lockout set point, V <sub>(UV)</sub>    | 10.8 V        |

| Overvoltage protection set point, V <sub>(LIM)</sub> | 16.5 V        |

| Load at Start-Up, R <sub>L(SU)</sub>                 | 4.8 Ω         |

| Current limit, I <sub>(LIM)</sub>                    | 5 A           |

| Load capacitance, C <sub>(OUT)</sub>                 | 100 μF        |

| Maximum ambient temperatures, T <sub>A</sub>         | 85°C          |

## 10.2.2 Detailed Design Procedure

The following design procedure can be used to select component values for the TPS25940xx-Q1.

## 10.2.2.1 Step by Step Design Procedure

To begin the design process a few parameters must be decided upon. The designer must know the following:

- · Normal input operation voltage

- · Maximum output capacitance

- · Maximum current Limit

- Load during start-up

- Maximum ambient temperature of operation

This design procedure below seeks to control the junction temperature of device under both static and transient conditions by proper selection of output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria.

## 10.2.2.2 Programming the Current-Limit Threshold: R<sub>(ILIM)</sub> Selection

The R<sub>(ILIM)</sub> resistor at the ILIM pin sets the over load current limit, this can be set using 方程式 9.

$$R_{\text{(ILIM)}} = \frac{89}{5} = 17.8 \text{k}\Omega \tag{9}$$

Choose closest standard value: 17.8-k, 1% standard value resistor.

#### 10.2.2.3 Undervoltage Lockout and Overvoltage Set Point

$$V_{(OVPR)} = \frac{R_3}{R_1 + R_2 + R_3} \times V_{(OV)}$$

(10)

$$V_{(ENR)} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \times V_{(UV)}$$

(11)

For minimizing the input current drawn from the power supply  $\{I_{(R123)} = V_{(IN)}/(R_1 + R_2 + R_3)\}$ , it is recommended to use higher values of resistance for  $R_1$ ,  $R_2$  and  $R_3$ .

However, leakage currents because of the external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I_{(R123)}$  must be chosen to be 20 times greater than the leakage current expected.

Using the closest standard 1% resistor values gives R<sub>1</sub> = 475 k  $\Omega$  , R<sub>2</sub> = 16.7 k  $\Omega$  , and R<sub>3</sub> = 31.2 k  $\Omega$  .

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 7% lower than the rising threshold,  $V_{(UV)}$ . This is calculated using 方程式 12.

$$V_{(PFAIL)} = 0.93 \times V_{(UV)} \tag{12}$$

#### 10.2.2.4 Programming Current Monitoring Resistor—R<sub>IMON</sub>

Voltage at IMON pin  $V_{(IMON)}$  represents the voltage proportional to load current. This can be connected to an ADC of the downstream system for health monitoring of the system. The  $R_{(IMON)}$  need to be configured based on the maximum input voltage range of the ADC used.  $R_{(IMON)}$  is set using 方程式 13.

$$R_{\text{(IMON)}} = \frac{V_{\text{(IMONmax)}}}{I_{\text{(LIM)}} \times 52 \times 10^{-6}} \text{ k}\Omega$$

(13)

For  $I_{(LIM)} = 5$  A, and considering the operating range of ADC from 0 V to 5 V,  $V_{(IMONmax)}$  is 5 V and  $R_{(IMON)}$  is determined by:

$$R_{\text{(IMON)}} = \frac{5}{5 \times 52 \times 10^{-6}} = 19.23 \text{ k}\Omega \tag{14}$$

Selecting  $R_{(IMON)}$  value less than determined by 方程式 14 ensures that ADC limits are not exceeded for maximum value of load current.

If the IMON pin voltage is not being digitized with an ADC,  $R_{(IMON)}$  can be selected to produce a 1V/1A voltage at the IMON pin, using 方程式 13.

Choose closest 1 % standard value: 19.1 k  $\Omega$ .

If current monitoring up to  $I_{(FASTRIP)}$  is desired,  $R_{(IMON)}$  can be reduced by a factor of 1.6, as in 方程式 5.

#### 10.2.2.5 Setting Output Voltage Ramp Time (t<sub>dVdT</sub>)

For a successful design, the junction temperature of device must be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The ramp-up capacitor  $C_{(dVdT)}$  needed is calculated considering the two possible cases Case 1: Start-up Without Load: Only Output Capacitance C(OUT) Draws Current During Start-up and Case 2: Start-Up With Load: Output Capacitance C(OUT) and Load Draws Current During Start-Up.

#### 10.2.2.5.1 Case1: Start-Up Without Load: Only Output Capacitance C<sub>(OUT)</sub> Draws Current During Start-Up

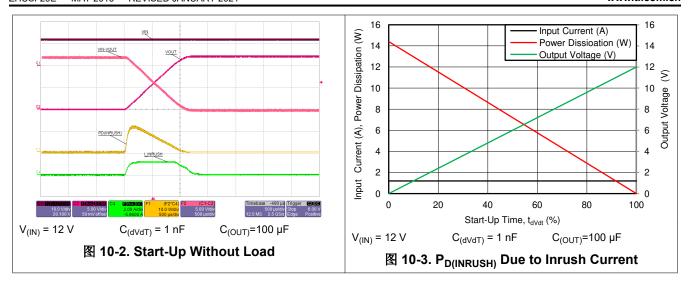

During start-up, as the output capacitor charges, the voltage difference across the internal FET decreases, and the power dissipated decreases as well. Typical ramp-up of output voltage  $V_{(OUT)}$  with inrush current limit of 1.2 A and power dissipated in the device during start-up is shown in Start-Up Without Load. The average power dissipated in the device during start-up is equal to area of triangular plot (red curve in Start-Up Without Load) averaged over  $t_{dVdT}$ .

Copyright © 2021 Texas Instruments Incorporated

For the TPS25940-Q1 device, the inrush current is determined as shown in 方程式 15.

$$I = C \times \frac{dV}{dT} = > I_{(INRUSH)} = C_{(OUT)} \times \frac{V_{(IN)}}{t_{dVdT}}$$

(15)

Power dissipation during start-up is given by 方程式 16.

$$P_{D(INRUSH)} = 0.5 \times V_{(IN)} \times I_{(INRUSH)}$$

(16)

方程式 16 assumes that load does not draw any current until the output voltage has reached its final value.

## 10.2.2.5.2 Case 2: Start-Up With Load: Output Capacitance C(OUT) and Load Draws Current During Start-Up

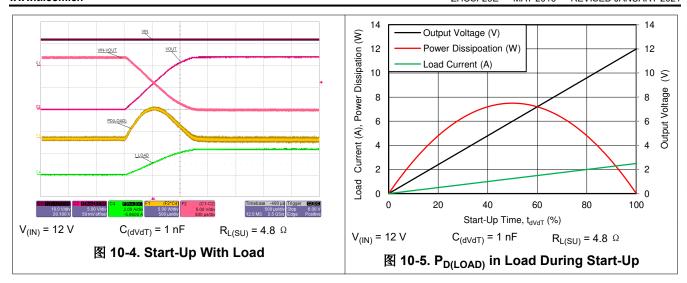

When load draws current during the turn-on sequence, there is additional power dissipated. Considering a resistive load  $R_{L(SU)}$  during start-up, load current ramps up proportionally with increase in output voltage during  $t_{dVdT}$  time. Typical ramp-up of output voltage, Load current and power dissipation in the device is shown in Start-Up With Load and power dissipation with respect to time is plotted in  $P_{D(LOAD)}$  in Load During Start-Up. The additional power dissipation during start-up phase is calculated as shown in 5 元代 17 and 5 元代 18.

$$(V_{I} - V_{O})(t) = V_{(IN)} \times \left(1 - \frac{t}{t_{dVdT}}\right)$$

(17)

$$I_{L}(t) = \left(\frac{V_{(IN)}}{R_{L}(SU)}\right) \times \frac{t}{t_{d}VdT}$$

(18)

Where  $R_{L(SU)}$  is the load resistance present during start-up. Average energy loss in the internal FET during charging time due to resistive load is given by 方程式 19.

$$W_{t} = \int_{0}^{tdVdT} V_{(IN)} \times \left(1 - \frac{t}{t_{dVdT}}\right) \times \left(\frac{V_{(IN)}}{R_{L(SU)}} \times \frac{t}{t_{dVdT}}\right) dt$$

(19)

On solving 方程式 19 the average power loss in the internal FET due to load is shown in 方程式 20.

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{V^2(IN)}{R_{L(SU)}}$$

(20)

Total power dissipated in the device during startup is shown is 方程式 21.

$$P_{D(STARTUP)} = P_{D(INRUSH)} + P_{D(LOAD)}$$

(21)

Total current during startup is given by 方程式 22.

$$I_{(STARTUP)} = I_{(INRUSH)} + I_{L}(t)$$

(22)

If  $I_{(STARTUP)} > I_{(LIM)}$ , the device limits the current to  $I_{(LIM)}$  and the current limited charging time is determined by 方程式 23.

$$t_{dVdT(current\ limited)} = C_{(OUT)} \times \frac{V_{(IN)}}{I_{(LIM)}}$$

(23)

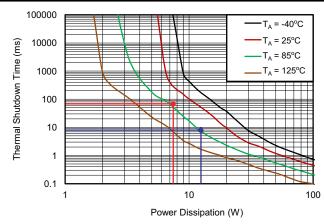

The power dissipation, with and without load, for selected start-up time must not exceed the shutdown limits as shown in Thermal Shutdown Limit Plot.

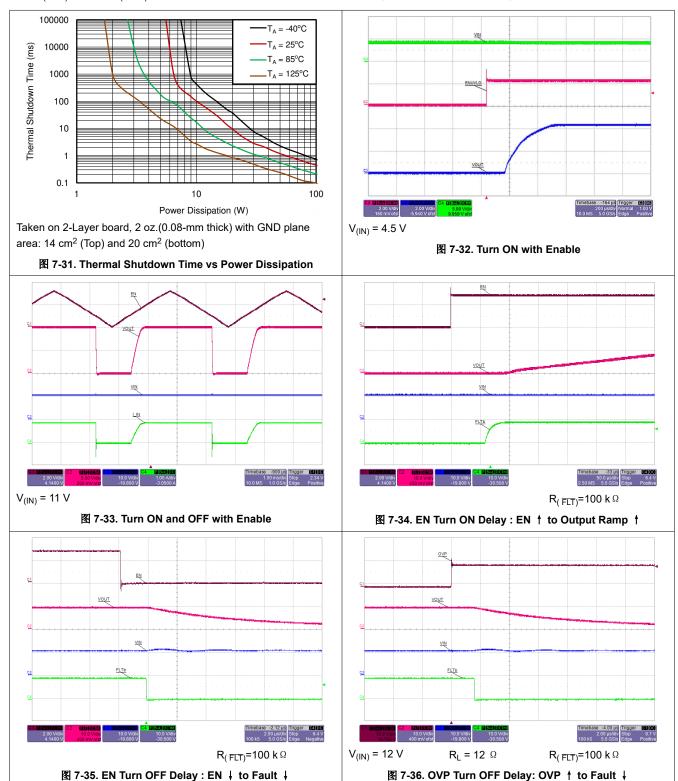

Taken on 2-Layer board, 2oz.(0.08-mm thick) with GND plane area: 14 cm<sup>2</sup> (Top) and 20 cm<sup>2</sup> (bottom)

#### 图 10-6. Thermal Shutdown Limit Plot

For the design example under discussion,

Select ramp-up capacitor  $C_{(dVdT)}$  = 1nF, using 方程式 24.

$$t_{dvdt} = 8.3 \times 10^4 \times 12 \times 1 \times 10^{-9} = 0.996 \text{ms} = \sim 1 \text{ms}$$

(24)

The inrush current drawn by the load capacitance ( $C_{(OUT)}$ ) during ramp-up using 方程式 25.

$$I_{\text{(INRUSH)}} = \left(100 \times 10^{-6}\right) \times \left(\frac{12}{1 \times 10^{-3}}\right) = 1.2 \text{ A}$$

(25)

The inrush Power dissipation is calculated, using 方程式 26.

$$P_{D(INRUSH)} = 0.5 \times 12 \times 1.2 = 7.2 \text{ W}$$

(26)

For 7.2 W of power loss, the thermal shut down time of the device must not be less than the ramp-up time  $t_{dVdT}$  to avoid the false trip at maximum operating temperature. From thermal shutdown limit graph Thermal Shutdown Limit Plot at  $T_A = 85$ °C, for 7.2 W of power the shutdown time is approximately 60 ms. So it is safe to use 1 ms as start-up time without any load on output.

Considering the start-up with load 4.8  $\Omega$ , the additional power dissipation, when load is present during start up is calculated, using 方程式 27.

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{12 \times 12}{4.8} = 5 \text{ W}$$

(27)

The total device power dissipation during start up is given by 方程式 28.

$$P_{D(STARTUP)} = (7.2+5) = 12.2 \text{ W}$$

(28)

From thermal shutdown limit graph at  $T_A$  = 85°C, the thermal shutdown time for 12.2 W is close to 7.5 ms. It is safe to have 30% margin to allow for variation of system parameters such as load, component tolerance, and input voltage. So it is well within acceptable limits to use the 1 nF capacitor with start-up load of 4.8  $\Omega$ .

If there is a need to decrease the power loss during start-up, it can be done with increase of  $C_{(dVdT)}$  capacitor.

To illustrate, choose  $C_{(dVdT)} = 1.5 \text{ nF}$  as an option and recalculate:

$$t_{dvdt} = 1.5ms$$

(29)

$$I_{\text{(INRUSH)}} = \left(100 \times 10^{-6}\right) \times \left(\frac{12}{1.5 \times 10^{-3}}\right) = 0.8 \text{ A}$$

(30)

$$P_{D(INRUSH)} = 0.5 \times 12 \times 0.8 = 4.8 \text{ W}$$

(31)

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \left(\frac{12 \times 12}{4.8}\right) = 5 \text{ W}$$

(32)

$$P_{D(STARTUP)} = 4.8 + 5 = 9.8 \text{ W}$$

(33)

From thermal shutdown limit graph at  $T_A = 85^{\circ}C$ , the shutdown time for 10-W power dissipation is approximately 17 ms, which increases the margins further for shutdown time and ensures successful operation during start up and steady state conditions.

The spreadsheet tool available on the web can be used for iterative calculations.

### 10.2.2.6 Programing the Power Good Set Point

As shown in  $\[ egin{align*} 2 & 10-1 \]$ ,  $\[ R_4 \]$  and  $\[ R_5 \]$  sets the required limit for PGOOD signal as needed for the downstream converters. Considering a power good threshold of 11 V for this design, the values of  $\[ R_4 \]$  and  $\[ R_5 \]$  are calculated using 方程式 34.

$$V_{(PGTH)} = 0.99 \times \left(1 + \frac{R_4}{R_5}\right)$$

(34)

It is recommended to have high values for these resistors to limit the current drawn from the output node. Choosing a value of  $R_4$  = 475 k  $\Omega$ ,  $R_5$  = 47 k  $\Omega$  provides  $V_{(PGTH)}$  = 11 V.

## 10.2.2.7 Support Component Selections—R<sub>6</sub>, R<sub>7</sub> and C<sub>IN</sub>