# TPS23754, TPS23754-1, TPS23756

ZHCSHL4I - OCTOBER 2008 - REVISED DECEMBER 2017

# TPS2375x 符合 IEEE 802.3at 标准的高效 PoE 接口和直流/直流控制器

# 1 特性

- 可为功率高达 30W 的(输入) 受电设备供电

- 直流/直流控制,针对隔离式转换器进行了优化

- 支持高效拓扑结构

- 完整的 PoE 接口

- 符合 IEEE 802.3at 标准且具有状态标志的增强型分类

- 适配器 ORing 支持

- 可编程频率具有同步功能

- 稳定耐用的 100V, 0.5Ω 热插拔金属氧化物半导体 场效应晶体管 (MOSFET)

- -40°C 至 125°C 的工作结点温范围

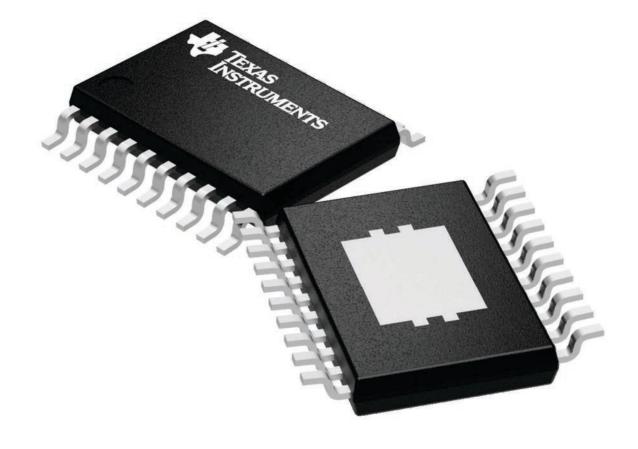

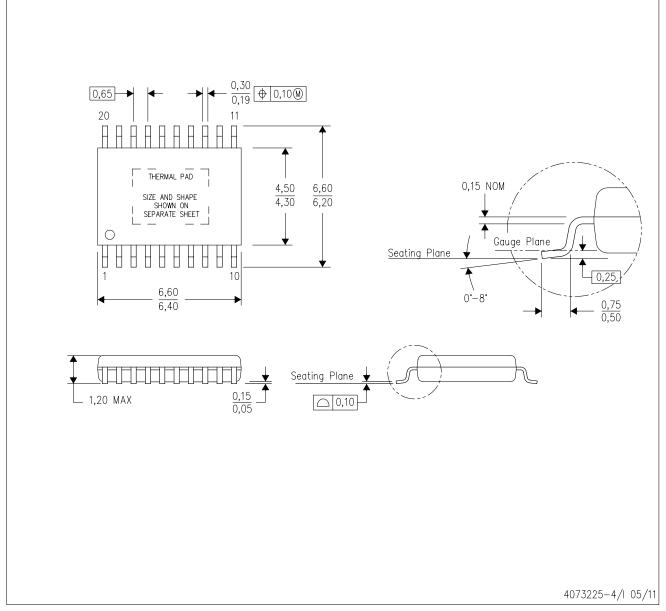

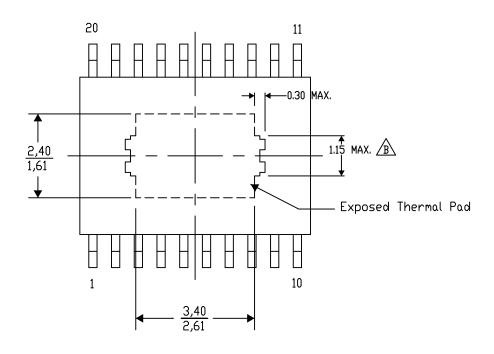

- 行业标准 PowerPAD™HTSSOP-20

### 2 应用

- IEEE 802.3at 兼容器件

- 视频和网络语音 (VoIP) 电话

- RFID 阅读器

- 多频带访问点

- 监控摄像机

# 3 说明

TPS23754 和 TPS23756 器件具有合并的以太网供电 (PoE) 受电设备 (PD) 接口和电流模式直流/直流控制器 (专门针对隔离式转换器进行了优化)。此 PoE 接口支持 IEEE 802.3at 标准。

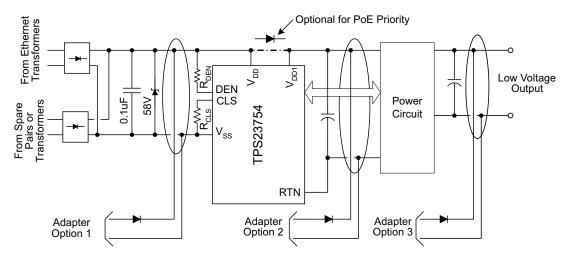

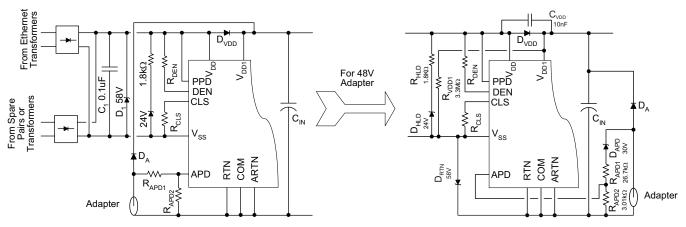

TPS23754 和 TPS23756 支持多个输入电压 ORing 选项,其中包括最高电压、外部适配器首选项和 PoE 首选项。这些 特性 使得设计人员在任何情况下都能确定哪个电源承担负载。

PoE 接口 具有 与高功率中跨供电设备 (PSE) 兼容 (符合 IEEE 802.3at 标准) 所需的新扩展硬件分类。 签名检测引脚也可被用来强制关闭 PoE 供电。使用一个单个电阻器可将分类设定为已定义类别中的任何一个。

该直流/直流控制器 采用 两个具有可编程死区时间的互补栅极驱动器。这简化了有源钳位正向转换器或优化的栅极驱动器设计,从而实现高效的反激式拓扑。如果只需单个 MOSFET 拓扑需要,则可以禁用第二个栅极驱动器。该控制器还 具有 内部软启动、自举启动电源、电流模式补偿以及 78% 最大占空比等特性。一个可编程和可同步振荡器可针对使用效率对设计进行优化并简化控制器的使用以升级现有的电源设计。具有一个缺省周期的精确可编程消隐简化了常见电流感测滤波器设计平衡。

TPS23754 器件具有 15V 的转换器启动电压阈值,而 TPS23756 器件具有 9V 的转换器启动电压阈值。 TPS23754-1 使用 no-connect (不连接)连接状态取代了 PPD 引脚,从而增大引脚间距。

### 器件信息(1)

| 器件型号       | 封装          | 封装尺寸 (标称值)      |

|------------|-------------|-----------------|

| TPS23754   |             |                 |

| TPS23754-1 | HTSSOP (20) | 6.50mm x 4.40mm |

| TPS23756   |             |                 |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

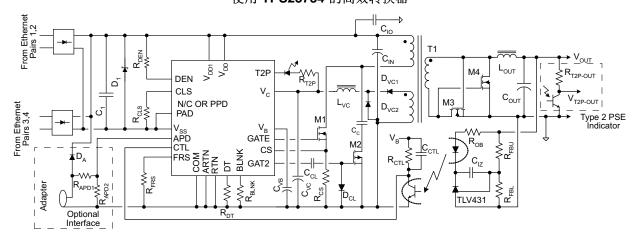

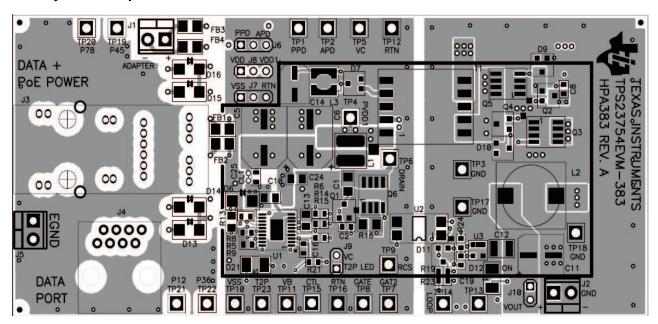

### 使用 TPS23754 的高效转换器

| 口水 |

|----|

|----|

| 1 | 特性1                                             |    | 7.3 Feature Description        | 13        |

|---|-------------------------------------------------|----|--------------------------------|-----------|

| 2 | 应用 1                                            |    | 7.4 Device Functional Modes    | 17        |

| 3 |                                                 | 8  | Application and Implementation | 27        |

| 4 | 修订历史记录                                          |    | 8.1 Application Information    | <u>27</u> |

| 5 | Pin Configuration and Functions                 |    | 8.2 Typical Application        |           |

| 6 | Specifications4                                 | 9  | Power Supply Recommendations   |           |

| U | 6.1 Absolute Maximum Ratings                    | 10 | Layout                         | 37        |

|   | 6.2 ESD Ratings                                 |    | 10.1 Layout Guidelines         | 37        |

|   | 6.3 Recommended Operating Conditions            |    | 10.2 Layout Example            | 37        |

|   | 6.4 Thermal Information                         |    | 10.3 ESD                       | 37        |

|   | 6.5 Electrical Characteristics 6                | 11 | 器件和文档支持                        | 38        |

|   | 6.6 Electrical Characteristics: PoE and Control |    | 11.1 文档支持                      |           |

|   | 6.7 Switching Characteristics                   |    | 11.2 社区资源                      | 38        |

|   | 6.8 Typical Characteristics                     |    | 11.3 商标                        |           |

| 7 | Detailed Description                            |    | 11.4 静电放电警告                    | 38        |

| • | 7.1 Overview                                    |    | 11.5 Glossary                  |           |

|   | 7.2 Functional Block Diagram 13                 | 12 | 机械、封装和可订购信息                    |           |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Revision H (September 2015) to Revision IPage• 已更改 将标题更改成了 TPS2375x 符合 IEEE 802.3at 标准的高效 PoE 接口和直流/直流控制器1Changes from Revision G (October 2013) to Revision HPage• 添加了引脚配置和功能 部分、ESD 额定值 表、特性 说明 部分、器件功能模式、应用和实施 部分、电源相关建议 部分、布局 部分、器件和文档支持 部分以及机械、封装和可订购信息 部分1• Changed "Operating junction temperature" row to "Maximum junction temperature", and updated the MIN and MAX values to Internally limited4

# 5 Pin Configuration and Functions

### **Pin Functions**

|      | PIN                         |            |      |                                                                                                                                                                                                                        |  |  |

|------|-----------------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | TPS23754<br>and<br>TPS23756 | TPS23754-1 | TYPE | DESCRIPTION                                                                                                                                                                                                            |  |  |

| APD  | 17                          | 17         | I    | Raising $V_{APD} - V_{ARTN}$ above 1.5 V disables the internal hotswap switch, turns class off, and forces T2P active. This forces power to come from a external $V_{DD1-RTN}$ adapter. Tie APD to ARTN when not used. |  |  |

| ARTN | 8                           | 8          | _    | ARTN is the DC-DC converter analog return. Tie to RTN and COM on the circuit board.                                                                                                                                    |  |  |

| BLNK | 18                          | 18         | I    | Connect to ARTN to use the internally set current-sense blanking period, or connect a resistor from BLNK to ARTN to program a more accurate period.                                                                    |  |  |

| CLS  | 15                          | 15         | I    | Connect a resistor from CLS to V <sub>SS</sub> to program classification current. 2.5 V is applied to the program resistor during classification to set class current.                                                 |  |  |

| COM  | 4                           | 4          | _    | Gate driver return, connect to ARTN and RTN.                                                                                                                                                                           |  |  |

| CS   | 3                           | 3          | I/O  | DC-DC converter switching MOSFET current sense input. See R <sub>CS</sub> in Figure 27.                                                                                                                                |  |  |

| CTL  | 1                           | 1          | I    | The control loop input to the pulse-width modulator (PWM), typically driven by output regulation feedback (for example, optocoupler). Use V <sub>B</sub> as a pullup for CTL.                                          |  |  |

| DEN  | 13                          | 13         | I/O  | Connect a 24.9-k $\Omega$ resistor from DEN to V <sub>DD</sub> to provide the PoE detection signature. Pulling this pin to V <sub>SS</sub> during powered operation causes the internal hotswap MOSFET to turn off.    |  |  |

| DT   | 16                          | 16         | I    | Connect a resistor from DT to ARTN to set the GATE to GAT2 dead time. Tie DT to $V_{\text{B}}$ to disable GAT2 operation.                                                                                              |  |  |

| FRS  | 19                          | 19         | I    | Connect a resistor from FRS to ARTN to program the converter switching frequency. FRS may be used to synchronize the converter to an external timing source.                                                           |  |  |

| GATE | 5                           | 5          | 0    | Gate drive output for the main DC-DC converter switching MOSFET.                                                                                                                                                       |  |  |

| GAT2 | 7                           | 7          | 0    | Gate drive output for a second DC-DC converter switching MOSFET (see Figure 27).                                                                                                                                       |  |  |

| NC   | _                           | 14         | _    | Float this no-connect pin.                                                                                                                                                                                             |  |  |

| PAD  | _                           | _          | _    | Connect to V <sub>SS</sub> .                                                                                                                                                                                           |  |  |

| PPD  | 14                          | _          | I    | Raising $V_{PPD\text{-VSS}}$ above 1.55 V enables the hotswap MOSFET and activates T2P. Connecting PPD to $V_{DD}$ enables classification when APD is active. Tie PPD to $V_{SS}$ or float when not used.              |  |  |

| RTN  | 9                           | 9          | _    | RTN is the output of the PoE hotswap MOSFET.                                                                                                                                                                           |  |  |

| T2P  | 20                          | 20         | 0    | Active low output that indicates a PSE has performed the IEEE 802.3at type 2 hardware classification, PPD is active, or APD is active.                                                                                 |  |  |

### Pin Functions (continued)

| PIN             |                                        |    |      |                                                                                                                                                         |  |  |

|-----------------|----------------------------------------|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | TPS23754<br>and TPS23754-1<br>TPS23756 |    | TYPE | DESCRIPTION                                                                                                                                             |  |  |

| V <sub>B</sub>  | 2                                      | 2  | 0    | 5.1-V bias rail for DC-DC control circuits and the feedback optocoupler. Typically bypass with a 0.1 $\mu$ F to ARTN.                                   |  |  |

| V <sub>C</sub>  | 6                                      | 6  | I/O  | DC-DC converter bias voltage. Connect a 0.47 µF (minimum) ceramic capacitor to ARTN at the pin, and a larger capacitor to power start-up.               |  |  |

| $V_{DD}$        | 12                                     | 12 | ı    | Connect to the positive PoE input power rail. V <sub>DD</sub> powers the PoE interface circuits. Bypass with a 0.1-µF capacitor and protect with a TVS. |  |  |

| $V_{DD1}$       | 11                                     | 11 | I    | Source of DC-DC converter start-up current. Connect to V <sub>DD</sub> for many applications.                                                           |  |  |

| V <sub>SS</sub> | 10                                     | 10 | _    | Connect to the negative power rail derived from the PoE source.                                                                                         |  |  |

# **Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2). Voltage with respect to V<sub>SS</sub> unless otherwise noted.

|                                       |                                                                                                              | MIN                | MAX                  | UNIT  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-------|--|

|                                       | ARTN <sup>(2)</sup> , COM <sup>(2)</sup> , DEN, PPD, RTN <sup>(3)</sup> , V <sub>DD</sub> , V <sub>DD1</sub> | -0.3               | 100                  | O.u.  |  |

|                                       | CLS <sup>(4)</sup>                                                                                           | -0.3               | 6.5                  |       |  |

| Input voltage                         | [APD, BLNK <sup>(4)</sup> , CTL, DT <sup>(4)</sup> , FRS <sup>(4)</sup> , VB <sup>(4)</sup> ] to [ARTN, COM] | -0.3               | 6.5                  | V     |  |

|                                       | CS to [ARTN,COM]                                                                                             | -0.3               | V <sub>B</sub>       |       |  |

|                                       | [ARTN, COM] to RTN                                                                                           | -2                 | 2                    |       |  |

| N-11                                  | V <sub>C</sub> , T2P, to [ARTN, COM]                                                                         | -0.3               | 19                   | \/    |  |

| Voltage                               | GATE <sup>(4)</sup> , GAT2 <sup>(4)</sup> to [ARTN, COM]                                                     | -0.3               | V <sub>C</sub> + 0.3 | V     |  |

| Sinking current                       | RTN                                                                                                          | Internally limited |                      | mA    |  |

| Sourcing current                      | V <sub>B</sub>                                                                                               | Internally limited |                      | mA    |  |

| Average Sourcing or sinking current   | GATE, GAT2                                                                                                   |                    | 25                   | mArms |  |

| Maximum junction temperature, T       | Interna                                                                                                      | lly limited        | °C                   |       |  |

| Storage temperature, T <sub>stg</sub> |                                                                                                              | -65                | 150                  | °C    |  |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE        | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|--------------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | 2000         |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | 500          | V    |

|                    |                         | System level (contact/air) at RJ-45 <sup>(3)</sup>                  | 8000 / 15000 |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

ARTN and COM must be tied to RTN.

$I_{RTN} = 0$  for  $V_{RTN} > 80$  V. Do not apply voltage to these pins

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

ESD per EN61000-4-2. A power supply containing the TPS23754 was subjected to the highest test levels in the standard. See the ESD section.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted). Voltage with respect to V<sub>SS</sub> (unless otherwise noted)<sup>(1)</sup>

|                                                                |                                                         | MIN  | NOM | MAX            | UNIT |

|----------------------------------------------------------------|---------------------------------------------------------|------|-----|----------------|------|

|                                                                | ARTN, COM, PPD, RTN, V <sub>DD</sub> , V <sub>DD1</sub> | 0    |     | 57             | V    |

| lanut valtaga ranga                                            | T2P, V <sub>C</sub> to [ARTN, COM]                      | 0    |     | 18             | V    |

| Input voltage range                                            | APD, CTL, DT to [ARTN, COM]                             | 0    |     | V <sub>B</sub> | V    |

|                                                                | CS to [ARTN, COM]                                       | 0    |     | 2              | V    |

| Continuous RTN current (T <sub>J</sub> ≤ 125°C) <sup>(2)</sup> |                                                         |      |     | 825            | mA   |

| Sourcing current                                               | $V_{B}$                                                 | 0    | 2.5 | 5              | mA   |

| V <sub>B</sub> capacitance                                     | ·                                                       | 0.08 |     |                | μF   |

| R <sub>BLNK</sub>                                              |                                                         | 0    |     | 350            | kΩ   |

| Synchronization pulse w                                        | idth input (when used)                                  | 25   |     |                | ns   |

| Operating junction temporal                                    | erature range, T <sub>J</sub>                           | -40  |     | 125            | °C   |

<sup>(1)</sup> ARTN and COM tied to RTN.

# 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                             | TPS23754,<br>TPS23754-1,<br>TPS23756 | UNIT          |

|----------------------|-----------------------------------------------------------|--------------------------------------|---------------|

|                      |                                                           | PWP (HTSSOP)                         | <b>O</b> 1111 |

|                      |                                                           | 20 PINS                              |               |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                    | 44.4                                 | °C/W          |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                 | 23.4                                 | °C/W          |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                      | 20.1                                 | °C/W          |

| ΨЈТ                  | Junction-to-top characterization parameter <sup>(2)</sup> | 0.7                                  | °C/W          |

| ΨЈВ                  | Junction-to-board characterization parameter              | 19.9                                 | °C/W          |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> This is the minimum current limit value. Viable systems are designed for maximum currents less than this value with reasonable margin. IEEE 802.3at permits 600-mA continuous loading.

<sup>(2)</sup> Thermal resistance junction to case top for devices mounted per SLMA002.  $T_J = T_{TOP} + (\Psi_{JT} \times P_J)$ . Use  $\Psi_{JT}$  to validate  $T_J$  from measurements.

### 6.5 Electrical Characteristics

Unless otherwise noted: CS = COM = APD = CTL = RTN = ARTN, GATE and GAT2 float,  $R_{FRS}$ = 68.1 k $\Omega$ ,  $R_{BLNK}$ = 249 k $\Omega$ , DT =  $V_B$ , PPD =  $V_{SS}$ , T2P open,  $C_{VB}$  =  $C_{VC}$  = 0.1  $\mu$ F,  $R_{DEN}$  = 24.9 k $\Omega$ ,  $R_{CLS}$  open, 0 V ≤ ( $V_{DD}$ ,  $V_{DD1}$ ) ≤ 57 V, 0 V ≤  $V_C$  ≤ 18 V,  $-40^{\circ}$ C ≤  $T_J$  ≤ 125°C. Typical specifications are at 25°C.

### **CONTROLLER SECTION ONLY**

$[V_{SS} = RTN \text{ and } V_{DD} = V_{DD1}] \text{ or } [V_{SS} = RTN = V_{DD}], \text{ all voltages referred to } [ARTN, COM]$

|                    | PARAMETER                                  | TEST CONDITIONS                                                                                                      | MIN  | TYP  | MAX  | UNIT |

|--------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>C</sub>     |                                            |                                                                                                                      |      |      |      |      |

| .,                 |                                            | V <sub>C</sub> rising '754                                                                                           | 14.3 | 15   | 15.7 |      |

| V <sub>CUV</sub>   | 100                                        | V <sub>C</sub> rising '756                                                                                           | 8.7  | 9    | 9.3  | .,   |

| .,                 | UVLO                                       | Hysteresis '754 (1)                                                                                                  | 6.2  | 6.5  | 6.8  | V    |

| V <sub>CUVH</sub>  |                                            | Hysteresis '756 (1)                                                                                                  | 3.3  | 3.5  | 3.7  | İ    |

|                    | Operating current                          | $V_C = 12 \text{ V, CTL} = V_B, R_{DT} = 68.1 \text{ k}\Omega$                                                       | 0.7  | 0.92 | 1.2  | mA   |

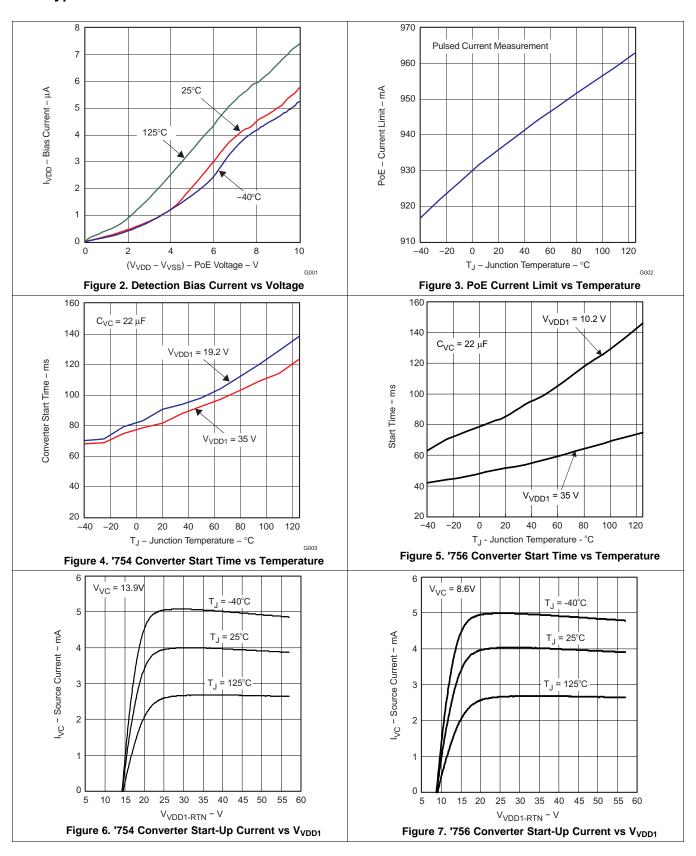

|                    |                                            | TPS23756, V <sub>DD1</sub> = 10.2 V, V <sub>C</sub> (0) = 0 V                                                        | 50   | 85   | 175  |      |

|                    | Bootstrap start-up time,                   | TPS23756, V <sub>DD1</sub> = 35 V, V <sub>C</sub> (0) = 0 V                                                          | 27   | 45   | 92   |      |

| t <sub>ST</sub>    | C <sub>VC</sub> = 22 μF                    | TPS23754, V <sub>DD1</sub> = 19.2 V, V <sub>C</sub> (0) = 0 V                                                        | 49   | 81   | 166  | ms   |

|                    |                                            | TPS23754, V <sub>DD1</sub> = 35 V, V <sub>C</sub> (0) = 0 V                                                          | 44   | 75   | 158  | İ    |

|                    |                                            | TPS23754, V <sub>DD1</sub> = 19.2 V, V <sub>C</sub> = 13.9 V                                                         | 1.7  | 3.4  | 5.5  |      |

|                    | Start-up current source is I <sub>VC</sub> | TPS23756, V <sub>DD1</sub> = 10.2 V, V <sub>C</sub> = 8.6 V                                                          | 0.44 | 1.06 | 1.8  | mA   |

|                    |                                            | TPS23754, TPS23756, V <sub>DD1</sub> = 48 V, V <sub>C</sub> = 0 V                                                    | 2.7  | 4.8  | 6.8  | İ    |

| V <sub>B</sub>     |                                            |                                                                                                                      |      |      |      |      |

|                    | Voltage                                    | $6.5 \text{ V} \le \text{V}_{\text{C}} \le 18 \text{ V}, \ 0 \le \text{I}_{\text{VB}} \le 5 \text{ mA}$              | 4.8  | 5.1  | 5.25 | V    |

| FRS                |                                            |                                                                                                                      |      |      |      |      |

|                    | 0 :: 1: (                                  | CTL = V <sub>B</sub> , measure GATE                                                                                  |      |      |      |      |

|                    | Switching frequency                        | $R_{FRS} = 68.1 \text{ k}\Omega$                                                                                     | 227  | 253  | 278  | kHz  |

| D <sub>MAX</sub>   | Duty cycle                                 | CTL= V <sub>B</sub> , measure GATE                                                                                   | 76%  | 78%  | 80%  |      |

| V <sub>SYNC</sub>  | Synchronization                            | Input threshold                                                                                                      | 2    | 2.2  | 2.4  | V    |

| CTL                |                                            |                                                                                                                      | *    |      |      |      |

| $V_{ZDC}$          | 0% duty cycle threshold                    | V <sub>CTL</sub> ↓ until GATE stops                                                                                  | 1.3  | 1.5  | 1.7  | V    |

|                    | Input resistance                           |                                                                                                                      | 70   | 100  | 145  | kΩ   |

| CS                 |                                            |                                                                                                                      |      |      |      |      |

| V <sub>CSMAX</sub> | Maximum threshold voltage                  | V <sub>CTL</sub> = V <sub>B</sub> , V <sub>CS</sub> rising until GATE duty cycle drops                               | 0.5  | 0.55 | 0.6  | V    |

| V <sub>SLOPE</sub> | Internal slope compensation voltage        | Peak voltage at maximum duty cycle, referenced to CS                                                                 | 120  | 155  | 185  | mV   |

| I <sub>SL_EX</sub> | Peak slope compensation current            | V <sub>CTL</sub> = V <sub>B</sub> , I <sub>CS</sub> at maximum duty cycle                                            | 30   | 42   | 54   | μΑ   |

|                    | Bias current (sourcing)                    | DC component of I <sub>CS</sub>                                                                                      | 1    | 2.5  | 4.3  | μΑ   |

| GATE               |                                            |                                                                                                                      |      |      |      |      |

|                    | Source current                             | V <sub>CTL</sub> = V <sub>B</sub> , V <sub>C</sub> = 12 V, GATE high, pulsed measurement                             | 0.37 | 0.6  | 0.95 | Α    |

|                    | Sink current                               | V <sub>CTL</sub> = V <sub>B</sub> , V <sub>C</sub> = 12 V, GATE low, pulsed measurement                              | 0.7  | 1    | 1.4  | Α    |

| GAT2               |                                            |                                                                                                                      |      |      |      |      |

|                    | Source current                             | $V_{CTL}$ = $V_{B}$ , $V_{C}$ = 12 V, GAT2 high, $R_{DT}$ = 24.9 kΩ, pulsed measurement                              | 0.37 | 0.6  | 0.95 | Α    |

|                    | Sink current                               | $V_{CTL} = V_{B}, V_{C} = 12 \text{ V}, \text{ GAT2 low}, R_{DT} = 24.9 \text{ k}\Omega, \text{ pulsed}$ measurement | 0.7  | 1    | 1.4  | Α    |

<sup>(1)</sup> The hysteresis tolerance tracks the rising threshold for a given device.

# **Electrical Characteristics (continued)**

Unless otherwise noted: CS = COM = APD = CTL = RTN = ARTN, GATE and GAT2 float,  $R_{FRS}$ = 68.1 k $\Omega$ ,  $R_{BLNK}$ = 249 k $\Omega$ , DT =  $V_B$ , PPD =  $V_{SS}$ , T2P open,  $C_{VB}$  =  $C_{VC}$  = 0.1  $\mu$ F,  $R_{DEN}$  = 24.9 k $\Omega$ ,  $R_{CLS}$  open, 0 V ≤ ( $V_{DD}$ ,  $V_{DD1}$ ) ≤ 57 V, 0 V ≤  $V_C$  ≤ 18 V,  $-40^{\circ}$ C ≤  $T_J$  ≤ 125°C. Typical specifications are at 25°C.

### **CONTROLLER SECTION ONLY**

$[V_{SS} = RTN \text{ and } V_{DD} = V_{DD1}] \text{ or } [V_{SS} = RTN = V_{DD}], \text{ all voltages referred to } [ARTN, COM]$

|                    | PARAMETER                            | TEST CONDITIONS                                          | MIN  | TYP  | MAX  | UNIT |

|--------------------|--------------------------------------|----------------------------------------------------------|------|------|------|------|

| APD / PF           | PD                                   |                                                          |      |      |      |      |

| V <sub>APDEN</sub> | ADD throughold valte as              | V <sub>APD</sub> rising                                  | 1.43 | 1.5  | 1.57 | V    |

| V <sub>APDH</sub>  | APD threshold voltage                | Hysteresis <sup>(1)</sup>                                | 0.29 | 0.31 | 0.33 | V    |

| V <sub>PPDEN</sub> | PPD threshold voltage                | V <sub>PPD</sub> - V <sub>VSS</sub> rising, UVLO disable | 1.45 | 1.55 | 1.65 | V    |

| V <sub>PPDH</sub>  |                                      | Hysteresis <sup>(1)</sup>                                | 0.29 | 0.31 | 0.33 | V    |

| V <sub>PPD2</sub>  |                                      | V <sub>PPD</sub> - V <sub>VSS</sub> rising, Class enable | 7.4  | 8.3  | 9.2  | V    |

| V <sub>PPD2H</sub> |                                      | Hysteresis <sup>(1)</sup>                                | 0.5  | 0.6  | 0.7  | V    |

|                    | APD leakage current (source or sink) | $V_C = 12 \text{ V}, V_{APD} = V_B$                      |      |      | 1    | μΑ   |

| I <sub>PPD</sub>   | PPD sink current                     | $V_{PPD-VSS} = 1.5 \text{ V}$                            | 2.5  | 5    | 7.5  | μА   |

| THERMA             | AL SHUTDOWN                          |                                                          |      |      |      |      |

|                    | turnon temperature                   | T <sub>J</sub> rising                                    | 135  | 145  | 155  | °C   |

|                    | Hysteresis <sup>(2)</sup>            |                                                          |      | 20   |      | °C   |

<sup>(2)</sup> These parameters are provided for reference only, and do not constitute part of TI's published specifications for purposes of TI's product warranty.

# 6.6 Electrical Characteristics: PoE and Control

[V<sub>DD</sub> = V<sub>DD1</sub>] or [V<sub>DD1</sub> = RTN], V<sub>C</sub> = RTN, COM = RTN = ARTN, all voltages referred to V<sub>SS</sub> unless otherwise noted

|                     | PARAMETER                                      | TEST CONDITIONS                                                                                     | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| DETECTION (DEN)     |                                                | (VDD = VDD1 = RTN = V <sub>SUPPLY</sub> positive)                                                   |      |      |      |      |

|                     |                                                | Measure I <sub>SUPPLY</sub>                                                                         |      |      |      |      |

|                     | Detection current                              | V <sub>DD</sub> = 1.6 V                                                                             | 62   | 64.3 | 66.5 | ^    |

|                     |                                                | V <sub>DD</sub> = 10 V                                                                              | 399  | 406  | 414  | μΑ   |

|                     | Detection bias current                         | V <sub>DD</sub> = 10 V, float DEN, measure I <sub>SUPPLY</sub> , <b>Note:</b> Not during Mark state |      | 5.6  | 10   | μΑ   |

| $V_{PD\_DIS}$       | Hotswap disable threshold                      |                                                                                                     | 3    | 4    | 5    | V    |

|                     | DEN leakage current                            | $V_{DEN} = V_{DD} = 57 \text{ V}$ , float $V_{DD1}$ and RTN, measure $I_{DEN}$                      |      | 0.1  | 5    | μΑ   |

| CLASSIF             | FICATION (CLS)                                 | $(V_{DD} = V_{DD1} = RTN = V_{SUPPLY} positive)$                                                    | •    |      |      |      |

|                     | Classification current, applies to both cycles | 13 V ≤ V <sub>DD</sub> ≤ 21 V, Measure I <sub>SUPPLY</sub>                                          |      |      |      | mA   |

|                     |                                                | $R_{CLS} = 1270 \Omega$                                                                             | 1.8  | 2.1  | 2.4  |      |

|                     |                                                | $R_{CLS} = 243 \Omega$                                                                              | 9.9  | 10.4 | 10.9 |      |

| I <sub>CLS</sub>    |                                                | $R_{CLS} = 137 \Omega$                                                                              | 17.6 | 18.5 | 19.4 |      |

|                     |                                                | $R_{CLS} = 90.9 \Omega$                                                                             | 26.5 | 27.7 | 29.3 |      |

|                     |                                                | $R_{CLS} = 63.4 \Omega$                                                                             | 38   | 39.7 | 42   |      |

|                     | Classification mark resistance                 | 5.6 V ≤ V <sub>DD</sub> ≤ 9.4 V                                                                     | 7.5  | 9.7  | 12   | kΩ   |

| V <sub>CL_ON</sub>  | Classification regulator lower                 | Regulator turns on, V <sub>DD</sub> rising                                                          | 11.2 | 11.9 | 12.6 | V    |

| V <sub>CL_H</sub>   | the search of the                              | Hysteresis <sup>(1)</sup>                                                                           | 1.55 | 1.65 | 1.75 | V    |

| V <sub>CU_OFF</sub> | _OFF Classification regulator upper            | Regulator turns off, V <sub>DD</sub> rising                                                         | 21   | 22   | 23   | V    |

| V <sub>CU_H</sub>   |                                                | Hysteresis <sup>(1)</sup>                                                                           | 0.5  | 0.75 | 1    | V    |

| V <sub>MSR</sub>    | Mark state reset                               | V <sub>DD</sub> falling                                                                             | 3    | 4    | 5    | V    |

|                     | Leakage current                                | $V_{DD}$ = 57 V, $V_{CLS}$ = 0 V, DEN = $V_{SS}$ , measure $I_{CLS}$                                |      |      | 1    | μΑ   |

<sup>(1)</sup> The hysteresis tolerance tracks the rising threshold for a given device.

# **Electrical Characteristics: PoE and Control (continued)**

$[V_{DD} = V_{DD1}]$  or  $[V_{DD1} = RTN]$ ,  $V_C = RTN$ , COM = RTN = ARTN, all voltages referred to  $V_{SS}$  unless otherwise noted

| PARAMETER                          | TEST CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT |  |  |  |

|------------------------------------|--------------------------------------------------------------------------|------|------|------|------|--|--|--|

| PASS DEVICE (RTN)                  | $(V_{DD1} = RTN)$                                                        |      |      |      |      |  |  |  |

| On resistance                      |                                                                          | 0.25 | 0.43 | 0.75 | Ω    |  |  |  |

| Current limit                      | V <sub>RTN</sub> = 1.5 V, V <sub>DD</sub> = 48 V, pulsed measurement     |      | 970  | 1100 | mA   |  |  |  |

| Inrush limit                       | V <sub>RTN</sub> = 2 V, V <sub>DD</sub> : 0 V → 48 V, pulsed measurement |      | 140  | 180  | mA   |  |  |  |

| Foldback voltage threshold         | V <sub>DD</sub> rising                                                   | 11   | 12.3 | 13.6 | V    |  |  |  |

| UVLO                               |                                                                          |      |      |      |      |  |  |  |

| V <sub>UVLO_R</sub> UVLO threshold | V <sub>DD</sub> rising                                                   | 33.9 | 35   | 36.1 | V    |  |  |  |

| V <sub>UVLO_H</sub>                | Hysteresis <sup>(1)</sup>                                                | 4.4  | 4.55 | 4.76 | V    |  |  |  |

| T2P                                |                                                                          |      |      |      |      |  |  |  |

| ON characteristic                  | Perform classification algorithm, V <sub>T2P-RTN</sub> = 1 V, CTL = ARTN | 2    |      |      | mA   |  |  |  |

| Leakage current                    | $V_{T2P} = 18 \text{ V, CTL} = V_{B}$                                    |      |      | 10   | μΑ   |  |  |  |

| THERMAL SHUTDOWN                   |                                                                          |      |      |      |      |  |  |  |

| Turnoff temperature                | T <sub>J</sub> rising                                                    | 135  | 145  | 155  | °C   |  |  |  |

| Hysteresis (2)                     |                                                                          |      | 20   |      | °C   |  |  |  |

<sup>(2)</sup> These parameters are provided for reference only, and do not constitute part of TI's published specifications for purposes of TI's product warranty.

# 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER        |                                              | TEST CONDITIONS                                                                                                                                                                            | MIN | TYP | MAX  | UNIT |  |

|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|

| CTL              |                                              |                                                                                                                                                                                            |     |     |      |      |  |

|                  | Soft-start period                            | Interval from switching start to V <sub>CSMAX</sub>                                                                                                                                        | 1.9 | 3.9 | 6.2  | ms   |  |

| BLNK             |                                              |                                                                                                                                                                                            |     |     |      |      |  |

|                  | Blanking delay                               | BLNK = RTN                                                                                                                                                                                 | 35  | 55  | 78   |      |  |

|                  | (In addition to t <sub>1</sub> )             | $R_{BLNK} = 49.9 \text{ k}\Omega$                                                                                                                                                          | 38  | 55  | 70   | ns   |  |

| DT               |                                              |                                                                                                                                                                                            |     |     |      |      |  |

|                  |                                              | $\begin{aligned} \text{CTL} &= \text{V}_{\text{B}},  \text{C}_{\text{GATE}} = 1  \text{nF}, \\ \text{C}_{\text{GAT2}} &= 1  \text{nF},  \text{measure GATE}, \\ \text{GAT2} \end{aligned}$ |     |     |      |      |  |

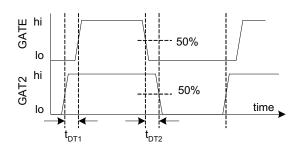

| t <sub>DT1</sub> | Dead time                                    | $R_{DT}$ = 24.9 k $\Omega$ , GAT2 $\uparrow$ to GATE $\uparrow$                                                                                                                            | 40  | 50  | 62.5 | ns   |  |

| t <sub>DT2</sub> | See Figure 1 for t <sub>DTx</sub> definition | $R_{DT}$ = 24.9 k $\Omega$ , GATE $\downarrow$ to GAT2 $\downarrow$                                                                                                                        | 40  | 50  | 62.5 | 110  |  |

| t <sub>DT1</sub> |                                              | $R_{DT}$ = 75 kΩ, GAT2 ↑ to GATE ↑                                                                                                                                                         | 120 | 150 | 188  |      |  |

| t <sub>DT2</sub> |                                              | $R_{DT} = 75 \text{ k}\Omega, \text{ GATE } \downarrow \text{ to GAT2 } \downarrow$                                                                                                        | 120 | 150 | 188  |      |  |

| CS               |                                              |                                                                                                                                                                                            |     |     |      |      |  |

| t <sub>1</sub>   | Turnoff delay                                | V <sub>CS</sub> = 0.65 V                                                                                                                                                                   | 24  | 40  | 70   | ns   |  |

| PoE AN           | ID CONTROL - T2P                             |                                                                                                                                                                                            |     |     |      |      |  |

| t <sub>T2P</sub> | Delay                                        | From start of switching to T2P active                                                                                                                                                      | 5   | 9   | 15   | ms   |  |

Figure 1. GATE and GAT2 Timing and Phasing

# TEXAS INSTRUMENTS

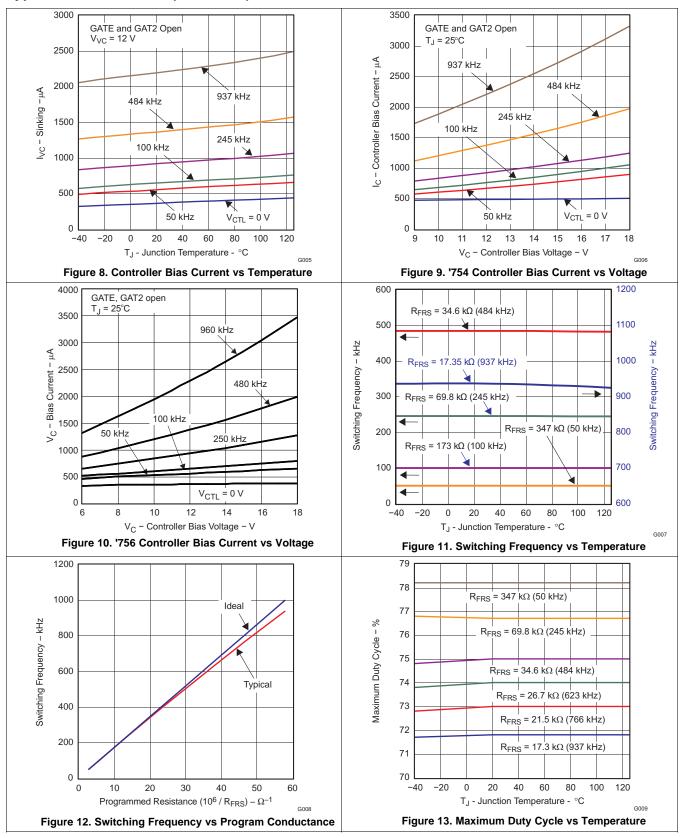

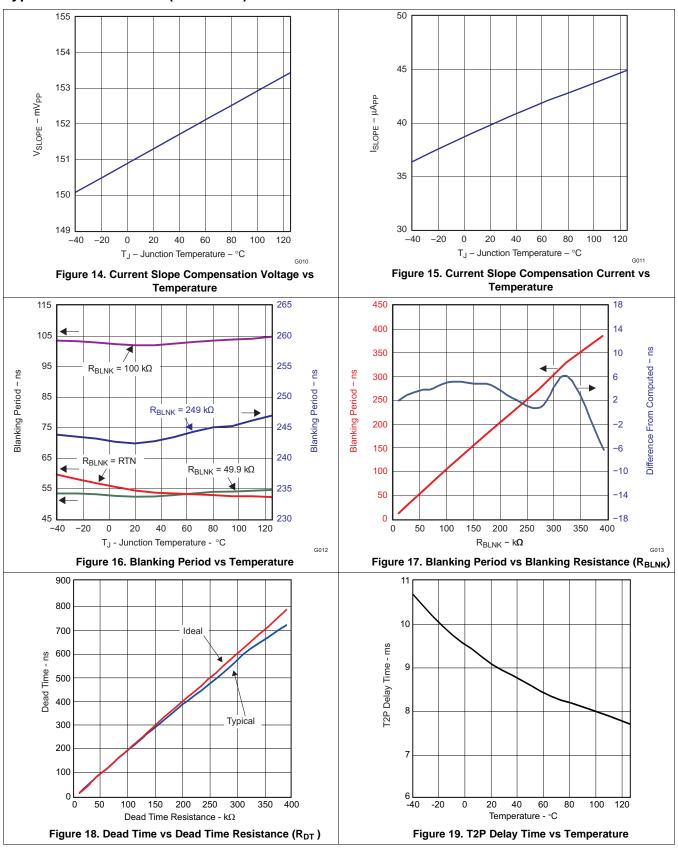

# 6.8 Typical Characteristics

# **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

# 7 Detailed Description

### 7.1 Overview

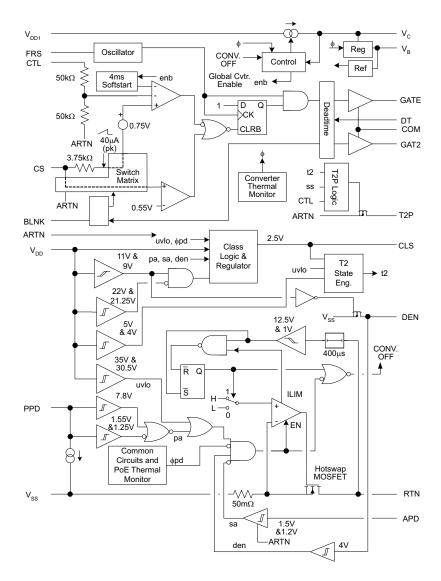

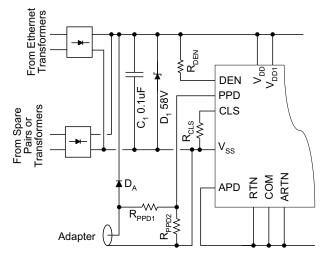

The TPS23754 and TPS23756 devices have a PoE that contains all of the features needed to implement an IEEE802.3at type-2 powered device (PD) such as Detection, Classification, Type 2 Hardware Classification, and 140-mA inrush current limit during start-up. It combines a current mode DC-DC controller optimized specifically for isolated converters.

The TPS23754 and TPS23756 devices integrate a low  $0.5-\Omega$  internal switch to allow for up to 0.85 A of continuous current through the PD during normal operation.

The TPS23754 and TPS23756 devices contain several protection features such as thermal shutdown, current limit foldback, and a robust 100-V internal switch.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

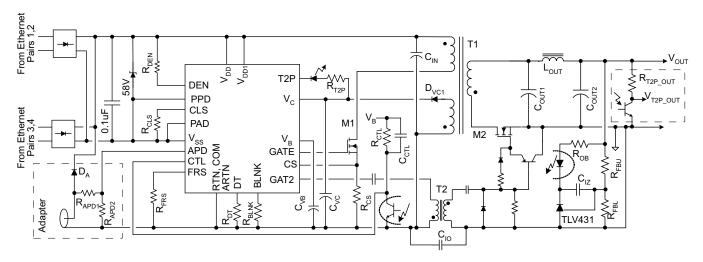

See Figure 27 for component reference designators (R<sub>CS</sub> for example), and the *Electrical Characteristics* for values denoted by reference (V<sub>CSMAX</sub> for example). Electrical characteristic values take precedence over any numerical values used in the following sections.

# **Feature Description (continued)**

### 7.3.1 APD

APD forces power to come from an external adapter connected from V<sub>DD1</sub> to RTN by opening the hotswap switch, disabling the CLS output (see PPD pin description), and enabling the T2P output. TI recommends a resistor divider on APD when it is connected to an external adapter. The divider provides ESD protection, leakage discharge for the adapter ORing diode, and input voltage qualification. Voltage qualification assures the adapter output voltage is high enough that it can support the PD before the PoE current is cut off.

Select the APD divider resistors per Equation 1 where  $V_{ADPTR-ON}$  is the desired adapter voltage that enables the APD function as adapter voltage rises.

$$R_{APD1} = R_{APD2} \times (V_{ADPTR\_ON} - V_{APDEN})/V_{APDEN}$$

$$V_{ADPTR\_OFF} = \frac{R_{APD1} + R_{APD2}}{R_{APD2}} \times (V_{APDEN} - V_{APDH})$$

(1)

Place the APD pulldown resistor adjacent to the APD pin.

APD should be tied to ARTN when not used.

### 7.3.2 BLNK

Blanking provides an interval between GATE going high and the current-control comparators on CS actively monitoring the input. This delay allows the normal turnon current transient (spike) to subside before the comparators are active, preventing undesired short duty cycles and premature current limiting.

Connect BLNK to ARTN to obtain the internally set blanking period. Connect a resistor from BLNK to ARTN for a more accurate, programmable blanking period. The relationship between the desired blanking period and the programming resistor is defined by Equation 2.

$$R_{BLNK}(k\Omega) = t_{BLNK}(ns)$$

(2)

Place the resistor adjacent to the BLNK pin when it is used.

### 7.3.3 CLS

A resistor from CLS to V<sub>SS</sub> programs the classification current per the IEEE standard. The PD power ranges and corresponding resistor values are listed in Table 1. The power assigned should correspond to the maximum average power drawn by the PD during operation.

High-power PSEs may perform two classification cycles if Class 4 is presented on the first cycle. The TPS23754 device presents the same (resistor programmed) class each cycle per the standard.

**Table 1. Class Resistor Selection**

| CLASS | POWER AT PD    |                | DECICTOR        |                                                                                                    |  |  |

|-------|----------------|----------------|-----------------|----------------------------------------------------------------------------------------------------|--|--|

|       | MINIMUM<br>(W) | MAXIMUM<br>(W) | RESISTOR<br>(Ω) | NOTES                                                                                              |  |  |

| 0     | 0.44           | 13             | 1270            | Minimum may be reduced by pulsed loading. Serves as a catch-all default class.                     |  |  |

| 1     | 0.44           | 3.84           | 243             |                                                                                                    |  |  |

| 2     | 3.84           | 6.49           | 137             |                                                                                                    |  |  |

| 3     | 6.49           | 13             | 90.9            |                                                                                                    |  |  |

| 4     | 13             | 25.5           | 63.4            | Not allowed before IEEE 802.3at. Use to indicate a Type 2 PD (high power) device per IEEE 802.3at. |  |  |

### 7.3.4 Current Sense (CS)

The CS input for the DC-DC converter should be connected to the high side of the switching MOSFET's current sense resistor ( $R_{CS}$ ). The current limit threshold,  $V_{CSMAX}$ , defines the voltage on CS above which the GATE ON time will be terminated regardless of the voltage on CTL.

The TPS23754 device provides internal slope compensation (150 mV, V<sub>SLOPE</sub>), an output current for additional slope compensation, a peak current limiter, and an off-time pulldown to this pin.

Routing between the current-sense resistor and the CS pin should be short to minimize cross-talk from noisy traces such as the gate drive signal.

### 7.3.5 Control (CTL)

CTL is the voltage-control loop input to the pulse-width modulator (PWM). Pulling  $V_{CTL}$  below  $V_{ZDC}$  causes GATE to stop switching. Increasing  $V_{CTL}$  above  $V_{ZDC}$  (0 duty cycle voltage) raises the switching MOSFET programmed peak current. The maximum (peak) current is requested at approximately  $V_{ZDC}$  + (2 ×  $V_{CSMAX}$ ). The AC gain from CTL to the PWM comparator is 0.5. The internal divider from CTL to ARTN is approximately 100 k $\Omega$ .

Use V<sub>B</sub> as a pullup source for CTL.

### 7.3.6 Detection and Enable (DEN)

DEN is a multifunction pin for PoE detection and inhibiting operation from PoE power. Connect a 24.9-k $\Omega$  resistor from DEN to V<sub>DD</sub> to provide the PoE detection signature. DEN goes to a high-impedance state when V<sub>VDD-VSS</sub> is outside of the detection range. Pulling DEN to V<sub>SS</sub> during powered operation causes the internal hotswap MOSFET and class regulator to turn off, while the reduced detection resistance prevents the PD from properly redetecting.

### 7.3.7 DT

Dead-time programming sets the delay between GATE and GAT2 to prevent overlap of MOSFET ON times as shown in Figure 1. GAT2 turns the second MOSFET off when it transitions high. Both MOSFETs should be off between GAT2 going high to GATE going high, and GATE going low to GAT2 going low. The maximum GATE ON time is reduced by the programmed dead-time period. The dead time period is specified with 1 nF of capacitance on GATE and GAT2. Different loading on these pins changes the effective dead time.

A resistor connected from DT to ARTN sets the delay between GATE and GAT2 per Equation 3.

$$R_{DT}(k\Omega) = \frac{t_{DT}(ns)}{2}$$

(3)

Connect DT to V<sub>B</sub> to set the dead time to 0 and turn GAT2 off.

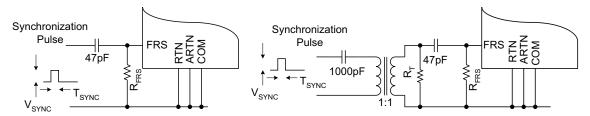

### 7.3.8 Frequency and Synchronization (FRS)

Connect a resistor from FRS to ARTN to program the converter switching frequency. Select the resistor per the following relationship.

$$R_{FRS}(k\Omega) = \frac{17250}{f_{SW}(kHz)}$$

(4)

The converter may be synchronized to a frequency above its maximum free-running frequency by applying short AC-coupled pulses into the FRS pin per Figure 30.

The FRS pin is high impedance. Keep the connections short and apart from potential noise sources. Take special care to avoid crosstalk when synchronizing circuits are used.

### 7.3.9 GATE

Gate drive output for the DC-DC converter's main switching MOSFET. GATE's phase turns the main switch on when it transitions high, and off when it transitions low. GATE is held low when the converter is disabled.

### 7.3.10 GAT2

GAT2 is the second gate drive output for the DC-DC converter. GAT2's phase turns the second switch off when it transitions high, and on when it transitions low. This drives active-clamp PMOS devices per Figure 27, and driven flyback synchronous rectifiers per Figure 27. See the DT pin description for GATE to GAT2 timing. Connecting DT to  $V_B$  disables GAT2 in a high-impedance condition. GAT2 is low when the converter is disabled.

### 7.3.11 PPD

PPD is a multifunction pin that has two voltage thresholds, PPD1 and PPD2.

PPD1 permits power to come from an external low voltage adapter, that is, 24 V, connected from  $V_{DD}$  to  $V_{SS}$  by overriding the normal hotswap UVLO. Voltage on PPD more than 1.55 V ( $V_{PPDEN}$ ) enables the hotswap MOSFET, inhibits class current, and enables T2P. A resistor divider per Figure 34 provides ESD protection, leakage discharge for the adapter ORing diode, reverse adapter protection, and input voltage qualification. Voltage qualification assures the adapter output voltage is high enough that it can support the PD before it begins to draw current.

$$R_{PPD1} = \left( \frac{V_{ADPTR\_ON} - V_{PPDEN}}{\frac{V_{PPDEN}}{R_{PPD2}} + I_{PPD}} \right)$$

$$V_{ADPTR\_OFF} = \left(V_{PPDEN} - V_{PPDH}\right) + \left[R_{PPD1} \times \left(\frac{\left(V_{PPDEN} - V_{PPDH}\right)}{R_{PPD2}} + I_{PPD}\right)\right]$$

(5)

PPD2 enables normal class regulator operation when  $V_{PPD}$  is more than 8.3 V to permit type 2 classification when APD is used in conjunction with diode  $D_{VDD}$  (see Figure 33). Tie PPD to  $V_{DD}$  when PPD2 operation is desired.

The PPD pin has a 5-μA internal pulldown current.

Locate the PPD pulldown resistor adjacent to the pin when used.

PPD may be tied to V<sub>SS</sub> or left open when not used.

### 7.3.12 RTN, ARTN, COM

RTN is internally connected to the drain of the PoE hotswap MOSFET, while ARTN is the quiet analog reference for the DC-DC controller return. COM serves as the return path for the gate drivers and should be tied to ARTN on the circuit board. The ARTN / COM / RTN net should be treated as a local reference plane (ground plane) for the DC-DC control and converter primary. RTN and (ARTN/COM) may be separated by several volts for special applications.

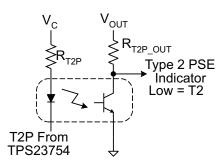

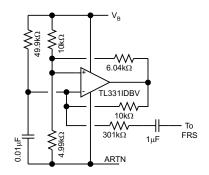

### 7.3.13 T2P

T2P is an active low output that indicates [  $(V_{APD} > 1.5 \text{ V})$  OR (1.55 V  $\leq V_{PPD} \leq 8.3 \text{ V})$  OR (type 2 hardware classification observed) ]. T2P is valid after both a delay of  $t_{T2P}$  from the start of converter switching, and [ $V_{CTL} \leq (V_B - 1 \text{ V})$ ]. Once T2P is valid,  $V_{CTL}$  does not affect it. T2P becomes invalid if the converter goes back into soft start, overtemperature, or is held off by the PD during  $C_{IN}$  recharge (inrush). T2P is referenced to ARTN and is intended to drive the diode side of an optocoupler. T2P should be left open or tied to ARTN if not used.

### 7.3.14 V<sub>B</sub>

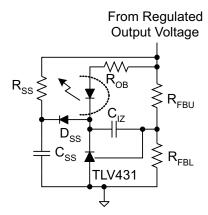

$V_B$  is an internal 5.1-V regulated DC-DC controller supply rail that is typically bypassed by a 0.1- $\mu$ F capacitor to ARTN.  $V_B$  should be used to bias the feedback optocoupler.

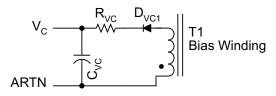

### 7.3.15 V<sub>C</sub>

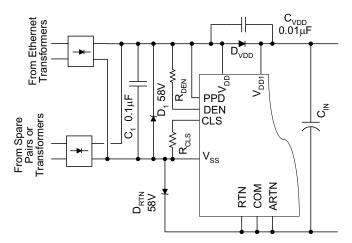

$V_C$  is the bias supply for the DC-DC controller. The MOSFET gate drivers run directly from  $V_C$ .  $V_B$  is regulated down from  $V_C$ , and is the bias voltage for the rest of the converter control. A start-up current source from  $V_{DD1}$  to  $V_C$  is controlled by a comparator with hysteresis to implement the converter bootstrap start-up.  $V_C$  must be connected to a bias source, such as a converter auxiliary output, during normal operation.

A minimum 0.47  $\mu$ F-capacitor, located adjacent to the V<sub>C</sub> pin, should be connected from V<sub>C</sub> to COM to bypass the gate driver. A larger total capacitance is required for start-up to provide control power between the time the converter starts switching and the availability of the converter auxiliary output voltage.

### $7.3.16 V_{DD}$

$V_{DD}$  is the positive input power rail that is derived from the PoE source (PSE).  $V_{DD}$  should be bypassed to  $V_{SS}$  with a 0.1- $\mu$ F capacitor as required by the IEEE standard. A transient suppressor diode (TVS), a special type of Zener diode, such as SMAJ58A should be connected from  $V_{DD}$  to  $V_{SS}$  to protect against overvoltage transients.

### 7.3.17 V<sub>DD1</sub>

$V_{DD1}$  is the DC-DC converter start-up supply. Connect to  $V_{DD}$  for many applications.  $V_{DD1}$  may be isolated by a diode from  $V_{DD}$  to support PoE priority operation.

### 7.3.18 V<sub>SS</sub>

V<sub>SS</sub> is the PoE input-power return side. It is the reference for the PoE interface circuits and has a current limited hotswap switch that connects it to RTN. V<sub>SS</sub> is clamped to a diode drop above RTN by the hotswap switch.

A local  $V_{SS}$  reference plane should be used to connect the input bypass capacitor, TVS,  $R_{CLS}$ , and the PowerPAD. This plane becomes the main heatsink for the TPS23754.

V<sub>SS</sub> is internally connected to the PowerPAD.

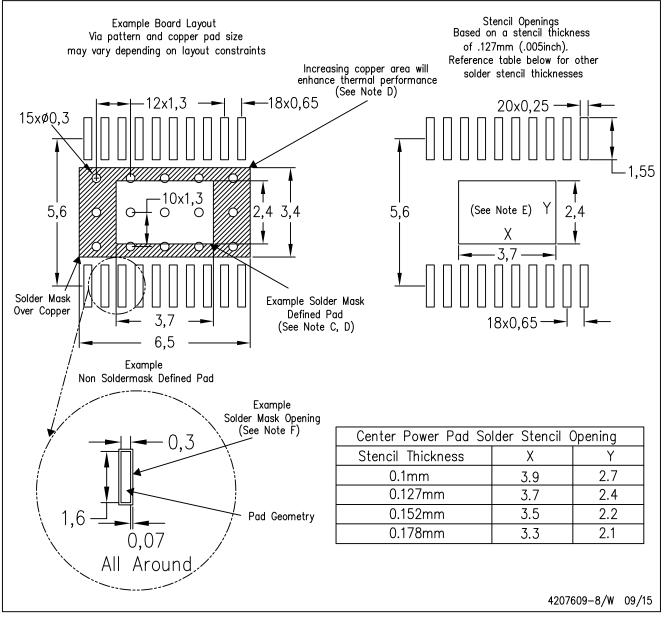

### 7.3.19 PowerPAD

The PowerPAD is internally connected to  $V_{SS}$ . It should be tied to a large  $V_{SS}$  copper area on the PCB to provide a low-resistance thermal path to the circuit board. TI recommends that a clearance of 0.025" be maintained between  $V_{SS}$ , RTN, and various control signals to high-voltage signals such as  $V_{DD}$  and  $V_{DD1}$ .

### 7.4 Device Functional Modes

The following text is intended as an aid in understanding the operation of the TPS23754, but not as a substitute for the IEEE 802.3at standard. The IEEE 802.3at standard is an update to IEEE 802.3-2008 clause 33 (PoE), adding high-power options and enhanced classification. Generally speaking, a device compliant to IEEE 802.3-2008 is referred to as a type 1 device, and devices with high power and enhanced classification are referred to as type 2 devices. Standards change and should always be referenced when making design decisions.

### 7.4.1 PoE Overview

The IEEE 802.3at standard defines a method of safely powering a PD over a cable by power sourcing equipment (PSE), and then removing power if a PD is disconnected. The process proceeds through an idle state and three operational states of detection, classification, and operation. The PSE leaves the cable unpowered (idle state) while it periodically looks to see if something has been plugged in; this is referred to as detection. The low-power levels used during detection are unlikely to damage devices not designed for PoE. If a valid PD signature is present, the PSE my inquire how much power the PD requires; this is referred to as classification. The PSE may then power the PD if it has adequate capacity.

Type 2 PSEs are required to do type 1 hardware classification, plus a (new) data-layer classification, or an enhanced type 2 hardware classification. Type 1 PSEs are not required to do hardware or data link layer (DLL) classification. A type 2 PD must do type 2 hardware classification as well as DLL classification. The PD may return the default, 13W current-encoded class, or one of four other choices. DLL classification occurs after power-on and the ethernet data link has been established.

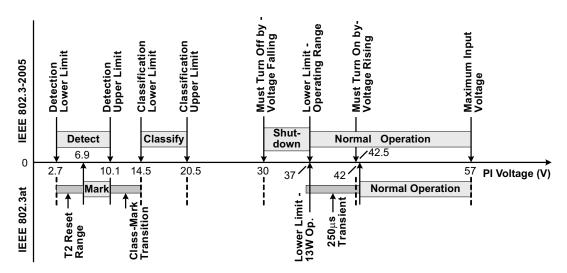

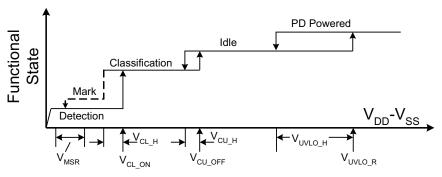

Once started, the PD must present the maintain power signature (MPS) to assure the PSE that it is still present. The PSE monitors its output for a valid MPS, and turns the port off if it loses the MPS. Loss of the MPS returns the PSE to the idle state. Figure 20 shows the operational states as a function of PD input voltage. The upper half is for IEEE 802.3-2008, and the lower half shows specific differences for IEEE 802.3at. The dashed lines in the lower half indicate these are the same (for example, Detect and Class) for both.

# **Device Functional Modes (continued)**

Figure 20. Operational States for PD

The PD input, typically an RJ-45 eight-lead connector, is referred to as the power interface (PI). PD input requirements differ from PSE output requirements to account for voltage drops and operating margin. The standard allots the maximum loss to the cable regardless of the actual installation to simplify implementation. IEEE 802.3-2008 was designed to run over infrastructure including ISO/IEC 11801 class C (CAT3 per TIA/EIA-568) that may have had AWG 26 conductors. IEEE 802.3at type 2 cabling power loss allotments and voltage drops have been adjusted for 12.5- $\Omega$  power loops per ISO/IEC11801 class D (CAT5 or higher per TIA/EIA-568, typically AWG number 24 conductors). Table 2 shows key operational limits broken out for the two revisions of the standard.

**POWER LOOP PSE PSE STATIC** PD INPUT STATIC PD INPUT VOLTAGE RESISTANCE OUTPUT POWER **OUTPUT VOLTAGE POWER STANDARD** POWER > POWER ≤ (max) (min) (min) (max) 13 W 13 W IEEE 802.3-2008 20 Ω 15.4 W 44 V 13 W 37 - 57 VN/A 802.3at (Type 1) 802.3at (Type 2) 12.5 Ω 30 W 50 V 25.5 W 37 - 57 V 42.5 - 57 V

**Table 2. Comparison of Operational Limits**

The PSE can apply voltage either between the RX and TX pairs (pins 1 to 2 and 3 to 6 for 10baseT or 100baseT), or between the two spare pairs (4 to 5 and 7 to 8). Power application to the same pin combinations in 1000baseT systems is recognized in IEEE 802.3at. 1000baseT systems can handle data on all pairs, eliminating the spare pair terminology. The PSE may only apply voltage to one set of pairs at a time. The PD uses input diode bridges to accept power from any of the possible PSE configurations. The voltage drops associated with the input bridges create a difference between the standard limits at the PI and the TPS23754 specifications.

A compliant type 2 PD has power management requirements not present with a type 1 PD. These requirements include the following:

- 1. Must interpret type 2 hardware classification

- Must present hardware class 4

- 3. Must implement DLL negotiation

- 4. Must behave like a type 1 PD during inrush and start-up

- 5. Must not draw more than 13 W for 80 ms after PSE applies operating voltage (power up)

- 6. Must not draw more than 13 W if it has not received a type 2 hardware classification or received permission through DLL

- 7. Must meet various operating and transient templates

### 8. Optionally monitor for the presence or absence of an adapter (assume high power)

As a result of these requirements, the PD must be able to dynamically control its loading and monitor T2P for changes. In cases where the design must know specifically if an adapter is plugged in and operational, the adapter should be individually monitored, typically with an optocoupler.

### 7.4.1.1 Threshold Voltages

The TPS23754 has a number of internal comparators with hysteresis for stable switching between the various states. Figure 21 relates the parameters in the *Electrical Characteristics* to the PoE states. The mode labeled idle between classification and operation implies that the DEN, CLS, and RTN pins are all high impedance. The state labeled Mark, which is drawn in dashed lines, is part of the new type 2 hardware class state machine.

Note: Variable names refer to Electrical Characteristic Table parameters

Figure 21. Threshold Voltages

### 7.4.1.2 PoE Start-Up Sequence

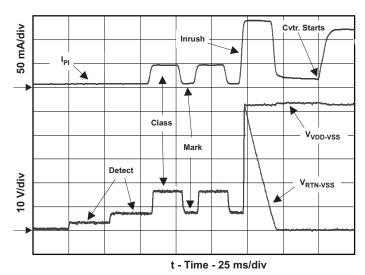

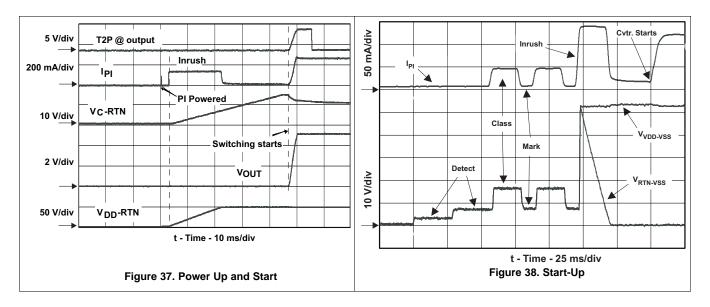

The waveforms of Figure 22 demonstrate detection, classification, and start-up from a PSE with type 2 hardware classification. The key waveforms shown are  $V_{VDD}$ - $V_{VSS}$ ,  $V_{RTN}$ - $V_{VSS}$ , and  $I_{Pl}$ . IEEE 802.3at requires a minimum of two detection levels, two class and mark cycles, and start-up from the second mark event.  $V_{RTN}$  to  $V_{SS}$  falls as the TPS23754 charges  $C_{IN}$  following application of full voltage. Subsequently, the converter starts up, drawing current as seen in the  $I_{Pl}$  waveform.

Figure 22. Start-Up

### 7.4.1.3 Detection

The TPS23754 drives DEN to  $V_{SS}$  whenever  $V_{VDD}$ - $V_{VSS}$  is below the lower classification threshold. When the input voltage rises above  $V_{CL-ON}$ , the DEN pin goes to an open-drain condition to conserve power. While in detection, RTN is high impedance, and almost all the internal circuits are disabled. An  $R_{DEN}$  of 24.9 k $\Omega$  (1%), presents the correct signature. It may be a small, low-power resistor because it only sees a stress of about 5 mW. A valid PD detection signature is an incremental resistance (  $\Delta V / \Delta I$  ) from 23.7 k $\Omega$  to 26.3 k $\Omega$  at the PI.

The detection resistance seen by the PSE at the PI is the result of the input bridge resistance in series with the parallel combination of  $R_{DEN}$  and internal  $V_{DD}$  loading. The input diode bridge's incremental resistance may be hundreds of ohms at the very low currents drawn when 2.7 V is applied to the PI. The input bridge resistance is partially cancelled by the TPS23754's effective resistance during detection.

The type 2 hardware classification protocol of IEEE 802.3at specifies that a type 2 PSE drops its output voltage into the detection range during the classification sequence. The PD is required to have an incorrect detection signature in this condition, which is referred to as the mark event (see Figure 22). After the first mark event, the TPS23754 will present a signature less than 12 k $\Omega$  until it has experienced a  $V_{VDD}$ - $V_{VSS}$  voltage below the mark reset ( $V_{MSR}$ ). This is explained more fully in *Hardware Classification*.

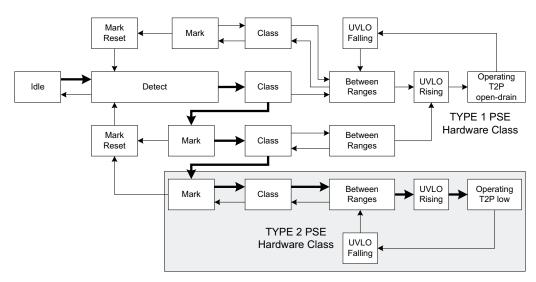

### 7.4.1.4 Hardware Classification

Hardware classification allows a PSE to determine a PD's power requirements before powering, and helps with power management once power is applied. Type 2 hardware classification permits high power PSEs and PDs to determine whether the connected device can support high-power operation. A type 2 PD presents class 4 in hardware to indicate it is a high-power device. A type 1 PSE will treat a class 4 device like a class 0 device, allotting 13 W if it chooses to power the PD. A PD that receives a 2 event class understands that it is powered from a high-power PSE and it may draw up to 25.5 W immediately after the 80-ms start-up period completes. A type 2 PD that does not receive a 2-event hardware classification may choose to not start, or must start in a 13 W condition and request more power through the DLL after start-up. The standard requires a type 2 PD to indicate that it is underpowered if this occurs. Start-up of a high-power PD under 13 W implicitly requires some form of powering down sections of the application circuits.

The maximum power entries in Table 1 determine the class the PD must advertise. The PSE may disconnect a PD if it draws more than its stated class power, which may be the hardware class or a lower DLL-derived power level. The standard permits the PD to draw limited current peaks that increase the instantaneous power above the Table 1 limit; however, the average power requirement always applies.

The TPS23754 implements two-event classification. Selecting an  $R_{CLS}$  of 63.4  $\Omega$  provides a valid type 2 signature. TPS23754 may be used as a compatible type 1 device simply by programming class 0–3 per Table 1. DLL communication is implemented by the ethernet communication system in the PD and is not implemented by the TPS23754.

The TPS23754 disables classification above  $V_{\text{CU\_OFF}}$  to avoid excessive power dissipation. CLS voltage is turned off during PD thermal limit or when APD or DEN are active. The CLS output is inherently current limited, but should not be shorted to  $V_{\text{SS}}$  for long periods of time.

Figure 23 shows how classification works for the TPS23754. Transition from state-to-state occurs when comparator thresholds are crossed (see Figure 20 and Figure 21). These comparators have hysteresis, which adds inherent memory to the machine. Operation begins at idle (unpowered by PSE) and proceeds with increasing voltage from left to right. A 2-event classification follows the (heavy-lined) path towards the bottom, ending up with a latched type 2 decode along the lower branch that is highlighted. This state results in a low T2P during normal operation. Once the valid path to type 2 PSE detection is broken, the input voltage must transition below the mark reset threshold to start anew.

Figure 23. Two-Event Class Internal States

### 7.4.1.5 Inrush and Start-Up

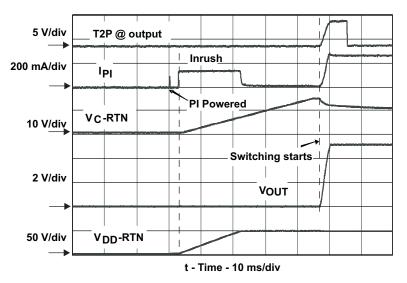

802.3at has a start-up current and time limitation, providing type 2 PSE compatibility for type 1 PDs. A type 2 PSE limits output current to from 400 mA to 450 mA for up to 75 ms after power up (applying 48 V to the PI) to mirror type 1 PSE functionality. The type 2 PSE supports higher output current after 75 ms. The TPS23754 implements a 140-mA inrush current, which is compatible with all PSE types. A high-power PD must control its converter start-up peak and operational currents drawn to less than 400 mA for 80 ms. The TPS23754 device's internal soft-start permits control of the converter start-up; however, the application circuits must assure that their power draw does not cause the PD to exceed the current/time limitation. This requirement implicitly requires some form of powering down sections of the application circuits. T2P becomes valid within t<sub>T2P</sub> after switching starts, or if an adapter is plugged in while the PD is operating from a PSE.

### 7.4.1.6 Maintain Power Signature

The MPS is an electrical signature presented by the PD to assure the PSE that it is still present after operating voltage is applied. A valid MPS consists of a minimum DC current of 10 mA (or a 10-mA pulsed current for at least 75 ms every 325 ms) and an AC impedance lower than 26.3 k $\Omega$  in parallel with 0.05  $\mu$ F. The AC impedance is usually accomplished by the minimum operating  $C_{IN}$  requirement of 5  $\mu$ F. When either APD or DEN is used to force the hotswap switch off, the DC MPS will not be met. A PSE that monitors the DC MPS will remove power from the PD when this occurs. A PSE that monitors only the AC MPS may remove power from the PD.

### 7.4.1.7 Start-Up and Converter Operation

The internal PoE undervoltage lockout (UVLO) circuit holds the hotswap switch off before the PSE provides full voltage to the PD. This prevents the converter circuits from loading the PoE input during detection and classification. The converter circuits discharge  $C_{IN}$ ,  $C_{VC}$ , and  $C_{VB}$  while the PD is unpowered. Thus  $V_{VDD}$ - $V_{RTN}$  will be a small voltage just after full voltage is applied to the PD, as seen in Figure 22. The PSE drives the PI voltage to the operating range once it has decided to power up the PD. When  $V_{VDD}$  rises above the UVLO turnon threshold ( $V_{UVLO-R}$ , about 35 V) with RTN high, the TPS23754 device enables the hotswap MOSFET with an approximately 140-mA (inrush) current limit as seen in Figure 24. Converter switching is disabled while  $C_{IN}$  charges and  $V_{RTN}$  falls from  $V_{VDD}$  to nearly  $V_{VSS}$ , however the converter start-up circuit is allowed to charge  $C_{VC}$  (the bootstrap start-up capacitor). Additional loading applied between  $V_{VDD}$  and  $V_{RTN}$  during the inrush state may prevent successful PD and subsequent converter start-up. Converter switching is allowed if the PD is not in inrush, OTSD is not active, and the  $V_C$  UVLO permits it. Once the inrush current falls about 10% less than the inrush current limit, the PD current limit switches to the operational level (about 970 mA). Continuing the start-up sequence shown in Figure 24,  $V_{VC}$  continues to rise until the start-up threshold ( $V_{CUV}$ , about 15 V or about 9 V) is exceeded, turning the start-up source off and enabling switching. The  $V_B$  regulator is always active, powering the

internal converter circuits as  $V_{VC}$  rises. There is a slight delay between the removal of charge current and the start of switching as the soft-start ramp sweeps above the  $V_{ZDC}$  threshold.  $V_{VC}$  falls as it powers both the internal circuits and the switching MOSFET gates. If the converter control bias output rises to support  $V_{VC}$  before it falls to  $V_{CUV} - V_{CUVH}$  (about 8.5 V or about 5.5 V), a successful start-up occurs. T2P in Figure 22 (Figure 27,  $V_{T2P-OUT}$ ) becomes active within  $t_{T2P}$  from the start of switching, indicating that a type 2 PSE or an adapter is plugged in.

Figure 24. Power Up and Start

If  $V_{VDD}$ -  $V_{VSS}$  drops below the lower PoE UVLO ( $V_{UVLO-R}$  -  $V_{UVLO-H}$ , about 30.5 V), the hotswap MOSFET is turned off, but the converter will still run. The converter will stop if  $V_{VC}$  falls below the converter UVLO ( $V_{CUV} - V_{CUVH}$ , about 8.5 V or about 5.5 V), the hotswap is in inrush current limit, 0% duty cycle is demanded by  $V_{CTL}$  ( $V_{CTL} < V_{ZDC}$ , about 1.5 V), or the converter is in thermal shutdown.

### 7.4.1.8 PD Hotswap Operation

IEEE 802.3at has taken a new approach to PSE output limiting. A type 2 PSE must meet an output current versus time template with specified minimum and maximum sourcing boundaries. The peak output current may be as high as 50 A for 10  $\mu$ s or 1.75 A for 75 ms. This makes robust protection of the PD device even more important than it was in IEEE 802.3-2008.

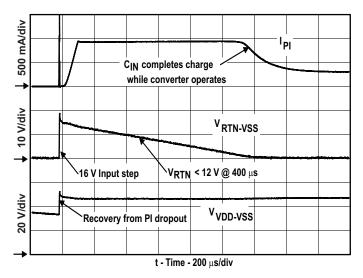

The internal hotswap MOSFET is protected against output faults and input voltage steps with a current limit and deglitched (time-delay filtered) foldback. An overload on the pass MOSFET engages the current limit, with  $V_{RTN}-V_{VSS}$  rising as a result. If  $V_{RTN}$  rises above about 12 V for longer than about 400  $\mu$ s, the current limit reverts to the inrush value, and turns the converter off. The 400  $\mu$ s deglitch feature prevents momentary transients from causing a PD reset, provided that recovery lies within the bounds of the hotswap and PSE protection. Figure 25 shows an example of recovery from a 16 V PSE rising voltage step. The hotswap MOSFET goes into current limit, overshooting to a relatively low current, recovers to about 950-mA full current limit, and charges the input capacitor while the converter continues to run. The MOSFET did not go into foldback because  $V_{RTN}-V_{VSS}$  was less than 12 V after the 400  $\mu$ s deglitch.

Figure 25. Response to PSE Step Voltage

The PD control has a thermal sensor that protects the internal hotswap MOSFET. Conditions like start-up or operation into a V<sub>DD</sub> to RTN short cause high power dissipation in the MOSFET. An overtemperature shutdown (OTSD) turns off the hotswap MOSFET and class regulator, which are restarted after the device cools. The hotswap MOSFET will be re-enabled with the inrush current limit when exiting from an overtemperature event.

Pulling DEN to  $V_{SS}$  during powered operation causes the internal hotswap MOSFET to turn off. This feature allows a PD with Option three ORing per Figure 26 to achieve adapter priority. Take care with synchronous converter topologies that can deliver power in both directions.

The hotswap switch will be forced off under the following conditions:

- 1. V<sub>APD</sub> above V<sub>APDEN</sub> (about 1.5 V)

- 2.  $V_{DEN} < V_{PD-DIS}$  when  $V_{VDD} V_{VSS}$  is in the operational range

- 3. PD over-temperature

- 4.  $(V_{VDD} V_{VSS})$  < PoE UVLO (about 30.5 V)

### 7.4.1.9 Converter Controller Features

The TPS23754 DC-DC controller implements a typical current-mode control as shown in the *Functional Block Diagram*. Features include oscillator, overcurrent and PWM comparators, current-sense blanker, dead-time control, soft start, and gate driver. In addition, an internal slope-compensation ramp generator, frequency synchronization logic, thermal shutdown, and start-up current source with control are provided.

The TPS23754 is optimized for isolated converters, and does not provide an internal error amplifier. Instead, the optocoupler feedback is directly fed to the CTL pin which serves as a current-demand control for the PWM. There is an offset of  $V_{ZDC}$  (about 1.5 V) and 2:1 resistor divider between the CTL pin and the PWM. A  $V_{CTL}$  below  $V_{ZDC}$  will stop converter switching, while voltages above ( $V_{ZDC}$  + (2 ×  $V_{CSMAX}$ )) will not increase the requested peak current in the switching MOSFET. Optocoupler biasing design is eased by this limited control range.

### 7.4.1.10 Bootstrap Topology

The internal start-up current source and control logic implement a bootstrap-type start-up as discussed in Start-Up and Converter Operation. The start-up current source charges  $C_{VC}$  from  $V_{DD1}$  when the converter is disabled (either by the PD control or the  $V_C$  control) to store enough energy to start the converter. Steady-state operating power must come from a converter (bias winding) output or other source. Loading on  $V_C$  and  $V_B$  must be minimal while  $C_{VC}$  charges, otherwise the converter may never start. The optocoupler will not load  $V_B$  when the converter is off for most situations; however take care in ORing topologies where the output is powered when PoE is off.