www.ti.com.cn ZHCSBF3A – AUGUST 2013

# 双通道高速静电放电 (ESD) 保护器件

查询样品: TPD2E1B06

### 特性

- 为低压输入输出 (IO) 接口提供系统级的静电放电 (ESD) 保护

- IEC 61000-4-2 4 级接触 ESD 额定值

- IO 电容值 1pF (典型值)

- 直流 (DC) 击穿电压 7V (最小值)

- 超低泄漏电流 10nA (最大值)

- 低 ESD 钳位电压

- 车用温度范围: -40°C 至 125°C

- 小型易于走线的 DRL 封装

### 应用范围

- 游戏机

- 电子书

- 便携式媒体播放器

- 数码摄像机

### 说明

TPD2E1B06 是一款双通道超低电容 ESD 保护器件。它提供 ±10KV IEC 接触 ESD 保护。 其 1pF 线路电容值使得这款器件适合于广泛应用。 典型应用接口为 USB 2.0,低压差分信令 (LVDS) 和 I2C。 有两个针对 TPD2E1B06 的常见布局布线方法并且都在应用信息部分中突出显示。

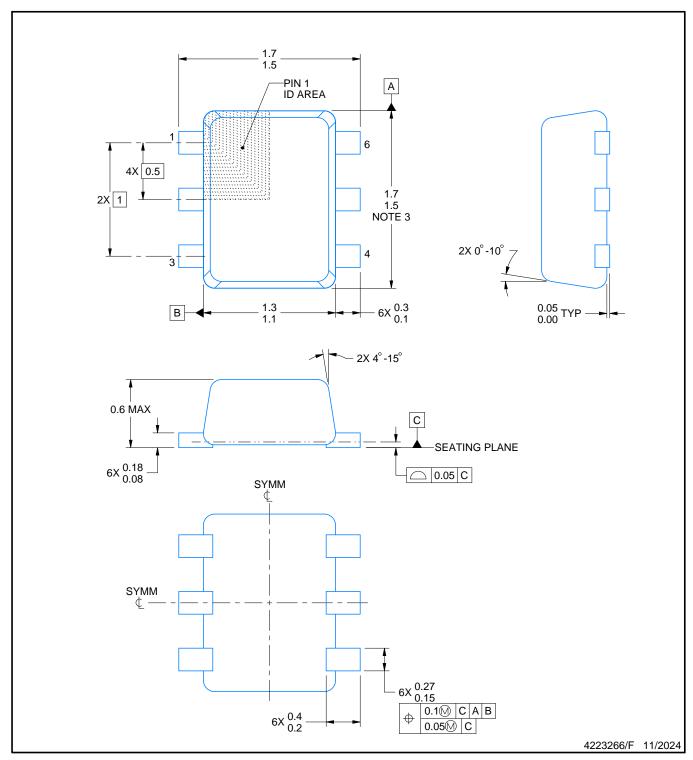

1.6 mm x 1.2 mm x 0.55mm (0.5-mm pitch)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ZHCSBF3A – AUGUST 2013 www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

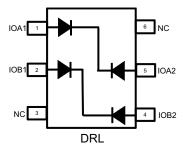

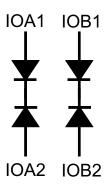

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. CIRCUIT SCHEMATIC DIAGRAM

### **TERMINAL FUNCTIONS**

|      | PIN TYPE |        | DESCRIPTION           | USAGE                                                |  |  |  |  |  |

|------|----------|--------|-----------------------|------------------------------------------------------|--|--|--|--|--|

| NAME | NO.      | PINITE | DESCRIPTION           | USAGE                                                |  |  |  |  |  |

| IOA1 | 1        | I/O    |                       |                                                      |  |  |  |  |  |

| IOA2 | 5        | I/O    | ESD protected channel | Diagon refer to the Application Information Costion  |  |  |  |  |  |

| IOB1 | 2        | I/O    | ESD protected channel | Please refer to the Application Information Section. |  |  |  |  |  |

| IOB2 | 4        | I/O    |                       |                                                      |  |  |  |  |  |

| NC   | 3, 6     | NC     | No connect            | Can be left floating, grounded, or connected to VCC  |  |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                 |                                                 | VALUE      | UNIT |

|-----------------|-------------------------------------------------|------------|------|

|                 | Operating temperature range                     | -40 to 125 | °C   |

|                 | Storage temperature                             | -65 to 155 | °C   |

|                 | IEC 61000-4-2 contact ESD <sup>(1)</sup>        | ±10        | kV   |

| I <sub>PP</sub> | Peak pulse current (tp = 8/20µs) <sup>(1)</sup> | 2.5        | Α    |

| P <sub>PP</sub> | Peak pulse power (tp = 8/20µs) <sup>(1)</sup>   | 35         | W    |

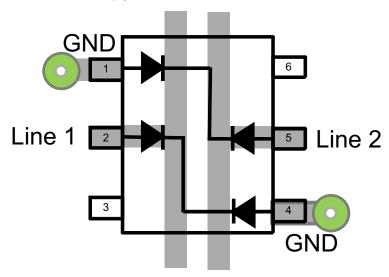

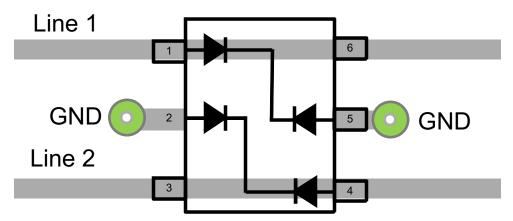

<sup>(1)</sup> Using Routing Option 1 or 2 as shown in Figure 2 or Figure 3.

### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                  |                                              | TPD2E1B06 |      |

|------------------|----------------------------------------------|-----------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                | DRL       | UNIT |

|                  |                                              | (6) PINS  |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 349.7     |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 120.5     |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 171.4     | °C/W |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 10.8      |      |

| ΨЈВ              | Junction-to-board characterization parameter | 169.4     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

www.ti.com.cn ZHCSBF3A - AUGUST 2013

### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range. (unless otherwise noted)

|                    | PARAMETER                 | TEST CONDITIONS                                           | MIN | TYP  | MAX | UNIT |

|--------------------|---------------------------|-----------------------------------------------------------|-----|------|-----|------|

| V <sub>RWM</sub>   | Reverse stand-off voltage |                                                           |     |      | 5.5 | V    |

| \ /                | Clamp voltage with ESD    | $I_{PP} = 1 \text{ A, TLP, I/O to GND}^{(1)(2)}$          |     | 11   |     | V    |

| $V_{CLAMP}$        | strike                    | $I_{PP} = 5 \text{ A}, TLP, I/O \text{ to } GND^{(1)(2)}$ |     | 15   |     | V    |

| V <sub>CLAMP</sub> | Clamp voltage with ESD    | $I_{PP} = 1 \text{ A, TLP, GND to I/O}$                   |     | 11   |     | V    |

|                    | strike                    | $I_{PP} = 5 \text{ A}$ , TLP, GND to I/O $^{(1)(2)}$      |     | 15   |     | V    |

| R <sub>DYN</sub>   | Dynamic resistance        |                                                           |     | 0.9  |     | Ω    |

| C <sub>L1</sub>    | Pin 2 and 5 capacitance   | Pin 1 and 4 = GND, f = 1MHz, $V_{BIAS} = +2.5V^{(2)(3)}$  |     | 0.85 |     | pF   |

| C <sub>L2</sub>    | Pin 1 and 4 capacitance   | Pin 2 and 5 = GND, f = 1MHz, $V_{BIAS} = +2.5V^{(2)(4)}$  |     | 1.05 |     | pF   |

| V <sub>BR</sub>    | Break-down voltage        | I <sub>IO</sub> = 1 mA                                    | 7   |      | 9.5 | V    |

| I <sub>LEAK</sub>  | Leakage current           | V <sub>BIAS</sub> = +2.5 V                                |     | 1    | 10  | nA   |

<sup>(1)</sup> Transmission line pulse with rise time 10ns and pulse width 100ns.

<sup>(2)</sup>  $T_A = 25^{\circ}C$ (3) Using Routing Option 1, Figure 2. (4) Using Routing Option 2, Figure 3.

ZHCSBF3A – AUGUST 2013 www.ti.com.cn

#### **APPLICATION INFORMATION**

There are 2 channels of back-to-back diodes in TPD2E1B06DRL. The device should be routed in one of the two ways shown below. Routing option 1 is recommended because TPD2E1B06 is designed to maximize signal integrity in this configuration while still comply with IEC 61000-4-2 level 4 contact ESD rating.

Figure 2. Routing Option 1

Figure 3. Routing Option 2

www.ti.com.cn ZHCSBF3A – AUGUST 2013

### **REVISION HISTORY**

| Cł | nanges from Original (July 20 | 13) to Revision A | Page |

|----|-------------------------------|-------------------|------|

| •  | 将文档从预览改为生产数据。                 |                   | 1    |

www.ti.com 17-Jun-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)  |

|-----------------------|--------|---------------|-------------------|-----------------------|------|-------------------------------|----------------------------|--------------|-------------------|

|                       |        |               |                   |                       |      | (4)                           | (5)                        |              |                   |

| TPD2E1B06DRLR         | Active | Production    | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes  | NIPDAU   NIPDAUAG             | Level-1-260C-UNLIM         | -40 to 125   | (DUH, DUL)<br>DUG |

| TPD2E1B06DRLR.B       | Active | Production    | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | (DUH, DUL)<br>DUG |

| TPD2E1B06DRLRG4       | Active | Production    | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | DUL               |

| TPD2E1B06DRLRG4.B     | Active | Production    | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | DUL               |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jul-2025

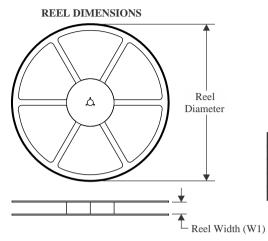

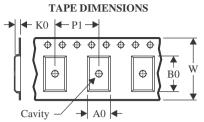

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

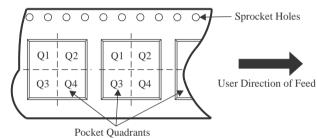

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPD2E1B06DR  | RLR SOT-5X3     | DRL                | 6 | 4000 | 180.0                    | 8.4                      | 2.0        | 1.8        | 0.75       | 4.0        | 8.0       | Q3               |

| TPD2E1B06DRL | .RG4 SOT-5X3    | DRL                | 6 | 4000 | 180.0                    | 8.4                      | 2.0        | 1.8        | 0.75       | 4.0        | 8.0       | Q3               |

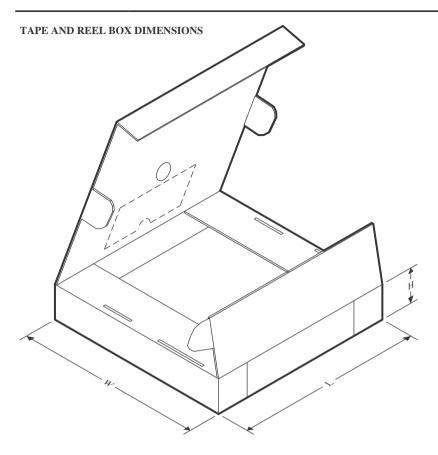

**PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jul-2025

### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPD2E1B06DRLR   | SOT-5X3      | DRL             | 6    | 4000 | 210.0       | 185.0      | 35.0        |

| TPD2E1B06DRLRG4 | SOT-5X3      | DRL             | 6    | 4000 | 210.0       | 185.0      | 35.0        |

PLASTIC SMALL OUTLINE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-293 Variation UAAD

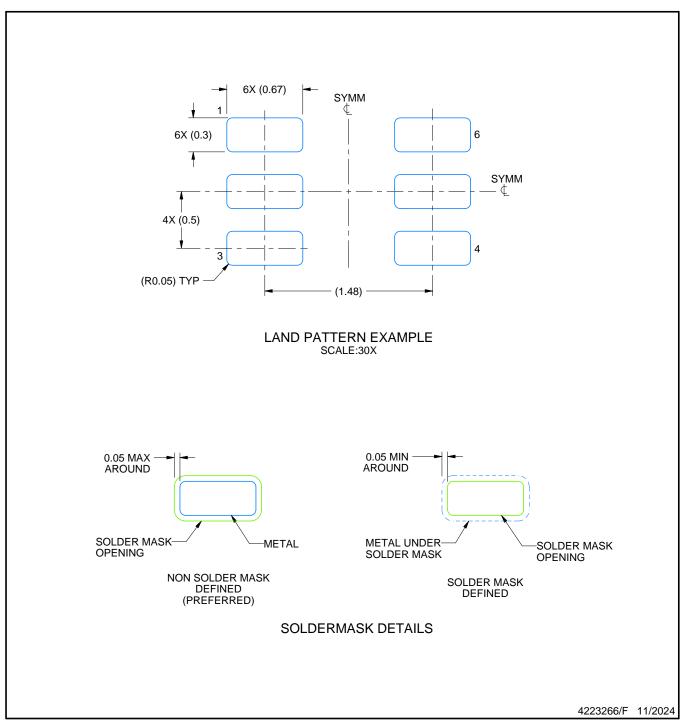

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.7. Land pattern design aligns to IPC-610, Bottom Termination Component (BTC) solder joint inspection criteria.

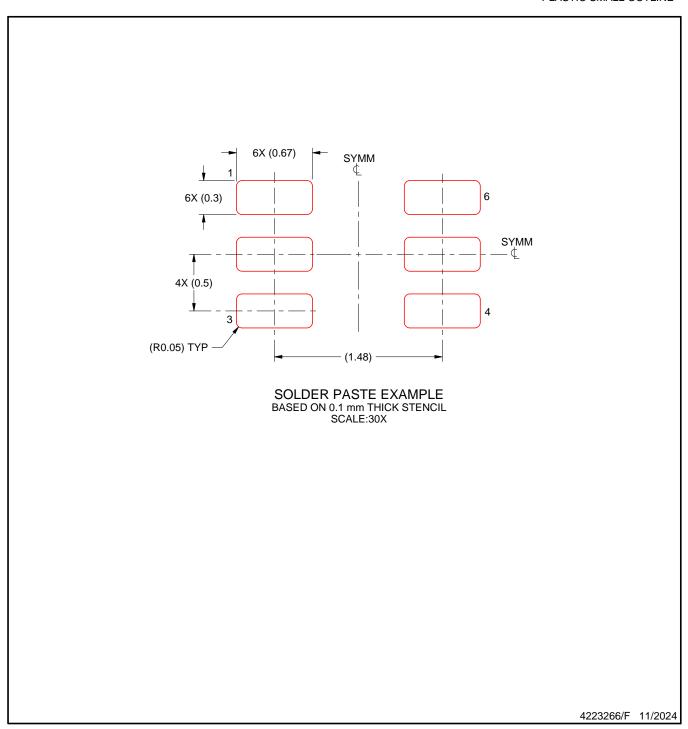

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司