TPA3220

ZHCSHB1B - JANUARY 2018 - REVISED AUGUST 2018

# TPA3220 60W 立体声 100W 峰值高清模拟输入 D 类放大器(焊盘朝下)

### 1 特性

- 立体声 (2 x BTL) 和单声道 (1 x PBTL) 运行

- THD+N 为 10% 时的输出功率

- 60W (连续功率)/8Ω, BTL 立体声配置

- 110W(峰值功率)/4Ω, BTL 立体声配置

- THD+N 为 1% 时的输出功率

- 50W (连续功率)/8Ω, BTL 立体声配置

- 89W (峰值功率) /4Ω, BTL 立体声配置

- 用于可选单电源操作的 5V 栅极驱动器或内置 LDO

- 闭环反馈设计

- 高达 100kHz 的信号带宽,用于高清源的高频成分

- 1W/4Ω 时的 THD+N 为 0.02%

- PSRR 为 60dB (BTL, 无输入信号)

- 输出噪声(A 加权) < 72μV</li>

- SNR (A 加权) > 108dB

- AD 或 HEAD 调制方案

- 低功耗操作模式

- 待机模式:静音,<1mA关断

- 低空闲电流 HEAD 调制方案

- 单通道 BTL 操作

- 多输入操作,可简化前置放大器设计

- 差动或单端模拟输入

- 可选增益: 18dB、24dB、30dB、34dB

- 集成式保护:欠压、逐周期电流限制、短路、削波 检测、过热警告和关断以及直流扬声器保护

- 90% 高效 D 类操作 (4Ω)

- 散热垫位于封装的底部

- 具有电压和功率级别选项的引脚兼容系列器件

# 2 应用

- 蓝牙和 Wi-Fi™扬声器

- 条形音箱

- 低音炮

- 书架立体声系统

- 专业和公共广播 (PA) 扬声器和

### 3 说明

TPA3220 是一款可在全功率、空闲和待机状态下实现高效操作的焊盘朝下的 D 类放大器。该器件 采用 具有高达 100kHz 带宽的闭环反馈,从而在音频频带内提供低失真并提供出色的质量。该器件以 AD 或低空闲电流 HEAD (高效 AD) 调制运行,并可为 4Ω 负载提供 2 x 60W 的连续功率或 2 x 110W 的峰值功率(底部的散热垫连接到 PCB)。

TPA3220 具有 单端或差分模拟输入接口,该接口最高支持 2V<sub>RMS</sub> 的电压并具有四种可选增益: 18dB、24dB、30dB 和 34dB。TPA3220 还实现了大于 90%的效率、低空闲功率 (<0.25 W) 和超低待机功耗 (<0.1 W)。这是通过使用 70mΩ MOSFET、经优化的栅极驱动方案和低功耗操作模式实现的。TPA3220 包含用于轻松集成在单电源系统中的内置 LDO。为了进一步简化设计,该级器件集成了重要的保护 功能,包含低压、逐周期电流限制、短路、削波检测、过热警告和关断以及直流扬声器保护。

### 器件信息(1)

|         | HH I I IH 7G. |                  |

|---------|---------------|------------------|

| 器件型号    | 封装            | 封装尺寸 (NOM)       |

| TPA3220 | HTSSOP (44)   | 6.10mm x 14.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

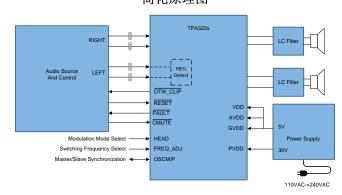

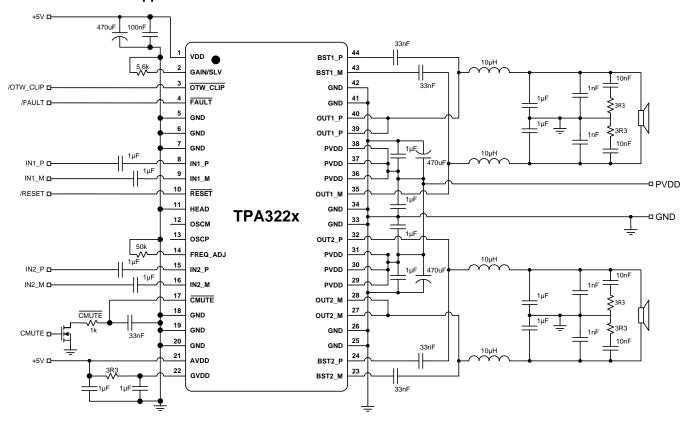

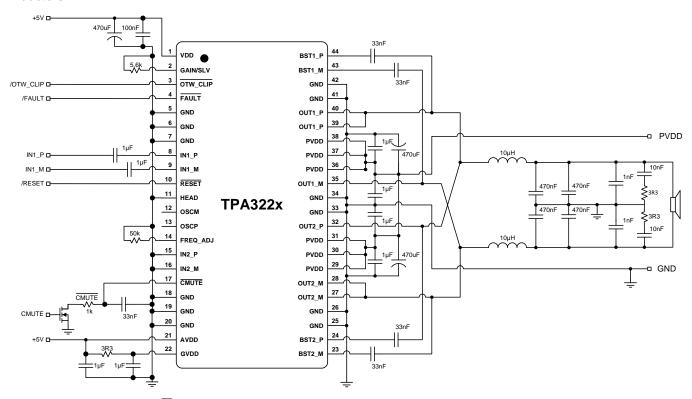

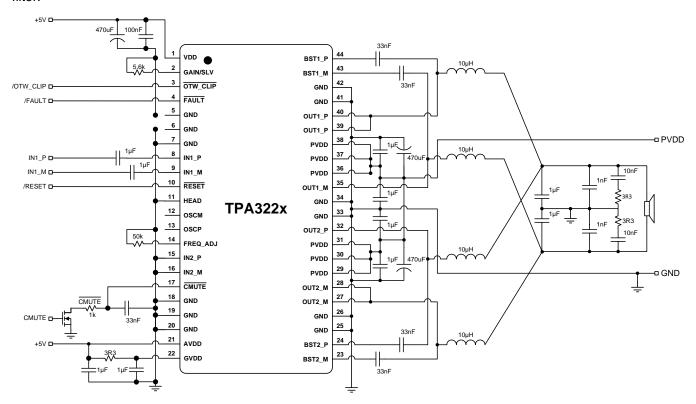

# 简化原理图

|                                 | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 录                    |              |      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 应用       1         说明       1         修订历史记录       2         Device Comparison Table       3         Pin Configuration and Functions       3         Specifications       5         7.1 Absolute Maximum Ratings       5         7.2 ESD Ratings       5         7.3 Recommended Operating Conditions       6         7.4 Thermal Information       6         7.5 Electrical Characteristics       7         7.6 Audio Characteristics (BTL)       9         7.7 Audio Characteristics (PBTL)       9         7.8 Typical Characteristics, BTL Configuration, ADmode       10         7.9 Typical Characteristics, PBTL Configuration, ADmode       13         Parameter Measurement Information       15 | 10<br>11<br>12<br>13 | 9.1 Overview |      |

|                                 | 修订历史记录<br>inges from Revision A (July 2018) to Revision B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |              | Page |

|                                 | 在以下部分中将"可选增益: 18dB、24dB、30dB 和 34dB L<br>益: 18dB、24dB、30dB 和 34dB": 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |              | 1    |

| Cha                             | inges from Original (January 2018) to Revision A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |              | Page |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |              |      |

# 5 Device Comparison Table

| DEVICE<br>NAME | DESCRIPTION                                                       | SUPPLY<br>VOLTAGE | THERMAL PAD LOCATION | TPA3220<br>PIN-<br>COMPATIBLE |

|----------------|-------------------------------------------------------------------|-------------------|----------------------|-------------------------------|

| TPA3221        | 100 W Stereo, 200 W Mono HD, Analog-Input, Class-D Amplifier      | 30 V              | Тор                  | Υ                             |

| TPA3244        | 40 W Stereo, 100 W Peak Ultra-HD, Analog-Input, Pad-Down Class-D  | 30 V              | Bottom               |                               |

| TPA3245        | 100 W Stereo, 200 W Mono Ultra-HD, Analog-Input Class-D Amplifier | 30 V              | Тор                  |                               |

| TPA3250        | 70 W Stereo, 130 W Peak Ultra-HD, Analog-Input, Pad-Down Class-D  | 36 V              | Bottom               |                               |

| TPA3251        | 175 W Stereo, 350 W Mono Ultra-HD, Analog-Input Class-D Amplifier | 36 V              | Тор                  |                               |

| TPA3255        | 315 W Stereo, 600 W Mono Ultra-HD, Analog-Input Class-D Amplifier | 53.5 V            | Тор                  |                               |

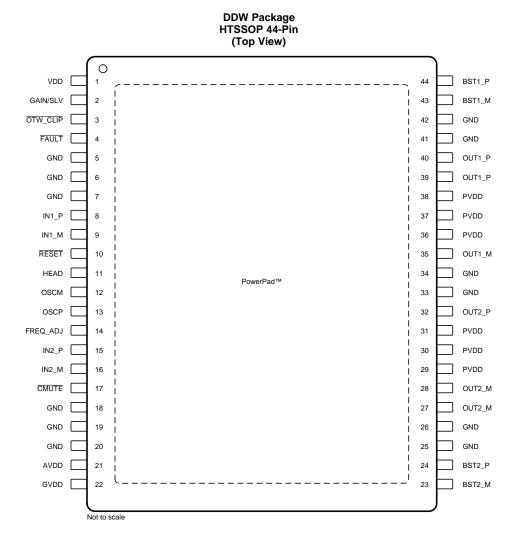

# 6 Pin Configuration and Functions

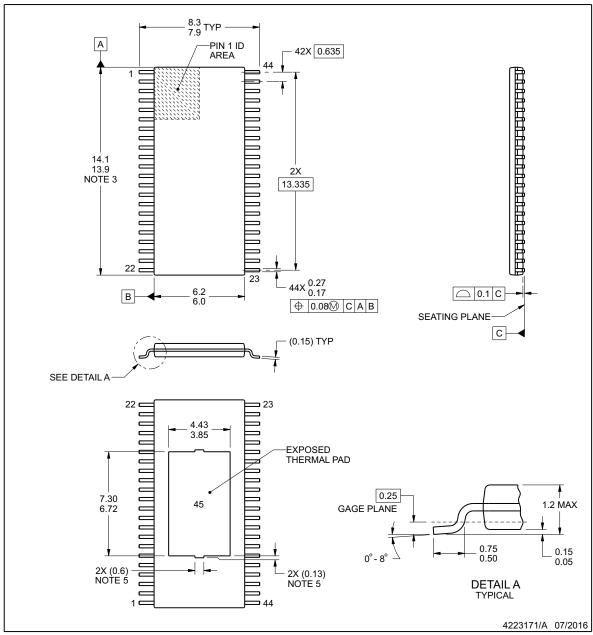

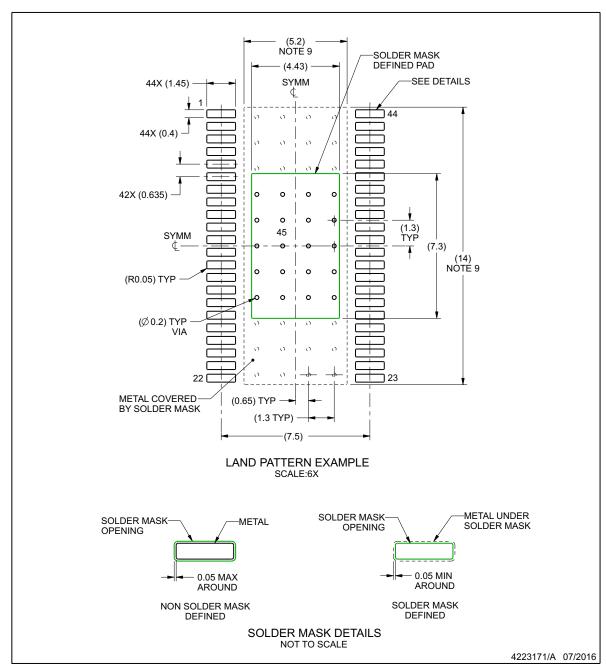

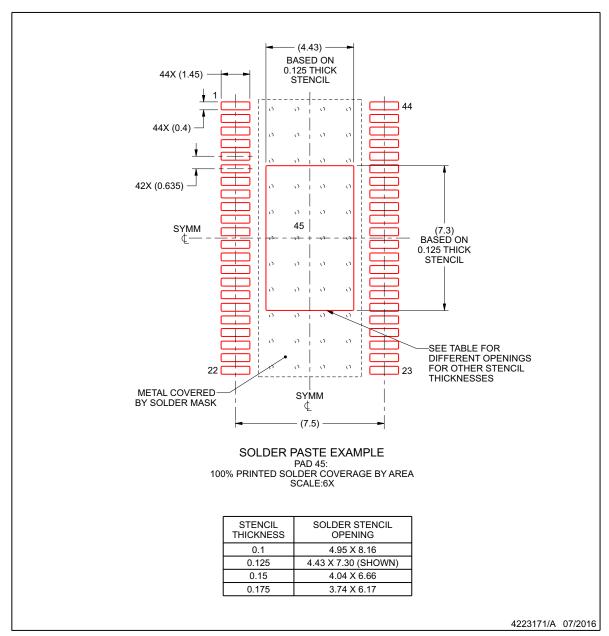

The TPA3220 is available in a thermally enhanced TSSOP package. The package type contains a thermal pad located on the bottom side of the device for convenient thermal coupling to the PCB.

### **Pin Functions**

| NAME      | NO.                                               | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                 |

|-----------|---------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| HEAD      | 11                                                | 1                  | 0 = AD, 1 = HEAD. Refer to: AD-Mode and HEAD-Mode PWM Modulation                                                            |

| AVDD      | 21                                                | Р                  | AVDD voltage supply. Refer to: Internal LDO, AVDD and GVDD Supplies                                                         |

| BST1_M    | 43                                                | Р                  | OUT1_M HS bootstrap supply (BST), 0.033 µF capacitor to OUT1_M required.  Refer to: BST capacitors                          |

| BST1_P    | 44                                                | Р                  | OUT1_P HS bootstrap supply (BST), 0.033 μF capacitor to OUT1_P required. Refer to: BST capacitors                           |

| BST2_M    | 23                                                | Р                  | OUT2_M HS bootstrap supply (BST), 0.033 µF capacitor to OUT2_M required.  Refer to: BST capacitors                          |

| BST2_P    | 24                                                | Р                  | OUT2_P HS bootstrap supply (BST), 0.033 μF capacitor to OUT2_P required. Refer to:BST capacitors                            |

| CMUTE     | 17                                                | Р                  | Mute and Startup Timing capacitor. Refer to: Device Soft Mute                                                               |

| FAULT     | 4                                                 | 0                  | Shutdown signal, open drain; active low. Refer to: Error Reporting                                                          |

| FREQ_ADJ  | 14                                                | 0                  | Oscillator frequency programming pin. Refer to: Oscillator                                                                  |

| GAIN/SLV  | 2                                                 | I                  | Closed loop gain and master/slave programming pin. Refer to: Input Configuration, Gain Setting And Master / Slave Operation |

| GND       | 5, 6, 7, 18, 19,<br>20, 25, 26, 33,<br>34, 41, 42 | Р                  | Ground                                                                                                                      |

| GVDD      | 22                                                | Р                  | Gate drive supply. Refer to: Internal LDO, AVDD and GVDD Supplies                                                           |

| IN1_M     | 9                                                 | I                  | Negative audio input for channel 1.                                                                                         |

| IN1_P     | 8                                                 | I                  | Positive audio input for channel 1.                                                                                         |

| IN2_M     | 16                                                | I                  | Negative audio input for channel 2.                                                                                         |

| IN2_P     | 15                                                | I                  | Positive audio input for channel 2.                                                                                         |

| OSCM      | 12                                                | I/O                | Oscillator synchronization interface. Refer to: Input Configuration, Gain Setting And Master / Slave Operation              |

| OSCP      | 13                                                | I/O                | Oscillator synchronization interface. Refer to: Input Configuration, Gain Setting And Master / Slave Operation              |

| OUT1_M    | 35                                                | 0                  | Negative output for channel 1.                                                                                              |

| OTW_CLIP  | 3                                                 | 0                  | Clipping warning and Over-temperature warning; open drain; active low. Refer to: Error Reporting                            |

| OUT1_P    | 39, 40                                            | 0                  | Positive output for channel 1.                                                                                              |

| OUT2_M    | 27, 28                                            | 0                  | Negative output for channel 2.                                                                                              |

| OUT2_P    | 32                                                | 0                  | Positive output for channel 2.                                                                                              |

| PVDD      | 29, 30, 31, 36,<br>37, 38                         | Р                  | PVDD supply. Refer to: PVDD Capacitor Recommendation, PVDD Supply                                                           |

| RESET     | 10                                                | I                  | Device reset Input; active Iow. Refer to: Fault Handling, Powering Up, Powering Down                                        |

| VDD       | 1                                                 | Р                  | Input power supply. Refer to: Internal LDO, VDD Supply                                                                      |

| PowerPad™ |                                                   | Р                  | Ground, connect to PCB copper pour. Placed on bottom side of device.                                                        |

(1) I=Input, O=Output, I/O= Input/Output, P=Power

# **Table 1. Mode Selection Pins**

| MODE PINS <sup>(1)</sup> |       | INPUT MODE <sup>(2)</sup> | OUTPUT     | DESCRIPTION   |                                                                                                          |

|--------------------------|-------|---------------------------|------------|---------------|----------------------------------------------------------------------------------------------------------|

| IN2_M                    | IN2_P | HEAD                      | INPUT MODE | CONFIGURATION | DESCRIPTION                                                                                              |

| X                        | Х     | 0                         | 1N/2N + 1  | 2 × BTL       | Stereo, BTL output configuration, AD mode modulation                                                     |

| X                        | X     | 1                         | 1N/2N + 1  | 2 × BTL       | Stereo, BTL output configuration, HEAD mode modulation                                                   |

| 0                        | 0     | 0                         | 1N/2N + 1  | 1 x PBTL      | Mono, Parallelled BTL configuration. Connect OUT1_P to OUT2_P and OUT1_M to OUT2_M, AD mode modulation   |

| 0                        | 0     | 1                         | 1N/2N + 1  | 1 x PBTL      | Mono, Parallelled BTL configuration. Connect OUT1_P to OUT2_P and OUT1_M to OUT2_M, HEAD mode modulation |

| 1                        | 1     | 0                         | 1N/2N + 1  | 1 x BTL       | Mono, BTL configuration. OUT1_M and OUT1_P active, AD mode modulation                                    |

| 1                        | 1     | 1                         | 1N/2N + 1  | 1 x BTL       | Mono, BTL configuration. OUT1_M and OUT1_P active, HEAD mode modulation                                  |

(1) X refers to inputs connected through AC coupling capacitor, 0 refers to logic low (GND), 1 refers to logic high (AVDD).

(2) 2N refers to differential input signal, 1N refers to single ended input signal. +1 refers to number of logic control (RESET) input pins.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                           | MIN  | MAX  | UNIT |

|------------------|-----------------------------------------------------------|------|------|------|

|                  | PVDD to GND <sup>(2)</sup>                                | -0.3 | 37   | V    |

|                  | BST_X to GVDD <sup>(2)</sup>                              | -0.3 | 37   | V    |

| Cumply valtage   | BST1_M, BST1_P, BST2_M, BST2_P to GND <sup>(2)</sup>      | -0.3 | 47.8 | V    |

| Supply voltage   | VDD to GND                                                | -0.3 | 43   | V    |

|                  | GVDD to GND <sup>(2)</sup>                                | -0.3 | 5.5  | V    |

|                  | AVDD to GND                                               | -0.3 | 5.5  | V    |

|                  | OUT1_M, OUT1_P, OUT2_M, OUT2_P to GND <sup>(2)</sup>      | -0.3 | 43   | V    |

|                  | IN1_M, IN1_P, IN2_M, IN2_P to GND                         | -0.3 | 5.5  | V    |

| Interface pins   | HEAD, FREQ_ADJ, GAIN/SLV, CMUTE, RESET, OSCP, OSCM to GND | -0.3 | 5.5  | V    |

|                  | FAULT, OTW_CLIP to GND                                    | -0.3 | 5.5  | V    |

|                  | Continuous sink current, FAULT, OTW_CLIP to GND           |      | 9    | mA   |

| T <sub>J</sub>   | Operating junction temperature range                      | -40  | 150  | °C   |

| T <sub>stg</sub> | Storage temperature range                                 | -40  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) These voltages represents the DC voltage + peak AC waveform measured at the terminal of the device in all conditions.

# 7.2 ESD Ratings

|                  |                         |                                                                               | VALUE | UNIT |

|------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

| V                | Clastrostatia disabarra | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±1000 | V    |

| V <sub>ESD</sub> |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                   |                                                                   | MIN  | TYP | MAX  | UNIT |

|-------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|------|-----|------|------|

| PVDD                    | Power-stage supply                                                | DC supply voltage                                                 | 7    | 30  | 32   | V    |

| VDD <sup>(1)</sup>      | Supply voltage for internal LDO regulator to supply GVDD and AVDD | DC supply voltage                                                 | 7    |     | 32   | V    |

| VDD                     | External supply for VDD, GVDD and AVDD. Internal LDO bypassed     | DC supply voltage                                                 | 4.5  | 5   | 5.5  | V    |

| AVDD                    | Supply voltage for analog circuits                                | DC supply voltage                                                 | 4.5  | 5   | 5.5  | V    |

| GVDD                    | Supply voltage for gate-drive circuitry                           | DC supply voltage                                                 | 4.5  | 5   | 5.5  | V    |

| R <sub>L</sub> (BTL)    | Load impedance                                                    | PVDD = 30 V, Output filter inductance                             | 2.7  | 4   |      | Ω    |

| R <sub>L</sub> (PBTL)   | Load impedance                                                    | within recommended range                                          | 1.6  | 3   |      |      |

| L <sub>OUT</sub> (BTL)  | Output filter inductance                                          | Minimum output inductance at I <sub>OC</sub>                      | 5    | 10  |      |      |

| I (DDTI)                | Output filter inductance, PBTL before the LC filter               | Minimum output inductance at I <sub>OC</sub>                      | 5    | 10  |      | μΗ   |

| L <sub>OUT</sub> (PBTL) | Output filter inductance, PBTL after the LC filter                | Minimum output inductance at half $I_{\text{OC}}$ , each inductor | 5    | 10  |      |      |

|                         | PWM frame rate selectable for AM                                  | Nominal                                                           | 575  | 600 | 625  |      |

| $F_{PWM}$               | interference avoidance; 1% Resistor                               | AM1                                                               | 510  | 533 | 555  | kHz  |

|                         | tolerance                                                         | AM2                                                               | 460  | 480 | 500  |      |

|                         |                                                                   | Nominal; Master mode                                              | 49.5 | 50  | 50.5 |      |

| $R_{(FREQ\_ADJ)}$       | PWM frame rate programming resistor                               | AM1; Master mode                                                  | 29.7 | 30  | 30.3 | kΩ   |

|                         |                                                                   | AM2; Master mode                                                  | 9.9  | 10  | 10.1 | 1    |

| C <sub>PVDD</sub>       | PVDD close decoupling capacitors                                  |                                                                   |      | 1.0 |      | μF   |

| V <sub>(FREQ_ADJ)</sub> | Voltage on FREQ_ADJ pin for slave mode operation                  | Slave Mode (Connect to AVDD)                                      |      | 5   |      | V    |

<sup>(1)</sup> VDD must be connected to a supply of 5V in LDO bypass mode; OR 7V to 30V with LDO active. VDD can be connected directly to PVDD in LDO active mode, but must not exceed PVDD voltage.

# 7.4 Thermal Information

|                      |                                              | TPA3220                    |      |

|----------------------|----------------------------------------------|----------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DDW 44-PINS HTSSOP         | UNIT |

|                      |                                              | JEDEC STANDARD 4 LAYER PCB |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 23.5                       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 11.1                       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 4.5                        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2                        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 4.5                        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.1                        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

PVDD\_X = 30 V, VDD = 5 V, GVDD = 5 V, T<sub>C</sub> (Case temperature) = 75 °C, f<sub>S</sub> = 480 kHz, unless otherwise specified.

|                          | PARAMETER                                                                                                               | TEST CONDITIONS                                                       | MIN  | TYP   | MAX  | UNIT    |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|-------|------|---------|

| INTERNAL VOL             | TAGE REGULATOR AND CURRENT CONSUMPTI                                                                                    | ON                                                                    | -    | -     |      | -       |

| AVDD                     | Voltage regulator. Only used as reference node when supplied by internal LDO. Voltage regulator bypassed for VDD = 5 V. | VDD = 30 V                                                            |      | 5     |      | V       |

|                          | VDD gupply gurrent LDQ mode (VDD > 7 V)                                                                                 | Operating, no audio signal                                            |      | 25    |      | mA      |

| •                        | VDD supply current. LDO mode (VDD > 7 V)                                                                                | Reset mode                                                            |      | 118   |      |         |

| VDD                      | VDD supply current. LDO bypass mode                                                                                     | Operating, no audio signal                                            |      | 150   |      | μΑ      |

|                          | (VDD = 5 V)                                                                                                             | Reset mode                                                            |      | 50    |      |         |

| 1                        | Gate-supply current. LDO bypass mode                                                                                    | Operating, no audio signal                                            |      | 10    |      |         |

| I <sub>AVDD</sub>        | (VDD = 5 V)                                                                                                             | Reset mode                                                            |      | 1     |      | mA      |

|                          | Gate-supply current. LDO bypass mode                                                                                    | 50% duty cycle                                                        |      | 16    |      |         |

|                          | (VDD = 5 V), AD-mode modulation                                                                                         | Reset mode                                                            |      | 50    |      | μA      |

| I <sub>GVDD</sub>        | Gate-supply current. LDO bypass mode                                                                                    | HEAD-mode modulation                                                  |      | 16    |      | mA      |

|                          | (VDD = 5 V), HEAD-mode modulation                                                                                       | Reset mode                                                            |      | 50    |      | μΑ      |

|                          |                                                                                                                         | 50% duty cycle with recommended output filter                         |      | 17    |      |         |

|                          | Total PVDD idle current, AD-mode modulation, BTL                                                                        | 50% duty cycle with recommended output filter, T <sub>C</sub> = 25 °C |      | 17    |      |         |

|                          |                                                                                                                         | Reset mode, No switching                                              |      | 1     |      |         |

| I <sub>PVDD</sub>        |                                                                                                                         | HEAD-mode modulation with recommended output filter                   |      | 12    |      | mA      |

|                          | Total PVDD idle current, HEAD-mode modulation, BTL                                                                      | HEAD-mode with recommended output filter, $T_C = 25$ °C               |      | 12    |      |         |

|                          |                                                                                                                         | Reset mode, No switching                                              |      | 1     |      |         |

| ANALOG INPUT             | rs                                                                                                                      |                                                                       | ı    |       |      |         |

| V <sub>IN</sub>          | Maximum input voltage swing                                                                                             |                                                                       |      |       | ±2.8 | V       |

| I <sub>IN</sub>          | Maximum input current                                                                                                   |                                                                       | -1   |       | 1    | mA      |

|                          | Inverting voltage Gain, V <sub>OUT</sub> /V <sub>IN</sub> (Master                                                       | $R_1 = 5.6 \text{ k}\Omega, R_2 = \text{OPEN}$                        |      | 18    |      |         |

|                          |                                                                                                                         | $R_1 = 20 \text{ k}\Omega, R_2 = 100 \text{ k}\Omega$                 |      | 24    |      |         |

|                          | Mode)                                                                                                                   | $R_1 = 39 \text{ k}\Omega, R_2 = 100 \text{ k}\Omega$                 |      | 30    |      |         |

| _                        |                                                                                                                         | $R_1 = 47 \text{ k}\Omega, R_2 = 75 \text{ k}\Omega$                  |      | 34    |      |         |

| G                        |                                                                                                                         | $R_1 = 51 \text{ k}\Omega, R_2 = 51 \text{ k}\Omega$                  |      | 18    |      | dB      |

|                          |                                                                                                                         | $R_1 = 75 \text{ k}\Omega, R_2 = 47 \text{ k}\Omega$                  |      | 24    |      |         |

|                          | Inverting voltage Gain, V <sub>OUT</sub> /V <sub>IN</sub> (Slave Mode)                                                  | $R_1 = 100 \text{ k}\Omega, R_2 = 39 \text{ k}\Omega$                 |      | 30    |      |         |

|                          |                                                                                                                         | $R_1 = 100 \text{ k}\Omega, R_2 = 16 \text{ k}\Omega$                 |      | 34    |      |         |

|                          |                                                                                                                         | G = 18 dB                                                             |      | 48    |      |         |

|                          |                                                                                                                         | G = 24 dB                                                             |      | 24    |      |         |

| R <sub>IN</sub>          | Input resistance                                                                                                        | G = 30 dB                                                             |      | 12    |      | kΩ      |

|                          |                                                                                                                         | G = 34 dB                                                             |      | 7.7   |      |         |

| OSCILLATOR               |                                                                                                                         | 1                                                                     |      |       |      |         |

|                          | Nominal, Master Mode                                                                                                    |                                                                       | 3.45 | 3.6   | 3.75 |         |

| f <sub>OSC(IO)</sub> (1) | AM1, Master Mode                                                                                                        | F <sub>PWM</sub> × 6                                                  | 3.06 | 3.198 | 3.33 | MHz     |

| -000(10)                 | AM2, Master Mode                                                                                                        | · · · · · ·                                                           | 2.76 | 2.88  | 3    |         |

| V <sub>IH</sub>          | High level input voltage                                                                                                |                                                                       | 1.88 | 2.50  | J    | V       |

| V <sub>IL</sub>          | Low level input voltage                                                                                                 |                                                                       | 1.00 |       | 1.65 | V       |

|                          | CILLATOR (Slave Mode)                                                                                                   |                                                                       |      |       | 1.00 | •       |

| ,                        | CLK input on OSCM/OSCP (Slave Mode)                                                                                     |                                                                       | 2.3  |       | 3.78 | MHz     |

| output etaci             | , , ,                                                                                                                   |                                                                       | 2.3  |       | 5.70 | IVII IZ |

| OUTPUT-STAGI             |                                                                                                                         |                                                                       |      | 70    | 1    |         |

| R <sub>DS(on)</sub>      | Drain-to-source resistance, low side (LS)                                                                               | T <sub>J</sub> = 25 °C, Excludes metallization resistance,            |      | 70    |      | mΩ      |

|                          | Drain-to-source resistance, high side (HS)                                                                              | GVDD = 5 V                                                            |      | 70    |      | mΩ      |

<sup>(1)</sup> Nominal, AM1 and AM2 use same internal oscillator with fixed ratio 4:4.5:5

# **Electrical Characteristics (continued)**

$PVDD_X = 30 \text{ V}, VDD = 5 \text{ V}, GVDD = 5 \text{ V}, T_C \text{ (Case temperature)} = 75 ^{\circ}\text{C}, f_S = 480 \text{ kHz}, unless otherwise specified.}$

|                                   | PARAMETER                                                                                  | TEST CONDITIONS                                                                  | MIN | TYP  | MAX | UNIT    |

|-----------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|---------|

| I/O PROTECTION                    |                                                                                            |                                                                                  |     |      |     |         |

| $V_{uvp,AVDD}$                    | Undervoltage protection limit, AVDD                                                        |                                                                                  |     | 4    |     | V       |

| V <sub>uvp,AVDD,hyst</sub> (2)    | Undervoltage protection hysteresis, AVDD                                                   |                                                                                  |     | 0.1  |     | V       |

| $V_{uvp,PVDD}$                    | Undervoltage protection limit, PVDD_x                                                      |                                                                                  |     | 6.4  |     | V       |

| V <sub>uvp,PVDD,hyst</sub> (2)    | Undervoltage protection hysteresis, PVDD_x                                                 |                                                                                  |     | 0.45 |     | V       |

| OTW                               | Overtemperature warning, OTW_CLIP (2)                                                      |                                                                                  | 115 | 125  | 135 | °C      |

| OTW <sub>hyst</sub> (2)           | Temperature drop needed below OTW temperature for OTW_CLIP to be inactive after OTW event. |                                                                                  |     | 20   |     | °C      |

| OTE <sup>(2)</sup>                | Overtemperature error                                                                      |                                                                                  | 145 | 155  | 165 | °C      |

| OTE <sub>hyst</sub> (2)           | A reset needs to occur for FAULT to be released following an OTE event                     |                                                                                  |     | 20   |     | °C      |

| OTE-OTW <sub>(differential)</sub> | OTE-OTW differential                                                                       |                                                                                  |     | 25   |     | °C      |

| OLPC                              | Overload protection counter                                                                | f <sub>PWM</sub> = 600 kHz (1024 PWM cycles)                                     |     | 1.7  |     | ms      |

| I <sub>OC, BTL</sub>              | Overcurrent limit protection, speaker output current                                       | Nominal peak current in 1Ω load                                                  |     | 10   |     | Α       |

| I <sub>OC, PBTL</sub>             |                                                                                            | Nominal peak current in 122 load                                                 |     | 20   |     | Α       |

| I <sub>DCspkr, BTL</sub>          | DC Speaker Protection Current Threshold                                                    | BTL current imbalance threshold                                                  |     | 1.8  |     | Α       |

| I <sub>DCspkr, PBTL</sub>         | DC Speaker Protection Current Threshold                                                    | PBTL current imbalance threshold                                                 |     | 3.6  |     | Α       |

| I <sub>OCT</sub>                  | Overcurrent response time                                                                  | Time from switching transition to flip-state induced by overcurrent.             |     | 150  |     | ns      |

| I <sub>PD</sub>                   | Output pulldown current of each half                                                       | Connected when RESET is active to provide bootstrap charge. Not used in SE mode. |     | 3    |     | mA      |

| STATIC DIGITAL S                  | PECIFICATIONS                                                                              |                                                                                  |     |      |     |         |

| V <sub>IH</sub>                   | High level input voltage                                                                   |                                                                                  | 1.9 |      |     | V       |

| V <sub>IL</sub>                   | Low level input voltage                                                                    | HEAD, OSCM, OSCP, CMUTE, RESET                                                   |     |      | 0.8 | V       |

| $I_{lkg}$                         | Input leakage current                                                                      |                                                                                  |     |      | 100 | μΑ      |

| OTW/SHUTDOWN                      | FAULT)                                                                                     |                                                                                  |     |      |     |         |

| R <sub>INT_PU</sub>               | Internal pullup resistance, OTW_CLIP to AVDD, FAULT to AVDD                                |                                                                                  | 20  | 26   | 32  | kΩ      |

| V <sub>OH</sub>                   | High level output voltage                                                                  | Internal pullup resistor                                                         | 3   | 3.3  | 3.6 | V       |

| V <sub>OL</sub>                   | Low level output voltage                                                                   | I <sub>O</sub> = 4 mA                                                            |     | 200  | 500 | mV      |

| Device fanout                     | OTW_CLIP, FAULT                                                                            | No external pullup                                                               |     | 30   |     | devices |

<sup>(2)</sup> Specified by design.

### 7.6 Audio Characteristics (BTL)

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 30 V, VDD = 5 V, GVDD = 5 V, R<sub>L</sub> = 4  $\Omega$ , f<sub>S</sub> = 480 kHz, T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, AD-Modulation, AES17 + AUX-0025 measurement filters, unless otherwise noted.

|                   | PARAMETER                                                   | TEST CONDITIONS                                                                   | MIN TYP | MAX | UNIT |  |

|-------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----|------|--|

|                   |                                                             | R <sub>L</sub> = 8 Ω, 10% THD+N                                                   | 60      |     |      |  |

|                   |                                                             | $R_L$ = 4 $\Omega$ , 10% THD+N, 1-channel, 5 s duration                           | 110     |     |      |  |

| Po                | Power output per channel                                    | R <sub>L</sub> = 8 Ω, 1% THD+N                                                    | 50      |     | w    |  |

| 10                | Tower output per channel                                    | $R_L$ = 4 $\Omega$ , 1% THD+N, 2-channels, 3 s duration                           | 89      |     | VV   |  |

|                   |                                                             | $R_L = 4 \Omega$ , 1% THD+N, 1-channel, 60 s duration                             | 89      |     |      |  |

| THD+N             | Total harmonic distortion + noise                           | 1 W                                                                               | 0.02    |     | %    |  |

| V <sub>n</sub>    | Output integrated noise                                     | A-weighted, AES17 filter, Input Capacitor<br>Grounded, Gain = 18 dB               | 72      |     | μV   |  |

| Vos               | Output offset voltage                                       | Inputs AC coupled to GND                                                          | 20      | 60  | mV   |  |

| SNR               | Signal-to-noise ratio <sup>(1)</sup>                        | A-weighted, Gain = 18 dB                                                          | 108     |     | dB   |  |

| DNR               | Dynamic range                                               | A-weighted, Gain = 18 dB                                                          | 109     |     | dB   |  |

| Б                 | Power dissipation due to idle losses (I <sub>PVDD_X</sub> ) | $P_{O}$ = 0, all outputs switching, AD-modulation, $T_{C}$ = 25°C <sup>(2)</sup>  | 0.55    |     | W    |  |

| P <sub>idle</sub> |                                                             | $P_O = 0$ , all outputs switching, HEAD-<br>modulation, $T_C = 25^{\circ}C^{(2)}$ | 0.38    |     | W    |  |

<sup>(1)</sup> SNR is calculated relative to 1% THD+N output level.

# 7.7 Audio Characteristics (PBTL)

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 30 V, VDD = 5 V, GVDD = 5 V, R<sub>L</sub> = 3  $\Omega$ , f<sub>S</sub> = 480 kHz, T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, Pre-Filter PBTL, AD-Modulation, AES17 + AUX-0025 measurement filters, unless otherwise noted.

|                   | PARAMETER                                      | TEST CONDITIONS                                                                   | MIN TYP | MAX | UNIT |  |

|-------------------|------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----|------|--|

|                   | Power output per channel                       | R <sub>L</sub> = 3 Ω, 10% THD+N                                                   | 155     |     |      |  |

| Po                |                                                | $R_L = 4 \Omega$ , 10% THD+N                                                      | 120     |     | 10/  |  |

|                   |                                                | $R_L = 3 \Omega$ , 1% THD+N                                                       | 125     |     | W    |  |

|                   |                                                | $R_L = 4 \Omega$ , 1% THD+N                                                       | 98      |     |      |  |

| THD+N             | Total harmonic distortion + noise              | 1 W                                                                               | 0.017   |     | %    |  |

| V <sub>n</sub>    | Output integrated noise                        | A-weighted, AES17 filter, Input Capacitor<br>Grounded, Gain = 18 dB               | 75      |     | μV   |  |

| V <sub>OS</sub>   | Output offset voltage                          | Inputs AC coupled to GND                                                          | 20      | 60  | mV   |  |

| SNR               | Signal to noise ratio <sup>(1)</sup>           | A-weighted, Gain = 18 dB                                                          | 108     |     | dB   |  |

| DNR               | Dynamic range                                  | A-weighted, Gain = 18 dB                                                          | 110     |     | dB   |  |

| P <sub>idle</sub> | Power dissipation due to idle losses (IPVDD_X) | $P_O = 0$ , all outputs switching, AD-<br>modulation, $T_C = 25^{\circ}C^{(2)}$   | 0.25    |     | W    |  |

|                   |                                                | $P_O = 0$ , all outputs switching, HEAD-<br>modulation, $T_C = 25^{\circ}C^{(2)}$ | 0.19    |     | W    |  |

<sup>(1)</sup> SNR is calculated relative to 1% THD+N output level.

<sup>(2)</sup> Actual system idle losses also are affected by core losses of output inductors.

<sup>(2)</sup> Actual system idle losses are affected by core losses of output inductors.

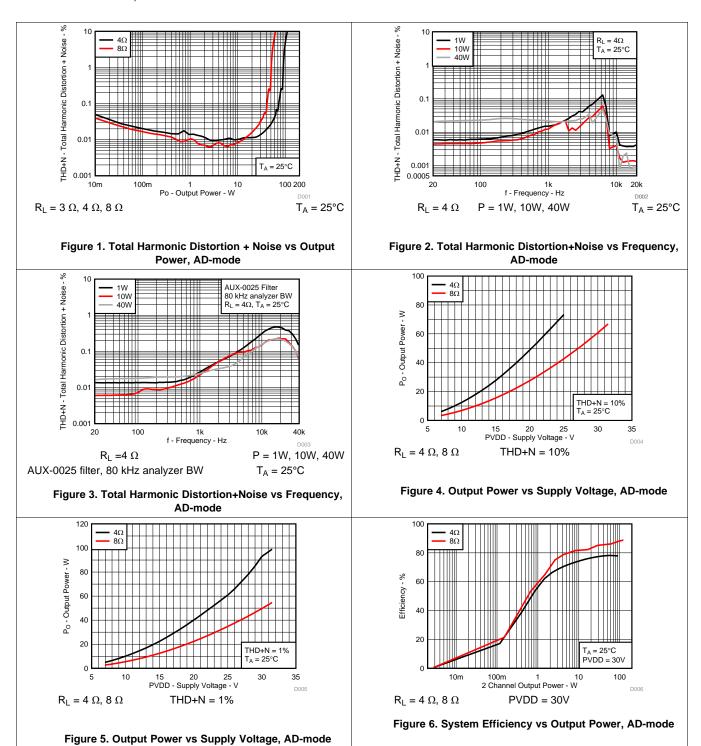

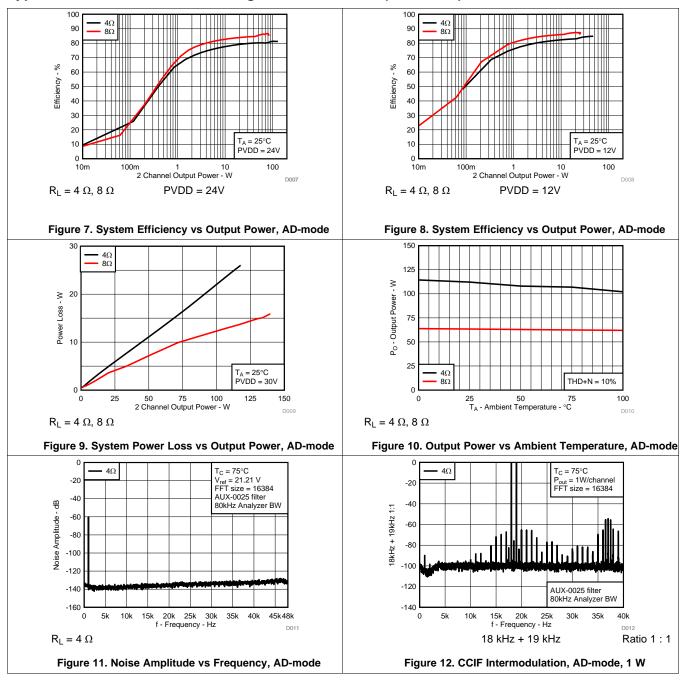

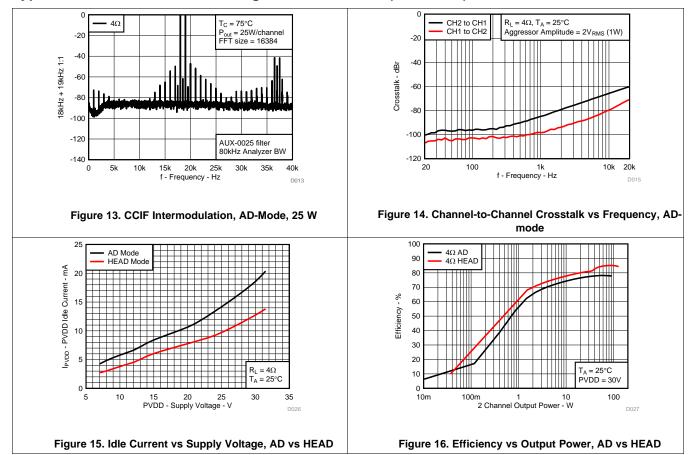

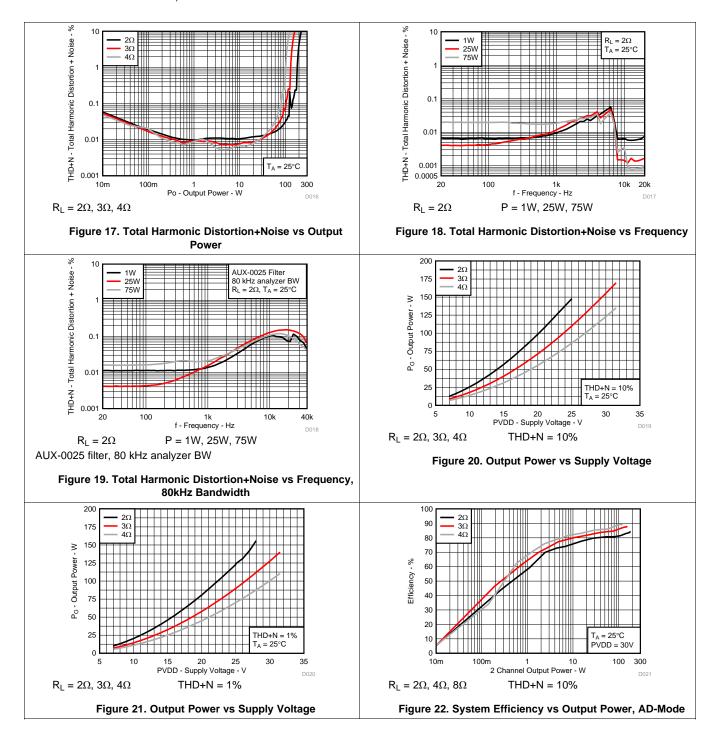

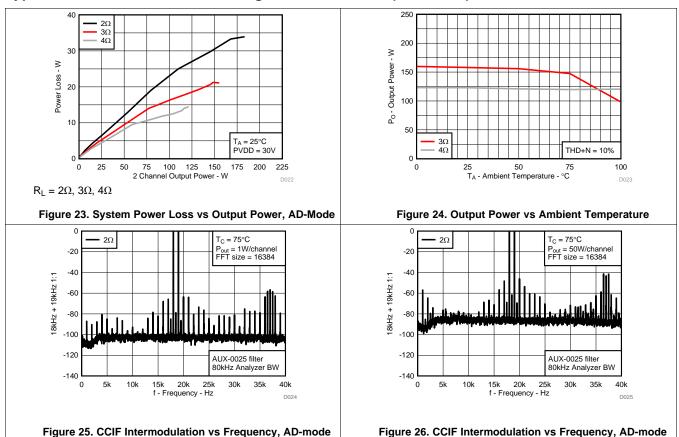

# 7.8 Typical Characteristics, BTL Configuration, AD-mode

All Measurements taken at audio frequency = 1 kHz, PVDD\_X = 30 V, VDD = 5 V, GVDD = 5 V, R\_L = 4  $\Omega$ , f\_S = 480 kHz,  $T_A$  = 25°C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ F, AD Modulation, AES17 + AUX-0025 measurement filters, unless otherwise noted.

# Typical Characteristics, BTL Configuration, AD-mode (continued)

# TEXAS INSTRUMENTS

# Typical Characteristics, BTL Configuration, AD-mode (continued)

# 7.9 Typical Characteristics, PBTL Configuration, AD-mode

All Measurements taken at audio frequency = 1 kHz, PVDD\_X = 30V, VDD = 5 V, GVDD = 5 V, R<sub>L</sub> =  $2\Omega$ , f<sub>S</sub> = 480 kHz, T<sub>A</sub> =  $25^{\circ}$ C, Output Filter: L<sub>DEM</sub> =  $10 \mu$ H, C<sub>DEM</sub> =  $1 \mu$ F, Pre-Filter PBTL, AD modulation, AES17 + AUX-0025 measurement filters, unless otherwise noted.

# Typical Characteristics, PBTL Configuration, AD-mode (continued)

#### 8 Parameter Measurement Information

All parameters are measured according to the conditions described in the *Recommended Operating Conditions*.

Most audio analyzers will not give correct readings of Class-D amplifiers' performance due to their sensitivity to out of band noise present at the amplifier output. AES-17 + AUX-0025 pre-analyzer filters are recommended to use for Class-D amplifier measurements. In absence of such filters, a 30-kHz low-pass filter (10  $\Omega$  + 47 nF) can be used to reduce the out of band noise remaining on the amplifier outputs.

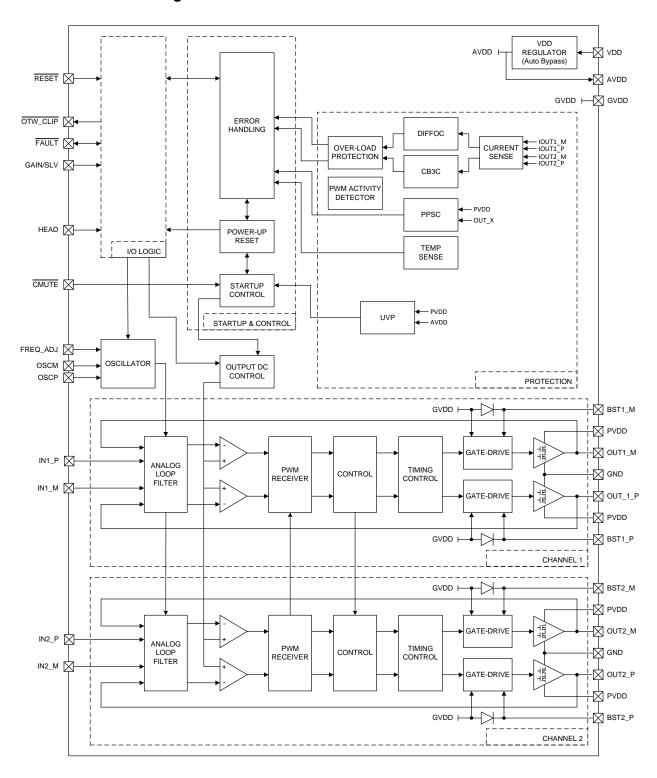

### 9 Detailed Description

#### 9.1 Overview

TPA3220 is designed as a feature-enhanced cost efficient high power Class-D audio amplifier. It has built-in advanced protection circuitry to ensure maximum product robustness as well as a flexible feature set including built in LDO for easy supply of low voltage circuitry, selectable gain, switching frequency, master/slave synchronization of multiple devices, selectable PWM modulation scheme, mute function, temperature and clipping status signals. TPA3220 has a bandwidth up to 100 kHz and low output noise designed for high resolution audio applications and accepts both differential and single ended analog audio inputs at levels from 1  $V_{RMS}$  to 2  $V_{RMS}$ . With its closed loop operation TPA3220 is designed for high audio performance with a system power supply between 7 V and 30 V.

To facilitate system design, the TPA3220 needs only a (typical) 30 V power stage supply. The TPA3220 has an internal voltage regulator supplied from the VDD pin for the analog and digital system blocks and the output stage gate drive respectively. The VDD pin can be connected directly to PVDD in case of only this power supply rail being available.

To reduce device power losses an external 5 V supply can be used for the AVDD and VDD supply pins. The internal voltage regulator connected to the VDD pin is automatically turned off if an external 5 V supply is used for this pin. Although supplied from the same 5 V source, separating AVDD and VDD on the printed-circuit board (PCB) by RC filters (see application diagram for details) is recommended. These RC filters provide the recommended high-frequency isolation. Special attention should be paid to placing all decoupling capacitors as close to their associated pins as possible. In general, the physical loop with the power supply pins, decoupling capacitors and GND return path to the device pins must be kept as short as possible and with as little area as possible to minimize induction (see *Layout Examples* for additional information).

The floating supplies for the output stage high side gate drives are supplied by built-in bootstrap circuitry requiring only an external capacitor for each half-bridge.

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BST\_X) to the power-stage output pin (OUT\_X). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD) and the bootstrap pins. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. It is recommended to use 33 nF ceramic capacitors, size 0603 or 0805, for the bootstrap supply. These 33 nF capacitors ensure sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of the PWM cycle.

Special attention should be paid to the power stage power supply; this includes component selection, PCB placement, and routing.

For optimal electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_X node is decoupled with 1  $\mu$ F ceramic capacitors placed as close as possible to the PVDD supply pins. It is recommended to follow the PCB layout of the TPA3220 reference design. For additional information on recommended power supply and required components, see the application diagrams in this data sheet.

If using external power supply for the AVDD and VDD internal regulators, this supply should be from a low-noise, low-output-impedance voltage regulator. Likewise, the 30 power stage supply is assumed to have low output impedance throughout the entire audio band, and low noise. The power supply sequence is not critical as facilitated by the internal power-on-reset circuit, but it is recommended to release RESET after the power supply is settled for minimum turn on audible artefacts. Moreover, the TPA3220 is fully protected against erroneous power-stage turn on due to parasitic gate charging. Thus, voltage-supply ramp rates (dV/dt) are noncritical within the specified range (see the *Recommended Operating Conditions* table of this data sheet).

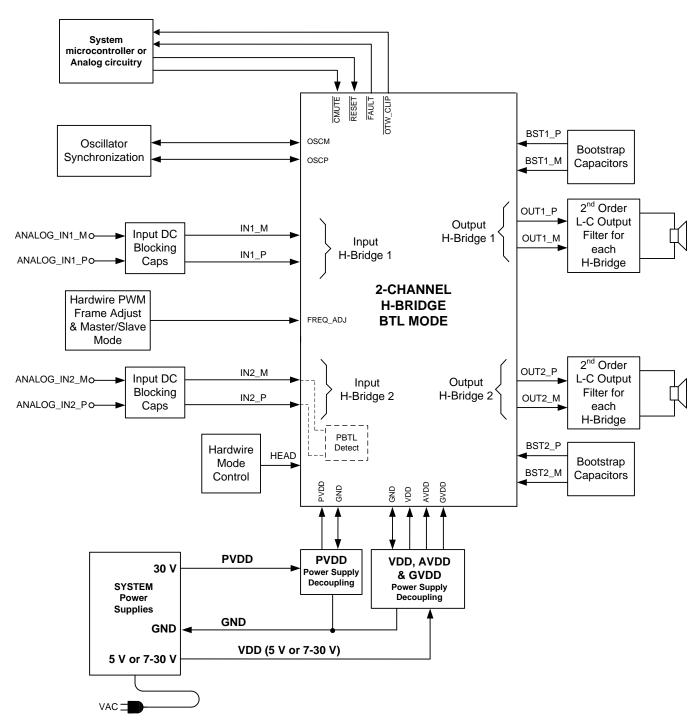

# 9.2 Functional Block Diagrams

# Functional Block Diagrams (接下页)

\*NOTE1: Logic AND in or outside microcontroller

图 27. System Block Diagram

### 9.3 Feature Description

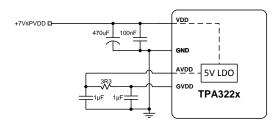

#### 9.3.1 Internal LDO

TPA3220 has a built in optional LDO (Low dropout voltage regulator) to supply the analog and digital circuits as well as the gate drive for the output stages. The LDO can be used in systems where only the high voltage power rail is available, hence no additional power supply rails need to be generated for the TPA3220 to operate. As being a linear regulator, the LDO will add to the power losses of the device due to the (PVDD-5V) voltage drop and the supply current for AVDD and GVDD given in the *Electrical Characteristics* table.

图 28. Internal LDO for Single Supply Systems

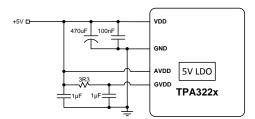

图 29. Internal LDO Bypass for Highest Power Efficiency

For highest system power efficiency the LDO can be bypassed by connecting VDD to an external 5 V supply. In this configuration AVDD and GVDD should be supplied by 5 V from the external power supply. GVDD should be supplied through a RC filter for best noise performance as shown in  $\boxtimes 29$ .

### 9.3.1.1 Input Configuration, Gain Setting And Master / Slave Operation

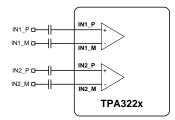

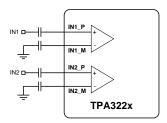

TPA3220 is designed to accept either a differential or a single-ended audio input signal. To accept a wide range of system front ends TPA3220 has selectable input gain that allows full scale output with a wide range of input signal levels.

Best system noise performance is obtained with balanced audio interface. However, to be used in systems with only a single ended audio input signal available, one input terminal can be connected to AC ground, to accept single ended audio input signals.

图 30. Balanced Audio Input Configuration

# Feature Description (接下页)

In systems with single ended audio inputs the device gain will typically need to be set higher than for systems with balanced audio input signals.

图 31. Single Ended Audio Input Configuration

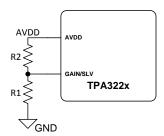

### 9.3.2 Gain Setting And Master / Slave Operation

The gain of TPA3220 is set by the voltage divider connected to the GAIN/SLV control pin. Master or Slave mode is also controlled by the same pin. An internal ADC is used to detect the 8 input states. The first four stages sets the GAIN in Master mode in gains of 18, 24, 30, 34 dB respectively, while the next four stages sets the GAIN in Slave mode in gains of 18, 24, 30, 34 dB respectively. The gain setting is latched when RESET goes high and cannot be changed while RESET is high. 表 2 shows the recommended resistor values, the state and gain:

表 2. Gain and Master / Slave

| Master / Slave<br>Mode | Gain  | R1 (to GND) | R2 (to AVDD) | Differential Input Signal Level (each input pin) | Single Ended Input Signal<br>Level |

|------------------------|-------|-------------|--------------|--------------------------------------------------|------------------------------------|

| Master                 | 18 dB | 5.6 kΩ      | OPEN         | 2 VRMS                                           | 2 VRMS                             |

| Master                 | 24 dB | 20 kΩ       | 100 kΩ       | 1 VRMS                                           | 2 VRMS                             |

| Master                 | 30 dB | 39 kΩ       | 100 kΩ       | 0.5 VRMS                                         | 1 VRMS                             |

| Master                 | 34 dB | 47 kΩ       | 75 kΩ        | 0.32 VRMS                                        | 0.63 VRMS                          |

| Slave                  | 18 dB | 51 kΩ       | 51 kΩ        | 2 VRMS                                           | 2 VRMS                             |

| Slave                  | 24 dB | 75 kΩ       | 47 kΩ        | 1 VRMS                                           | 2 VRMS                             |

| Slave                  | 30 dB | 100 kΩ      | 39 kΩ        | 0.5 VRMS                                         | 1 VRMS                             |

| Slave                  | 34 dB | 100 kΩ      | 16 kΩ        | 0.32 VRMS                                        | 0.63 VRMS                          |

图 32. Gain and Master / Slave Setup

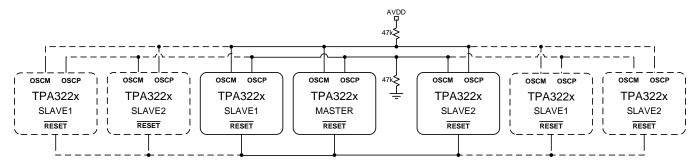

For easy multi-channel system design TPA3220 has a Master / Slave feature that allows automatic synchronization of multiple slave devices operated at the PWM switching frequency of a master device. This benefits system noise performance by eliminating spurious crosstalk sum and difference tones due to unsynchronized channel-to-channel switching frequencies. Furthermore the Master / Slave scheme is designed to interleave switching of the individual channels in a multi-channel system such that the power supply current ripple frequency is moved to a higher frequency which reduces the RMS ripple current in the power supply bulk capacitors.

The Master / Slave scheme and the interleaving of the output stage switching is automatically configured by connecting the OSCx pins between a master and multiple slave devices. Connect the OSCx pins in either positive or negative polarity to configure either a Slave1 or Slave2 device. Connect the OSCM of the Master device to the OSCM of a slave device to configure for Slave1 or OSCP to configure for Slave2. Then connect the remaining OSCx pins between the master and slave devices. The Master, Slave1 and Slave2 PWM switching will be 30 degrees out of phase with each other. All switching channels are automatically synchronized by releasing RESET on all devices at the same time.

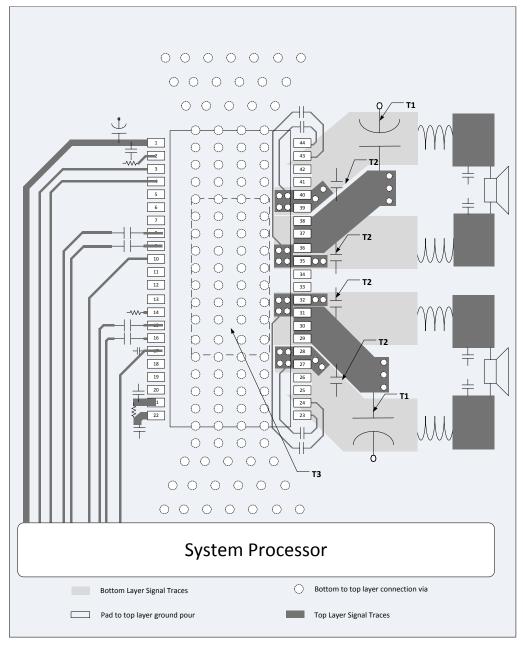

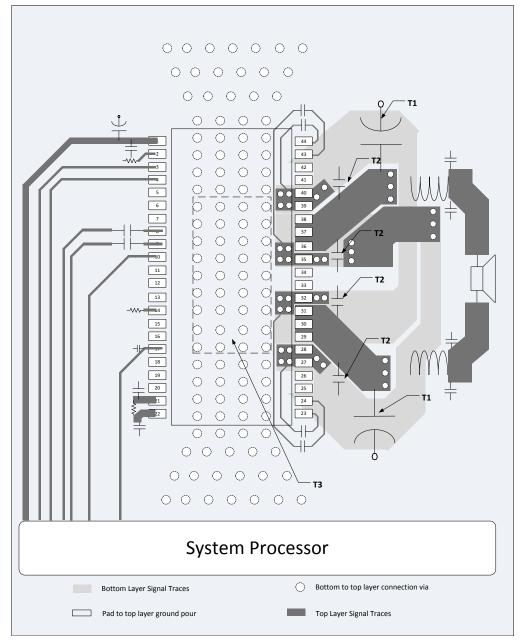

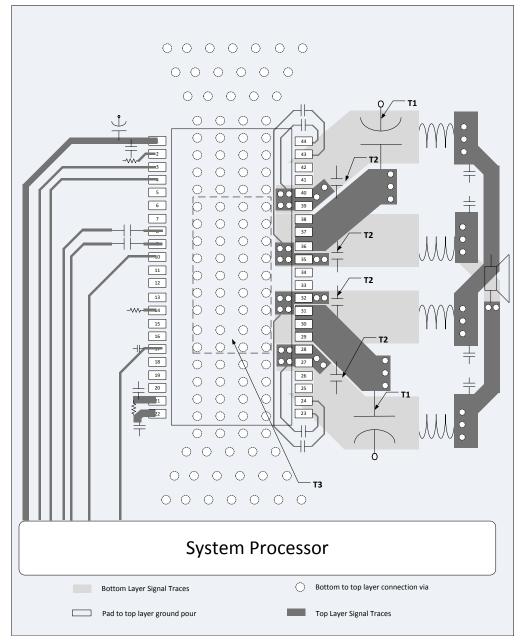

图 33. Gain and Master PCB Implementation

Placement on the PCB and connection of multiple TPA3220 devices in a multi channel system is illustrated in 33. Slave devices should be placed on either side of the master device, with a Slave1 device on one side of the Master device, and a Slave2 device on the other. In systems with more than 3 TPA3220 devices, the master should be in the middle, and every second slave devices should be a Slave1 or Slave 2 as illustrated in 33. A  $47k\Omega$  pull up resistor to AVDD should be connected to the master device OSCM output and a  $47k\Omega$  pull down resistor to GND should be connected to the master OSCP CLK outputs.

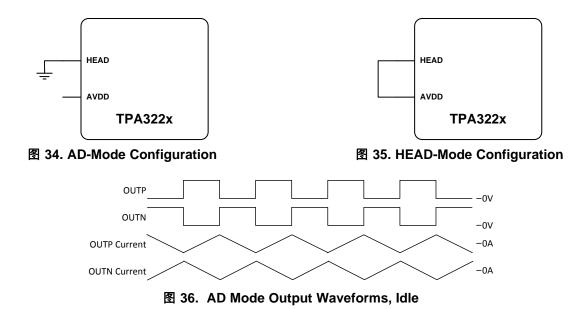

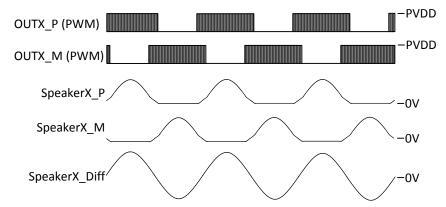

#### 9.3.3 AD-Mode and HEAD-Mode PWM Modulation

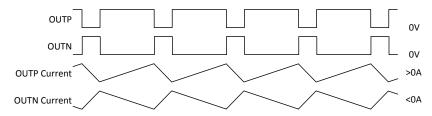

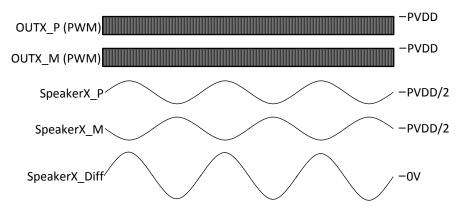

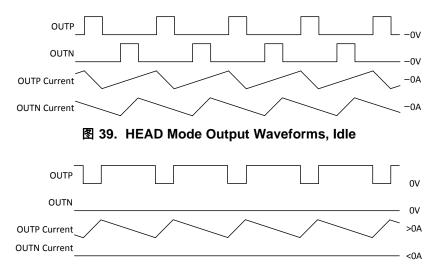

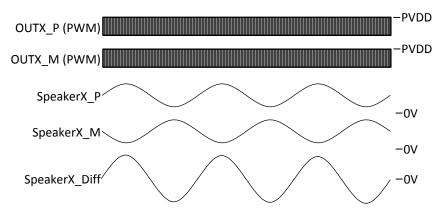

TPA3220 has the option of using either AD-Mode or HEAD-Mode PWM modulation scheme. AD mode has continuous switching of the two half bridge outputs in each BTL output channel. Both half bridge outputs are switching in HEAD mode, but with reduced duty cycle for idle operation and while playing small signals. With higher output levels one half bridge stops switching on HEAD mode operation. HEAD benefits both device power loss and EMI performance, where AD mode is considered to have the highest audio performance.

图 37. AD Mode Output Waveforms, High Level Output

图 38. AD Mode Speaker Output Signals, Low or and High Level Output

图 40. HEAD Mode Output Waveforms, High Level Output

图 41. HEAD Mode Speaker Output Signals, Low Level Output

图 42. HEAD Mode Speaker Output Signals, High Level Output

#### 9.3.4 Oscillator

The oscillator frequency can be trimmed by external control of the FREQ\_ADJ pin.

To reduce interference problems while using radio receiver tuned within the AM band, the switching frequency can be changed from nominal to higher values. These values should be chosen such that the nominal and the higher value switching frequencies together results in the fewest cases of interference throughout the AM band. The oscillator frequency can be selected by the value of the FREQ\_ADJ resistor connected to GND in master mode according to the description in the *Recommended Operating Conditions* table.

For slave mode operation, turn off the oscillator by pulling the FREQ\_ADJ pin to AVDD. This configures the OSC\_I/O pins as inputs to be slaved from an external differential clock. In a master/slave system inter channel delay is automatically setup between the switching of the audio channels, which can be illustrated by no idle channels switching at the same time. This will not influence the audio output, but only the switch timing to minimize noise coupling between audio channels through the power supply to optimize audio performance and to get better operating conditions for the power supply. The inter channel delay will be setup for a slave device depending on the polarity of the OSC\_I/O connection such that a slave mode 1 is selected by connecting the master device OSC\_I/O to the slave 1 device OSC\_I/O with same polarity (+ to + and - to -), and slave mode 2 is selected with the inverse polarity (+ to - and - to +).

### 9.3.5 Input Impedance

The TPA3220 input stage is a fully differential input stage and the input impedance changes with the gain setting from 7.7 k $\Omega$  at 34 dB gain to 47 k $\Omega$  at 18 dB gain. Table 1 lists the values from min to max gain. The tolerance of the input resistor value is  $\pm 20$  % so the minimum value will be higher than 6.2 k $\Omega$ . The inputs need to be AC-coupled to minimize the output DC-offset and ensure correct ramping of the output voltages during power-ON and power-OFF. The input ac-coupling capacitor together with the input impedance forms a high-pass filter with the following cut-off frequency:

If a flat bass response is required down to 20 Hz the recommended cut-off frequency is a tenth of that, 2 Hz.  $\frac{1}{8}$  3 lists the recommended ac-couplings capacitors for each gain step. If a -3 dB is accepted at 20 Hz 10 times lower capacitors can used – for example, a 1  $\mu$ F can be used.

| Gain  | Input Impedance | Input AC-Coupling Capacitance | Input High Pass Filter |

|-------|-----------------|-------------------------------|------------------------|

| 18 dB | 48 kΩ           | 4.7 µF                        | 0.7 Hz                 |

| 24 dB | 24 kΩ           | 10 μF                         | 0.7 Hz                 |

| 30 dB | 12 kΩ           | 10 μF                         | 1.3 Hz                 |

| 34 dB | 7.7 kΩ          | 10 μF                         | 2.1 Hz                 |

表 3. Recommended Input AC-Coupling Capacitors

The input capacitors used should be a type with low leakage, like quality electrolytic, tantalum, film or ceramic. If a polarized type is used the positive connection should face such that the capacitor has a positive DC bias.

### 9.3.6 Error Reporting

The FAULT, and OTW\_CLIP, pins are active-low, open-drain outputs. The FAULT function is for protection-mode signaling to a system-control device. Any fault resulting in device shutdown is signaled by the FAULT pin going low. Also, OTW\_CLIP goes low when the device junction temperature exceeds 125°C (see  $\frac{1}{8}$  4).

表 4. Error Reporting

| FAULT | OTW_CLIP | DESCRIPTION                                                                                                                     |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0        | Overtemperature (OTE), overload (OLP), or undervoltage (UVP). Junction temperature higher than 125°C (overtemperature warning). |

| 0     | 1        | Overload (OLP) or undervoltage (UVP). Junction temperature lower than 125°C                                                     |

| 1     | 0        | Junction temperature higher than 125°C (overtemperature warning)                                                                |

| 1     | 1        | Junction temperature lower than 125°C and no OLP or UVP faults (normal operation)                                               |

Note that asserting RESET low forces the FAULT signal high, independent of faults being present. TI recommends monitoring the OTW\_CLIP signal using the system microcontroller and responding to an overtemperature warning signal by turning down the volume to prevent further heating of the device resulting in device shutdown (OTE).

To reduce external component count, an internal pullup resistor to 3.3 V is provided on both FAULT and OTW\_CLIP outputs.

#### 9.4 Device Functional Modes

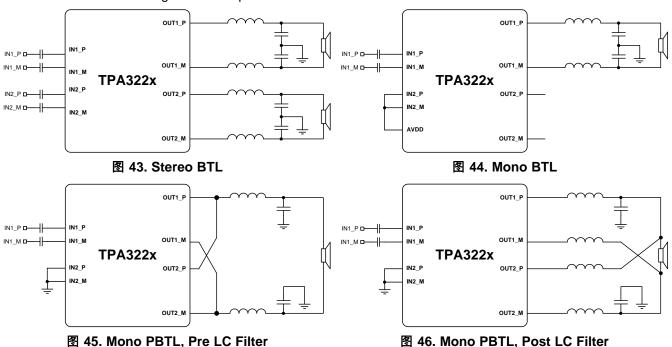

TPA3220 can be configured in either a stereo BTL (Bridge Tied Load) mode, mono BTL mode (only one output BTL channel active), or in a mono PBTL (Parallel Bridge Tied Load) mode. In PBTL mode the two output BTL channels are parallelled with double output current available. The parallelling of the two BTL outputs can be made either before the output LC filter, or after the output LC filter. For PBTL mode the audio performance will in general be higher when parallelling before the output LC filter, but parallelling after the LC output filter may be preferred in some systems.

See Table 1 for mode configuration setup.

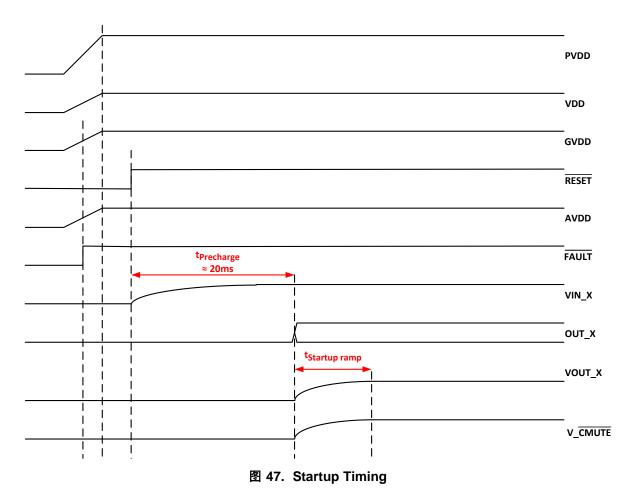

#### 9.4.1 Powering Up

The TPA3220 does not require a power-up sequence because of the integrated undervoltage protection (UVP), but it is recommended to hold RESET low until PVDD supply voltage is stable to avoid audio artifacts. The outputs of the H-bridges remain in a high-impedance state until the gate-drive supply (GVDD) and AVDD voltages are above their UVP voltage thresholds (see the *Electrical Characteristics* table of this data sheet). This allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pull-down of the half-bridge output as well as initiating a controlled ramp up sequence of the output voltage.

When RESET is released to turn on TPA3220, FAULT signal will turn low and AVDD voltage regulator will be enabled. FAULT will stay low until AVDD reaches the undervoltage protection (UVP) voltage threshold (see the Electrical Characteristics table of this data sheet). After a pre-charge time to stabilize the DC voltage across the input AC coupling capacitors, the ramp up sequence starts and completes once the CMUTE node is charged to its final value.

### 9.4.1.1 Startup Ramp Time

During the startup ramp the CMUTE capacitor is charged by an internal current generator. With use of the recommended 33 nF CMUTE capacitor value, the startup ramp time is approximately 20 ms. Higher CMUTE capacitor value will increase the ramp time, and a lower value will decrease the ramp time. The recommended CMUTE capacitor value is selected for minimum audible artifacts during startup and shutdown ramp.

#### 9.4.2 Powering Down

The TPA3220 does not require a power-down sequence. The device remains fully operational as long as the VDD, AVDD and PVDD voltages are above their undervoltage protection (UVP) voltage thresholds (see the *Electrical Characteristics* table of this data sheet). Although not specifically required, it is a good practice to hold RESET low during power down, thus preventing audible artifacts including pops or clicks by initiating a controlled ramp down sequence of the output voltage. The ramp down sequence will complete once the CMUTE node is discharged.

#### 9.4.2.1 Power Down Ramp Time

During the power down ramp the  $\overline{\text{CMUTE}}$  capacitor is discharged by internal circuitry. With use of the recommended 33 nF  $\overline{\text{CMUTE}}$  capacitor value, the power-down ramp time is approximately 20 ms.

#### 9.4.3 Device Reset

Asserting RESET low initiates the device ramp down. The output FETs go into a <u>Hi-Z state</u> after the ramp down is complete. Output pull downs are active in both BTL mode and PBTL mode with RESET low.

In BTL modes, to accommodate bootstrap charging prior to switching start, asserting the RESET input low enables weak pull-down of the half-bridge outputs.

Asserting RESET low removes any fault information to be signaled on the FAULT output, that is, FAULT is forced high. A rising-edge transition on RESET allows the device to resume operation after a fault. To ensure thermal reliability, the rising edge of RESET must occur no sooner than 4 ms after the falling edge of FAULT.

The TPA3220 will enter a low power state once the ramp down sequence is complete.

#### 9.4.4 Device Soft Mute

Asserting CMUTE low initiates the device soft mute function. The soft mute function initiates a ramp down sequence of the outputs, and the output FETs go into a Hi-Z state after the ramp down is complete. All internal circuits are powered while in soft mute state. External control of the soft mute function must provide high impedance output when not engaged (open drain output) to allow the CMUTE node to charge/discharge during device ramp up and ramp down when de-asserting and asserting RESET.

### 9.4.5 Device Protection System

The TPA3220 contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overload, overtemperature and undervoltage. The TPA3220 responds to a fault by immediately setting the power stage in a high-impedance (Hi-Z) state and asserting the FAULT pin low. In situations other than overload and overtemperature error (OTE), the device automatically recovers when the fault condition has been removed, that is, the supply voltage has increased. The device will handle errors, as shown in 表 5.

**BTL MODE PBTL MODE LOCAL ERROR IN TURNS OFF LOCAL ERROR IN TURNS OFF** Α Α A+B В В A+B+C+D С С C+D D D

表 5. Device Protection

Bootstrap UVP does not shutdown according to the table, it shuts down the respective halfbridge (non-latching, does not assert FAULT).

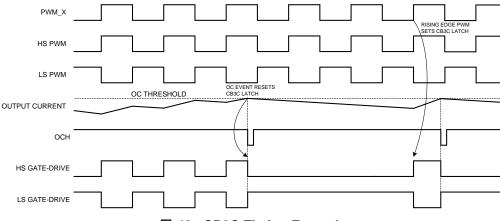

#### 9.4.5.1 Overload and Short Circuit Current Protection

TPA3220 has fast reacting current sensors on all high-side and low-side FETs. To prevent output current from increasing beyond the overcurrent threshold, TPA3220 uses current limiting of the output current for each switching cycle (Cycle By Cycle Current Control, CB3C) in case of excess output current. CB3C prevents premature shutdown due to high output current transients caused by high level music transients and a drop of real speaker's load impedance, and allows the output current to be limited to a maximum programmed level. If the maximum output current persists, i.e. the power stage being overloaded with too low load impedance, the device will shut down the affected output channel and the affected output is put in a high-impedance (Hi- Z) state until a RESET cycle is initiated. CB3C works individually for each full-bridge output. If an over current event is triggered, CB3C performs a state flip of the full-bridged output that is cleared upon beginning of next PWM frame.

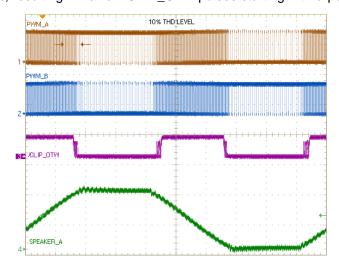

图 48. CB3C Timing Example

# 9.4.5.2 Signal Clipping and Pulse Injector

A built in activity detector monitors the PWM activity of the OUT\_X pins. TPA3220 is designed to drive unclipped output signals all the way to PVDD and GND rails. In case of audio signal clipping when applying excessive input signal voltage, or in case of CB3C current protection being active, the amplifier feedback loop of the audio channel will respond to this condition with a saturated state, and the output PWM signals will stop unless special circuitry is implemented to handle this situation. To prevent the output PWM signals from stopping in a clipping or CB3C situation, narrow pulses are injected to the gate drive to maintain output activity. The injected narrow pulses are injected at every 4<sup>th</sup> PWM frame, and thus the effective switching frequency during this state is reduced to 1/4 of the normal switching frequency.

Signal clipping is signalled on the OTW\_CLIP pin and is self clearing when signal level reduces and the device reverts to normal operation. The OTW\_CLIP pulses starts at the onset to output clipping, typically at a THD level around 0.01%, resulting in narrow OTW\_CLIP pulses starting with a pulse width of ~500ns.

图 49. Signal Clipping PWM and Speaker Output Signals

### 9.4.5.3 DC Speaker Protection

The output DC protection scheme protects a speaker from excess DC current in case one terminal of the speaker is connected to the amplifier while the other is accidentally shorted to the chassis ground. Such a short circuit results in a DC voltage of PVDD/2 across the speaker, which potentially can result in destructive current levels. The output DC protection detects any unbalance of the output and input current of a BTL or PBTL output configuration (current into/out of one half-bridge equals current out of/into the other half-bridge), and in the event of the unbalance exceeding a programmed threshold, the overload counter increments until its maximum value and the affected output channel is shut down. DC Speaker Protection is enabled in both BTL and PBTL mode operation.

### 9.4.5.4 Pin-to-Pin Short Circuit Protection (PPSC)