🚽 Order

Now

#### TMDS171, TMDS1711

ZHCSEG5E - OCTOBER 2015 - REVISED SEPTEMBER 2017

# TMDS171/I 3.4Gbps TMDS 重定时器

# 1 特性

- 高清多媒体接口 (HDMI) 输入端口与输出端口间具 有时钟和数据恢复 (CDR) 电路,支持高达

3.4Gbps 的数据传输速率

- 兼容 HDMI1.4b 电气参数。

- 支持 4k2k30p 和高达 WUXGA 12 位色深或 1080p,具有更高的刷新率™

- 对输入流重新定时以补偿随机抖动

- 自适应接收器均衡器或可编程固定均衡器

- I<sup>2</sup>C和引脚设置可编程

- 5+ 位对内偏移补偿

- 包括眼图的链路调试工具, 位于 RX 均衡器之后

- 支持单端模式 ARC

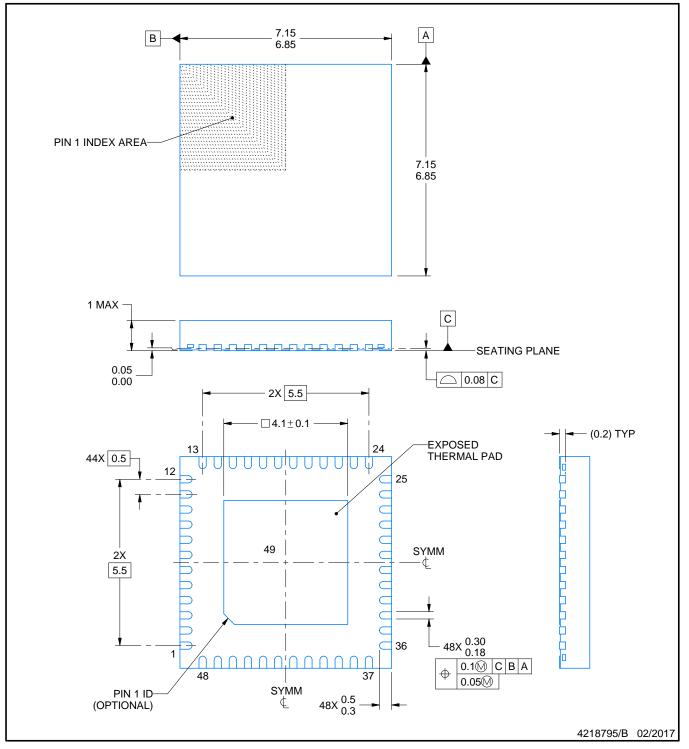

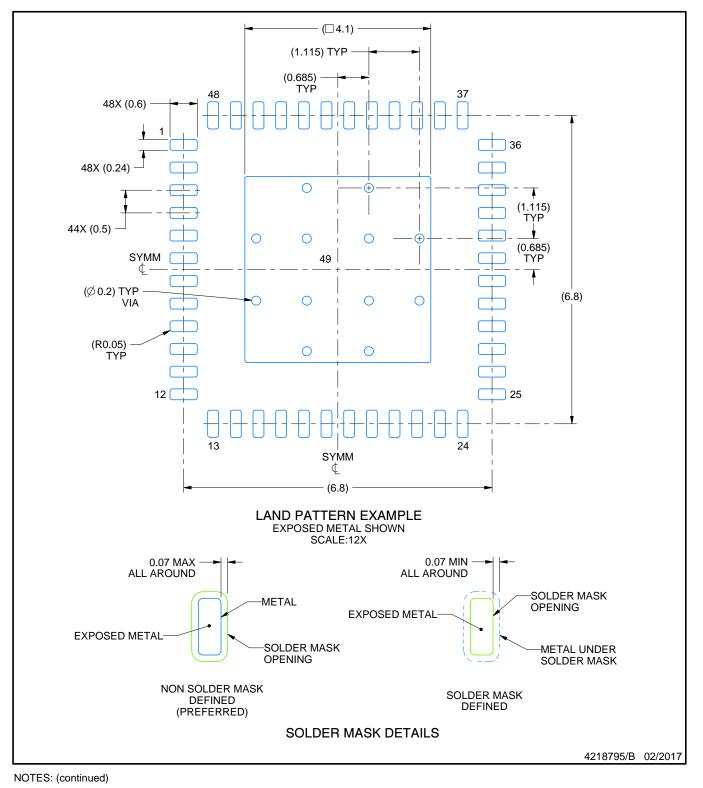

- 48 引脚 7mm x 7mm 0.5mm 间距超薄型四方扁平 无引线 (VQFN) 封装

- 扩展商业温度范围为 0°C 至 85°C (TMDS171)

- 工业温度范围为 -40℃ 至 85℃ (TMDS171I)

# 2 应用

- 数字电视

- 数字投影仪

- 音频/视频设备

- 蓝光 (Blu-Ray) DVD

- 监视器

- 台式机/一体化计算机

- 有源线缆

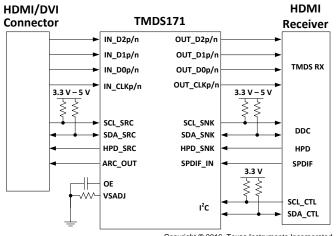

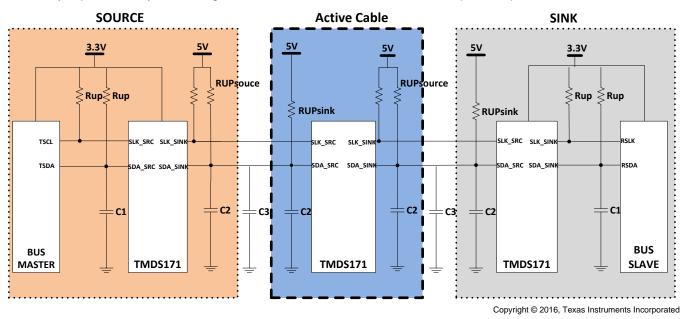

#### 简化电路原理图

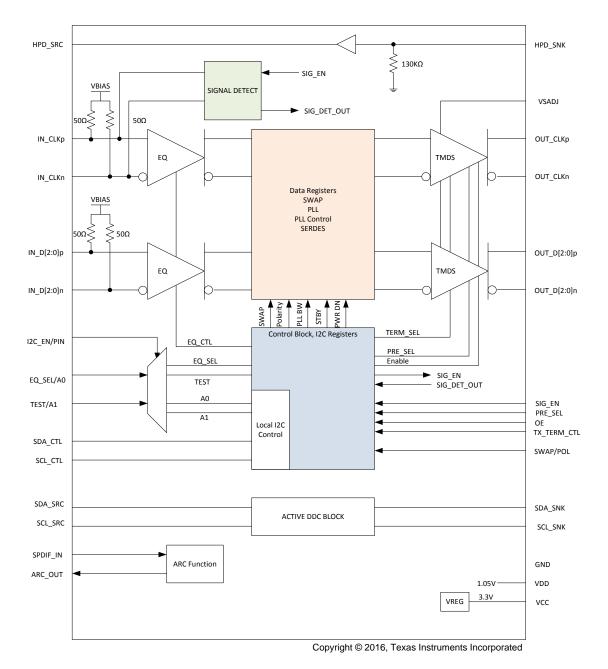

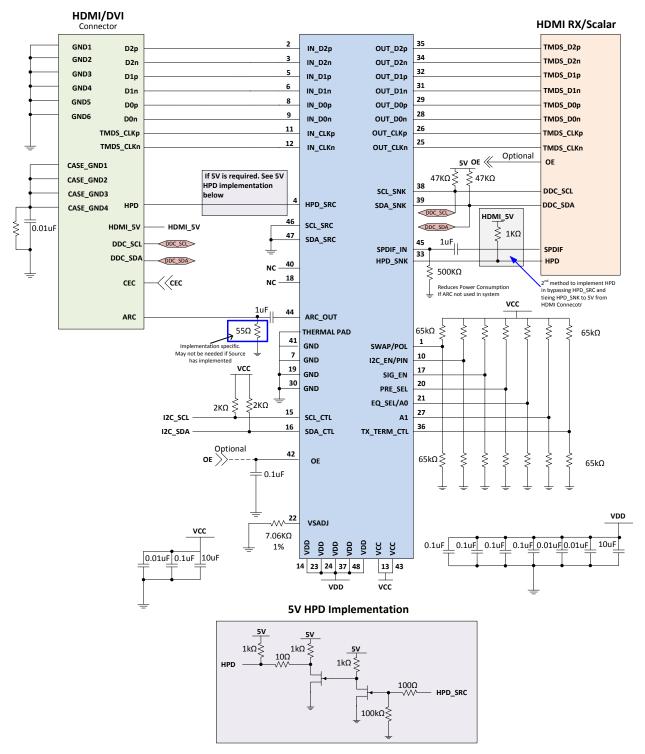

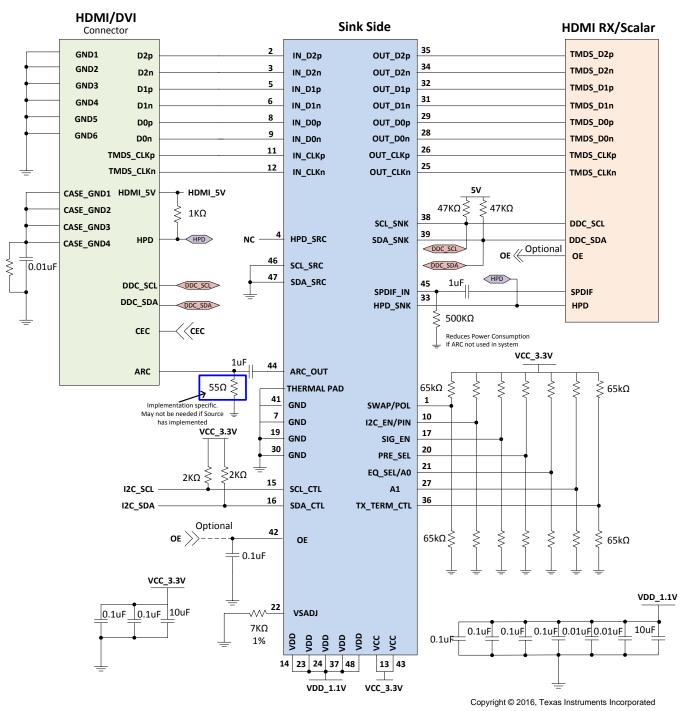

TMDS171 是一款数字视频接口 (DVI) 或高清多媒体接口 (HDMI) 重定时器。TMDS171 支持四条 TMDS 通道,音频返回通道 (SPDIF\_IN/ARC\_OUT)、热插拔检测 (HPD) 和数字显示控制 (DDC) 接口。TMDS171 支持高达 3.4Gbps 的信号传输速率,可实现最高分辨率达 4k2k30p 24 位/像素和高达 WUXGA 12 位色深或1080p,并且具有较高的刷新率。TMDS171 在低于1Gbps 的数据速率下会自动配置为重驱动器,而在高于该速率时会自动配置为重定时器。

TMDS171 支持双电源轨(VDD 为 1.2V, VCC 为 3.3V),有助于降低功耗。该器件采用多种电源管理 方法来降低整体功耗。TMDS171x 通过 I<sup>2</sup>C 或引脚设 置支持固定的 EQ 增益或自适应 EQ 控制,以补偿不 同长度的输入电缆或电路板走线。

器件信息(1)

| 器件型号     | 封装           | 封装尺寸(标称值)       |  |  |

|----------|--------------|-----------------|--|--|

| TMDS171  |              | 7.00mm v 7.00mm |  |  |

| TMDS171I | (VQFN) 48 引脚 | 7.00mm x 7.00mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

53

#### TMDS171, TMDS1711 ZHCSEG5E-OCTOBER 2015-REVISED SEPTEMBER 2017

# 目录

| 应用       1       8.5       Register Maps       30         说明       1       1       8.5       Register Maps       30         修订历史记录       2       2       9       Application and Implementation       43         9       Application and Implementation       43       9.1       Application Information       43         9       Application and Implementation       43       9.1       Application Information       43         9       Application Information       43       9.1       Application Information       43         9.1       Application Information       43       9.2       Source Side Application       45         9.1       Absolute Maximum Ratings       6       6       6       9.3       System Examples       49         10       Power Supply Recommendations       50       11       Layout       52         11.1       Layout Guidelines       52       11.1       Layout Example       53         12       Betailed Description       12       Taken       54         12.2       Byoyate Example       54       54         12.3       At@@@       54         12.4       mak       54         12.4 <th>特性1</th> <th>8.4 Device Functional Modes</th> <th> 28</th> | 特性1                  | 8.4 Device Functional Modes      | 28               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------|------------------|

| 说明19Application and Implementation43修订历史记录29Application and Implementation43Pin Configuration and Functions49Application Information43Specifications69.1Application Information439.1Application and Implementation439.2Source Side Application439.3System Examples499.3System Examples499.4Power Supply Recommendations506.2ESD Ratings66.3Recommended Operating Conditions76.4Thermal Information76.5Electrical Characteristics106.6Switching Characteristics106.7Typical Characteristics12Parameter Measurement Information12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 应用1                  | 8.5 Register Maps                | 30               |

| 修订历史记录2Pin Configuration and Functions4Specifications66.1 Absolute Maximum Ratings66.2 ESD Ratings66.3 Recommended Operating Conditions76.4 Thermal Information76.5 Electrical Characteristics86.6 Switching Characteristics10712Parameter Measurement Information129.1 Application Information439.2 Source Side Application459.3 System Examples499.4 Opener Supply Recommendations509.5 Electrical Characteristics71012Parameter Measurement Information12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | 9 Application and Implementation | 43               |

| Pin Configuration and Functions4Specifications66.1 Absolute Maximum Ratings66.2 ESD Ratings66.3 Recommended Operating Conditions76.4 Thermal Information76.5 Electrical Characteristics86.6 Switching Characteristics1071271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271271213121412.11512161217121812191210121012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 9.1 Application Information      | 43               |

| Specifications66.1 Absolute Maximum Ratings66.1 Absolute Maximum Ratings66.2 ESD Ratings66.3 Recommended Operating Conditions76.4 Thermal Information76.5 Electrical Characteristics86.6 Switching Characteristics10712Parameter Measurement Information129.3 System Examples499.4 Power Supply Recommendations5010 Power Supply Recommendations5211 Layout5211.1 Layout Guidelines5211.2 Layout Example5312 器件和文档支持5412.1 相关文档5412.3 社区资源5412.4 直后5412.3 社区资源54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | 9.2 Source Side Application      | 45               |

| 6.1Absolute Maximum Ratings66.2ESD Ratings66.3Recommended Operating Conditions76.4Thermal Information76.5Electrical Characteristics86.6Switching Characteristics106.7Typical Characteristics12Parameter Measurement Information12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                    | 9.3 System Examples              | 49               |

| 6.2ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                    | 10 Power Supply Recommendations  | 50               |

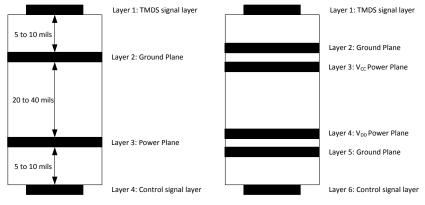

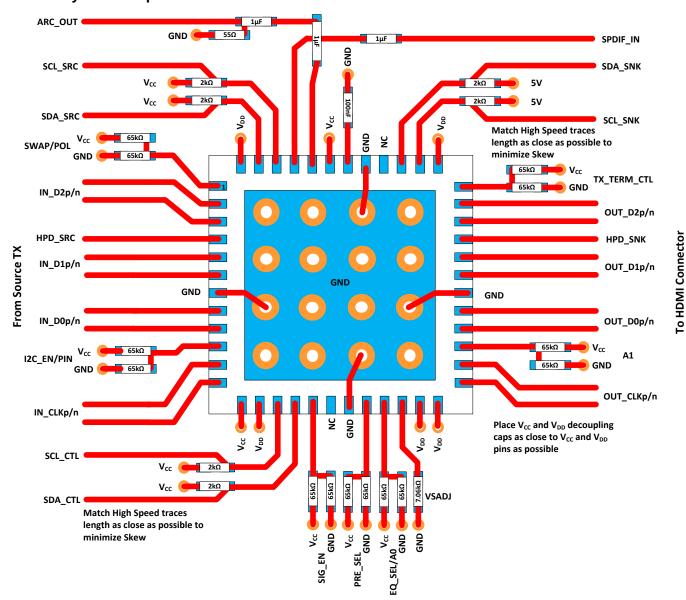

| 6.3 Recommended Operating Conditions       7         6.4 Thermal Information       7         6.4 Thermal Information       7         6.5 Electrical Characteristics       8         6.6 Switching Characteristics       10         6.7 Typical Characteristics       12         Parameter Measurement Information       12         12       社区资源         12       社区资源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C C                  | 11 Layout                        | <mark>52</mark>  |

| 6.4Thermal Information711.2Layout Example536.5Electrical Characteristics812器件和文档支持546.6Switching Characteristics101212.1相关文档546.7Typical Characteristics1212指关文档54Parameter Measurement Information1212指以交档更新通知541212接收文档更新通知541212.3社区资源54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                    | 11.1 Layout Guidelines           | <mark>52</mark>  |

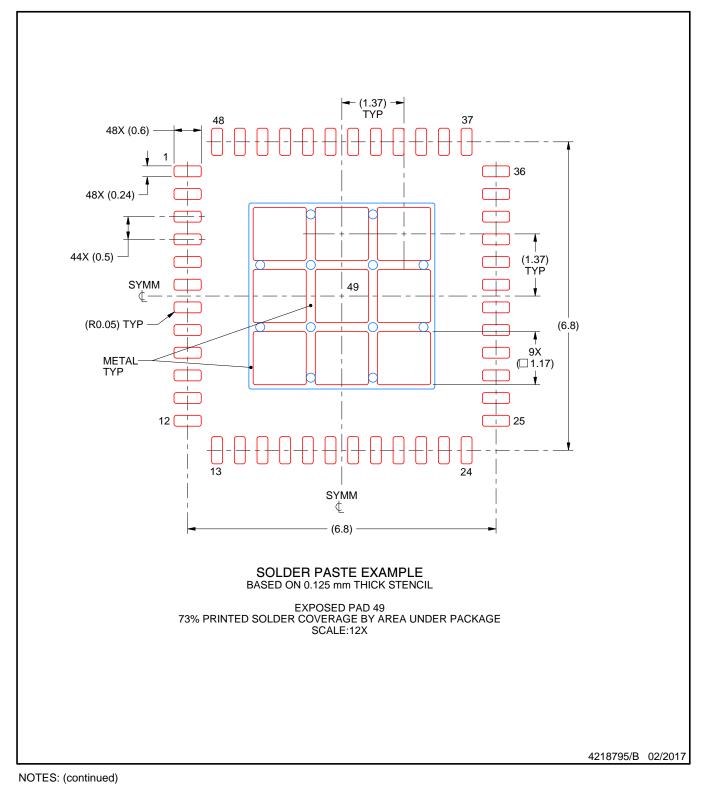

| 6.5 Electrical Characteristics       8       12 器件和文档支持       54         6.6 Switching Characteristics       10       12       指关文档       54         6.7 Typical Characteristics       12       12       指关文档       54         Parameter Measurement Information       12       12       指以文档更新通知       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | 11.2 Layout Example              | <mark>53</mark>  |

| 6.6 Switching Characteristics       10       12.1 相关文档       54         6.7 Typical Characteristics       12       12       接收文档更新通知       54         Parameter Measurement Information       12       12.3 社区资源       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 12 器件和文档支持                       | 54               |

| 6.7 Typical Characteristics       12       12.2 接收文档更新通知       54         Parameter Measurement Information       12       12.3 社区资源       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 12.1 相关文档                        | <mark>54</mark>  |

| Parameter Measurement Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                    | 12.2 接收文档更新通知                    | <mark>5</mark> 4 |

| 40.4 幸福                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | 12.3 社区资源                        | <mark>54</mark>  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Detailed Description | 12.4 商标                          | 54               |

# 4 修订历史记录

1 2

3

4

5

6

7

8

| Cł | hanges from Revision D (August 2016) to Revision E                                                          |                  |

|----|-------------------------------------------------------------------------------------------------------------|------------------|

| •  | Added Note 3 to the Electrical Characteristics table                                                        | 8                |

| •  | Deleted text "which is needed for certain HDMI CTS test." from the second paragraph in the Overview section | 20               |

| •  | Changed section: Input Signal Detect Block                                                                  | 25               |

| •  | Changed H to X in the first row of the HPD_SNK column in Table 36                                           | <mark>5</mark> 1 |

| •  | Changed the IN_Dx column in Table 36                                                                        | 51               |

# Changes from Revision C (April 2016) to Revision D

8.1 Overview ...... 20 8.2 Functional Block Diagram ...... 21

8.3 Feature Description...... 21

| • | Recommended Operating Conditions, Changed the CONTROL PINS section | 7 |

|---|--------------------------------------------------------------------|---|

| • | Electrical Characteristics Changed the DDC and I2C section         | 9 |

# Changes from Revision B (February 2016) to Revision C

| • | Changed pin 36 Description From: TX_TERM_CTL = L: 150 - 300 $\Omega$ To: TX_TERM_CTL = L: Reserved in the <i>Pin Functions</i> table                           | 6  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added OE to VIL "Low-level input voltage" in the Recommended Operating Conditions table                                                                        | 7  |

| • | Added OE to V <sub>IH</sub> "High-level input voltage" in the <i>Recommended Operating Conditions</i> table                                                    | 7  |

| • | Changed Figure 23                                                                                                                                              | 22 |

| • | Deleted the VDD_ramp and VCC_ramp MIN values in Table 1                                                                                                        | 23 |

| • | Changed TX_TERM_CTL = L to Reserved in Table 3                                                                                                                 | 25 |

| • | Changed text "address 22h through the I <sup>2</sup> C interface" To: "address 0Bh through the I <sup>2</sup> C interface" <i>DDC Functional Description</i> . | 29 |

| • | Added Note to 11-400-kbps in Table 8                                                                                                                           | 32 |

| • | Added Note to 11-400-kbps in Table 10                                                                                                                          | 34 |

|   |                                                                                                                                                                |    |

#### www.ti.com.cn

|    | 8.5 I | Register Maps 30             |

|----|-------|------------------------------|

| 9  | Appli | cation and Implementation 43 |

|    | 9.1 / | Application Information 43   |

|    | 9.2   | Source Side Application 45   |

|    | 9.3   | System Examples 49           |

| 10 | Powe  | er Supply Recommendations 50 |

| 11 | Layo  | ut                           |

|    | 11.1  | Layout Guidelines            |

|    | 11.2  | Layout Example               |

| 12 | 器件和   | 和文档支持 54                     |

|    | 12.1  | 相关文档 54                      |

|    | 12.2  | 接收文档更新通知 54                  |

|    | 12.3  | 社区资源                         |

|    | 12.4  | 商标54                         |

|    | 12.5  | 静电放电警告54                     |

|    | 12.6  | Glossary                     |

| 13 | 机械、   | 封装和可订购信息54                   |

# STRUMENTS

# Page

# Page

ZHCSEG5E - OCTOBER 2015-REVISED SEPTEMBER 2017

| С | hanges from Revision A (December 2015) to Revision B                                                                             | Page    |

|---|----------------------------------------------------------------------------------------------------------------------------------|---------|

| • | Changed Pin 44 From: AUX_SRCn To: ARC_OUT Pin 45 From: AUX_SRCn To: SPDIF_IN in the <i>Pin Configuration and Functions</i> image | on<br>4 |

| С | hanges from Original (October 2015) to Revision A                                                                                | Page    |

| • | 已将器件状态从"产品预览"更改为"量产数据"                                                                                                           | 1       |

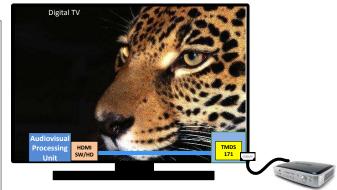

# 5 Pin Configuration and Functions

#### TMDS171, TMDS1711

ZHCSEG5E -OCTOBER 2015-REVISED SEPTEMBER 2017

#### **Pin Functions**

| Pin Functions                          |                     |                    |                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------|---------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                        | PIN                 | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |

| NAME                                   | NO.                 |                    |                                                                                                                                                                                                                                                                                             |  |

| VCC                                    | 13, 43              | P                  | 3.3 V Power Supply                                                                                                                                                                                                                                                                          |  |

| VDD                                    | 14, 23, 24, 37, 48  | Р                  | 1.2 V Power Supply                                                                                                                                                                                                                                                                          |  |

| GND                                    | 7, 19, 41, 30       | G                  | Ground                                                                                                                                                                                                                                                                                      |  |

| Thermal Pad                            |                     | G                  | Ground                                                                                                                                                                                                                                                                                      |  |

| MAIN LINK INPUT                        | PINS (FAIL SAFE)    |                    |                                                                                                                                                                                                                                                                                             |  |

| IN_D2p/n                               | 2, 3                | I                  | Channel 2 Differential Input                                                                                                                                                                                                                                                                |  |

| IN_D1p/n                               | 5, 6                | I                  | Channel 1 Differential Input                                                                                                                                                                                                                                                                |  |

| IN_D0p/n                               | 8, 9                | I                  | Channel 0 Differential Input                                                                                                                                                                                                                                                                |  |

| IN_CLKp/n                              | 11, 12              | I                  | Clock Differential Input                                                                                                                                                                                                                                                                    |  |

| MAIN LINK OUTPU                        | JT PINS (FAIL SAFE) |                    |                                                                                                                                                                                                                                                                                             |  |

| OUT_D2n/p                              | 34, 35              | 0                  | TMDS Data 2 Differential Output                                                                                                                                                                                                                                                             |  |

| OUT_D1n/p                              | 31, 32              | 0                  | TMDS Data 1 Differential Output                                                                                                                                                                                                                                                             |  |

| OUT_D0n/p                              | 28, 29              | 0                  | TMDS Data 0 Differential Output                                                                                                                                                                                                                                                             |  |

| OUT_CLKn/p                             | 25, 26              | 0                  | TMDS Clock Differential Output                                                                                                                                                                                                                                                              |  |

| HOT PLUG DETEC                         |                     |                    |                                                                                                                                                                                                                                                                                             |  |

| HPD_SRC                                | 4                   | 0                  | Hot Plug Detect Output to source side                                                                                                                                                                                                                                                       |  |

| HPD_SNK                                | 33                  | 1                  | Hot Plug Detect Input from sink side                                                                                                                                                                                                                                                        |  |

| _                                      | HANNEL and DDC PINS |                    |                                                                                                                                                                                                                                                                                             |  |

| SPDIF_IN                               | 45                  | 1                  | SPDIF signal input                                                                                                                                                                                                                                                                          |  |

| ARC_OUT                                | 44                  | 0                  | Audio return channel output                                                                                                                                                                                                                                                                 |  |

| SDA_SRC                                | 47                  | I/O                | Source Side TMDS Port Bidirectional DDC Data line                                                                                                                                                                                                                                           |  |

| SCL_SRC                                | 46                  | I/O                | Source Side TMDS Port Bidirectional DDC Clock line                                                                                                                                                                                                                                          |  |

|                                        | 39                  | I/O                | Sink Side TMDS Port Bidirectional DDC Data Line                                                                                                                                                                                                                                             |  |

| SDA_SNK,                               |                     |                    |                                                                                                                                                                                                                                                                                             |  |

| SCL_SNK<br>CONTROL PINS <sup>(2)</sup> | 38                  | I/O                | Sink Side TMDS Port Bidirectional DDC Clock Line                                                                                                                                                                                                                                            |  |

| CONTROL PINS                           |                     |                    |                                                                                                                                                                                                                                                                                             |  |

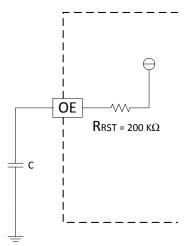

| OE                                     | 42                  | I                  | Operation Enable/Reset Pin<br>OE = L: Power Down Mode<br>OE = H: Normal Operation<br>Internal weak pull up: Resets device when transitions from H to L                                                                                                                                      |  |

| SIG_EN                                 | 17                  | I                  | Signal detector circuit enable<br>SIG_EN = L: Signal Detect Circuit Disabled: Term resistors always connected (Default)<br>SIG_EN = H: Signal Detect Circuit Enabled: When no valid clock device enters Standby<br>Mode.<br>Internal weak pull down                                         |  |

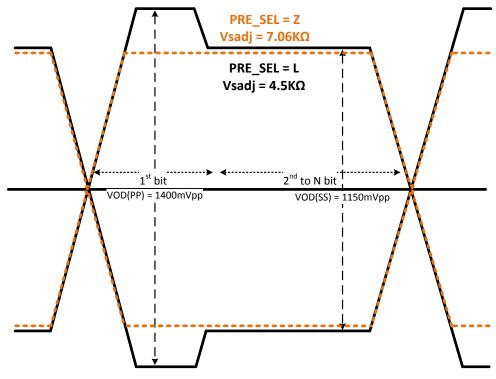

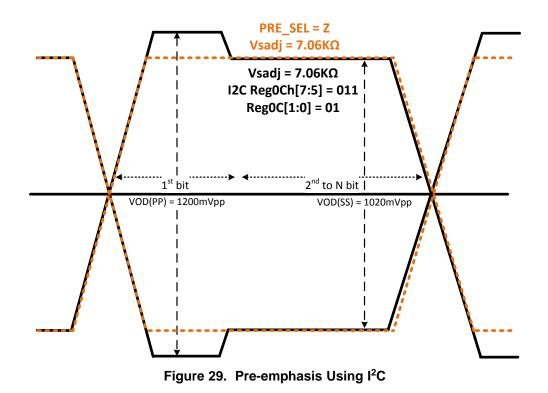

| PRE_SEL                                | 20                  | l<br>3-Level       | De-emphasis Control when I2C_EN/PIN = Low.<br>PRE_SEL = L: -2 dB<br>PRE_SEL = No Connect: 0 dB<br>PRE_SEL = H: Reserved<br>When I2C_EN/PIN = High; De-emphasis is controlled through I <sup>2</sup> C                                                                                       |  |

| EQ_SEL/A0                              | 21                  | I                  | Input Receive Equalization pin strap when I2C_EN/PIN = Low<br>EQ_SEL = L: Fixed EQ at 7.5 dB<br>EQ_SEL = No Connect: Adaptive EQ<br>EQ_SEL = H: Fixed at 14 dB<br>When I2C_EN/PIN = High Address Bit 1<br>Note: 3 level for pin strap programming but 2 level when I <sup>2</sup> C address |  |

| I2C_EN/PIN                             | 10                  | I                  | I2C_EN/PIN = High; Puts Device into I2C Control Mode<br>I2C_EN/PIN = Low; Puts Device into Pin Strap Mode                                                                                                                                                                                   |  |

| SCL_CTL                                | 15                  | I/O                | $\rm I^2C$ Clock Signal when $\rm I^2C\_EN/PIN$ = High. Note: When I2C\_EN = Low; Pin strapping takes priority and those functions cannot be changed by $\rm I^2C$                                                                                                                          |  |

| SDA_CTL                                | 16                  | I/O                | $\rm I^2C$ Data Signal when $\rm I^2C\_EN/PIN$ = High Note: When $\rm I2C\_EN$ = Low; Pin strapping takes priority and those functions cannot be changed by $\rm I^2C$                                                                                                                      |  |

| VSadj                                  | 22                  | Ι                  | TMDS Output Voltage Swing Control; Nominal 7.06 k $\Omega$ Resistor to GND                                                                                                                                                                                                                  |  |

(1) (1) G = Ground, I = Input, O = Output, P = Power (2) (H) Logic High (Pin strapped to VCC through 65 k $\Omega$  resistor); (L) Logic Low (Pin strapped to GND through 65 k $\Omega$  resistor); (Mid-Level = No connect)

#### TMDS171, TMDS171I ZHCSEG5E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com.cn

STRUMENTS

XAS

# Pin Functions (continued)

| P           | IN     | I/O <sup>(1)</sup> | DECODIDITION                                                                                                                                                                                                                                                                                                                             |

|-------------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.    | 1/0("/             | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

| A1          | 27     | I                  | High address bit 2 for I <sup>2</sup> C programming<br>Weak internal pull down.<br>Note: When I2C_EN/PIN = Low for Pin Strapping Mode leave this pin as No connect                                                                                                                                                                       |

| TX_TERM_CTL | 36     | l<br>3-Level       | Transmit Termination Control<br>TX_TERM_CTL = H: No transmit Termination<br>TX_TERM_CTL = L: Reserved<br>TX_TERM_CTL = No Connect: Automatically selects the termination impedance<br>2 Gbps > DR $\leq$ 3.4 Gbps – 150 - 300 $\Omega$ differential near end termination<br>DR < 2 Gbps – no termination<br>DR < 2 Gbps – no termination |

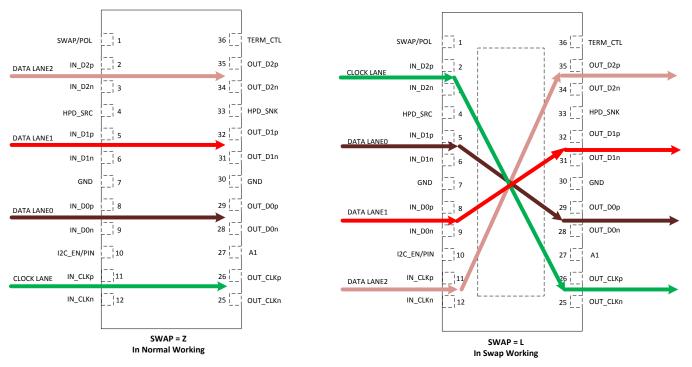

| SWAP/POL    | 1      | l<br>3-Level       | Receive Polarity Swap and Receive Lane Swap control pin<br>SWAP/POL = H: Receive Lanes Polarity Swap (Retimer Mode Only)<br>SWAP/POL = L: Receive Lanes (Retimer and Redriver Mode)<br>Swap SWAP/POL = No Connect, Normal Operation                                                                                                      |

| NC          | 18, 40 | -                  | No connect                                                                                                                                                                                                                                                                                                                               |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                       |                                                                                                      | MIN                      | MAX                     | UNIT |

|---------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|------|

| Supply Voltage Range                  | VCC                                                                                                  | -0.3                     | 4                       |      |

|                                       | VDD                                                                                                  | -0.3                     | 1.4                     |      |

| Voltage Range                         | Main Link Input Differential Voltage (IN_Dx, IN_CLKx); I <sub>IN</sub> = 15mA                        | V <sub>CC</sub> - 0.75 V | V <sub>CC</sub> + 0.3 V |      |

|                                       | TMDS Outpus ( OUT_Dx)                                                                                | -0.3                     | 4                       | V    |

|                                       | HPD_SRC, Vsadj, SDA_CTL, SCL_CTL, OE, A1,<br>PRE_SEL, EQ_SEL/A0, I2C_EN/PIN, SIG_EN,<br>TX_TERM_CTL, | -0.3                     | 4                       |      |

|                                       | HDP_SNK, SDA_SNK, SCL_SNK, SDA_SRC, SCL_SRC                                                          | -0.3                     | 6                       |      |

| Input Current I <sub>IN</sub>         | Main Link Input Differential Voltage (IN_Dx, IN_CLKx);                                               |                          | 15                      | mA   |

| Continuous power dissipation          | n                                                                                                    | See Therma               | I Information           |      |

| Storage temperature, T <sub>stg</sub> |                                                                                                      | -65                      | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-B

# 6.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                |                                                                                                                   | MIN       | NOM  | MAX       | UNIT |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------|------|-----------|------|

| V <sub>CC</sub>                | Supply Voltage Nominal Value 3.3 V                                                                                | 3.135     | 3.3  | 3.465     | V    |

| V <sub>DD</sub>                | Supply Voltage Nominial Value 1.2 V                                                                               | 1.1       | 1.2  | 1.27      | V    |

| T <sub>STG</sub>               | Storage temperature                                                                                               | -65       |      | 150       | °C   |

| T <sub>CASE</sub>              | Case temperature                                                                                                  |           |      | 92.7      | °C   |

| <b>-</b>                       | Operating free-air temperature (TMDS171)                                                                          | 0         |      | 85        | °C   |

| T <sub>A</sub>                 | Operating free-air temperature (TMDS171I)                                                                         | -40       |      | 85        | °C   |

|                                | CONFERENTIAL PINS                                                                                                 |           |      | 4         |      |

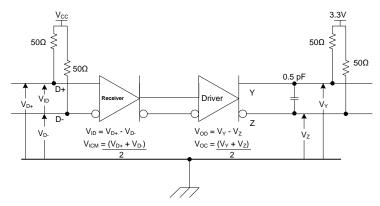

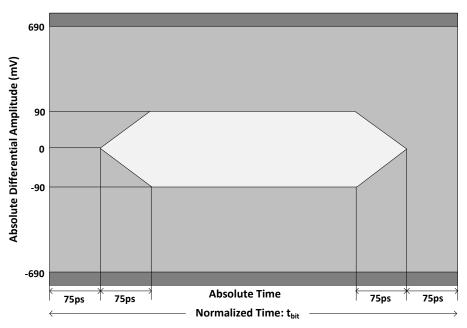

| V <sub>ID(PP)</sub>            | Peak-to-peak input differential voltage                                                                           | 75        |      | 1560      | mVpp |

| V <sub>IC</sub>                | Input Common Mode Voltage                                                                                         | VCC - 0.4 |      | VCC + 0.1 | V    |

| d <sub>R</sub>                 | Data rate                                                                                                         | 0.25      |      | 3.4       | Gbps |

| R <sub>(VSADJ)</sub>           | TMDS compliant swing voltage bias resistor 1%                                                                     |           | 7.06 |           | KΩ   |

| CONTROL                        | PINS                                                                                                              | L         |      | I         |      |

| V <sub>I(DC)</sub>             | DC Input Voltage                                                                                                  | -0.3      |      | 3.6       | V    |

|                                | Low-level input voltage OE                                                                                        |           |      | 0.8       | V    |

| V <sub>IL</sub> <sup>(1)</sup> | Low-level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL, SWAP/POL pins only <sup>(1)</sup>                     |           |      | 0.3       | V    |

| V <sub>IM</sub> <sup>(1)</sup> | Mid-Level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL, SWAP/POL pins only <sup>(1)</sup>                     | 1         | 1.2  | 1.4       | V    |

| V <sub>IH</sub> <sup>(1)</sup> | High-level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL, SWAP/POL, OE <sup>(2)</sup> pins only <sup>(1)</sup> | 2.6       |      |           | V    |

| V <sub>OL</sub>                | Low-level output voltage                                                                                          |           |      | 0.4       | V    |

| V <sub>OH</sub>                | High-level output voltage                                                                                         | 2.4       |      |           | V    |

| I <sub>IH</sub>                | High level input current                                                                                          | 30        |      | 30        | μA   |

| IIL                            | Low level input current                                                                                           | -25       |      | 25        | μΑ   |

| l <sub>os</sub>                | Short circuit output current                                                                                      | -50       |      | 50        | mA   |

| l <sub>oz</sub>                | High impedance output current                                                                                     |           |      | 10        | μA   |

| R <sub>(OEPU)</sub>            | Pull up resistance on OE pin                                                                                      | 150       |      | 250       | KΩ   |

(1) These values are based upon a microcontroller driving the control pins. The pull up/down/floating resistor configuration will set control pins properly which will have a different value than shown due to internal biasing. This value is based upon a microcontroller driving the OE pin. A passive reset circuit using an external capacitor and the internal pullup

(2) resistor will set OE pin properly, but may have a different value than shown due to internal biasing.

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | RGZ (QFN) |               |

|-----------------------|----------------------------------------------|-----------|---------------|

|                       |                                              | 48 PINS   | UNIT          |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 31.1      |               |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.2      |               |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.1       | 8 <b>0</b> AM |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4       | °C/W          |

| Ψјв                   | Junction-to-board characterization parameter | 8.1       |               |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.2       |               |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report.

ZHCSEG5E-OCTOBER 2015-REVISED SEPTEMBER 2017

# www.ti.com.cn

#### 6.5 Electrical Characteristics

The Maximum rating is simulated at 3.465 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature. The Typical rating is simulated at 3.3 V<sub>CC</sub> and 1.2 V V<sub>DD</sub> and at 27°C temperature (unless otherwise noted)

|                                         | PARAMETER                                                       | TEST CONDIT                                                                                  | TIONS                                 | MIN                        | TYP      | MAX                        | UNIT |

|-----------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|----------------------------|----------|----------------------------|------|

| Power Supply                            |                                                                 |                                                                                              |                                       |                            |          |                            |      |

| P <sub>(D1)</sub> <sup>(1)(2)</sup>     | Device power Dissipation (Retimer Operation)                    | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V, V <sub>DI</sub><br>IN_Dx: VID_PP = 1200 mV, I2C_E |                                       |                            | 675      | 875                        | mW   |

| P <sub>(D2)</sub> <sup>(1)(2)</sup>     | Device power Dissipation (Redriver Operation)                   | EQ_CTL= H, SDA_CTL/CLK_CTL<br>3.4 Gbps TMDS pattern, $V_1 = 3.3$ V                           |                                       |                            | 400      | 600                        | mW   |

| P <sub>(SD1)</sub> <sup>(1)(2)(3)</sup> | Device power in Standby                                         |                                                                                              |                                       |                            | 50       | 100                        | mW   |

| P <sub>(SD2)</sub> <sup>(1)(2)(3)</sup> | Device power in PowerDown                                       | OE = L, V <sub>CC</sub> = 3.3 V / 3.465 V<br>V <sub>DD</sub> = 1.2 V / 1.27 V                |                                       |                            | 10       | 30                         | mW   |

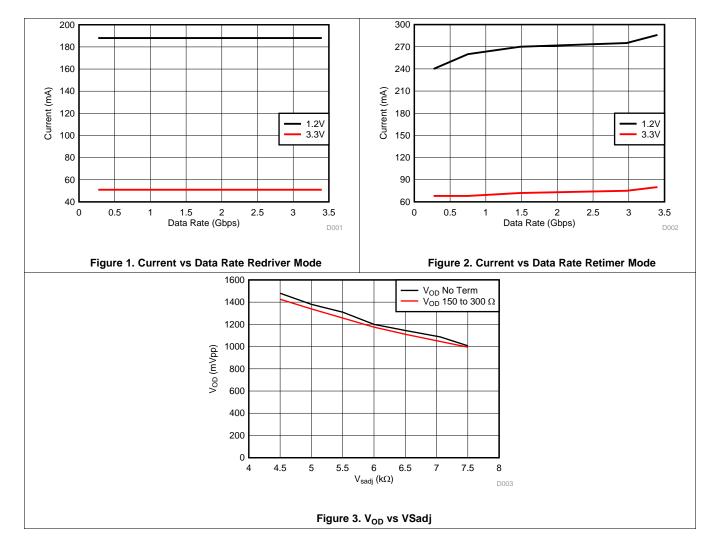

| I <sub>CC1</sub> <sup>(1)(2)</sup>      | V <sub>CC</sub> Supply current (TMDS 3.4<br>Gpbs Retimer Mode)  | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V<br>V <sub>DD</sub> = 1.2 V / 1.27 V                |                                       |                            | 80       | 140                        | mA   |

| I <sub>DD1</sub> <sup>(1) (2)</sup>     | V <sub>DD</sub> Supply current (TMDS 3.4<br>Gpbs Retimer Mode)  | IN_Dx: VID_PP = 1200 mV,<br>3.4 Gbps TMDS pattern I2C_EN/P<br>EQ_CTL = H, SDA_CTL/CLK_CTL    |                                       |                            | 286      | 325                        | mA   |

| I <sub>CC2</sub> <sup>(1)(2)</sup>      | V <sub>CC</sub> Supply current (TMDS 3.4<br>Gpbs Redriver Mode) | $OE = H, V_{CC} = 3.3 V / 3.465 V$ $V_{DD} = 1.2 V / 1.27 V$                                 |                                       |                            | 51       |                            | mA   |

| I <sub>DD2</sub> <sup>(1)(2)</sup>      | V <sub>DD</sub> Supply current (TMDS 3.4<br>Gpbs Redriver Mode) | IN_Dx: VID_PP = 1200 mV,<br>3.4 Gbps TMDS pattern I2C_EN/P<br>EQ_CTL = H, SDA_CTL/CLK_CTL    |                                       |                            | 188      |                            | mA   |

|                                         |                                                                 | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V                                                    | 3.3V Rail <sup>(1)</sup>              |                            | 6        | 15                         |      |

| I <sub>(SD1)</sub> <sup>(3)</sup>       | Standby current                                                 | $V_{DD} = 1.2 V / 1.27 V$<br>HPD = H: No valid signal on<br>IN_CLK                           | 1.2V Rail                             |                            | 40       | 50                         | mA   |

| I <sub>(SD2)</sub> <sup>(3)</sup>       | PowerDown current                                               | OE = L, V <sub>CC</sub> = 3.3 V / 3.465 V<br>V <sub>DD</sub> = 1.2 V / 1.27 V                | 3.3V Rail <sup>(1)</sup><br>1.2V Rail |                            | 2<br>3.5 | 5<br>15                    | mA   |

| TMDS Different                          | ial Input                                                       |                                                                                              | 1.2 V I (dii                          |                            | 5.5      | 15                         |      |

| D <sub>(R_RX_DATA)</sub>                | TMDS data lanes data rate                                       |                                                                                              |                                       | 0.25                       |          | 3.4                        | Gbps |

| D <sub>(R_RX_CLK)</sub>                 | TMDS clock lanes clock rate                                     |                                                                                              |                                       | 25                         |          | 340                        | MHz  |

|                                         | Input clock duty circle                                         |                                                                                              |                                       | 40%                        | 50%      | 60%                        |      |

| t <sub>CLK_JIT</sub>                    | Input clock jitter tolerance                                    |                                                                                              |                                       |                            |          | 0.3                        | Tbit |

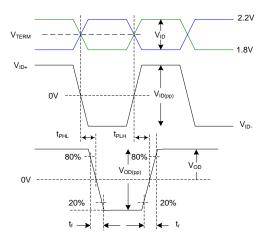

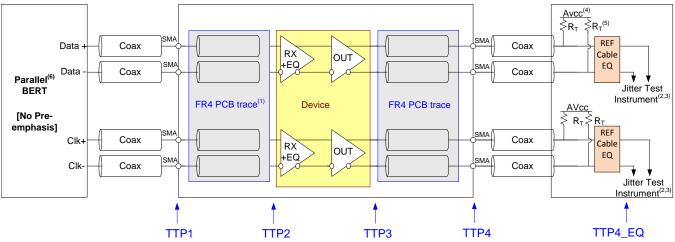

| t <sub>DATA_JIT</sub>                   | Input data jitter tolerance                                     | Test the TTP2 See Figure 11                                                                  |                                       |                            |          | 150                        | ps   |

| t <sub>RX_INTRA</sub>                   | Input intra-pair skew tolerance                                 | Test at TTP2 when DR = 1.6 Gbps                                                              | See Figure 11                         | 112                        |          |                            | ps   |

| t <sub>RX_INTER</sub>                   | Input inter-pair skew tolerance                                 |                                                                                              |                                       |                            |          | 1.8                        | ns   |

| E <sub>QH(D)</sub>                      | Fixed EQ gain for data lane<br>IN_D(0,1,2)n/p                   | EQ_SEL/A0=H; Fixed EQ gain, tes                                                              | st at 3.4 Gbps                        |                            | 14       |                            |      |

| E <sub>QL(D)</sub>                      | Fixed EQ gain for data lane<br>IN_D(0,1,2)n/p                   | EQ_SEL/A0=L; Fixed EQ gain, tes                                                              | t at 3.4 Gbps                         |                            | 7.5      |                            | dB   |

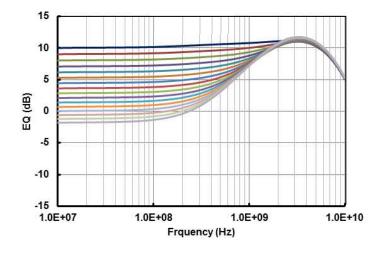

| E <sub>QZ(D)</sub>                      | Adaptive EQ gain for data lane<br>IN_D(0,1,2)n/p                | EQ_SEL/A0=NC; adaptive EQ                                                                    |                                       | 2                          |          | 14                         | uВ   |

| E <sub>Q(C)</sub>                       | EQ gain for clock lane<br>IN_CLKn/p                             | EQ_SEL/A0=H,LNC                                                                              |                                       |                            | 0        |                            |      |

| R <sub>(INT)</sub>                      | Input differential termination<br>impedance                     |                                                                                              |                                       | 90                         | 100      | 115                        | Ω    |

| TMDS Different                          | ial Output                                                      | 1                                                                                            |                                       |                            |          |                            |      |

| V <sub>OH</sub>                         | Single-ended high level output                                  | PRE_SEL = NC; TX_TERM_CTL = Mbps; VSadj = 7.06 k $\Omega$                                    | = H; OE = H; DR = 750                 | V <sub>CC</sub> -<br>10mV  |          | V <sub>CC</sub> +<br>10mV  |      |

| - OH                                    | voltage                                                         | PRE_SEL = NC; TX_TERM_CTL =<br>Gbps; VSadj = 7.06 kΩ                                         | = H; OE = NC; DR = 2.97               | V <sub>CC</sub> -<br>200mV |          | V <sub>CC</sub> +<br>10mV  | V    |

| V <sub>OL</sub>                         | Single-ended low level output voltage No Pre-emphasis,          | PRE_SEL = NC; TX_TERM_CTL =<br>Mbps; VSadj = 7.06 kΩ                                         | = H; OE = H; DR = 750                 | V <sub>CC</sub> -<br>600mV |          | V <sub>CC</sub> -<br>400mV | v    |

| - UL                                    | Load is 50 $\Omega$ pull ups to 3.135 V and 3.465 V             | PRE_SEL = NC; TX_TERM_CTL =<br>Gbps; VSadj = 7.06 kΩ                                         | = H; OE = NC; DR = 2.97               | V <sub>CC</sub> -<br>700mV |          | V <sub>CC</sub> -<br>400mV |      |

$I_{CC}$  is a direct result of the source design as the TMDS171 integrated receive termination resistor accounts for 85 mA to 100 mA.  $I_{DD}$  is impacted by ARC usage. Connecting a 500 K $\Omega$  resistor to GND at SPDIF reduces the value by more than 20 mA. The measurements were made with no active source connected. (1)

<sup>(2)</sup>

<sup>(3)</sup>

# **Electrical Characteristics (continued)**

The Maximum rating is simulated at 3.465 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature. The Typical rating is simulated at 3.3 V<sub>CC</sub> and 1.2 V V<sub>DD</sub> and at 27°C temperature (unless otherwise noted)

|                          | PARAMETER                                                                                                         | TEST CONDITIONS                                                                                                                                            | MIN                   | ΤΥΡ Ι | IAX                    | UNIT   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------------------------|--------|

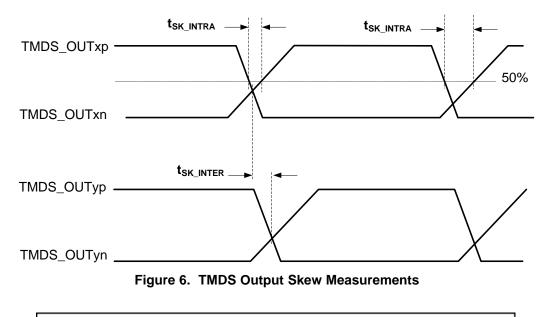

| V <sub>(SWING_DA)</sub>  | Single-ended output voltage<br>swing on data lane                                                                 | $\label{eq:pre_sel} \begin{array}{l} PRE\_SEL = NC; \ TX\_TERM\_CTL = H/NC; \ OE = NC; \\ DR = \le 3.4 \ Gbps; \ VSadj = 7.06 \ k\Omega \end{array}$       | 400                   | 500   | 600                    |        |

| V <sub>(SWING_CLK)</sub> | Single-ended output voltage<br>swing on clock lane                                                                | $\label{eq:pre_sel} \begin{array}{l} PRE\_SEL = NC; \; TX\_TERM\_CTL = H/NC; \; OE = NC; \\ DR = \leq 3.4 \; Gbps; \; VSadj = 7.06 \; k\Omega \end{array}$ | 400                   | 500   | 600                    |        |

| $\Delta V_{(SWING)}$     | Change in single-end output voltage swing per 100 $\Omega$ $\Delta VSadj$                                         |                                                                                                                                                            |                       | 20    |                        |        |

| $\Delta V_{OCM(SS)}$     | Change in steady state output<br>common mode voltage<br>between logic levels                                      |                                                                                                                                                            | -5 5                  |       |                        | mV     |

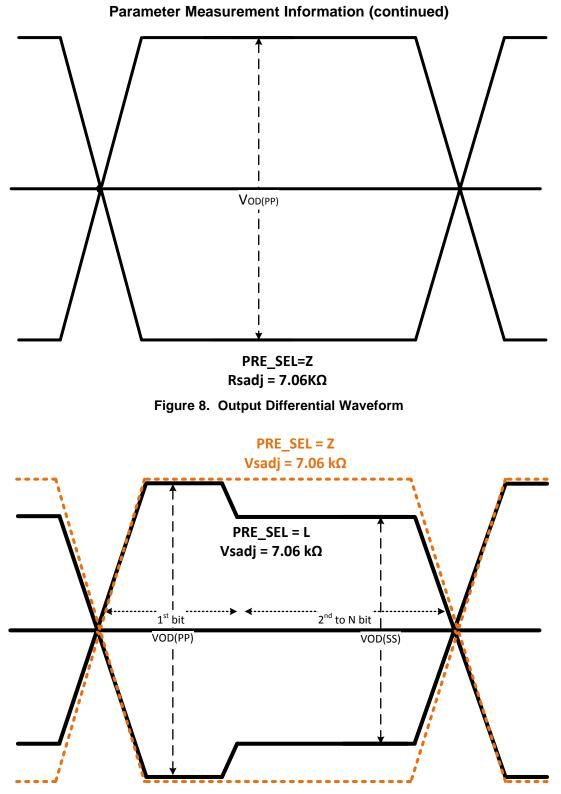

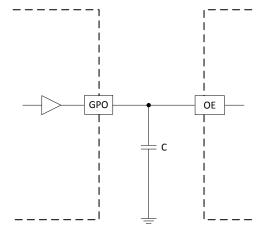

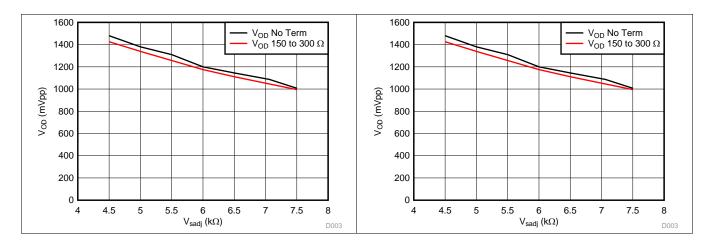

| V <sub>OD(PP)</sub>      | Initial output differential<br>voltage before steady state<br>when pre-emphasis or de-<br>emphasis is implemented | VSadj = 7.06 kΩ; PRE_SEL = NC, See Figure 8                                                                                                                | 800                   | 1     | 200                    |        |

| V <sub>OD(SS)</sub>      | Steady state output differential voltage                                                                          | VSadj = 7.06 kΩ; PRE_SEL = L, See Figure 9                                                                                                                 | 600                   | 1     | 075                    |        |

| I <sub>OS</sub>          | Short circuit current limit                                                                                       | Main link output shorted to GND                                                                                                                            |                       |       | 50                     | mA     |

| I <sub>LEAK</sub>        | Failsafe condition leakage<br>current                                                                             | $V_{CC}$ = 0 V; $V_{DD}$ = 0 V; TMDS Outputs pulled to 3.3V through 50 $\Omega$ resistor                                                                   |                       |       | 45                     | μA     |

| R <sub>(TERM)</sub>      | Source Termination resistance                                                                                     |                                                                                                                                                            | 150                   |       | 300                    | Ω      |

| DDC and I2C              |                                                                                                                   |                                                                                                                                                            |                       |       |                        |        |

| V <sub>I-DC</sub>        | SCL/SDA_SNK,<br>SCL/SDA_SRC DC input<br>voltage                                                                   |                                                                                                                                                            | -0.3                  |       | 5.5                    | V      |

|                          | SCL/SDA_CTL, DC input voltage                                                                                     |                                                                                                                                                            | -0.3                  |       | 3.6                    | V      |

| VIL                      | SCL/SDA_SNK,<br>SCL/SDA_SRC Low level<br>input voltage                                                            |                                                                                                                                                            |                       | 0.3 x | V <sub>CC</sub>        | V      |

|                          | SCL/SDA_CTL Low level input voltage                                                                               |                                                                                                                                                            |                       | 0.3 x | V <sub>CC</sub>        | V      |

| V <sub>IH</sub>          | SCL/SDA_SNK,<br>SCL/SDA_SRC high level<br>input voltage                                                           |                                                                                                                                                            | 3                     |       |                        | V      |

|                          | SCL/SDA_CTL high level input voltage                                                                              |                                                                                                                                                            | 0.7 x V <sub>CC</sub> |       |                        | V      |

| V <sub>OL</sub>          | SCL/SDA_CTL,<br>SCL/SDA_SRC low level<br>output voltage                                                           | $I_{O} = 3 \text{ mA and } V_{CC} > 2 \text{ V}$<br>$I_{O} = 3 \text{ mA and } V_{CC} < 2 \text{ V}$                                                       |                       | 0.2 x | 0.4<br>V <sub>CC</sub> | V<br>V |

| f <sub>SCL</sub>         | SCL clock frequency fast I2C<br>mode for local I2C control                                                        |                                                                                                                                                            |                       |       | 400                    | kHz    |

| C <sub>bus</sub>         | Total capacitive load for each<br>bus line (DDC and local I2C<br>pins)                                            |                                                                                                                                                            |                       |       | 400                    | pF     |

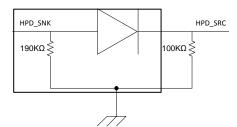

| HPD                      |                                                                                                                   | ·                                                                                                                                                          |                       |       |                        |        |

| V <sub>IH</sub>          | High-level input voltage                                                                                          | HPD_SNK                                                                                                                                                    | 2.1                   |       |                        |        |

| V <sub>IL</sub>          | Low-level input voltage                                                                                           | HPD_SNK                                                                                                                                                    |                       |       | 0.8                    |        |

| V <sub>OH</sub>          | High-level output voltage                                                                                         | I <sub>OH</sub> = -500 μA; HPD_SRC                                                                                                                         | 2.4                   |       | 3.6                    | V      |

| V <sub>OL</sub>          | Low-level output voltage                                                                                          | I <sub>OL</sub> = -500 μA; HPD_SRC                                                                                                                         | 0                     |       | 0.1                    | v      |

| I <sub>LEAK</sub>        | Failsafe condition leakage<br>current                                                                             | V <sub>CC</sub> = 0 V; V <sub>DD</sub> = 0 V; HPD_SNK = 5 V                                                                                                |                       |       | 40                     |        |

|                          |                                                                                                                   | Device powered; V <sub>IH</sub> = 5 V; I <sub>H(HPD)</sub> includes $R_{pd(HPD)}$ resistor current                                                         |                       |       | 40                     |        |

| I <sub>H(HPD)</sub>      | High level input current                                                                                          | Device powered; V <sub>IL</sub> = 0.8 V; I <sub>H(HPD)</sub> includes $R_{pd(HPD)}$ resistor current                                                       |                       |       | 30                     | μA     |

| R <sub>pd(HPD)</sub>     | HPD input termination to GND;                                                                                     | V <sub>CC</sub> < 0 V                                                                                                                                      | 150                   | 190   | 220                    | kΩ     |

| SPDIF and AF             | RC                                                                                                                |                                                                                                                                                            |                       |       |                        |        |

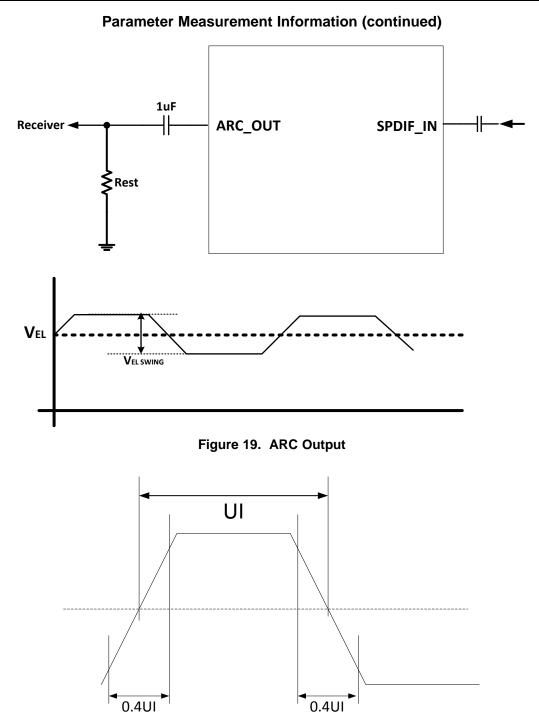

| V <sub>(EL)</sub>        | Operating DC voltage for<br>single mode ARC output                                                                | Test at ARC_OUT, see Figure 19                                                                                                                             | 0                     |       | 5                      | V      |

ZHCSEG5E - OCTOBER 2015-REVISED SEPTEMBER 2017

www.ti.com.cn

STRUMENTS

XAS

# **Electrical Characteristics (continued)**

The Maximum rating is simulated at 3.465 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature. The Typical rating is simulated at 3.3 V<sub>CC</sub> and 1.2 V V<sub>DD</sub> and at 27°C temperature (unless otherwise noted)

|                         | PARAMETER                                     | TEST CONDITIONS                                                           | MIN   | TYP            | MAX    | UNIT |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------|-------|----------------|--------|------|

| V <sub>IN(DC)</sub>     | Operating DC voltage for<br>SPDIF input       |                                                                           |       |                | 0.05   | V    |

| V <sub>(SP_SW)</sub>    | Signal amplitude of SPDIF input               |                                                                           | 0.2   | 0.5            | 0.6    | V    |

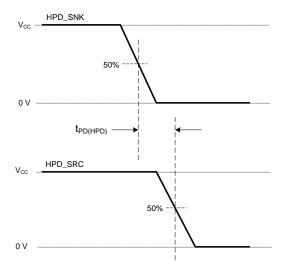

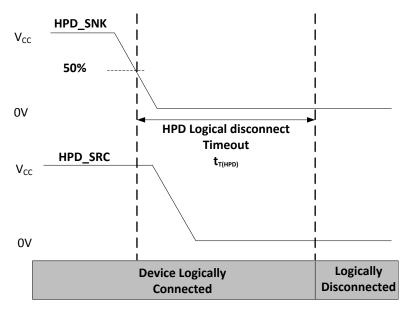

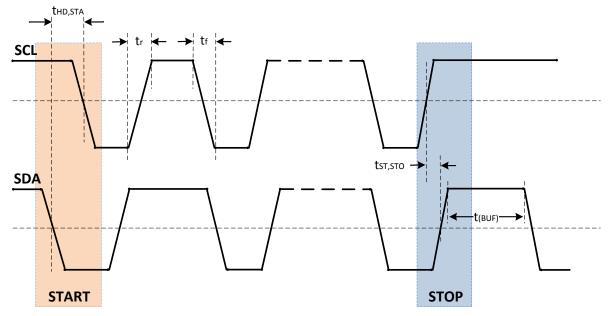

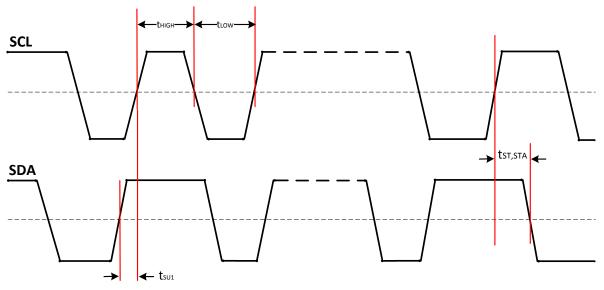

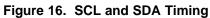

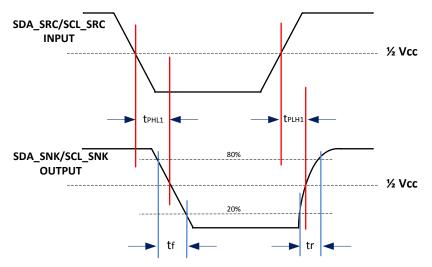

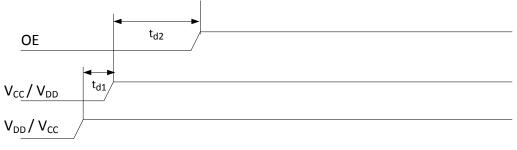

| V <sub>(EISWING)</sub>  | Signal amplitude on the ARC output            | Test at ARC_OUT, 75 $\Omega$ external termination resistor, see Figure 19 | 0.4   | 0.5            | 0.6    | V    |