TLV1702-Q1

ZHCSED6-NOVEMBER 2015

## TLV1702-Q1 2.2V 至 36V 微功耗比较器

### 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 的下列结果:

- 器件温度 1 级: -40℃ 至 +125℃ 的环境运行温度范围

- 器件人体模型 (HBM) 分类等级 1C

- 器件充电器件模型 (CDM) 分类等级 C6

- 电源电压范围: 2.2V 至 36V 或 ±1.1V 至 ±18V

- 低静态电流:每个比较器 55µA

- 输入共模范围包括两个电源轨

- 低传播延迟: 560ns

- 低输入偏移电压: 300μV

- 集电极开路输出:

- 最多可高出负电源电压 36V 且不受电源电压影响

- 工业温度范围: -40°C 至 +125°C

- 小型封装:

- 双列:超薄小外形尺寸 (VSSOP)-8

### 2 应用范围

- 过压和欠压检测器

- 窗口比较器

- 过流检测器

- 零交叉检测器

- 针对以下应用的系统监控:

- 电源

- 白色家电

- 工业传感器

- 汽车

- 医疗

### 3 说明

TLV1702-Q1 器件可提供宽电源电压范围、轨到轨输入、低静态电流和低传播延迟。 凭借符合行业标准且在极小型封装内集成的上述特性,此类器件成为当前市场中的最佳通用比较器。

集电极开路输出具有能够将输出拉至任意电压轨(最多可高出负电源 36 V)且不受 TLV1702-Q1 电源电压影响的优势。

该器件是一款双通道微功耗比较器。 低输入偏移电压、低输入偏置电流、低电源电流和集电极开路配置使TLV1702-Q1 器件能够灵活处理从简单电压检测到驱动单个继电器的多数应用。

该器件在  $-40^{\circ}$ C 至  $+125^{\circ}$ C 的扩展级工业温度范围内额定运行。

### 器件信息<sup>(1)</sup>

| 部件号        | 封装                       | 封装尺寸 (标称值)      |

|------------|--------------------------|-----------------|

| TLV1702-Q1 | 超薄小外形尺寸封装<br>(VSSOP) (8) | 3.00mm × 3.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

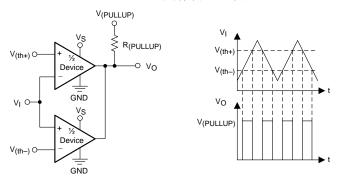

#### TLV1702-Q1 用作窗口比较器

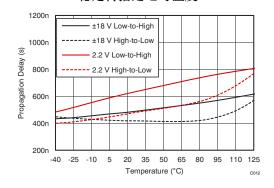

### 稳定传播延迟与温度

# 目录

| 1 | 特性 1                                 |    | 8.3 Feature Description        |    |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用范围 1                               |    | 8.4 Device Functional Modes    | 11 |

| 3 | 说明 1                                 | 9  | Application and Implementation | 12 |

| 4 | 修订历史记录 2                             |    | 9.1 Application Information    | 12 |

| 5 | Related Products                     |    | 9.2 Typical Application        | 12 |

| 6 | Pin Configuration and Functions4     | 10 | Power Supply Recommendations   | 13 |

| 7 | Specifications5                      | 11 | Layout                         | 14 |

| • | 7.1 Absolute Maximum Ratings 5       |    | 11.1 Layout Guidelines         | 14 |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Example            | 14 |

|   | 7.3 Recommended Operating Conditions | 12 | 器件和文档支持                        | 15 |

|   | 7.4 Thermal Information              |    | 12.1 文档支持                      | 15 |

|   | 7.5 Electrical Characteristics 6     |    | 12.2 社区资源                      | 15 |

|   | 7.6 Switching Characteristics 6      |    | 12.3 商标                        | 15 |

|   | 7.7 Typical Characteristics          |    | 12.4 静电放电警告                    | 15 |

| 8 | Detailed Description                 |    | 12.5 Glossary                  | 15 |

| • | 8.1 Overview                         | 13 | 机械、封装和可订购信息                    | 15 |

|   | 8.2 Functional Block Diagram         |    |                                |    |

### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期          | 修订版本 | 注释      |

|-------------|------|---------|

| 2015 年 11 月 | *    | 最初发布版本。 |

### 5 Related Products

| DEVICE      | FEATURES                                      |

|-------------|-----------------------------------------------|

| TLC3702-Q1  | Push-Pull, 20 μA, 20 mA drive                 |

| TLC3704-Q1  |                                               |

| TLV3012-Q1  | Push-Pull, 5 μA, Integrated 1.242-V Reference |

| TLV3501-Q1  | Push-Pull, 3.2 mA, 4.5-ns Propagation Delay   |

| TLV3502-Q1  |                                               |

| TLV3701-Q1  | Push-Pull, 560 nA, Reverse Battery to 16 V    |

| TLV3702-Q1  |                                               |

| REF50xx-Q1  | Series Reference, 0.1% Tolerance, 8 ppm/°C    |

| TL4050xx-Q1 | Shunt Reference, 0.1% Tolerance, 50 ppm/°C    |

| TLVH431-Q1  | Adjustable Shunt Reference 1.24 to 18 V       |

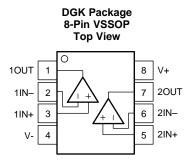

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN  |     | 1/0 | DESCRIPTION                     |

|------|-----|-----|---------------------------------|

| NAME | NO. | I/O | DESCRIPTION                     |

| 1IN+ | 3   | I   | Noninverting input, channel 1   |

| 2IN+ | 5   | 1   | Noninverting input, channel 2   |

| 1IN- | 2   | I   | Inverting input, channel 1      |

| 2IN- | 6   | I   | Inverting input, channel 2      |

| 1OUT | 1   | 0   | Output, channel 1               |

| 2OUT | 7   | 0   | Output, channel 2               |

| V+   | 8   | _   | Positive (highest) power supply |

| V-   | 4   | _   | Negative (lowest) power supply  |

ZHCSED6 - NOVEMBER 2015 www.ti.com.cn

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                         |                        | MIN                     | MAX            | UNIT |

|-------------------------|------------------------|-------------------------|----------------|------|

| Supply voltage          |                        | 40 (±20) V              |                |      |

| Cianal input pina       | Voltage <sup>(2)</sup> | (V <sub>S</sub> ) - 0.5 | $(V_S+) + 0.5$ | V    |

| Signal input pins       | Current <sup>(2)</sup> |                         | ±10            | mA   |

| Output short-circuit (3 |                        | Continuous mA           |                |      |

| Operating temperatu     | re                     | <b>-</b> 55 150         |                | °C   |

| Junction temperature    | e, T <sub>J</sub>      |                         | 150            | °C   |

| Storage temperature     | , T <sub>stg</sub>     | −65 150 °C              |                |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating* Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| \/                 |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            |       | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                        | MIN        | NOM MAX  | UNIT |

|----------------------------------------|------------|----------|------|

| Supply voltage $V_S = (V_S+) - (V_S-)$ | 2.2 (±1.1) | 36 (±18) | V    |

| Specified temperature                  | -40        | 125      | °C   |

### Thermal Information

|                      |                                              | TLV1702-Q1  |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | UNIT |

|                      |                                              | 8 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 199         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 89.5        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 120.4       | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 22          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 118.7       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Input pins are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails must be current limited to 10 mA or less.

<sup>(3)</sup> Short-circuit to ground; one comparator per package.

### 7.5 Electrical Characteristics

at  $T_A = 25^{\circ}C$ ,  $V_S = 2.2$  V to 36 V,  $C_L = 15$  pF,  $R_{PULLUP} = 5.1$  k $\Omega$ ,  $V_{CM} = V_S$  / 2, and  $V_S = V_{PULLUP}$  (unless otherwise noted)

|                      | PARAMETER                       | TEST CONDITIONS                                                         | MIN       | TYP               | MAX  | UNIT  |

|----------------------|---------------------------------|-------------------------------------------------------------------------|-----------|-------------------|------|-------|

| OFFSET V             | OLTAGE                          |                                                                         |           |                   |      |       |

|                      |                                 | T <sub>A</sub> = 25°C, V <sub>S</sub> = 2.2 V                           |           | ±0.5              | ±3.5 | mV    |

| Vos                  | Input offset voltage            | T <sub>A</sub> = 25°C, V <sub>S</sub> = 36 V                            |           | ±0.3              | ±2.5 | mV    |

|                      |                                 | $T_A = -40$ °C to +125°C                                                |           |                   | ±5.5 | mV    |

| dV <sub>OS</sub> /dT | Input offset voltage drift      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                    |           | ±4                | ±20  | μV/°C |

| DCDD                 | Davier aumiliarianties ratio    | T <sub>A</sub> = 25°C                                                   |           | 15                | 100  | μV/V  |

| PSRR                 | Power-supply rejection ratio    | $T_A = -40$ °C to +125°C                                                |           | 20                |      | μV/V  |

| INPUT VO             | LTAGE RANGE                     |                                                                         |           |                   |      |       |

| V <sub>CM</sub>      | Common-mode voltage range       | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                    | (V-)      |                   | (V+) | V     |

| INPUT BIA            | AS CURRENT                      |                                                                         |           |                   |      |       |

| I <sub>B</sub>       | land him and                    | T <sub>A</sub> = 25°C                                                   |           | 5                 | 15   | nA    |

|                      | Input bias current              | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                    |           |                   | 20   | nA    |

| los                  | Input offset current            |                                                                         |           | 0.5               |      | nA    |

| C <sub>LOAD</sub>    | Capacitive load drive           |                                                                         | See Typic | al Characteristic | s    |       |

| OUTPUT               |                                 |                                                                         |           |                   |      |       |

| .,                   | V-14                            | $I_O \le 4$ mA, input overdrive = 100 mV, $V_S = 36$ V                  |           |                   | 900  | mV    |

| Vo                   | Voltage output swing from rail  | $I_O$ = 0 mA, input overdrive = 100 mV, $V_S$ = 36 V                    |           |                   | 600  | mV    |

| I <sub>sc</sub>      | Short circuit sink current      |                                                                         |           | 20                |      | mA    |

|                      | Output leakage current          | $V_{IN+} > V_{IN-}$                                                     |           | 70                |      | nA    |

| POWER S              | UPPLY                           |                                                                         |           |                   |      |       |

| Vs                   | Specified voltage range         |                                                                         | 2.2       |                   | 36   | V     |

|                      | Outconent ourrent (nor channel) | I <sub>O</sub> = 0 A                                                    |           | 55                | 75   | μA    |

| lq                   | Quiescent current (per channel) | $I_O = 0 \text{ A}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |           |                   | 100  | μA    |

### 7.6 Switching Characteristics

at  $T_A = 25$ °C,  $V_S = +2.2$  V to +36 V,  $C_L = 15$  pF,  $R_{PULLUP} = 5.1$  k $\Omega$ ,  $V_{CM} = V_S$  / 2, and  $V_S = V_{PULLUP}$  (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------|--------------------------|-----|-----|-----|------|

| t <sub>pHL</sub> | Propagation delay time, high-to-low | Input overdrive = 100 mV |     | 460 |     | ns   |

| t <sub>pLH</sub> | Propagation delay time, low-to-high | Input overdrive = 100 mV |     | 560 |     | ns   |

| $t_R$            | Rise time                           | Input overdrive = 100 mV |     | 365 |     | ns   |

| t <sub>F</sub>   | Fall time                           | Input overdrive = 100 mV |     | 240 |     | ns   |

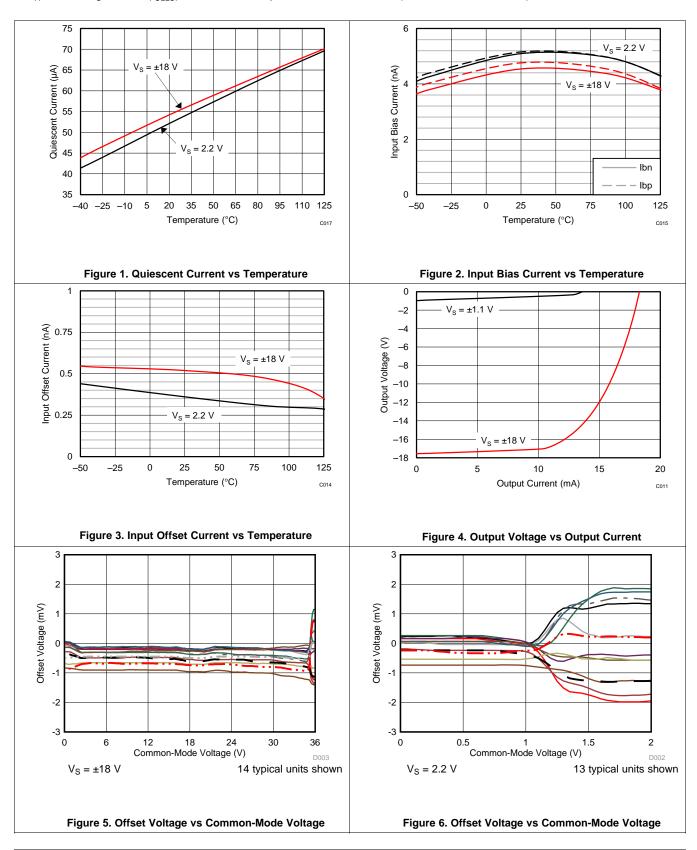

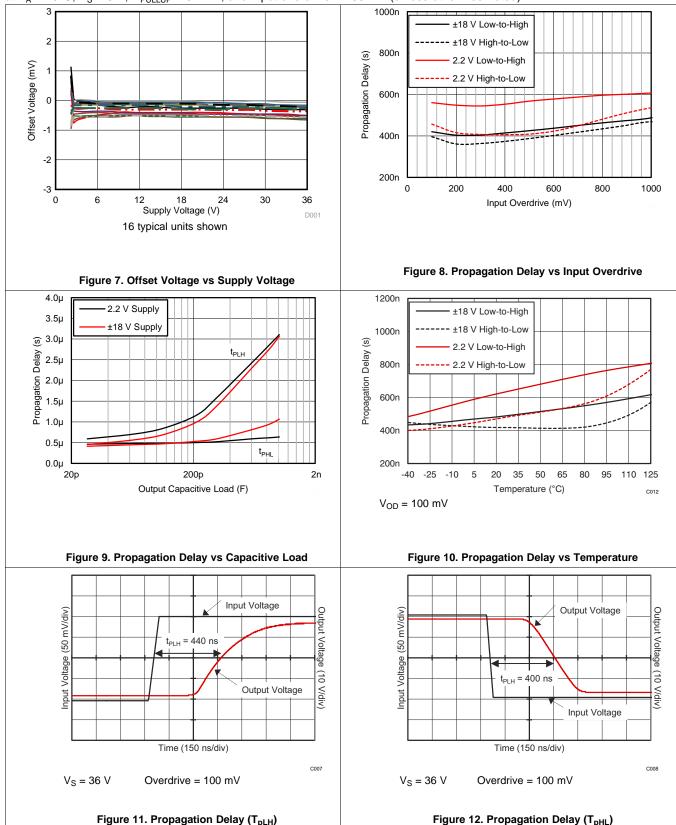

## 7.7 Typical Characteristics

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_{PULLUP} = 5.1$  k $\Omega$ , and input overdrive = 100 mV (unless otherwise noted)

### TEXAS INSTRUMENTS

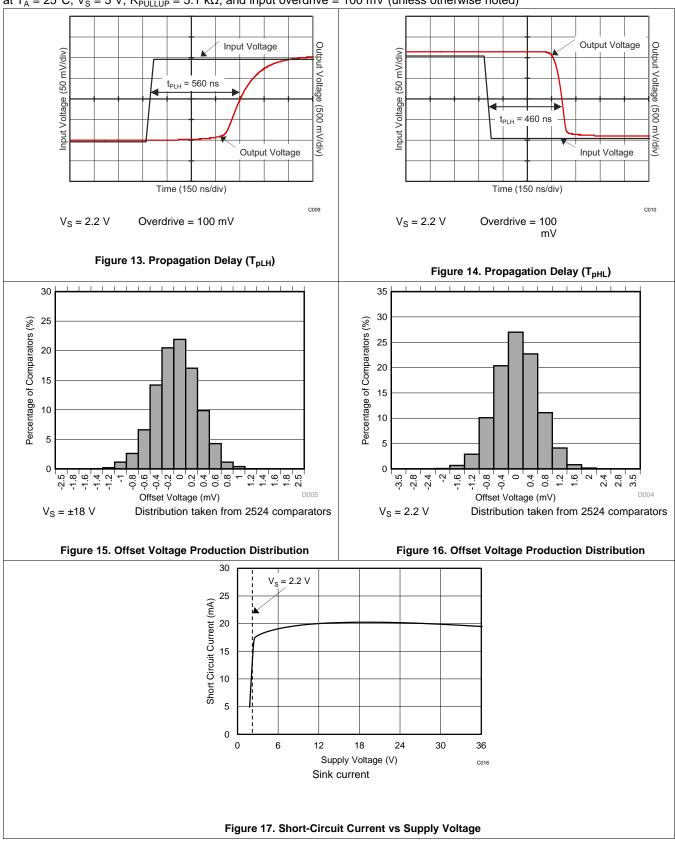

### **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_{PULLUP} = 5.1$  k $\Omega$ , and input overdrive = 100 mV (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_{PULLUP} = 5.1$  k $\Omega$ , and input overdrive = 100 mV (unless otherwise noted)

# TEXAS INSTRUMENTS

### 8 Detailed Description

### 8.1 Overview

The TLV1702-Q1 comparator features rail-to-rail input and output on supply voltages as high as 36 V. The rail-to-rail input stage enables detection of signals close to the supply and ground. The open collector configuration allows the device to be used in wired-OR configurations, such as a window comparator. A low supply current of  $55~\mu A$  per channel with small, space-saving packages, makes these comparators versatile for use in a wide range of applications, from portable to industrial.

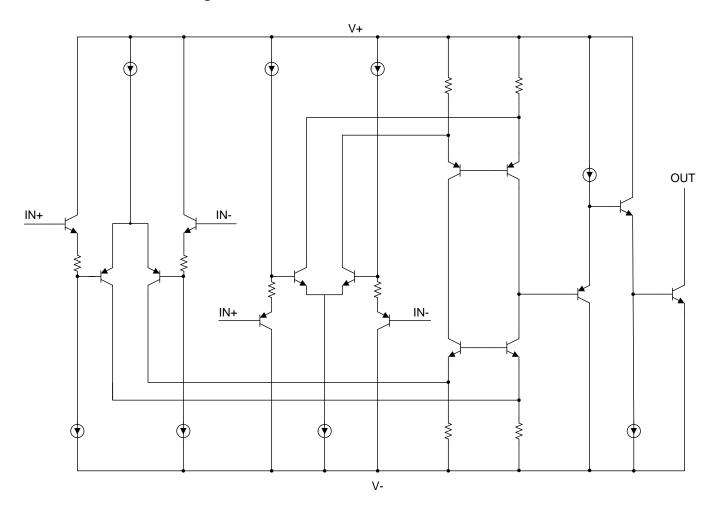

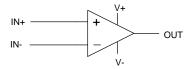

### 8.2 Functional Block Diagram

8.3 Feature Description

### 8.3.1 Comparator Inputs

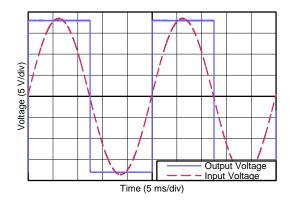

The TLV1702-Q1 device is a rail-to-rail input comparator, with an input common-mode range that includes the supply rails. The TLV1702-Q1 device is designed to prevent phase inversion when the input pins exceed the supply voltage. Figure 18 shows the TLV1702-Q1 device response when input voltages exceed the supply, resulting in no phase inversion.

Figure 18. No Phase Inversion: Comparator Response to Input Voltage (Propagation Delay Included)

#### 8.4 Device Functional Modes

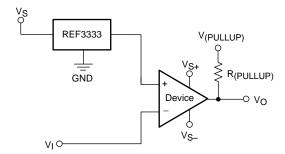

### 8.4.1 Setting Reference Voltage

Using a stable reference is important when setting the transition point for the TLV1702-Q1 device. The REF3333, as shown in Figure 19, provides a 3.3-V reference voltage with low drift and only 3.9 µA of guiescent current.

Figure 19. Reference Voltage for the TLV1702-Q1

### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TLV1702-Q1 device can be used in a wide variety of applications, such as zero crossing detectors, window comparators, over and undervoltage detectors, and high-side voltage sense circuits.

### 9.2 Typical Application

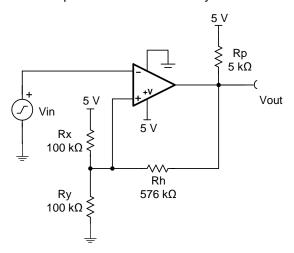

Comparators are used to differentiate between two different signal levels. For example, a comparator differentiates between an overtemperature and normal-temperature condition. However, noise or signal variation at the comparison threshold causes multiple transitions. This application example sets upper and lower hysteresis thresholds to eliminate the multiple transitions caused by noise.

Figure 20. Comparator Schematic with Hysteresis

#### 9.2.1 Design Requirements

The design requirements are as follows:

- Supply voltage: 5 V

- Input: 0 V to 5 V

- Lower threshold (VL) = 2.3 V ±0.1 V

- Upper threshold (VH) = 2.7 V ±0.1 V

- $VH VL = 2.4 V \pm 0.1 V$

- Low-power consumption

ZHCSED6 - NOVEMBER 2015 www.ti.com.cn

### **Typical Application (continued)**

### 9.2.2 Detailed Design Procedure

Make a small change to the comparator circuit to add hysteresis. Hysteresis uses two different threshold voltages to avoid the multiple transitions introduced in the previous circuit. The input signal must exceed the upper threshold (VH) to transition low, or below the lower threshold (VL) to transition high.

Figure 20 illustrates hysteresis on a comparator. Resistor Rh sets the hysteresis level. An open-collector output stage requires a pullup resistor (Rp). The pullup resistor creates a voltage divider at the comparator output that introduces an error when the output is at logic high. This error can be minimized if Rh > 100 Rp.

When the output is at a logic high (5 V), Rh is in parallel with Rx (ignoring Rp). This configuration drives more current into Ry, and raises the threshold voltage (VH) to 2.7 V. The input signal must drive above VH = 2.7 V to cause the output to transition to logic low (0 V).

When the output is at logic low (0 V), Rh is in parallel with Ry. This configuration reduces the current into Ry, and reduces the threshold voltage to 2.3 V. The input signal must drive below VL = 2.3 V to cause the output to transition to logic high (5 V).

For more details on this design and other alternative devices that can be used in place of the TLV1702, refer to Precision Design TIPD144, Comparator with Hysteresis Reference Design.

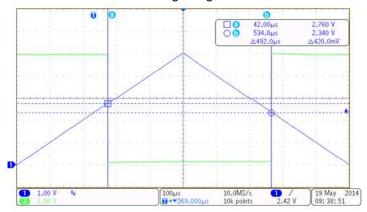

### 9.2.3 Application Curve

Figure 21 shows the upper and lower thresholds for hysteresis. The upper threshold is 2.76 V and the lower threshold is 2.34 V, both of which are close to the design target.

Figure 21. TLV1701 Upper and Lower Threshold with Hysteresis

### 10 Power Supply Recommendations

The TLV1702-Q1 device is specified for operation from 2.2 V to 36 V (±1.1 to ±18 V); many specifications apply from -40°C to +125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the *Typical Characteristics* section.

#### CAUTION

Supply voltages larger than 40 V can permanently damage the device; see the Absolute Maximum Ratings.

Place 0.1-µF bypass capacitors close to the power-supply pins to reduce errors coupling in from noisy or highimpedance power supplies. For more detailed information on bypass capacitor placement; see the Layout Guidelines section.

### 11 Layout

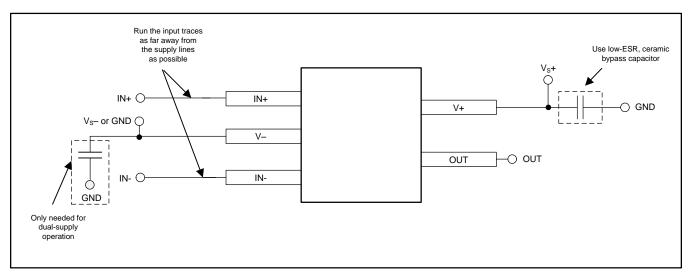

### 11.1 Layout Guidelines

Comparators are very sensitive to input noise. For best results, maintain the following layout guidelines:

- Use a printed circuit board (PCB) with a good, unbroken low-inductance ground plane. Proper grounding (use

of ground plane) helps maintain specified performance of the TLV1702-Q1 device.

- To minimize supply noise, place a decoupling capacitor (0.1-μF ceramic, surface-mount capacitor) as close as possible to V<sub>S</sub> as shown in Figure 22.

- On the inputs and the output, keep lead lengths as short as possible to avoid unwanted parasitic feedback around the comparator. Keep inputs away from the output.

- Solder the device directly to the PCB rather than using a socket.

- For slow-moving input signals, take care to prevent parasitic feedback. A small capacitor (1000 pF or less)

placed between the inputs can help eliminate oscillations in the transition region. This capacitor causes some

degradation to propagation delay when the impedance is low. Run the topside ground plane between the

output and inputs.

- Run the ground pin ground trace under the device up to the bypass capacitor, shielding the inputs from the outputs.

### 11.2 Layout Example

(Schematic Representation)

Figure 22. Comparator Board Layout

ZHCSED6 - NOVEMBER 2015 www.ti.com.cn

### 12 器件和文档支持

### 12.1 文档支持

### 12.1.1 相关文档

相关文档如下:

- 《高精度设计,采用滞后参考设计的比较器》,TIDU020

- 《REF33xx 3.9µA, SC70-3、SOT-23-3 和 UQFN-8, 30ppm/°C 漂移电压基准》, SBOS392

### 12.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.3 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.4 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可 能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可 能会导致器件与其发布的规格不相符。

### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 机械、封装和可订购信息

以下页中包括机械封装、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知 且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part nun | mber | Status (1) | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|--------------------|------|------------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TLV1702AQDGKR      | RQ1  | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU   NIPDAUAG             | Level-2-260C-1 YEAR        | -40 to 125   | 1702Q            |

| TLV1702AQDGKR0     | Q1.B | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAUAG                      | Level-2-260C-1 YEAR        | -40 to 125   | 1702Q            |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TLV1702-Q1:

Catalog: TLV1702

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

NOTE: Qualified Version Definitions:

$_{\bullet}$  Catalog - TI's standard catalog product

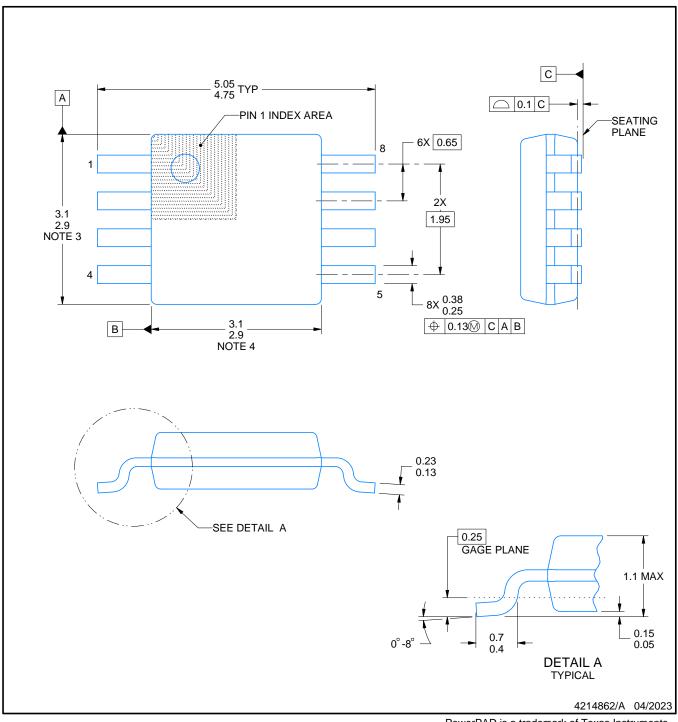

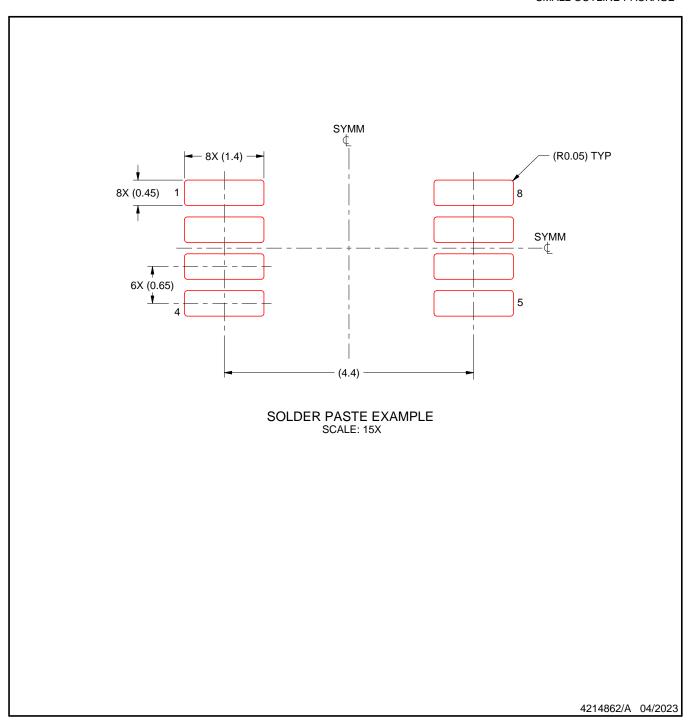

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

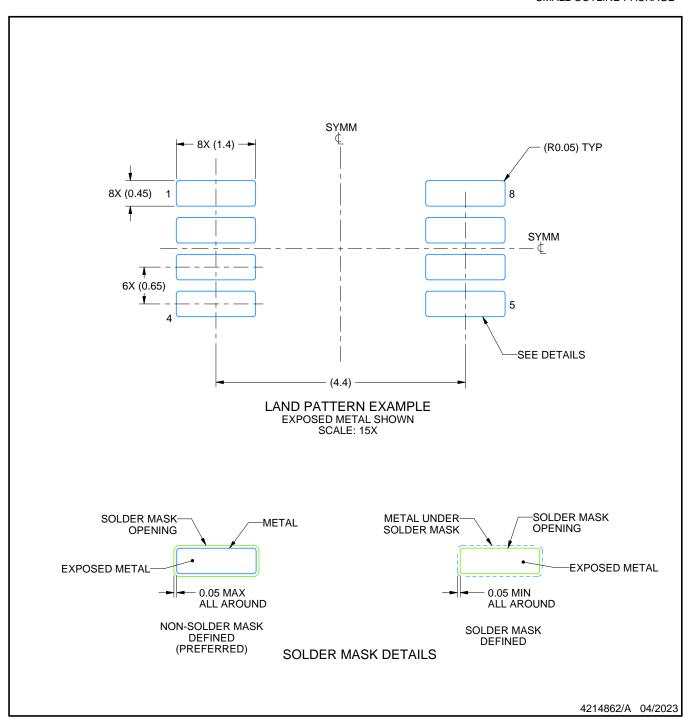

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月