TCAN4551-Q1

ZHCSK43A - AUGUST 2019 - REVISED NOVEMBER 2019

# 带有集成收发器的 TCAN4551-Q1 汽车控制区域网灵活数据速率 (CAN FD) 控制器

## 1 特性

- AEC-Q100 标准:符合汽车应用 要求 - 温度等级 1: -40°C 至 125°C T<sub>A</sub>

- 带有集成 CAN FD 收发器和串行外设接口 (SPI) 的 CAN FD 控制器

- CAN FD 控制器支持 ISO 11898-1:2015 和 Bosch M\_CAN 修订版 3.2.1.1

- 符合 ISO 11898-2:2016 的要求

- 支持 CAN FD 数据速率高达 8Mbps, 且 SPI 时钟 速率高达 18MHz

- 向后兼容经典 CAN

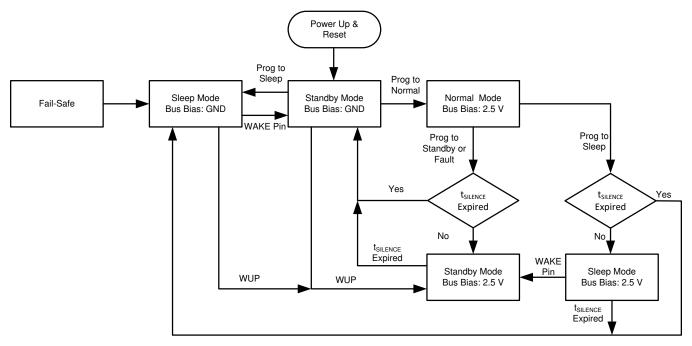

- 工作模式: 正常、待机、睡眠和失效防护

- 为微处理器提供 1.8V、3.3V 至 5V 输入/输出逻辑 支持

- 在 CAN 总线上具有宽工作范围

- ±58V 总线故障保护

- ±12V 共模电压

- 优化了未上电时的性能

- 总线和逻辑终端处于高阻态 (运行总线或应用上无负载)

- 加电和断电无干扰运行

#### 2 应用

- 车身电子装置和照明

- 信息娱乐系统和仪表组

- 工业运输

- 非军用无人机

## 3 说明

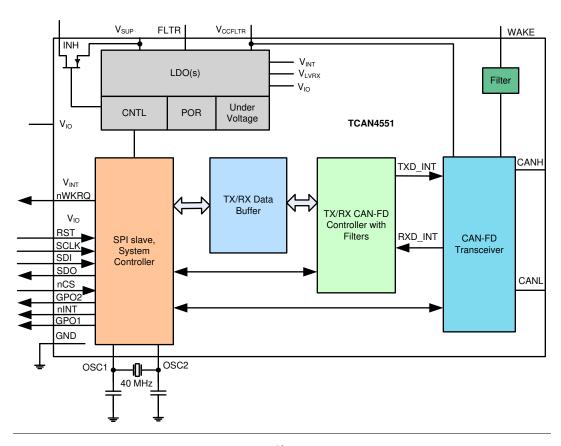

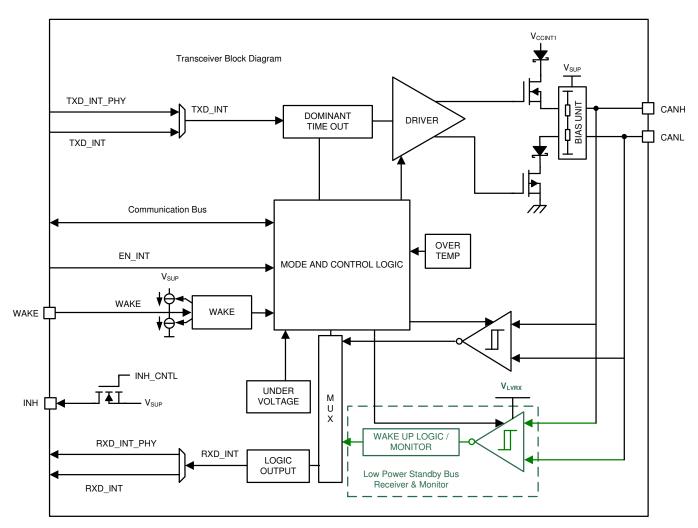

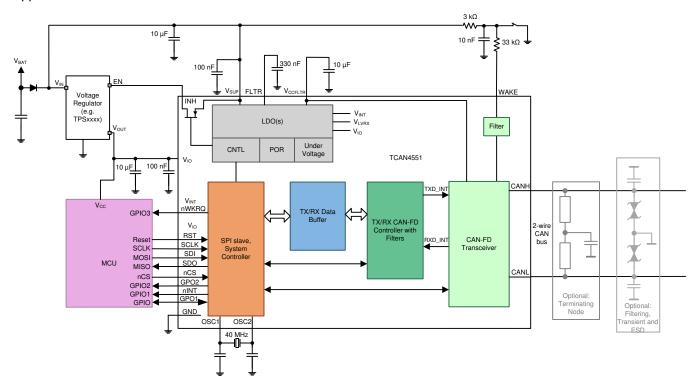

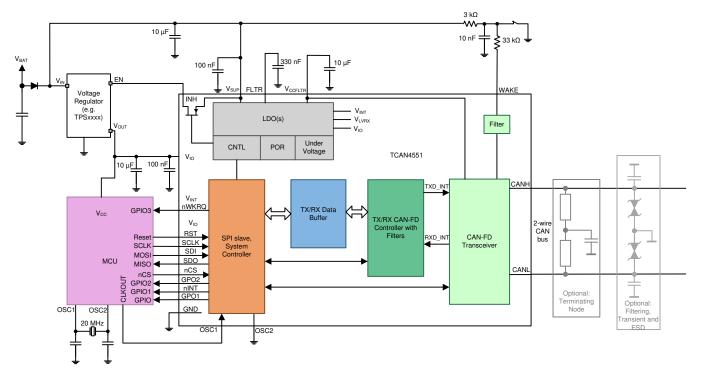

TCAN4551-Q1 是带有集成 CAN FD 收发器的 CAN FD 控制器,支持高达 8Mbps 的数据速率。此 CAN FD 控制器符合 ISO11898-1:2015 高速控制器局域网 (CAN) 数据链路层的规范,并满足 ISO11898-2:2016 高速 CAN 规范的物理层要求。TCAN4551-Q1 通过串 行外设接口 (SPI) 在 CAN 总线和系统处理器之间提供 了一个接口,同时支持经典 CAN 和 CAN FD,并为不 支持 CAN FD 的处理器实现 CAN 和 CAN FD 端口扩 展或 CAN 支持。TCAN4551-Q1 提供 CAN FD 收发器 功能: 传输到总线的差分传输能力和从总线接收的差分 接收能力。 该器件支持通过本地唤醒 (LWU) 进行唤醒 以及使用实现 ISO11898-2:2016 唤醒模式 (WUP) 的 CAN 总线进行总线唤醒。

该器件包含众多可 实现 器件和 CAN 总线可靠性的保 护特性。这些 特性 包括失效防护特性、内部显性状态 超时和宽总线工作范围等等。

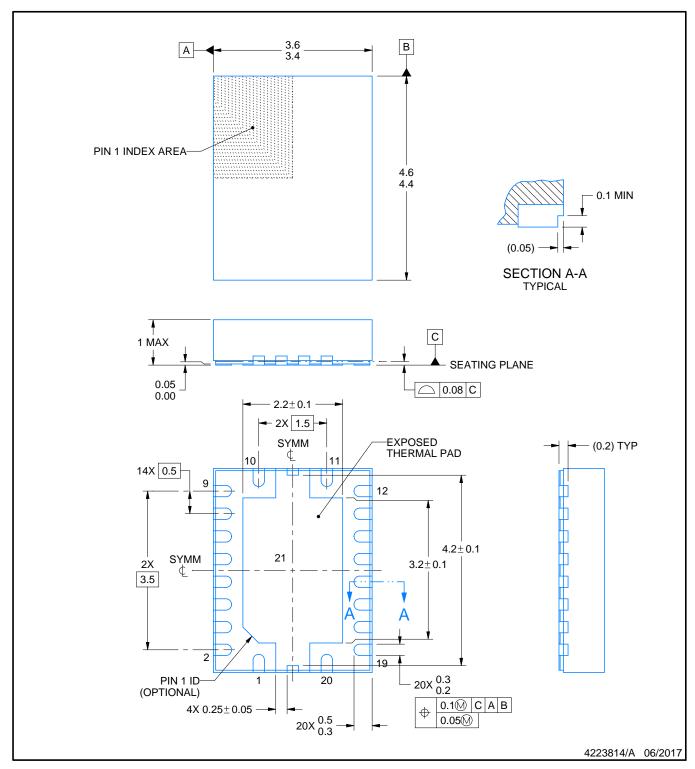

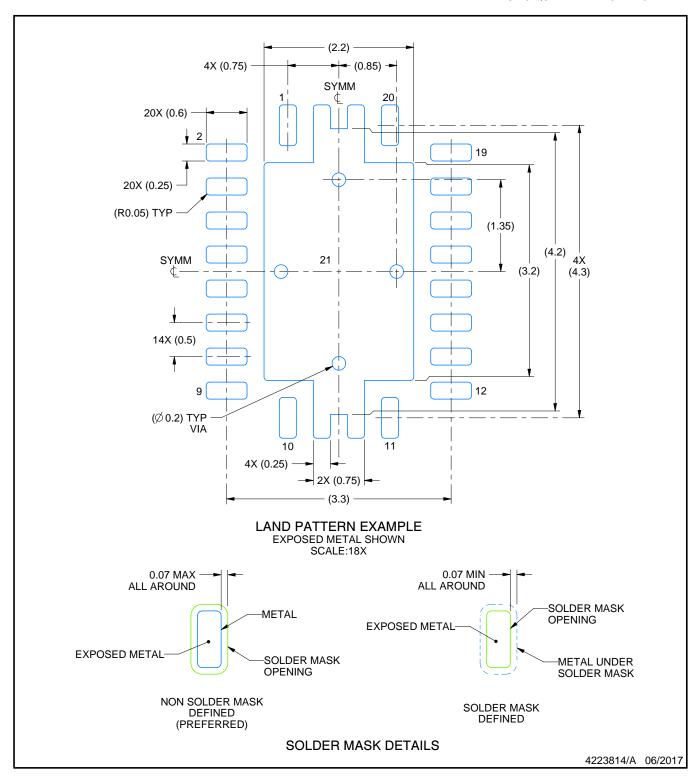

#### 器件信息(1)

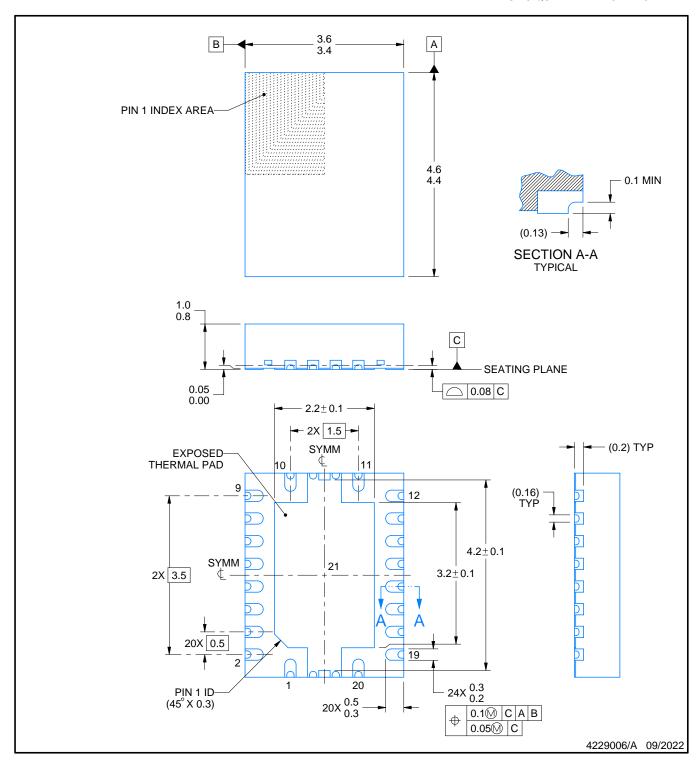

| 器件型号        | 封装        | 封装尺寸 (标称值)      |

|-------------|-----------|-----------------|

| TCAN4551-Q1 | VQFN (20) | 4.50mm x 3.50mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

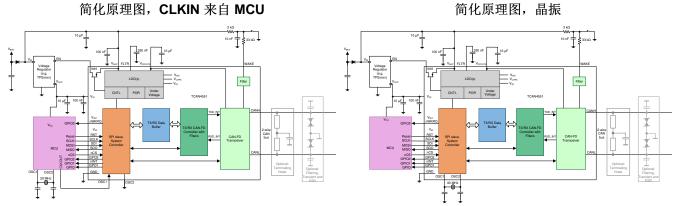

## 简化原理图, CLKIN 来自 MCU

|   | ⊣. |

|---|----|

| н | 沤  |

| 1 | 特性 1                                       |    | 8.2 Functional Block Diagram         | 21              |

|---|--------------------------------------------|----|--------------------------------------|-----------------|

| 2 | 应用 1                                       |    | 8.3 Feature Description              | 24              |

| 3 | 说明 1                                       |    | 8.4 Device Functional Modes          | <mark>27</mark> |

| 4 | 修订历史记录                                     |    | 8.5 Programming                      | 38              |

| 5 | Pin Configuration and Functions            |    | 8.6 Register Maps                    | 42              |

| 6 | Specifications                             | 9  | Application and Implementation       | 125             |

| U | 6.1 Absolute Maximum Ratings               |    | 9.1 Application Design Consideration | 125             |

|   | 6.2 ESD Ratings                            |    | 9.2 Typical Application              | 129             |

|   | 6.3 ESD Ratings, IEC ESD and ISO Transient | 10 | Power Supply Recommendations         | 132             |

|   | Specification4                             | 11 | Layout                               |                 |

|   | 6.4 Recommended Operating Conditions       |    | 11.1 Layout Guidelines               |                 |

|   | 6.5 Thermal Information                    |    | 11.2 Layout Example                  |                 |

|   | 6.6 Supply Characteristics 5               | 12 | 器件和文档支持                              | 135             |

|   | 6.7 Electrical Characteristics             |    | 12.1 文档支持                            |                 |

|   | 6.8 Timing Requirements8                   |    | 12.2 接收文档更新通知                        | 135             |

|   | 6.9 Switching Characteristics9             |    | 12.3 社区资源                            | 135             |

|   | 6.10 Typical Characteristics11             |    | 12.4 商标                              | 135             |

| 7 | Parameter Measurement Information 11       |    | 12.5 静电放电警告                          | 135             |

| 8 | Detailed Description                       |    | 12.6 Glossary                        | 135             |

|   | 8.1 Overview                               | 13 | 机械、封装和可订购信息                          | 136             |

|   |                                            |    |                                      |                 |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

##

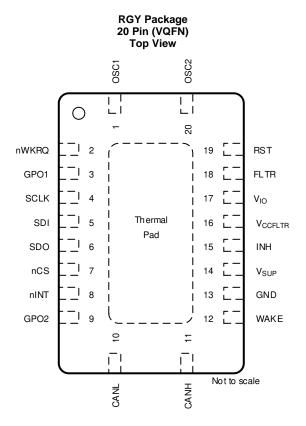

# 5 Pin Configuration and Functions

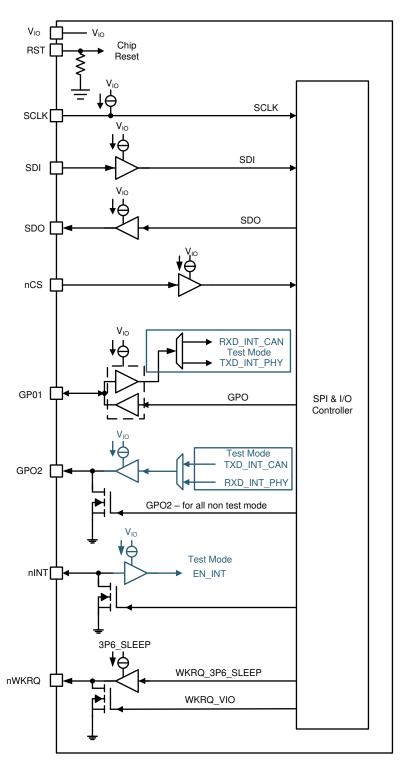

**Pin Functions**

| PIN |                     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                      |  |  |  |

|-----|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME                | ITPE\/              | DESCRIPTION                                                                                                      |  |  |  |

| 1   | OSC1                | I                   | External crystal oscillator or clock input                                                                       |  |  |  |

| 2   | nWKRQ               | DO                  | Wake request (active low)                                                                                        |  |  |  |

| 3   | GPO1                | DO                  | Configurable output function pin through SPI                                                                     |  |  |  |

| 4   | SCLK                | DI                  | SPI clock input                                                                                                  |  |  |  |

| 5   | SDI                 | DI                  | SPI slave data input from master output                                                                          |  |  |  |

| 6   | SDO                 | DO                  | SPI slave data output to master input                                                                            |  |  |  |

| 7   | nCS                 | DI                  | SPI chip select                                                                                                  |  |  |  |

| 8   | nINT                | DO                  | Interrupt pin to MCU (active low)                                                                                |  |  |  |

| 9   | GPO2                | DO                  | Configurable output function pin through SPI                                                                     |  |  |  |

| 10  | CANL                | HV Bus I/O          | Low level CAN bus line                                                                                           |  |  |  |

| 11  | CANH                | HV Bus I/O          | High level CAN bus line                                                                                          |  |  |  |

| 12  | WAKE                | HVI                 | Wake input, high voltage input                                                                                   |  |  |  |

| 13  | GND                 | GND                 | Ground connection                                                                                                |  |  |  |

| 14  | V <sub>SUP</sub>    | HV Supply<br>In     | Supply from battery                                                                                              |  |  |  |

| 15  | INH                 | HVO                 | Inhibit to control system voltage regulators and supplies (open drain)                                           |  |  |  |

| 16  | V <sub>CCFLTR</sub> | Supply Filter       | Internal 5 V regulator filter, requires external capacitor to ground                                             |  |  |  |

| 17  | V <sub>IO</sub>     | Supply In           | Digital I/O voltage supply                                                                                       |  |  |  |

| 18  | FLTR                | _                   | Internal regulator filter, requires external capacitor to ground                                                 |  |  |  |

| 19  | RST                 | DI                  | Device reset                                                                                                     |  |  |  |

| 20  | OSC2                | 0                   | External crystal oscillator output; when using single input clock to OSC1 this pin should be connected to ground |  |  |  |

(1) Note: DI = Digital Input; DO = Digital Output; HV = High Voltage; Thermal PAD and GND Pins must be soldered to GND

## **Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range for -40 °C  $\leq T_A \leq 125$  °C (unless otherwise noted)<sup>(1)</sup>

|                          |                                                                                | MIN  | MAX | UNIT |

|--------------------------|--------------------------------------------------------------------------------|------|-----|------|

| $V_{SUP}$                | Supply voltage                                                                 | -0.3 | 42  | V    |

| $V_{IO}$                 | Supply voltage I/O level shifter                                               | -0.3 | 6   | V    |

| V <sub>BUS</sub>         | CAN bus I/O voltage (CANH, CANL)                                               | -58  | 58  | V    |

| $V_{WAKE}$               | WAKE pin input voltage                                                         | -0.3 | 42  | V    |

| V <sub>INH</sub>         | Inhibit pin output voltage                                                     | -0.3 | 42  | V    |

| V <sub>Logic_Input</sub> | Logic input terminal voltage                                                   | -0.3 | 6   | V    |

| $V_{SO}$                 | Digital output terminal voltage                                                | -0.5 | 6   | V    |

| I <sub>O(SO)</sub>       | Digital output current                                                         |      | 8   | mA   |

| I <sub>O(INH)</sub>      | Inhibit output current                                                         |      | 4   | mA   |

| I <sub>O(WAKE)</sub>     | Wake current if due to ground shift $V_{(WAKE)} \le V_{(GND)} - 0.3 \text{ V}$ |      | 3   | mA   |

| TJ                       | Junction temperature                                                           | -40  | 150 | °C   |

| T <sub>stg</sub>         | Storage temperature                                                            | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

|                    |                         |                                                                                                                                                                                           |                                                                   | VALUE | UNIT     |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|----------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM) classification level 3A per AEC Q100-002 All terminal except for CANH and CANL. <sup>(1)</sup> WAKE terminals which are with respect to ground only <sup>(2)</sup> |                                                                   | ±4000 | <b>V</b> |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM) classifica CANL <sup>(2)</sup>                                                                                                                                     | iman body model (HBM) classification level H2 for CANH and NL (2) |       | V        |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM) classification level C5, per AEC Q100-011                                                                                                                      | All terminals                                                     | ±750  | ٧        |

- AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

- Terminals stressed with respect to GND

6.3 ESD Ratings, IEC ESD and ISO Transient Specification

|                    |                                                                   |                   | VALUE   | UNIT |

|--------------------|-------------------------------------------------------------------|-------------------|---------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge according to IBEE CAN EMC <sup>(1)</sup>  | Contact discharge | ±8000   | ٧    |

| \/                 | Electrostatic discharge according to SAEJ2962-                    | Contact discharge | ±8000   |      |

| $V_{(ESD)}$        | 2 (2)                                                             | Air discharge     | ±15 000 |      |

|                    |                                                                   | Pulse 1           | -100    | \/   |

| ISO7637 Ti         | EMC <sup>(1)</sup> Electrostatic discharge according to SAEJ2962- | Pulse 2           | 75      | V    |

| CAN bus te         | rminals (CANH and CANL), V <sub>SUP</sub> and WAKE (3)            | Pulse 3a          | -150    |      |

|                    |                                                                   | Pulse 3b          | 100     |      |

IEC 61000-4-2 is a system-level ESD test. Results given here are specific to the IBEE LIN EMC Test specification conditions per IEC TS 62228. Different system-level configurations may lead to different results

SAEJ2962-2 Testing performed at 3<sup>rd</sup> party US3 approved EMC test facility, test report available upon request.

ISO7637 is a system-level transient test. Results given here are specific to the IBEE CAN EMC Test specification conditions. Different

system-level configurations may lead to different results.

## 6.4 Recommended Operating Conditions

over operating free-air temperature range for – 40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C (unless otherwise noted)

|                        |                                                                            | MIN  | TYP | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------|------|-----|------|------|

| V <sub>SUP</sub>       | Supply voltage                                                             | 5.5  |     | 30   | V    |

| V <sub>IO</sub>        | Logic pin supply voltage                                                   | 1.71 |     | 5.25 | V    |

| I <sub>OH(DO)</sub>    | Digital terminal high-level output current                                 | -2   |     |      | mA   |

| I <sub>OL(DO)</sub>    | Digital terminal low-level output current                                  |      |     | 2    | mA   |

| I <sub>O (INH)</sub>   | INH output current                                                         |      |     | 1    | mA   |

| C <sub>(FLTR)</sub>    | Filter pin capacitance See Power Supply Recommendations                    | 300  |     |      | nF   |

| C <sub>(VCCFLTR)</sub> | Internal 5 V regulator filter capacitance See Power Supply Recommendations | 10   |     |      | μF   |

| C <sub>WAKE</sub>      | External WAKE pin capacitance                                              | 10   |     |      | nF   |

| T <sub>SDR</sub>       | Thermal shutdown rising                                                    | 160  |     |      | °C   |

| T <sub>SDF</sub>       | Thermal shutdown falling                                                   |      |     | 150  | °C   |

| T <sub>SD(HYS)</sub>   | Thermal shutdown hysteresis                                                |      | 10  |      | °C   |

#### 6.5 Thermal Information

|                       |                                              | TCAN4551      |      |

|-----------------------|----------------------------------------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PKG DES (RGY) | UNIT |

|                       |                                              | 20 PINS       |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 35.2          | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 28.1          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.8          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3           | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 12.7          | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

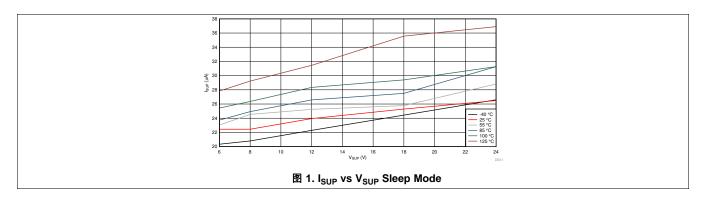

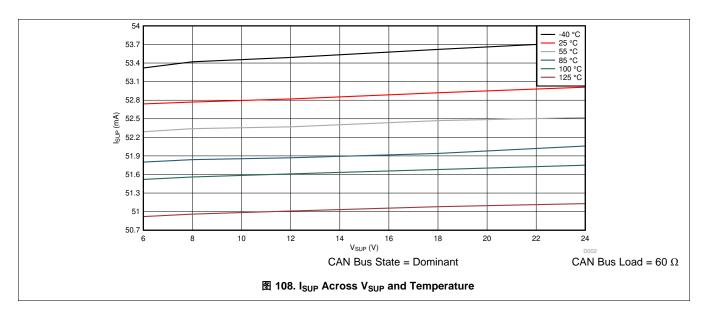

## 6.6 Supply Characteristics

over operating free-air temperature range for – 40  $^{\circ}\text{C} \le T_{\text{A}} \le 125 \,^{\circ}\text{C}$  (unless otherwise noted)

|                  | PARAMETER                    |                         | TEST CONDITIONS                                                                                                                  | MIN | TYP | MAX | UNIT |

|------------------|------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

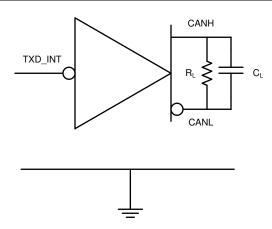

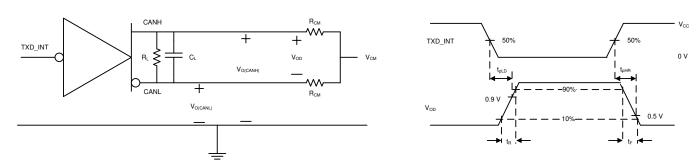

|                  |                              | Dominant                | See $\boxtimes$ 4 R <sub>L</sub> = 60 Ω, C <sub>L</sub> = open. typical bus load.                                                |     |     | 80  | mA   |

|                  | Supply ourrent permal made   | Dominant                | See $\boxtimes$ 4 R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = open, high bus load.                                           |     |     | 90  | mA   |

|                  | Supply current, normal mode  | Dominant with bus fault | See ₹ 4 CANH = - 25 V, R <sub>L</sub> = open, C <sub>L</sub> = open                                                              |     |     | 180 | mA   |

| I <sub>SUP</sub> |                              | Recessive               | See $\boxtimes$ 4 R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open,                                  |     |     | 15  | mA   |

|                  |                              |                         | See $\  \  \  \  \  \  \  \  \  \  \  \  \ $                                                                                     |     |     | 3.5 | mA   |

|                  | Supply current, standby mode |                         | See $\boxtimes$ 4 RL = 60 $\Omega$ , C <sub>L</sub> = open, -40°C < T <sub>A</sub> < 85°C, CANH/L terminated to GND $\pm$ 100 mV |     |     | 3.4 | mA   |

| I <sub>SUP</sub> | Supply current, sleep mode   |                         | SPI bus, OSC/CLKIN disabled: $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}, \text{ V}_{\text{IO}} = 0$         |     | 25  | 42  | μΑ   |

| l                | I/O supply current normal    | I/O supply current      | CLKIN = 40 MHz, $V_{IO}$ = 5 V                                                                                                   |     |     | 800 | μΑ   |

| I <sub>VIO</sub> | mode dominant                | I/O Supply culterit     | Crystal = 40 MHz, V <sub>IO</sub> = 5 V                                                                                          |     |     | 3   | mA   |

## **Supply Characteristics (continued)**

over operating free-air temperature range for  $-40~^{\circ}\text{C} \le T_{A} \le 125~^{\circ}\text{C}$  (unless otherwise noted)

|                   | PARAMETER                                        |                            | TEST CONDITIONS                                                          | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------------------------|----------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>VIO</sub>  | I/O supply current, sleep mode                   | I/O supply current         | Sleep Mode V <sub>IO</sub> = 5 V; OSC1 = CLKIN = 0 V and OSC2 = GND (1)  |     |     | 9   | μΑ   |

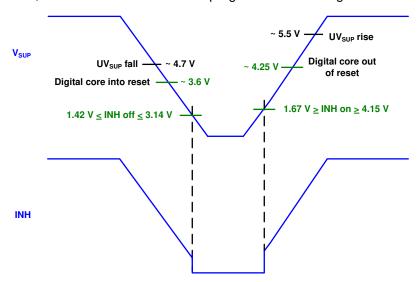

| LIV               | Under voltage detection on V <sub>SUF</sub> mode | rising ramp for protected  | See Section Under Voltage                                                |     | 5.5 | 5.9 | ٧    |

| UV <sub>SUP</sub> | Under voltage detection on V <sub>SUF</sub> mode | falling ramp for protected | Lockout (UVLO) and<br>Unpowered Device                                   | 4.5 | 4.7 |     | ٧    |

| t <sub>TSD</sub>  | Thermal shutdown timer (2)                       | Thermal shutdown timer (2) | See section Thermal<br>Shutdown for description of<br>thermal shut down. | 200 |     | 500 | ms   |

<sup>(1)</sup> When a crystal is used this current will be higher until the crystal's capacitors bleed off their energy. How much current and length of time to bleed of the energy is system dependent and will not be specified.

## 6.7 Electrical Characteristics

over operating free-air temperature range for – 40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C (unless otherwise noted)

|                     | PARAMETER                                                                                                                                                                                                        | TEST CONDITIONS (1)                                                                                                                                         | MIN  | TYP                                                               | MAX  | UNIT |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------|------|------|

| CAN DRIVE           | R ELECTRICAL CHARACTERISTICS                                                                                                                                                                                     |                                                                                                                                                             |      |                                                                   |      |      |

|                     | Bus output voltage (dominant) CANH                                                                                                                                                                               | See 图 4 and 图 5, TXD_INT = 0 V, EN                                                                                                                          | 2.75 |                                                                   | 4.5  | V    |

| $V_{O(D)}$          | Bus output voltage (dominant) CANL                                                                                                                                                                               | $ = 0 \text{ V}, 50 \Omega \leq R_{L} \leq 65 \Omega, C_{L} = \text{open}, $ $R_{CM} = \text{open} $                                                        | 0.5  |                                                                   | 2.25 | V    |

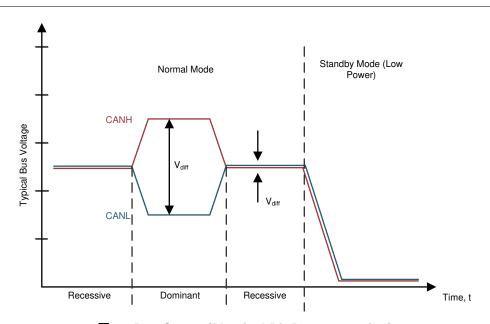

| $V_{O(R)}$          | Bus output voltage (recessive)                                                                                                                                                                                   | See $\boxtimes$ 2 and $\boxtimes$ 5, TXD_INT = V <sub>IO</sub> , R <sub>L</sub> = open (no load), R <sub>CM</sub> = open                                    | 2    | 2.5                                                               | 3    | ٧    |

| V <sub>(DIFF)</sub> | Maximum differential voltage rating                                                                                                                                                                              | See 图 2 and 图 5                                                                                                                                             | -5.0 |                                                                   | 10   | V    |

|                     | Bus output voltage (Standby Mode)<br>CANH                                                                                                                                                                        |                                                                                                                                                             | -0.1 |                                                                   | 0.1  | V    |

| V <sub>O(STB)</sub> | Bus output voltage (Standby Mode)<br>CANL                                                                                                                                                                        | See 图 2 and 图 5, TXD_INT = V <sub>IO</sub> , R <sub>L</sub> = open (no load), R <sub>CM</sub> = open                                                        | -0.1 |                                                                   | 0.1  | V    |

|                     | Bus output voltage (Standby Mode)<br>CANH - CANL                                                                                                                                                                 |                                                                                                                                                             | -0.2 | 4.5 2.25 2.5 3 10 0.1 0.1 0.2 3 3 5 12 50 1.1                     | V    |      |

|                     | Differential output voltage (dominant)                                                                                                                                                                           | See $\boxtimes$ 2 and $\boxtimes$ 5, TXD_INT = 0 V, 50 $\Omega$<br>$\leq$ R <sub>L</sub> $\leq$ 65 $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open | 1.5  |                                                                   | 3    | V    |

| V <sub>OD(D)</sub>  |                                                                                                                                                                                                                  | See $\boxtimes$ 2 and $\boxtimes$ 5, TXD_INT = 0 V, 45 $\Omega$<br>$\leq$ R <sub>L</sub> $\leq$ 70 $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open | 1.4  |                                                                   | 3    | V    |

|                     |                                                                                                                                                                                                                  | See $\boxtimes$ 2 and $\boxtimes$ 5, TXD_INT = 0 V, R <sub>L</sub> = 2.24 k $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open                        | 1.5  |                                                                   | 5    | V    |

|                     |                                                                                                                                                                                                                  | See $\boxtimes$ 2 and $\boxtimes$ 5, TXD_INT = V <sub>IO</sub> , R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open               | -120 |                                                                   | 12   | mV   |

| $V_{OD(R)}$         | Differential output voltage (recessive)                                                                                                                                                                          | See 图 2 and 图 5, TXD_INT = V <sub>IO</sub> , R <sub>L</sub> = open (no load), C <sub>L</sub> = open, R <sub>CM</sub> = open                                 | -50  | 5 2.25 2 2.5 3 0 10 1 0.1 1 0.1 2 0.2 5 3 4 3 5 5 0 12 0 50 9 1.1 | mV   |      |

| $V_{SYM}$           | Output symmetry (dominant or recessive) ( VO(CANH) + VO(CANL)) / VCC                                                                                                                                             | See $\boxtimes$ 2 and $\boxtimes$ 5, R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = open, R <sub>CM</sub> = open, C1 = 4.7 nF, TXD_INT - 250 kHZ, 1 MHz    | 0.9  |                                                                   | 1.1  | V/V  |

| V <sub>SYM_DC</sub> | Output symmetry (dominant or recessive) (VCC – VO(CANH) – VO(CANL)) with a frequency that corresponds to the highest bit rate for which the HS-PMA implementation is intended, however, at most 1 MHz (2 Mbit/s) | See $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                  | -300 |                                                                   | 300  | mV   |

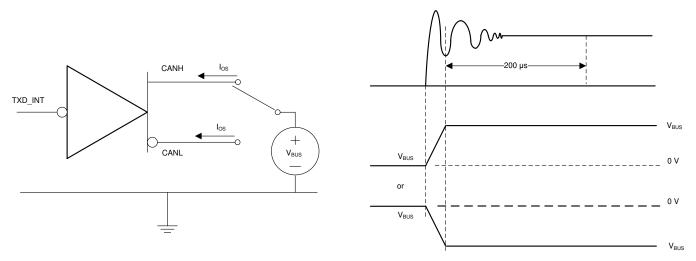

| IOS_DOM             | Short-circuit steady-state output current,                                                                                                                                                                       | See 图 2 and 图 9, -3.0 V ≤ V <sub>CANH</sub> ≤ 18.0 V, CANL = open, TXD_INT = 0 V                                                                            | -100 |                                                                   |      | mA   |

| IOS_DOM             | dominant                                                                                                                                                                                                         | See $\blacksquare$ 2 and $\blacksquare$ 9, -3.0 V ≤ V <sub>CANL</sub><br>≤+18.0 V, CANH = open, TXD_INT = 0 V                                               |      |                                                                   | 100  | mA   |

(1) All TXD\_INT, RXD\_INT and EN\_INT references are for internal nodes that represent the same functions for a physical layer transceiver.

<sup>(2)</sup> Specified by design

# **Electrical Characteristics (continued)**

over operating free-air temperature range for  $-40~^{\circ}\text{C} \le T_{\text{A}} \le 125~^{\circ}\text{C}$  (unless otherwise noted)

|                          | PARAMETER                                                                                   | TEST CONDITIONS (1)                                                                                          | MIN                 | TYP | MAX                 | UNIT     |

|--------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|----------|

| IOS_REC                  | Short-circuit steady-state output current, recessive                                        | See $\ 2$ and $\ 9$ , $-27 \ V \le V_{BUS} \le 32 \ V_{DUS} = CANH = CANL$                                   | <b>-</b> 5          |     | 5                   | mA       |

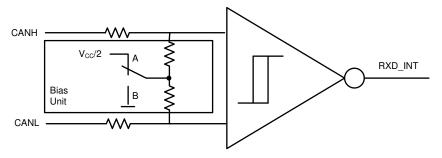

| CAN RECEIV               | ER ELECTRICAL CHARACTERISTICS                                                               |                                                                                                              |                     |     |                     |          |

| $V_{ITdom}$              | Receiver dominant state differential input voltage range, bus biasing active                | -12.0 V ≤ V <sub>CANL</sub> ≤ +12.0 V                                                                        | 0.9                 |     | 8                   | V        |

| V <sub>ITrec</sub>       | Receiver recessive state differential input voltage range bus biasing active                | -12.0 V ≤ V <sub>CANH</sub> ≤ +12.0 V See 图 6,表<br>2                                                         | -3.0                |     | 0.5                 | V        |

| V <sub>HYS</sub>         | Hysteresis voltage for input-threshold, normal modes                                        | See 图 6, 表 2                                                                                                 |                     | 120 |                     | mV       |

| V <sub>IT(ENdom)</sub>   | Receiver dominant state differential input voltage range, bus biasing inactive (VDiff)      | -12.0 V ≤ V <sub>CANL</sub> ≤ +12.0 V<br>-12.0 V ≤ V <sub>CANH</sub> ≤ +12.0 V See 图 6,表<br>2                | 1.15                |     | 8                   | V        |

| V <sub>IT(ENrec)</sub>   | Receiver recessive state differential input voltage range, bus biasing inactive (VDiff)     | -12.0 V ≤ V <sub>CANL</sub> ≤ +12.0 V<br>-12.0 V ≤ V <sub>CANH</sub> ≤ +12.0 V See 图 6,表<br>2                | -3                  |     | 0.4                 | V        |

| V <sub>CM</sub>          | Common mode range: normal                                                                   | See 图 6, 表 2                                                                                                 | -12                 |     | 12                  | V        |

| V <sub>CM(EN)</sub>      | Common mode range: standby mode                                                             | See 图 6, 表 2                                                                                                 | -12                 |     | 12                  | V        |

| I <sub>IOFF(LKG)</sub>   | Power-off (unpowered) bus input leakage current                                             | $V_{CANH} = V_{CANL} = 5 \text{ V}, V_{sup} \text{ to GND via 0}$<br>$\Omega$ and 47 k $\Omega$ resistor     |                     |     | 5                   | μΑ       |

| C <sub>I</sub>           | Input capacitance to ground (CANH or CANL)                                                  |                                                                                                              |                     |     | 25                  | pF       |

| C <sub>ID</sub>          | Differential input capacitance                                                              |                                                                                                              |                     |     | 14                  | pF       |

| $R_{\text{ID}}$          | Differential input resistance                                                               | TXD_INT = $V_{CCINT}$ , normal mode: -2.0 V $\leq V_{CANH} \leq$ +7.0 V; -2.0 V $\leq V_{CANL} \leq$ + 7.0 V | 60                  |     | 100                 | kΩ       |

| R <sub>IN</sub>          | Single ended Input resistance (CANH or CANL)                                                | -2.0 V ≤ V <sub>CANH</sub> ≤+7.0 V; -2.0 V ≤V <sub>CANL</sub> ≤ + 7.0 V                                      | 30                  |     | 50                  | kΩ       |

| R <sub>IN(M)</sub>       | Input resistance matching: [1 – (R <sub>IN(CANH)</sub> ) / (R <sub>IN(CANL</sub> ))] × 100% | V <sub>CANH</sub> = V <sub>CANL</sub> = 5.0 V                                                                | -1                  |     | 1                   | %        |

| V <sub>CCFLTR</sub> TERI | MINAL                                                                                       | -                                                                                                            |                     |     |                     |          |

| V <sub>MEASURE</sub>     | Voltage measured at VCCFLTR terminal                                                        |                                                                                                              | 4.75                | 5   | 5.25                | V        |

| FLTR TERMIN              | NAL                                                                                         |                                                                                                              |                     |     |                     |          |

| V <sub>MEASURE</sub>     | Voltage measured at FLTR pin                                                                |                                                                                                              |                     | 1.5 |                     | V        |

| $C_{(FLTR)}$             | Filter pin capacitor                                                                        | External filter capacitor                                                                                    | 300                 | 330 |                     | nF       |

| INH OUTPUT               | TERMINAL (HIGH VOLTAGE OUTPUT)                                                              |                                                                                                              |                     |     |                     |          |

| $\Delta V_{H}$           | High-level voltage drop INH with respect to $V_{\text{SUP}}$                                | I <sub>INH</sub> = - 0.5 mA                                                                                  |                     | 0.5 | 1                   | V        |

| I <sub>LKG(INH)</sub>    | Leakage current                                                                             | INH = 0 V, Sleep Mode                                                                                        | -0.5                |     | 0.7                 | μΑ       |

| WAKE INPUT               | TERMINAL (HIGH VOLTAGE INPUT)                                                               |                                                                                                              |                     |     |                     |          |

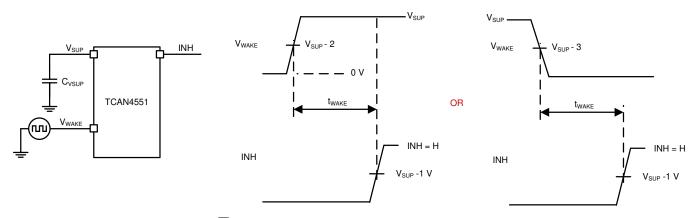

| V <sub>IH</sub>          | High-level input voltage                                                                    | Standby mode, WAKE pin enabled                                                                               | V <sub>SUP</sub> -2 |     |                     | V        |

| V <sub>IL</sub>          | Low-level input voltage                                                                     | Standby mode, WAKE pin enabled                                                                               |                     |     | V <sub>SUP</sub> -3 | V        |

| I <sub>IH</sub>          | High-level input current                                                                    | WAKE = V <sub>SUP</sub> -1 V                                                                                 | -25                 | -15 |                     | μΑ       |

| I <sub>IL</sub>          | Low-level input current                                                                     | WAKE = 1 V                                                                                                   |                     | 15  | 25                  | μΑ       |

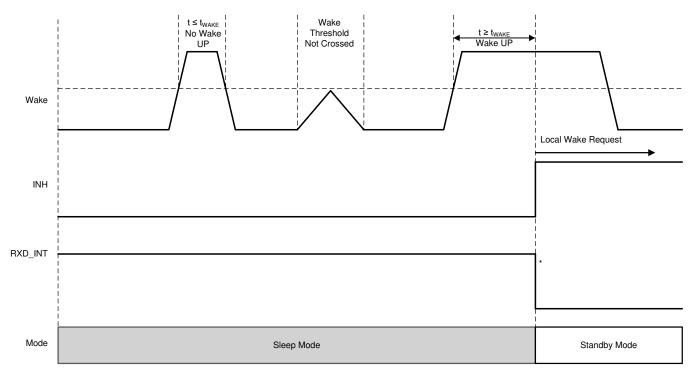

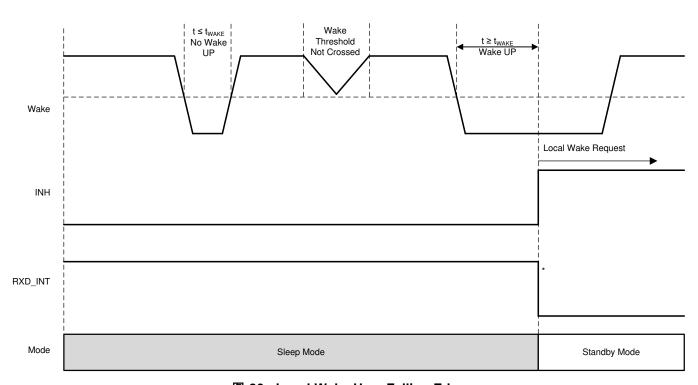

| t <sub>WAKE</sub>        | WAKE filter time                                                                            | Wake up filter time from a wake edge on WAKE; standby, sleep mode                                            | 50                  |     |                     | μs       |

| SDI, SCK, GP             | O1 INPUT TERMINALS                                                                          |                                                                                                              |                     |     |                     |          |

| V <sub>IH</sub>          | High-level input voltage                                                                    |                                                                                                              | 0.7                 |     |                     | $V_{IO}$ |

| V <sub>IL</sub>          | Low-level input voltage                                                                     |                                                                                                              |                     |     | 0.3                 | $V_{IO}$ |

| I <sub>IH</sub>          | High-level input leakage current                                                            | Inputs = V <sub>IO</sub> = 5.25 V                                                                            | -1                  |     | 1                   | μA       |

| I <sub>IL</sub>          | Low-level input leakage current                                                             | Inputs = 0 V, V <sub>IO</sub> = 5.25 V                                                                       | -100                |     | -5                  | μA       |

| C <sub>IN</sub>          | Input capacitance                                                                           | 18 MHz                                                                                                       |                     | 10  | 12                  | pF       |

| VIN .                    | при барабианов                                                                              | TO IVII IZ                                                                                                   |                     | 10  | 12                  |          |

## **Electrical Characteristics (continued)**

over operating free-air temperature range for – 40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C (unless otherwise noted)

|                                                                                              | PARAMETER                                                                                                                                                                                                                                                                                             | TEST CONDITIONS (1)                                                                                              | MIN       | TYP MAX                          | UNIT                                         |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------|----------------------------------------------|

| I <sub>LKG(OFF)</sub>                                                                        | Unpowered leakage current (SDI and SCK only)                                                                                                                                                                                                                                                          | Inputs = 5.25 V, V <sub>IO</sub> = V <sub>SUP</sub> = 0 V                                                        | -1        | 1                                | μΑ                                           |

| nCS INPUT T                                                                                  | ERMINAL                                                                                                                                                                                                                                                                                               |                                                                                                                  |           |                                  |                                              |

| V <sub>IH</sub>                                                                              | High-level input voltage                                                                                                                                                                                                                                                                              |                                                                                                                  | 0.7       |                                  | $V_{IO}$                                     |

| V <sub>IL</sub>                                                                              | Low-level input voltage                                                                                                                                                                                                                                                                               |                                                                                                                  |           | 0.3                              | V <sub>IO</sub>                              |

| I <sub>IH</sub>                                                                              | High-level input leakage current                                                                                                                                                                                                                                                                      | nCS = V <sub>IO</sub> = 5.25 V                                                                                   | -1        | 1                                | μΑ                                           |

| I <sub>IL</sub>                                                                              | Low-level input leakage current                                                                                                                                                                                                                                                                       | nCS = V <sub>IO</sub> = 5.25 V                                                                                   | -50       | <b>-</b> 5                       | μΑ                                           |

| I <sub>LKG(OFF)</sub>                                                                        | Unpowered leakage current                                                                                                                                                                                                                                                                             | $nCS = 5.25 \text{ V}, V_{IO} = V_{SUP} = 0 \text{ V}$                                                           | -1        | 1                                | μΑ                                           |

| RST INPUT T                                                                                  | ERMINAL                                                                                                                                                                                                                                                                                               |                                                                                                                  |           | •                                |                                              |

| V <sub>IH</sub>                                                                              | High-level input voltage                                                                                                                                                                                                                                                                              |                                                                                                                  | 0.7       |                                  | V <sub>IO</sub>                              |

| V <sub>IL</sub>                                                                              | Low-level input voltage                                                                                                                                                                                                                                                                               |                                                                                                                  |           | 0.3                              | $V_{IO}$                                     |

| I <sub>IH</sub>                                                                              | High-level input leakage current                                                                                                                                                                                                                                                                      | RST = V <sub>IO</sub> = 5.25 V                                                                                   | 1         | 10                               | μΑ                                           |

| I <sub>IL</sub>                                                                              | Low-level input leakage current                                                                                                                                                                                                                                                                       | RST = 0 V                                                                                                        | -1        | 1                                | μA                                           |

| I <sub>LKG(OFF)</sub>                                                                        | Unpowered leakage current                                                                                                                                                                                                                                                                             | $RST = V_{IO}, V_{SUP} = 0 V$                                                                                    | -7.5      | 7.5                              | μΑ                                           |

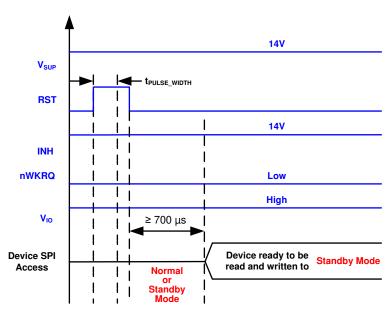

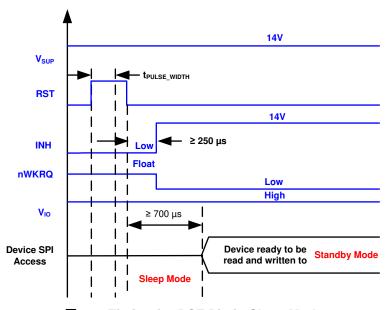

| t <sub>PULSE_WIDTH</sub>                                                                     | Width of the input pulse                                                                                                                                                                                                                                                                              |                                                                                                                  | 30        |                                  | μs                                           |

| SDO, GPO1,<br>OPEN DRAIN                                                                     |                                                                                                                                                                                                                                                                                                       | DRAIIN) and nWKRQ (WHEN PROGRAMN                                                                                 | IED TO WO | ORK OFF OF VIO                   | AND IS                                       |

| V <sub>OH</sub>                                                                              | High-level output voltage                                                                                                                                                                                                                                                                             |                                                                                                                  | 0.8       |                                  | V <sub>IO</sub>                              |

| V <sub>OL</sub>                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                                                                  |           |                                  |                                              |

|                                                                                              | Low-level output voltage                                                                                                                                                                                                                                                                              |                                                                                                                  |           | 0.2                              | V <sub>IO</sub>                              |

| nWKRQ OUT                                                                                    | Low-level output voltage PUT TERMINAL (DEFAULT INTERNAL )                                                                                                                                                                                                                                             | VOLTAGE RAIL)                                                                                                    |           | 0.2                              | V <sub>IO</sub>                              |

|                                                                                              |                                                                                                                                                                                                                                                                                                       | VOLTAGE RAIL)  Default value when based upon internal voltage rail                                               | 2.8       | 3.6                              | V <sub>IO</sub>                              |

| V <sub>OH</sub>                                                                              | PUT TERMINAL (DEFAULT INTERNAL )                                                                                                                                                                                                                                                                      | Default value when based upon internal                                                                           | 2.8       |                                  |                                              |

| V <sub>OH</sub>                                                                              | PUT TERMINAL (DEFAULT INTERNAL \ High-level output voltage                                                                                                                                                                                                                                            | Default value when based upon internal voltage rail  Default value when based upon internal                      | 2.8       | 3.6                              | V                                            |

| V <sub>OH</sub><br>V <sub>OL</sub><br>OSC1 TERMI                                             | PUT TERMINAL (DEFAULT INTERNAL ) High-level output voltage Low-level output voltage                                                                                                                                                                                                                   | Default value when based upon internal voltage rail  Default value when based upon internal                      | 2.8       | 3.6                              | V                                            |

| V <sub>OH</sub><br>V <sub>OL</sub><br>OSC1 TERMI                                             | PUT TERMINAL (DEFAULT INTERNAL ) High-level output voltage Low-level output voltage INAL AND CRYSTAL SPECIFICATION                                                                                                                                                                                    | Default value when based upon internal voltage rail  Default value when based upon internal                      |           | 3.6                              | V                                            |

| V <sub>OH</sub> V <sub>OL</sub> OSC1 TERMI V <sub>IH</sub> V <sub>IL</sub>                   | High-level output voltage  Low-level output voltage  NAL AND CRYSTAL SPECIFICATION  High-level input voltage                                                                                                                                                                                          | Default value when based upon internal voltage rail  Default value when based upon internal                      |           | 3.6<br>0.7                       | V<br>V                                       |

| V <sub>OH</sub> V <sub>OL</sub> OSC1 TERMI V <sub>IH</sub>                                   | PUT TERMINAL (DEFAULT INTERNAL ) High-level output voltage Low-level output voltage NAL AND CRYSTAL SPECIFICATION High-level input voltage Low-level input voltage Clock-In frequency tolerance, see section Crystal and Clock Input                                                                  | Default value when based upon internal voltage rail  Default value when based upon internal voltage rail         | 0.85      | 3.6<br>0.7<br>1.10<br>0.3        | V<br>V<br>V <sub>IO</sub><br>V <sub>IO</sub> |

| V <sub>OH</sub> V <sub>OL</sub> OSC1 TERMI V <sub>IH</sub> V <sub>IL</sub> F <sub>OSC1</sub> | High-level output voltage  Low-level output voltage  NAL AND CRYSTAL SPECIFICATION  High-level input voltage  Low-level input voltage  Clock-In frequency tolerance, see section Crystal and Clock Input Requirements  Clock-In frequency tolerance, see section Crystal and Clock Input Requirements | Default value when based upon internal voltage rail  Default value when based upon internal voltage rail  20 MHz | 0.85      | 3.6<br>0.7<br>1.10<br>0.3<br>0.5 | V V V V V V V V V V V V V V V V V V V        |

<sup>(2)</sup> Specified by design

## 6.8 Timing Requirements

over operating free-air temperature range for – 40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C (unless otherwise noted)

|                              |                                                                     | MIN | TYP | MAX | UNIT |  |  |

|------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|--|--|

| MODE CHANGE TIMES (FULL DEVI | MODE CHANGE TIMES (FULL DEVICE)                                     |     |     |     |      |  |  |

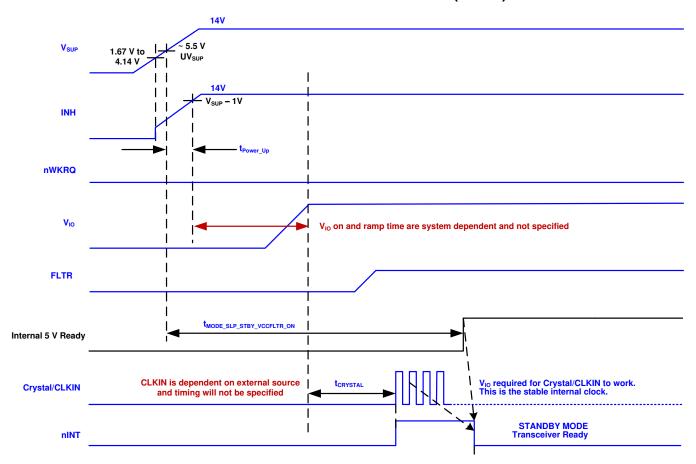

| t <sub>MODE_STBY_NOM</sub>   | Standby to normal mode change time based upon SPI write             |     |     | 70  | μs   |  |  |

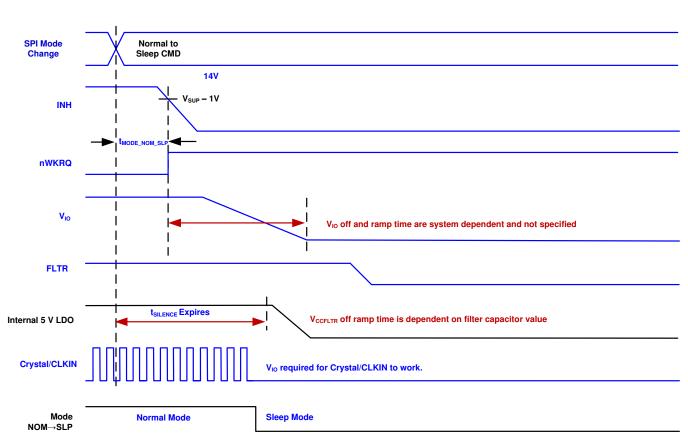

| t <sub>MODE_NOM_SLP</sub>    | SPI write to go to Sleep from Normal: INH and nWKRQ turned off, See | _   |     | 200 | μs   |  |  |

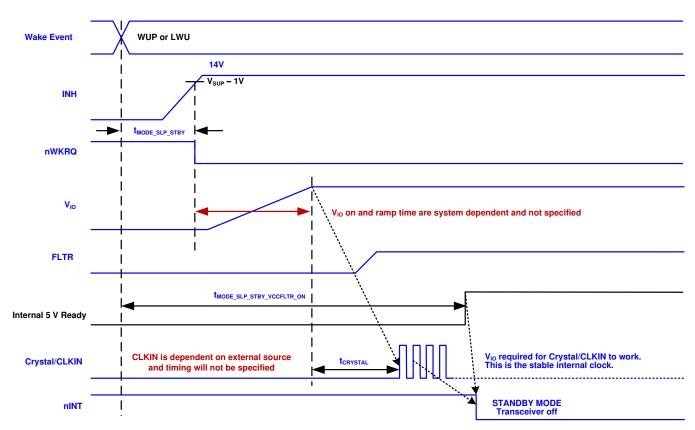

| t <sub>MODE_SLP_STBY</sub>   | WUP or LWU event until INH and nWKRQ asserted, See                  |     |     | 200 | μs   |  |  |

| t <sub>MODE_NOM_STBY</sub>   | SPI write to go to standby from normal mode, See                    |     |     | 200 | μs   |  |  |

## 6.9 Switching Characteristics

over operating free-air temperature range for  $-40 \,^{\circ}\text{C} \le T_A \le 125 \,^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER                |                                                                                                                                                                                        | TEST CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SWITCHING                | CHARACTERISTICS (CAN TRANSCEIVER                                                                                                                                                       | ONLY)                                                                                                                               |     |     |     |      |

| t <sub>pHR</sub>         | Propagation delay time, high TXD_INT to Driver Recessive (1)                                                                                                                           |                                                                                                                                     | 50  | 85  | 110 | ns   |

| t <sub>pLD</sub>         | Propagation delay time, low TXD_INT to driver dominant <sup>(1)</sup>                                                                                                                  | See $\boxed{8}$ 5, RST = 0 V. Typical conditions:<br>R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, R <sub>CM</sub> = open | 35  | 75  | 100 | ns   |

| t <sub>sk(p)</sub>       | Pulse skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  )                                                                                                                                    |                                                                                                                                     |     | 30  | 40  | ns   |

| t <sub>R/F</sub>         | Differential output signal rise time:                                                                                                                                                  |                                                                                                                                     | 8   | 55  | 75  | ns   |

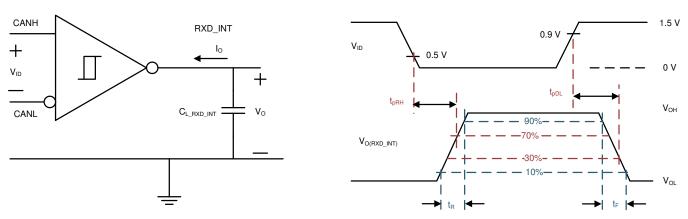

| t <sub>pRH</sub>         | Propagation delay time, bus recessive input to high RXD_INT output                                                                                                                     | See 图 6, typical conditions: CANL = 1.5                                                                                             | 35  | 55  | 90  | ns   |

| t <sub>pDL</sub>         | Propagation delay time, bus dominant input to RXD_INT low output                                                                                                                       | V, CANH = 3.5 V.                                                                                                                    | 35  | 55  | 90  | ns   |

| t <sub>pHR</sub>         | Propagation delay time, high TXD_INT to Driver Recessive <sup>(1)</sup>                                                                                                                |                                                                                                                                     | 50  | 85  | 120 | ns   |

| t <sub>pLD</sub>         | Propagation delay time, low TXD_INT to driver dominant <sup>(1)</sup>                                                                                                                  | See $\blacksquare$ 5, RST = 0 V. Typical conditions: $R_L = 60 \Omega$ , $C_L = 100 pF$ , $R_{CM} = open V_{IO}$                    | 35  | 75  | 110 | ns   |

| t <sub>sk(p)</sub>       | Pulse skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  )                                                                                                                                    | = 1.8 V                                                                                                                             |     | 30  | 40  | ns   |

| t <sub>R/F</sub>         | Differential output signal rise time:                                                                                                                                                  |                                                                                                                                     | 8   | 55  | 75  | ns   |

| t <sub>pRH</sub>         | Propagation delay time, bus recessive input to high RXD_INT output                                                                                                                     | See 图 6, typical conditions: CANL = 1.5                                                                                             | 35  | 55  | 105 | ns   |

| t <sub>pDL</sub>         | Propagation delay time, bus dominant input to RXD_INT low output                                                                                                                       | V, CANH = 3.5 V. V <sub>IO</sub> = 1.8 V                                                                                            | 35  | 55  | 105 | ns   |

| DEVICE SWI               | TCHING CHARACTERISTICS                                                                                                                                                                 |                                                                                                                                     |     |     | 1   |      |

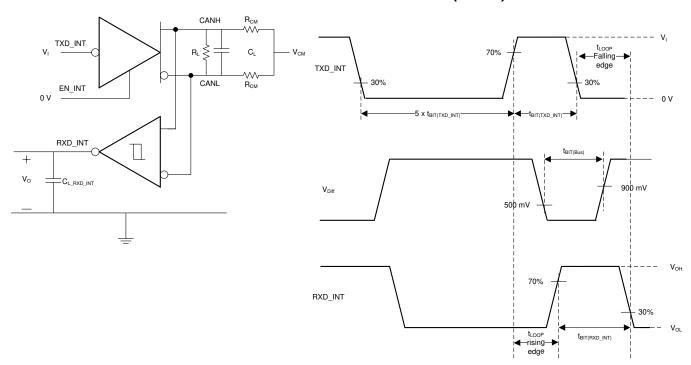

| t <sub>LOOP</sub>        | Loop delay (2)(CAN transceiver only)                                                                                                                                                   | See $\P$ 7, RST = 0 V. typical conditions:<br>R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, C <sub>RXD</sub> = 15 pF      |     |     | 235 | ns   |

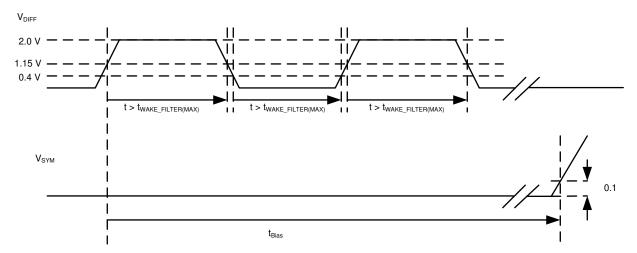

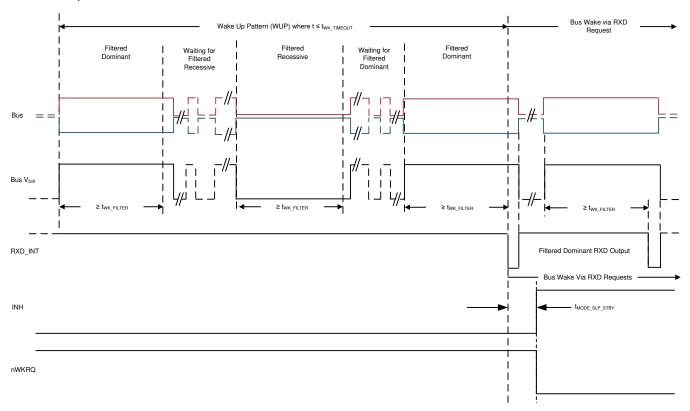

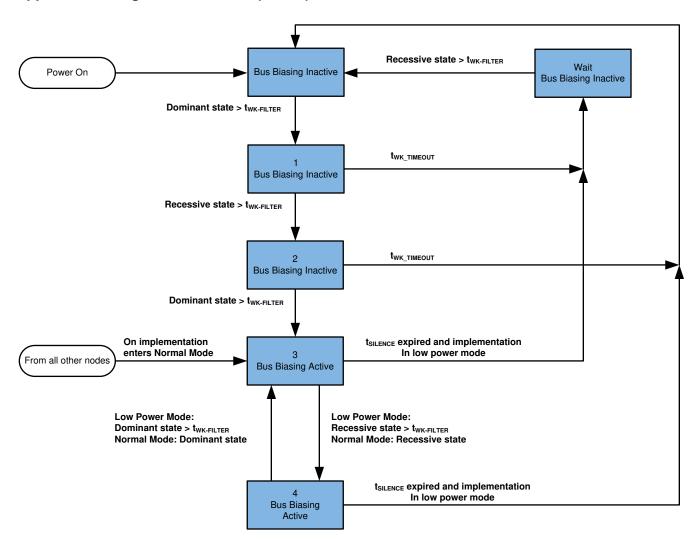

| t <sub>WK_FILTER</sub>   | Bus time to meet filtered bus requirements for wake up request                                                                                                                         | See 图 23, standby mode.                                                                                                             | 0.5 |     | 1.8 | μs   |

| t <sub>WK_TIMEOUT</sub>  | Bus wake-up timeout: time that a WUP must take place within to be considered valid                                                                                                     | See 图 23                                                                                                                            | 0.5 |     | 2.9 | ms   |

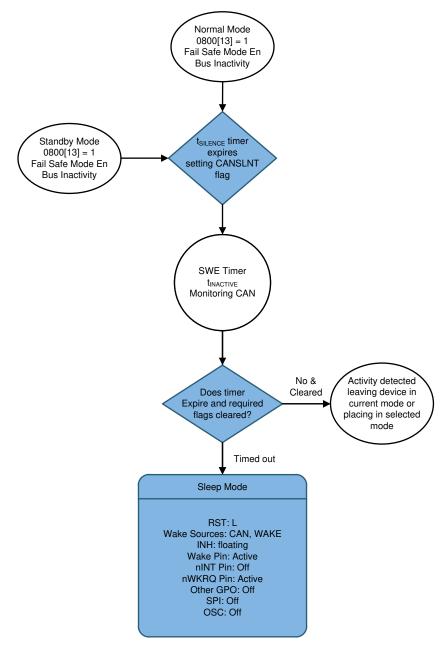

| tSILENCE                 | Timeout for bus inactivity (3)                                                                                                                                                         | Timer is reset and restarted when bus changes from dominant to recessive or vice versa.                                             | 0.6 |     | 1.2 | s    |

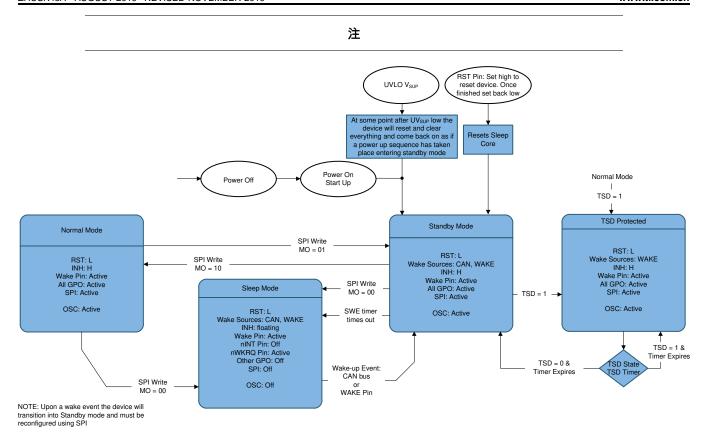

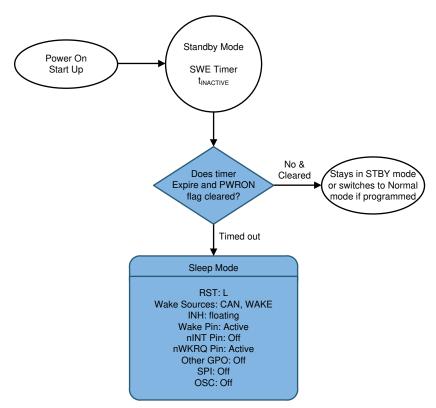

| <sup>t</sup> inactive    | Time required for the processor to clear wake flag or put the device into normal mode upon power up, power on reset or after wake event otherwise the device will enter sleep mode (3) |                                                                                                                                     | 2   | 4   | 6   | min  |

| t <sub>Bias</sub>        | Time from the start of a dominant-recessive-dominant sequence                                                                                                                          | Each phase 6 μs until V <sub>sym</sub> ≥ 0.1. See<br>☑ 11                                                                           |     |     | 250 | μs   |

| t <sub>Power_Up</sub>    | Power up time on V <sub>SUP</sub> <sup>(3)</sup>                                                                                                                                       | See 图 14                                                                                                                            |     |     | 250 | μs   |

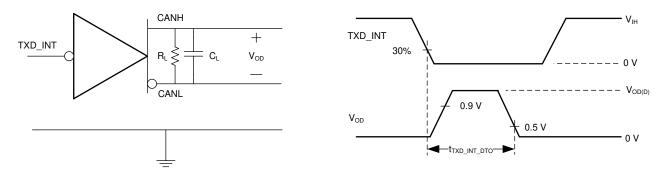

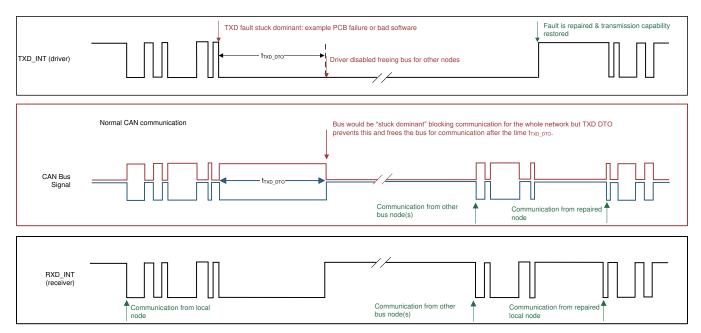

| t <sub>TXD_INT_DTO</sub> | Dominant time out <sup>(4)</sup> (CAN transceiver only) <sup>(1)</sup>                                                                                                                 | See 🛭 24, R <sub>I</sub> = 60 Ω, C <sub>I</sub> = open                                                                              | 1   |     | 5   | ms   |

<sup>(1)</sup> All TXD\_INT, RXD\_INT, EN\_INT and CAN transceiver only references are for internal nodes that represent the same functions for a stand-alone transceiver.

<sup>(2)</sup> Time span from signal edge on TXD\_INT input to next signal edge with same polarity on RXD output, the maximum of delay of both signal edges is to be considered.

<sup>(3)</sup> Specified by design

<sup>(4)</sup> The TXD\_INT dominant time out (t<sub>TXD\_INT\_DTO</sub>) disables the driver of the transceiver once the TXD\_INT has been dominant longer than t<sub>TXD\_INT\_DTO</sub>, which releases the bus lines to recessive, preventing a local failure from locking the bus dominant. The driver may only transmit dominant again after TXD\_INT has been returned HIGH (recessive). While this protects the bus from local faults, locking the bus dominant, it limits the minimum data rate possible. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD\_INT) for the worst case, where five successive dominant bits are followed immediately by an error frame. This, along with the t<sub>TXD\_INT\_DTO</sub> minimum, limits the minimum bit rate. The minimum bit rate may be calculated by: Minimum Bit Rate = 11/t<sub>TXD\_INT\_DTO</sub> = 11 bits / 1.2 ms = 9.2 kbps.

# **Switching Characteristics (continued)**

over operating free-air temperature range for  $-40~^{\circ}\text{C} \le T_{\text{A}} \le 125~^{\circ}\text{C}$  (unless otherwise noted)

|                                        | PARAMETER                                                  | TEST CONDITIONS                                                                                                                                                        | MIN | TYP | MAX | UNIT |

|----------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>Bit(Bus)2M</sub>                | Transmitted recessive bit width @ 2 Mbps                   | See <b>8</b> 6, RST = 0 V typical conditions:                                                                                                                          | 435 |     | 530 | ns   |

| t <sub>Bit(Bus)5M</sub>                | Transmitted recessive bit width @ 5 Mbps                   | $R_L = 60 \Omega, C_L = 100 \text{pF}, C_{RXD} = 15 \text{pF}$                                                                                                         | 155 |     | 210 | ns   |

| t <sub>Bit(Bus)8M</sub> (5)            | Transmitted recessive bit width @ 8 Mbps                   | See $\boxtimes$ 6, RST = 0 V typical conditions:<br>R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, C <sub>RXD</sub> = 15 pF,<br>V <sub>IO</sub> $\ge$ 3.135 V | 80  |     | 135 | ns   |

| t <sub>Bit(Bus)8M</sub> <sup>(5)</sup> | Transmitted recessive bit width @ 8 Mbps                   | See $\boxtimes$ 6, RST = 0 V typical conditions: R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, C <sub>RXD</sub> = 15 pF, V <sub>IO</sub> = 1.8 V             | 80  |     | 135 | ns   |

| t <sub>Bit(RXD)2M</sub>                | Received recessive bit width @ 2 Mbps                      | See 图 6, RST = 0 V typical conditions:                                                                                                                                 | 400 |     | 550 | ns   |

| t <sub>Bit(RXD)5M</sub>                | Received recessive bit width @ 5 Mbps                      | $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{RXD} = 15 pF$ , $V_{IO} \ge 3.135 V$                                                                                          | 120 |     | 220 | ns   |

| t <sub>Bit(RXD)2M</sub>                | Received recessive bit width @ 2 Mbps                      | See 图 6, RST = 0 V typical conditions:                                                                                                                                 | 394 |     | 550 | ns   |

| t <sub>Bit(RXD)5M</sub>                | Received recessive bit width @ 5 Mbps                      | $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{RXD} = 15 pF$ , $V_{IO} = 1.8 V$                                                                                              | 114 |     | 220 | ns   |

| t <sub>Bit(RXD)8M</sub> (5)            | Received recessive bit width @ 8 Mbps                      | See $\boxtimes$ 6, RST = 0 V typical conditions:<br>R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, C <sub>RXD</sub> = 15 pF,<br>V <sub>IO</sub> $\ge$ 3.135 V | 80  |     | 135 | ns   |

| t <sub>Bit(RXD)8M</sub> <sup>(5)</sup> | Received recessive bit width @ 8 Mbps                      | See $\boxtimes$ 6, RST = 0 V typical conditions:<br>R <sub>L</sub> = 60 $\Omega$ , C <sub>L</sub> = 100 pF, C <sub>RXD</sub> = 15 pF,<br>V <sub>IO</sub> = 1.8 V       | 72  |     | 135 | ns   |

| (6)                                    | Receiver Timing symmetry @ 2 Mbps See 图 6, RST = 0 V typic |                                                                                                                                                                        | -65 | 30  | 40  | ns   |

| $\Delta t_{Rec}^{(6)}$                 | Receiver Timing symmetry @ 5 Mbps                          | $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{RXD} = 15 pF$ , $V_{IO} \ge 3.135 V$                                                                                          | -45 | 5   | 15  | ns   |

| (6)                                    | Receiver Timing symmetry @ 2 Mbps                          | See 图 6, RST = 0 V typical conditions:                                                                                                                                 | -71 | 30  | 40  | ns   |

| ∆t <sub>Rec</sub> <sup>(6)</sup>       | Receiver Timing symmetry @ 5 Mbps                          | $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{RXD} = 15 pF$ , $V_{IO} 1.8 V$                                                                                                | -51 | 5   | 15  | ns   |

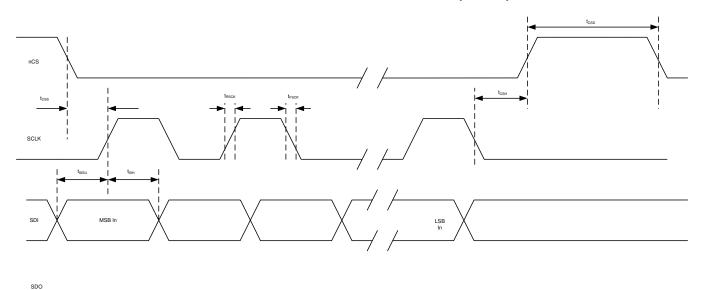

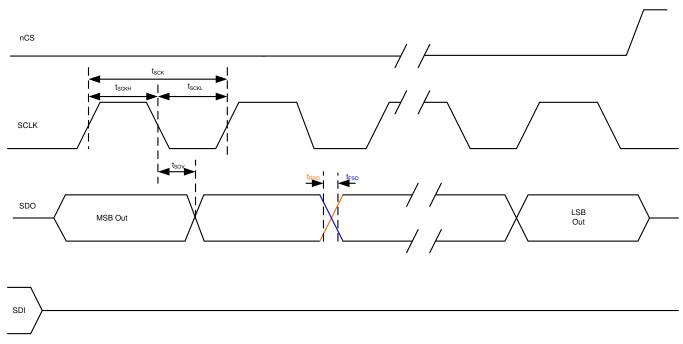

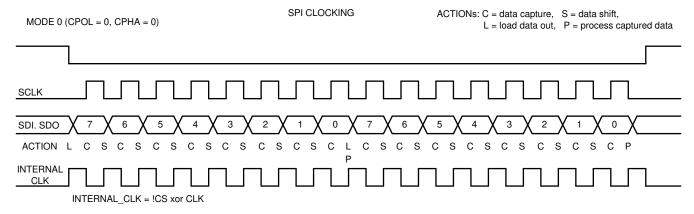

| SPI SWITCHI                            | NG CHARACTERISTICS                                         |                                                                                                                                                                        |     |     |     |      |

| f <sub>SCK</sub>                       | SCK, SPI clock frequency (3)                               |                                                                                                                                                                        |     |     | 18  | MHz  |

| t <sub>SCK</sub>                       | SCK, SPI clock period (3)                                  | See 图 13                                                                                                                                                               | 56  |     |     | ns   |

| t <sub>RSCK</sub>                      | SCK rise time (3)                                          | See 图 12                                                                                                                                                               |     |     | 10  | ns   |

| t <sub>FSCK</sub>                      | SCK fall time (3)                                          | See 图 12                                                                                                                                                               |     |     | 10  | ns   |

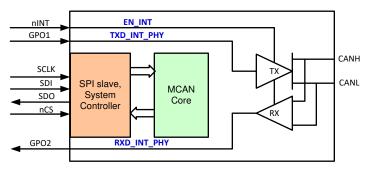

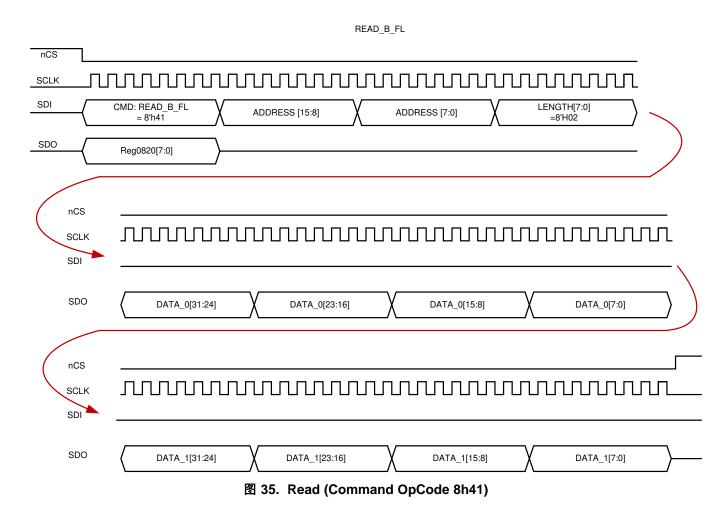

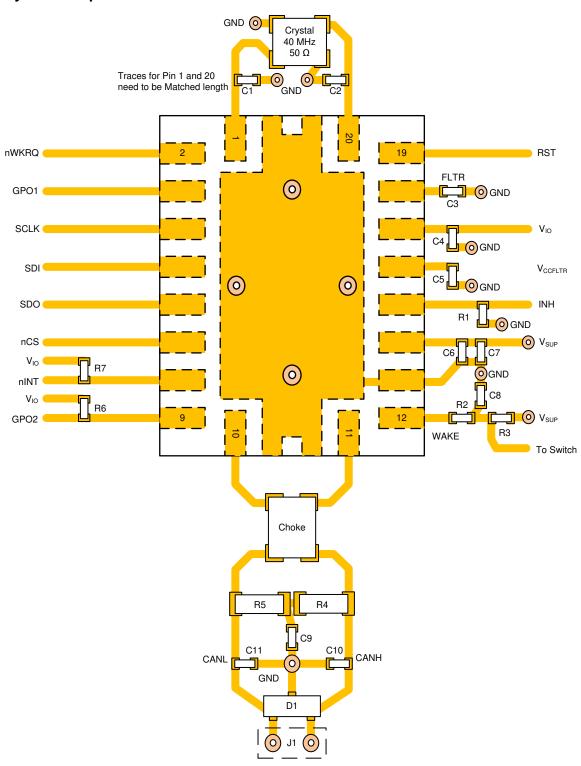

| t <sub>SCKH</sub>                      | SCK, SPI clock high (3)                                    | See 图 13                                                                                                                                                               | 18  |     |     | ns   |